JP2008305937A - 電子部品内蔵モジュールおよびその製造方法 - Google Patents

電子部品内蔵モジュールおよびその製造方法 Download PDFInfo

- Publication number

- JP2008305937A JP2008305937A JP2007151147A JP2007151147A JP2008305937A JP 2008305937 A JP2008305937 A JP 2008305937A JP 2007151147 A JP2007151147 A JP 2007151147A JP 2007151147 A JP2007151147 A JP 2007151147A JP 2008305937 A JP2008305937 A JP 2008305937A

- Authority

- JP

- Japan

- Prior art keywords

- insulating layer

- electronic component

- component built

- wiring

- module

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/18—Printed circuits structurally associated with non-printed electric components

- H05K1/182—Printed circuits structurally associated with non-printed electric components associated with components mounted in the printed circuit board, e.g. insert mounted components [IMC]

- H05K1/185—Components encapsulated in the insulating substrate of the printed circuit or incorporated in internal layers of a multilayer circuit

- H05K1/186—Components encapsulated in the insulating substrate of the printed circuit or incorporated in internal layers of a multilayer circuit manufactured by mounting on or connecting to patterned circuits before or during embedding

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73253—Bump and layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00011—Not relevant to the scope of the group, the symbol of which is combined with the symbol of this group

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/191—Disposition

- H01L2924/19101—Disposition of discrete passive components

- H01L2924/19105—Disposition of discrete passive components in a side-by-side arrangement on a common die mounting substrate

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0201—Thermal arrangements, e.g. for cooling, heating or preventing overheating

- H05K1/0203—Cooling of mounted components

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/02—Fillers; Particles; Fibers; Reinforcement materials

- H05K2201/0203—Fillers and particles

- H05K2201/0206—Materials

- H05K2201/0209—Inorganic, non-metallic particles

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10227—Other objects, e.g. metallic pieces

- H05K2201/10378—Interposers

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10431—Details of mounted components

- H05K2201/1056—Metal over component, i.e. metal plate over component mounted on or embedded in PCB

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/22—Secondary treatment of printed circuits

- H05K3/28—Applying non-metallic protective coatings

- H05K3/284—Applying non-metallic protective coatings for encapsulating mounted components

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/40—Forming printed elements for providing electric connections to or between printed circuits

- H05K3/4038—Through-connections; Vertical interconnect access [VIA] connections

- H05K3/4053—Through-connections; Vertical interconnect access [VIA] connections by thick-film techniques

- H05K3/4069—Through-connections; Vertical interconnect access [VIA] connections by thick-film techniques for via connections in organic insulating substrates

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4611—Manufacturing multilayer circuits by laminating two or more circuit boards

- H05K3/4614—Manufacturing multilayer circuits by laminating two or more circuit boards the electrical connections between the circuit boards being made during lamination

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4611—Manufacturing multilayer circuits by laminating two or more circuit boards

- H05K3/4614—Manufacturing multilayer circuits by laminating two or more circuit boards the electrical connections between the circuit boards being made during lamination

- H05K3/462—Manufacturing multilayer circuits by laminating two or more circuit boards the electrical connections between the circuit boards being made during lamination characterized by laminating only or mainly similar double-sided circuit boards

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/49—Method of mechanical manufacture

- Y10T29/49002—Electrical device making

- Y10T29/49117—Conductor or circuit manufacturing

Abstract

【課題】優れた放熱特性を有し、また製造工程の簡素化や部材の削減を図れる電子部品内蔵モジュールを提供する。

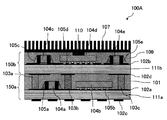

【解決手段】電子部品104a〜104bを内蔵した第1の部品内蔵基板150a上に、電子部品104c〜104eを内蔵した第2の部品内蔵基板150bが積層され、更に当該第2の部品内蔵基板150b上に放熱器107が取り付けられている。第2の部品内蔵基板150bは、一主面に電子部品が実装された配線層102bと、無機フィラと熱硬化性樹脂とを含む混合物を主成分とし、配線層102b上に実装された電子部品104c〜104eが埋設された絶縁層109とを備える。第2の部品内蔵基板150bの絶縁層109は、電子部品104c〜104eや配線層102bから出される熱を放熱器107に伝える。

【選択図】図1

【解決手段】電子部品104a〜104bを内蔵した第1の部品内蔵基板150a上に、電子部品104c〜104eを内蔵した第2の部品内蔵基板150bが積層され、更に当該第2の部品内蔵基板150b上に放熱器107が取り付けられている。第2の部品内蔵基板150bは、一主面に電子部品が実装された配線層102bと、無機フィラと熱硬化性樹脂とを含む混合物を主成分とし、配線層102b上に実装された電子部品104c〜104eが埋設された絶縁層109とを備える。第2の部品内蔵基板150bの絶縁層109は、電子部品104c〜104eや配線層102bから出される熱を放熱器107に伝える。

【選択図】図1

Description

本発明は、電子部品が電気絶縁性基板の内部に配置される電子部品内蔵モジュールおよびその製造方法に関する。

近年のエレクトロニクス機器の小型化や薄型化、高機能化に伴って、プリント基板に実装される電子部品の高密度化、および電子部品が実装されたプリント基板の高機能化の要求が益々強くなっている。このような状況の中、電子部品を基板中に埋め込んだ電子部品内蔵モジュールが開発されている(例えば、特許文献1参照)。

通常のプリント基板では、能動部品(例えば、半導体素子)や受動部品(例えば、コンデンサ)は基板の表面に実装されている。これに対し電子部品内蔵モジュールでは、別のプリント基板や電子部品内蔵モジュールを三次元的に重ね合わせて立体回路を容易に構成できる。また、同数の部品の実装に必要とされる面積は、1枚の基板に実装する場合に比べて、立体回路ではほぼ重ね合われた基板の枚数分の1程度でよい。また、立体回路では、部品の平面的距離を小さくできるので、基板の表面に電子部品を実装する場合と比較して、部品を配置する自由度が高まるため、電子部品間の配線の最適化によって高周波特性の改善なども見込まれる。

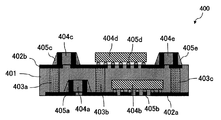

図6を参照して、特許文献1に開示された電子部品内蔵モジュールについて説明する。電子部品内蔵モジュール400は、絶縁性基板401と、配線層402aおよび402bとを含む。配線層402aの一主面に電子部品404aおよび404bがそれぞれ半田405aおよび405bによって接続されて配置されている。同様に配線層402bの一主面に電子部品404c、404dおよび404eがそれぞれ半田405c、405d、405eによって接続されて配置されている。

配線層402aおよび配線層402bは、それぞれ電子部品が実装されている面が同一の方向(図6においては上面)に位置する様に、絶縁性基板401を介して概ね平行に配置されている。

つまり、本例においては、配線層402aに実装された電子部品404aおよび404bは絶縁性基板401の内部に埋設されており、高密度部品実装が図られている。また絶縁性基板401の内部にはインナービア403a、403bおよび403cが配設され、配線層402aと402bとの間の電気的な接続が確保されている。

各構成部材の材質について簡単に説明すると、絶縁性基板401は、無機フィラと熱硬化性樹脂とを含む混合物を主成分とする。配線層402aおよび402bは電気伝導性を有する物質、例えば、銅箔や導電性樹脂組成物で形成されている。インアービア403a、403bおよび403cは、例えば熱硬化性の導電物質からなる。熱硬化性の導電性物質としては、例えば金属粒子と熱硬化性樹脂とを混合した導電性樹脂組成物が用いられる。

近年の半導体プロセスの進化に伴い、半導体部品からの発熱量が急激に増大化しており、その放熱対策が問題となっている。上述した電子部品内蔵モジュール400は、このような半導体部品の実装を前提としている。配線層402aに実装される半導体部品は絶縁性基板401に埋設されるため、モジュール内部から外部へ熱を積極的に逃がすための放熱対策が不可欠である。

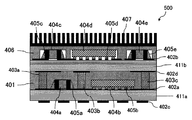

図7に、放熱対策を施した従来の電子部品内蔵モジュール500の構成を示す。電子部品内蔵モジュール500においては、上述の電子部品内蔵モジュール400の(図6)配線層402aの下面に多層の配線基板411aが設けられている。多層の配線基板411aの下面には複数の電極402cが設けられている。配線層402aと電極402cは、配線基板411aの内部に設けられた配線(図示せず)によって互いに接続されている。

配線層402bの下面には、配線層402aにおけるのと同様に、多層の配線基板411bおよび電極402dが設けられている。配線層402bと電極402dは、配線基板411bの内部に設けられた配線(図示せず)によって互いに接続されている。なお、電極402dは、インアービア403a、403b、および403cに接続されている。

配線層402bの上面側には、放熱シート406およびヒートシンク(放熱器)407が設けられている。放熱シート406やヒートシンク407は、接着やネジ止めなどにより配線層402bあるいは配線基板411bに固定されている。なお、放熱シート406には、電子部品404c、404d、および404eと半田405cおよび405eの部材を収納するための凹部(空間)が設けられている。これら凹部は収納する部材の外形より大きめに形成されている。

電子部品内蔵モジュール500の放熱メカニズムについて簡単に説明する。電子部品内蔵モジュール500においては、発熱源である電子部品404a〜404eから発生した熱は、主に熱伝導により放熱シート406を介してヒートシンク407に導かれ、ヒートシンク407から空気中に放出される。

絶縁性基板401に埋設された電子部品404aおよび404bのうち、特に半導体パッケージ部品では大量の熱が発生する。その対策として、絶縁性基板401に無機フィラを大量に添加することで熱伝導性能を高めている。電子部品404aや404bで発生した熱は、伝導により絶縁性基板401中に発散した後、熱を伝え易い配線層402d、配線基板411b中の配線および配線層402bを介して配線基板411bの上面まで伝わる。

放熱シート406には、電子部品404c〜404eの形状に合わせて凹部が形成されており、電子部品404c〜404eの背面や側面の一部が放熱シート406に接している。電子部品404c〜404eで発生した熱は、放熱シート406に接する部分を介してヒートシンク407に伝わり、空気中へ放出される。放熱シート406に電子部品の形状に合わせた凹部を形成することによって、放熱シート406と電子部品404c〜404eとの接触面積が高まり、熱伝導量が増加する。

次に、図8を参照して、図7に示す電子部品内蔵モジュールの製造方法について簡単に説明する。図8(a)に示すように、予め無機フィラと未硬化状態の熱硬化性樹脂の混合物がシート状に加工されて絶縁性基板401が形成される。続いて絶縁性基板401の所定の位置に貫通孔が形成され、その貫通孔に熱硬化性の導電物質を充填して、インナービア403a〜403cが形成される。

別途、図8(b)に示すように、多層の配線基板111aの一主面に形成された配線層402a上に、予め電子部品404aおよび404bが実装される。

次に、図8(c)に示すように、配線基板411aの主面上の所定の位置に、所定の向きで絶縁性基板401が載置され、さらにその上に、所定の位置に所定の向きで、配線基板411bが載置される。しかる後、配線基板411a、絶縁性基板401および配線基板411bを熱プレス板408aおよび408bで挟み込んで加圧および加熱処理が行われる。

図8(d)に示す加圧・過熱処理の際、熱プレス板408aおよび408bによって矢印方向に圧力が加えられ、電子部品404aおよび404bは絶縁性基板401に埋設される。その後、絶縁性基板401およびインナービア403a〜403c中の熱硬化性樹脂が硬化して、配線基板411a、絶縁性基板401および配線基板411bが一体化する。一体化と同時に、インナービア403a〜403cは配線層402aおよび402dと接続される。

その後、図8(e)に示すように、配線層402b上に、半田405a〜405cを用いて電子部品404c〜404eが実装される。

最後に、図8(f)に示すように、電子部品404c〜404eの形状に合わせて予め凹部が形成された放熱シート406とヒートシンク407が、順次所定の位置および所定の向きに載置され固定される。このようにして図8(g)に示す放熱対策が施された電子部品内蔵モジュール500が得られる。

特許第3375555号

特許第3547423号

上述したような、放熱シート406を用いた従来の放熱構造では、配線層402b上に実装される電子部品の位置や形状に合わせて放熱シート406に凹部を形成する必要がある。しかしモジュールによって電子部品の位置や形状が様々であるため、製造の都度、放熱シートに形成する凹部の位置や大きさを変更する必要がある。結果、電子部品内蔵モジュールを製造する際のコストアップにつながる。

さらに、放熱シート406に、電子部品の実装される姿に対応した凹部を形成することは、放熱シートのコストアップにつながる。このため凹部として直方体や円筒等の比較的加工しやすい形状が採用される。さらに、複数の電子部品を収納するために、電子部品間のピッチ誤差を考慮して、凹部のピッチの許容差も大きく設定する必要がある。

結果、電子部品が放熱シート406と接する面積は限られると共に、電子部品と放熱シート406との間に比較的大きな空気層が形成される。電子部品で発生した熱は、主として放熱シート406と接触する部分を介して熱伝導により拡散する。空気層が多いと、その分、放熱シート406への熱の伝導量が低下する。

また放熱シート406に形成される凹部のサイズは、囲う電子部品の実装位置や部品形状のバラツキ、さらには、半田材料のはみ出し量のバラツキを考慮して、一回り大きくする必要がある。結果として電子部品との接触面積が少なくなり、熱の伝導量がさらに低下する。

また、実装後の高さのバラツキにより電子部品の背面が放熱シート406に接触しない場合が生じる。このような場合、さらに熱伝導量を下げることになる。特に、半導体パッケージ部品の背面の接触面積が少ないと、異常な温度上昇が発生することとなり、半導体パッケージ部品の動作不良や故障を発生させる原因となる。

さらに、電子部品がCPU等の大量に熱を発生する半導体パッケージ部品である場合、動作中に温度が100℃程度まで上昇する。通常、放熱シート406は配線基板411bに接着されているため、凹部内の空気層は閉じられた空間内にある。従って、電子部品の温度が上昇すると、空気層もそれに伴って暖められて膨張する。最悪の場合、空気層の圧力によって電子部品が破損したり、放熱シート406が配線基板111bから剥離して、耐湿特性等が悪化する原因ともなる。

また図7では、電子部品が実装された配線基板が2枚積層された電子部品内蔵モジュールの例を示している。今後、高実装密度化の要請に応えて3枚以上の配線基板を積層した電子部品内蔵モジュールが開発される可能性が高い。積層される配線基板の数が増えるほど電子部品から発生する熱量の総和は増加する。多層の電子部品内蔵モジュールでは、下層の配線基板から放出される熱は、主として各層の配線を通って最上層の配線まで伝わる。最上層の配線に伝わった熱は、配線に接する放熱シートを介してヒートシンクに伝わる。

従って、ヒートシンクから外部に放出される熱量を増やすためには、配線と接する放熱シートの面積を増やす必要がある。しかし配線と接する放熱シートの面積は、実装密度との関係で決まるため、安易に増やすことはできない。このため、下層の配線基板で発生した熱量をヒートシンクに伝えるのには限界がある。

また、電子部品内蔵モジュールの製造工程において、放熱シートを加工する工程や、放熱シート及びヒートシンクを載置して固定する工程が付加されることとなる。このような工程の付加は、電子部品内蔵モジュールの製造コストを上昇させる要因となる。

本発明はかかる点に鑑みてなされたものであり、その主たる目的は、優れた放熱特性を有し、しかも放熱対策のために付加される工程の少ない電子部品内蔵モジュールを提供することにある。

上記目的を達成するため、本発明に係る電子部品内蔵モジュールは、

電子部品を内蔵した第1の部品内蔵基板上に、電子部品を内蔵した第2の部品内蔵基板が積層され、更に当該第2の部品内蔵基板上に放熱器が取り付けられた電子部品内蔵モジュールであって、

前記第1の部品内蔵基板は、

一主面に電子部品が実装された第1の配線層と、

無機フィラと熱硬化性樹脂とを含む混合物を主成分とし、前記第1の配線層上に実装された前記電子部品が埋設され、かつ電気接続用のインナービアが形成された第1の絶縁層とを備え、

前記第2の部品内蔵基板は、

一主面に電子部品が実装された第2の配線層と、

無機フィラと熱硬化性樹脂とを含む混合物を主成分とし、前記第2の配線層上に実装された前記電子部品が埋設された第2の絶縁層とを備える。

電子部品を内蔵した第1の部品内蔵基板上に、電子部品を内蔵した第2の部品内蔵基板が積層され、更に当該第2の部品内蔵基板上に放熱器が取り付けられた電子部品内蔵モジュールであって、

前記第1の部品内蔵基板は、

一主面に電子部品が実装された第1の配線層と、

無機フィラと熱硬化性樹脂とを含む混合物を主成分とし、前記第1の配線層上に実装された前記電子部品が埋設され、かつ電気接続用のインナービアが形成された第1の絶縁層とを備え、

前記第2の部品内蔵基板は、

一主面に電子部品が実装された第2の配線層と、

無機フィラと熱硬化性樹脂とを含む混合物を主成分とし、前記第2の配線層上に実装された前記電子部品が埋設された第2の絶縁層とを備える。

ここで、前記第2の絶縁層のうち前記放熱器と接する面に凹部が形成され、当該凹部には前記第2の絶縁層の主成分である混合物より熱伝導性の高い物質が充填されていることが好ましい。また前記第1の絶縁層の混合物と前記第2の絶縁層の混合物は同一の組成であることが好ましい。

また前記第1および第2の配線層は、それぞれ多層の配線基板上に形成されていてもよい。また前記第2の絶縁層と前記放熱器が一体に構成されていてもよく、前記剤2の絶縁層と前記放熱器は同一の物質で形成されていてもよい。

また上記目的を達成する本発明に係る電子部品内臓モジュールの製造方法は、

一主面に電子部品が実装された第1および第2の配線層を用意する工程と、

無機フィラと未硬化状態の熱硬化性樹脂とを含む混合物をシート状に成形して第1の絶縁層を用意すると共に、前記第1の絶縁層に貫通孔を形成し、当該貫通孔に未硬化状態の熱硬化性の導電性物質を充填する工程と、

無機フィラと未硬化状態の熱硬化性樹脂とを含む混合物をシート状に成形して第2の絶縁層を用意する工程と、

前記第1の配線層、前記第1の絶縁層、前記第2の配線層および前記第2の絶縁層を、それぞれが位置合わせされた状態で、かつ前記第1および第2の配線層の電子部品が実装された主面を上にして積層する工程と、

積層された前記第1の配線層、前記第1の絶縁層、前記第2の配線層および前記第2の絶縁層を、一対の熱プレス板で挟んだ状態で加圧および加熱して一体化する工程と

を含む。

一主面に電子部品が実装された第1および第2の配線層を用意する工程と、

無機フィラと未硬化状態の熱硬化性樹脂とを含む混合物をシート状に成形して第1の絶縁層を用意すると共に、前記第1の絶縁層に貫通孔を形成し、当該貫通孔に未硬化状態の熱硬化性の導電性物質を充填する工程と、

無機フィラと未硬化状態の熱硬化性樹脂とを含む混合物をシート状に成形して第2の絶縁層を用意する工程と、

前記第1の配線層、前記第1の絶縁層、前記第2の配線層および前記第2の絶縁層を、それぞれが位置合わせされた状態で、かつ前記第1および第2の配線層の電子部品が実装された主面を上にして積層する工程と、

積層された前記第1の配線層、前記第1の絶縁層、前記第2の配線層および前記第2の絶縁層を、一対の熱プレス板で挟んだ状態で加圧および加熱して一体化する工程と

を含む。

本発明に係る電子部品内蔵モジュールの製造方法は、一体化された前記第1の配線層、前記第1の絶縁層、前記第2の配線層および前記第2の絶縁層の上に放熱器を載置し固定する工程を更に含んでいてもよい。また前記第2の絶縁層の一主面に凹部を形成し、当該凹部に前記第2の絶縁層の主成分である混合物より熱伝導性の高い物質を充填する工程を更に含んでいてもよい。

本発明によれば、放熱対策のため従来必要であった工程や部材を削減でき、また、内部の熱伝導特性の向上に伴って優れた放熱特性を発揮できる。結果、低コストで高性能、高品質な電子部品内蔵モジュールを提供できる。

(実施の形態1)

図1に本発明の実施の形態1に係る電子部品内蔵モジュールの構成を示す。本実施の形態に係る電子部品内蔵モジュール100Aは、部品内蔵基板150aの上に部品内蔵基板150bが積層され、更にその上に放熱器であるヒートシンク107が取り付けられている。

図1に本発明の実施の形態1に係る電子部品内蔵モジュールの構成を示す。本実施の形態に係る電子部品内蔵モジュール100Aは、部品内蔵基板150aの上に部品内蔵基板150bが積層され、更にその上に放熱器であるヒートシンク107が取り付けられている。

部品内蔵基板150aは、上面に配線層102aが形成され下面に配線層102cが形成された配線基板111aと、配線基板111a上に形成された電気絶縁層(以後、「絶縁層」と略す)101で構成されている。

絶縁層101の内部には、半田105aおよび105bによって配線層102aに接続された電子部品104aおよび104bが埋設されている。また絶縁層101の内部には、配線層102aと後述する部品内蔵基板150bの配線層102dを電気的に接続するインナービア103a、103bおよび103cが配設されている。

絶縁層101は、無機フィラと熱硬化性樹脂とを含む混合物を主成分とする。前述したように無機フィラは熱伝導性に優れた材料である。無機フィラには、例えばAl2O3、MgO、BN、AlN、またはSiO2などを用いることができる。無機フィラは、混合物に対して70重量%から95重量%であることが好ましい。

熱硬化性樹脂としては、例えば、耐熱性が高いエポキシ樹脂、フェノール樹脂、またはシアネート樹脂が好ましい。なお、混合物は、さらに分散剤、着色剤、カップリング剤または離型剤を含んでいても良い。

配線層102aおよび102cは電気伝導性を有する物質、例えば、銅箔や導電性樹脂組成物からなる。インアービア103a、103bおよび103cは、例えば熱硬化性の導電物質からなる。熱硬化性の導電性物質としては、例えば金属粒子と熱硬化性樹脂とを混合した導電性樹脂組成物が用いられる。

部品内蔵基板150bも、基本的には、部品内蔵基板150aと同様の構成である。すなわち上面に配線層102bが形成され下面に配線層102dが形成された配線基板111bと、配線基板111b上に形成された絶縁層109で構成されている。

絶縁層109の内部には、半田105cおよび105dによって配線層102bに接続された電子部品104d、104eおよび104fが埋設されている。絶縁層109も、絶縁層101と同様に、無機フィラと熱硬化性樹脂とを含む混合物を主成分とする。また配線層102aおよび102bは電気伝導性を有する物質からなり、例えば、銅箔や導電性樹脂組成物で形成されている。

なお、図示しないが、配線基板111aの内部には、配線層102aおよび102cを接続する配線が形成されている。同様に、配線基板111bの内部にも、配線層102bおよび102dを接続する配線が形成されている。

積層された2つの部品内蔵基板のうち下段の部品内蔵基板150aの構造は、図7に示した従来の電子部品内蔵モジュール500と異なる部分はない。従来の電子部品内蔵モジュール500と異なるのは上段の部品内蔵基板150bの構造である。

前述したように、従来の電子部品内蔵モジュール500では、電子部品から出される熱をヒートシンク407に伝える手段として放熱シート406を用いている。これに対し、本実施の形態に係る電子部品内蔵モジュール100Aは、配線基板111b上に形成された絶縁層109を用いて、電子部品や配線層から出される熱をヒートシンク107に伝えている。

絶縁層109には無機フィラが大量に添加されているため、熱伝導性に優れている。また電子部品104c〜104eは絶縁層109に埋設されており、電子部品104c〜104eと絶縁層109との間にはほとんど隙間がない。すなわち、電子部品が絶縁層に接する面積が大きいことから、電子部品や配線層で発生した熱が伝導により絶縁層109中に効率よく発散され、ヒートシンク107に伝わる。

また配線層102bと絶縁層109との間もほとんど隙間がないことから、部品内蔵基板150aで発生し、配線を介して配線層102bに伝わった熱が絶縁層109中に効率よく発散され、ヒートシンク107に伝わる。

更に、絶縁層109のうち、大量に熱が発生する電子部品(例えば半導体パッケージ部品)104dと接する箇所にはサーマルビア110が形成されている。具体的には、絶縁層109の表面に形成された凹部に高い熱伝導性を備えた物質(例えば、アルミニウム合金粉とエポキシ樹脂の混合物)が充填されている。サーマルビア110の高い熱伝導性によって電子部品104dの熱が効率的にヒートシンク107に伝わる。

また後述するように、絶縁層101と絶縁層109を同質の材料で構成しているため、部品内蔵基板150aの絶縁層101を形成する際に、絶縁層109を同時に形成できる。従って、放熱シートに凹部を形成する工程や、放熱シールをモジュール上に載置する工程が不要となる。

次に、図2を参照して、電子部品内蔵モジュール100Aの製造方法について説明する。図2(a)〜(f)に、電子部品内蔵モジュール100Aの主要な製造工程を模式的に示す。

図2(a)に示すように、まず熱伝導特性を高めるために大量(例えば、80%wt)の無機フィラ(例えば、アルミナの粉末)と未硬化状態の熱硬化性樹脂(例えば、エポキシ樹脂)の混合物を成形して、高熱伝導特性を有するシート状の絶縁層101を準備する。この絶縁層101には所定の位置に貫通孔が形成され、その貫通孔に導電性ペースト(例えば、エポキシ樹脂と銅粉の混合物)が充填されてインナービア103a〜103cが形成されている。

更に図2(a)に示すように、絶縁層101と同一の混合物を成形して、高熱伝導特性を有するシート状の絶縁層109を準備する。絶縁層109の所定の位置に所定の深さの凹部が形成されており、その凹部に高熱伝導ペーストが充填されてサーマルビア110が形成される。

別途、図2(b)に示すように、電子部品104aおよび104bが配線層102a上に実装された多層の配線基板111aを準備しておく。また電子部品104c〜104eが配線層102b上に実装された別の多層の配線基板111bを準備しておく。それぞれの配線層と電子部品の電極は半田105a〜105eにより接続されている。

次に、図2(c)に示すように、配線基板111aの主面上の所定の位置に所定の向きで絶縁層101が載置され、更にその上に、所定の位置に所定の向きで配線基板111bと絶縁層109が順次載置される。しかる後、これらの配線基板および絶縁層を熱プレス板108aおよび108bで挟み込んで加圧および加熱処理が行われる。

図2(d)に示すように、加圧・過熱処理の際、熱プレス板108aおよび108bによって矢印方向に圧力が加えられ、電子部品104a〜104eは絶縁層101および109の各々に埋設される。その後、絶縁層101およびインナービア103a〜103cの熱硬化性樹脂、ならびに絶縁層109中の熱硬化性樹脂およびサーマルビア110中の熱硬化性樹脂が硬化して配線基板および絶縁層が一体化する。また一体化と同時に、インナービア103a〜103cは配線層102aおよび102dと接続される。

最後に、図2(e)に示すように、ヒートシンク107が最上部の所定の位置に所定の向きに載置され固定(例えば、ネジ止め)される。このようにして図2(f)に示すような放熱対策が施された電子部品内蔵モジュール100Aが得られる。

以上説明したように本実施の形態において、熱伝導特性の高い絶縁層109は、電子部品104c〜104eに、ほぼ隙間なく密着することができるので、接触面積が広く、ロスの少ない熱伝導を実現できる。また、従来必要であった放熱シートを加工する工程および放熱シートを固定するための工程が不要となる。

本実施の形態においては、絶縁層101と109に同一の混合物を用いることにより、絶縁層101と絶縁層109の形成を同時に行っている。両絶縁層の材質が同一であることから、加圧および加熱の条件を同一にできるため、製造工程における圧力や温度の制御が容易になる。ただし、絶縁層101と109に必ずしも同一の混合物を用いる必要はない。例えば、絶縁層109の熱伝導性を高めるため、絶縁層109に含まれるフィラの量を絶縁層109のそれよりも多くすることも可能である。すなわち、要求される熱伝導特性に応じて絶縁層に用いられる混合物の組成を調整すればよい。

(実施の形態2)

本実施の形態に係る電子部品内蔵モジュールは、構成的には、図1に示した電子部品内蔵モジュール100Aと変らない。本実施の形態が実施の形態1と異なる点は、電子部品内蔵モジュールを製造する工程において、図2(d)で説明した加圧および加熱工程と図2(e)で説明したヒートシンク107の載置および固定工程を同時に行う点である。

本実施の形態に係る電子部品内蔵モジュールは、構成的には、図1に示した電子部品内蔵モジュール100Aと変らない。本実施の形態が実施の形態1と異なる点は、電子部品内蔵モジュールを製造する工程において、図2(d)で説明した加圧および加熱工程と図2(e)で説明したヒートシンク107の載置および固定工程を同時に行う点である。

図3を参照して、本実施の形態に係る電子部品内蔵モジュール100の製造方法について説明する。図3(a)〜(e)に、本実施の形態に係る電子部品内蔵モジュール100Aの主な製造工程を模式的に示す。なお、図3において、図1および図2と実質的に同一の機能を有する構成要素には同一の符号を付している。

図3(a)及び(b)の工程は、図2(a)及び(b)の工程と同一であるため、説明を省略する。図3(c)に示す工程では、図2(c)に示す工程と同様にして、配線基板111a上に絶縁層101、配線基板111bおよび絶縁層109が、順次所定の向きで所定の位置に載置される。

図3(c)に示す工程では、さらに、その上にヒートシンク107が載置された後、熱プレス板108aおよび108bで、これらの配線基板および絶縁層が加圧、加熱処理により一体化される。図3(d)に示す加圧・過熱処理の工程を経て、図3(e)に示す放熱性の良好な電子部品内蔵モジュール100Aが得られる。

本実施の形態によれば、従来必要であったヒートシンクを取り付ける工程が不要となるため製造コストを削減できる。また実施の形態1と同様に、接触面積が広い、ロスの少ない熱伝導を実現できる。

(実施の形態3)

図4に本発明の実施の形態3に係る子部品内蔵モジュール100Bの構成を示す。本実施の形態に係る電子部品内蔵モジュール100Bは、図1に示した電子部品内蔵モジュール100Aと放熱構造が若干異なっている。具体的には、実施の形態1では絶縁層109とヒートシンク107は別体で構成されている。これに対し、本実施の形態の電子部品内蔵モジュール100Bは、絶縁層109とヒートシンク107が一体に構成されている。

図4に本発明の実施の形態3に係る子部品内蔵モジュール100Bの構成を示す。本実施の形態に係る電子部品内蔵モジュール100Bは、図1に示した電子部品内蔵モジュール100Aと放熱構造が若干異なっている。具体的には、実施の形態1では絶縁層109とヒートシンク107は別体で構成されている。これに対し、本実施の形態の電子部品内蔵モジュール100Bは、絶縁層109とヒートシンク107が一体に構成されている。

具体的には、図4に示すようにヒートシンクは設けられていない。図1に示す絶縁層109の代わりに、放熱面にヒートシンクの表面形状に似た形状の凹凸113が形成された絶縁層112が用いられる。サーマルビア114も絶縁層112と同様の凹凸形状に形成される。なお、図4において、図1および図2と実質的に同一の機能を有する構成要素には同一の符号を付している。

このように絶縁層112の放熱面を凹凸形状(図では鋸歯形状)に加工することによりヒートシンクを省略できる。結果として電子部品内蔵モジュールのコストを削減でき、また従来の製造工程で必要であったヒートシンクを絶縁層に固定する工程を削除できる。

次に、図5を参照して、図4に示した電子部品内蔵モジュール100Bの製造方法について説明する。図5(a)〜(d)に、本実施の形態に係る電子部品内蔵モジュール100Bの主要な製造工程を模式的に示す。

図5(a)及び(b)の工程は、図2(a)及び(b)の工程と同一であるため、説明を省略する。図5(c)の工程では、図2(c)の工程と同様にして、配線基板111a上に、絶縁層101、配線基板111bおよび絶縁層109が、順次、所定の向きで所定の位置に載置される。

加圧・加熱処理の際に使用する熱プレス板108aおよび108cのうち、絶縁層109を加圧、加熱する熱プレス板108cのプレス面には、ヒートシンクの表面形状に似る凹凸形状(例えば、鋸歯形状)が形成されている。このような形状の熱プレス板108cを用いることにより、絶縁層112の表面形状は、ヒートシンクに似た凹凸形状に成型される。

図7(d)に示す加圧・過熱処理の工程を経て、図7(e)に示すように、放熱対策を施した電子部品内蔵モジュール200Bが得られる。

本実施の形態によれば、実施の形態1と同様に接触面積が広い、ロスの少ない熱伝導を実現できる。また、ヒートシンクを用いなくても良いので、ヒートシンクを取り付ける工程が削減できる上、さらに部品を削減できる。

以上、図面を参照して本発明を実施するための最適な形態について説明したが、本発明の適用範囲はこれに限定されるものではなく、当業者であれば想到しうる形態についても本発明の範囲に属することは明らかである。

本発明は、低コストで高性能、高品質な電子部品内蔵モジュールが要求されるモバイル機器等の分野において広く利用できる。

100A、100B 電子部品内蔵モジュール

101、109 絶縁層

102a〜102d 配線層

103a〜103c インナービア

104a〜104e 電子部品

105a〜105e 半田

107 ヒートシンク

108a〜108c 熱プレス板

111a、111b 配線基板

150a、150b 部品内蔵基板

101、109 絶縁層

102a〜102d 配線層

103a〜103c インナービア

104a〜104e 電子部品

105a〜105e 半田

107 ヒートシンク

108a〜108c 熱プレス板

111a、111b 配線基板

150a、150b 部品内蔵基板

Claims (12)

- 電子部品を内蔵した第1の部品内蔵基板上に、電子部品を内蔵した第2の部品内蔵基板が積層され、更に当該第2の部品内蔵基板上に放熱器が取り付けられた電子部品内蔵モジュールであって、

前記第1の部品内蔵基板は、

一主面に電子部品が実装された第1の配線層と、

無機フィラと熱硬化性樹脂とを含む混合物を主成分とし、前記第1の配線層上に実装された前記電子部品が埋設され、かつ電気接続用のインナービアが形成された第1の絶縁層とを備え、

前記第2の部品内蔵基板は、

一主面に電子部品が実装された第2の配線層と、

無機フィラと熱硬化性樹脂とを含む混合物を主成分とし、前記第2の配線層上に実装された前記電子部品が埋設された第2の絶縁層とを備える電子部品内蔵モジュール。 - 前記第2の絶縁層のうち前記放熱器と接する面に凹部が形成され、当該凹部には前記第2の絶縁層の主成分である混合物より熱伝導性の高い物質が充填されている請求項1に記載の電子部品内蔵モジュール。

- 前記第1の絶縁層の混合物と前記第2の絶縁層の混合物は同一の組成である請求項1に記載の電子部品内蔵モジュール。

- 前記第1および第2の配線層は、それぞれ多層の配線基板上に形成されている請求項1に記載の電子部品内蔵モジュール。

- 前記第2の絶縁層と前記放熱器が一体に構成される請求項1に記載の電子部品内蔵モジュール。

- 前記剤2の絶縁層と前記放熱器は同一の物質で形成されている請求項5に記載の電子部品内蔵モジュール。

- 一主面に電子部品が実装された第1および第2の配線層を用意する工程と、

無機フィラと未硬化状態の熱硬化性樹脂とを含む混合物をシート状に成形して第1の絶縁層を用意すると共に、前記第1の絶縁層に貫通孔を形成し、当該貫通孔に未硬化状態の熱硬化性の導電性物質を充填する工程と、

無機フィラと未硬化状態の熱硬化性樹脂とを含む混合物をシート状に成形して第2の絶縁層を用意する工程と、

前記第1の配線層、前記第1の絶縁層、前記第2の配線層および前記第2の絶縁層を、それぞれが位置合わせされた状態で、かつ前記第1および第2の配線層の電子部品が実装された主面を上にして積層する工程と、

積層された前記第1の配線層、前記第1の絶縁層、前記第2の配線層および前記第2の絶縁層を、一対の熱プレス板で挟んだ状態で加圧および加熱して一体化する工程と

を含む電子部品内臓モジュールの製造方法。 - 一体化された前記第1の配線層、前記第1の絶縁層、前記第2の配線層および前記第2の絶縁層の上に放熱器を載置し固定する工程を更に含む請求項7に記載の電子部品内蔵モジュールの製造方法。

- 前記第2の絶縁層の一主面に凹部を形成し、当該凹部に前記第2の絶縁層の主成分である混合物より熱伝導性の高い物質を充填する工程を更に含む請求項7に記載の電子部品内蔵モジュールの製造方法。

- 前記一対の熱プレス板で挟んだ状態で加圧および加熱して一体化する工程において、前記第2の絶縁層の上に更に放熱器を積層し、その状態で前記一対の熱プレス板により加圧および加熱処理を行う請求項7に記載の電子部品内蔵モジュールの製造方法。

- 前記一対の熱プレス板のうち、前記第2の絶縁層と接する熱プレス板としてプレス面に凸凹が形成されたプレス板を用いる請求項7に記載の電子部品内蔵モジュールの製造方法。

- 前記第1および第2の配線層は、それぞれ多層の配線基板上に形成されている請求項7に記載の電子部品内蔵モジュールの製造方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007151147A JP2008305937A (ja) | 2007-06-07 | 2007-06-07 | 電子部品内蔵モジュールおよびその製造方法 |

| US12/131,439 US20080304237A1 (en) | 2007-06-07 | 2008-06-02 | Electronic component built-in module and method for manufacturing the same |

| CNA2008101082893A CN101321437A (zh) | 2007-06-07 | 2008-06-05 | 电子部件内置组件及其制造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007151147A JP2008305937A (ja) | 2007-06-07 | 2007-06-07 | 電子部品内蔵モジュールおよびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008305937A true JP2008305937A (ja) | 2008-12-18 |

| JP2008305937A5 JP2008305937A5 (ja) | 2010-05-13 |

Family

ID=40095688

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007151147A Withdrawn JP2008305937A (ja) | 2007-06-07 | 2007-06-07 | 電子部品内蔵モジュールおよびその製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US20080304237A1 (ja) |

| JP (1) | JP2008305937A (ja) |

| CN (1) | CN101321437A (ja) |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2013080790A1 (ja) | 2011-11-30 | 2013-06-06 | 株式会社フジクラ | 部品内蔵基板及びその製造方法並びに部品内蔵基板実装体 |

| US10952310B2 (en) | 2016-11-16 | 2021-03-16 | Murata Manufacturing Co., Ltd. | High-frequency module |

| WO2021140975A1 (ja) | 2020-01-10 | 2021-07-15 | 住友電気工業株式会社 | 高周波増幅器 |

| WO2022225314A1 (ko) * | 2021-04-21 | 2022-10-27 | 엘지이노텍 주식회사 | Sip 모듈 |

| WO2023090809A1 (ko) * | 2021-11-18 | 2023-05-25 | 엘지이노텍 주식회사 | Sip 모듈 |

| US11916519B2 (en) | 2020-04-14 | 2024-02-27 | Sumitomo Electric Industries, Ltd. | High frequency amplifier |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102804430B (zh) * | 2010-01-19 | 2015-11-25 | Lg伊诺特有限公司 | 封装结构及其制造方法 |

| KR20110085481A (ko) * | 2010-01-20 | 2011-07-27 | 삼성전자주식회사 | 적층 반도체 패키지 |

| TW201139641A (en) * | 2010-01-29 | 2011-11-16 | Nitto Denko Corp | Heat dissipation structure |

| JP4948613B2 (ja) * | 2010-02-25 | 2012-06-06 | 三菱電機株式会社 | 樹脂封止形電子制御装置、及びその製造方法 |

| CN102786772A (zh) * | 2011-05-20 | 2012-11-21 | 吴江华诚复合材料科技有限公司 | 一种半导体封包用环氧树脂组成物 |

| WO2014007129A1 (ja) * | 2012-07-05 | 2014-01-09 | 株式会社村田製作所 | 部品内蔵基板 |

| JP2014175485A (ja) * | 2013-03-08 | 2014-09-22 | Ibiden Co Ltd | 配線板及びその製造方法 |

| AT515069B1 (de) | 2013-11-07 | 2019-10-15 | At & S Austria Tech & Systemtechnik Ag | Leiterplattenstruktur |

| JP6312527B2 (ja) * | 2014-05-23 | 2018-04-18 | 新日本無線株式会社 | 放熱板を備えた電子部品の実装構造 |

| FR3036918B1 (fr) * | 2015-05-29 | 2018-08-10 | Thales | Carte electronique et procede de fabrication associe |

| US11452198B2 (en) * | 2019-07-25 | 2022-09-20 | Borgwarner, Inc. | Thermally insulated printed circuit board |

| KR20210076584A (ko) * | 2019-12-16 | 2021-06-24 | 삼성전기주식회사 | 전자부품 내장기판 |

| CN116897423A (zh) * | 2021-04-20 | 2023-10-17 | 华为技术有限公司 | 一种半导体封装 |

| CN113840449A (zh) * | 2021-09-06 | 2021-12-24 | 华为技术有限公司 | 一种基板和电子设备 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5541449A (en) * | 1994-03-11 | 1996-07-30 | The Panda Project | Semiconductor chip carrier affording a high-density external interface |

| US6320257B1 (en) * | 1994-09-27 | 2001-11-20 | Foster-Miller, Inc. | Chip packaging technique |

| US5896038A (en) * | 1996-11-08 | 1999-04-20 | W. L. Gore & Associates, Inc. | Method of wafer level burn-in |

| TWI255001B (en) * | 2001-12-13 | 2006-05-11 | Matsushita Electric Ind Co Ltd | Metal wiring substrate, semiconductor device and the manufacturing method thereof |

| TW200302685A (en) * | 2002-01-23 | 2003-08-01 | Matsushita Electric Ind Co Ltd | Circuit component built-in module and method of manufacturing the same |

| US20070035013A1 (en) * | 2003-05-09 | 2007-02-15 | Hiroyuki Handa | Module with built-in circuit elements |

| WO2005071745A1 (ja) * | 2004-01-27 | 2005-08-04 | Murata Manufacturing Co., Ltd. | 積層型電子部品およびその製造方法 |

| JP2006295119A (ja) * | 2005-03-17 | 2006-10-26 | Matsushita Electric Ind Co Ltd | 積層型半導体装置 |

| US20080042302A1 (en) * | 2006-08-16 | 2008-02-21 | Crispell Robert B | Plastic overmolded packages with molded lid attachments |

-

2007

- 2007-06-07 JP JP2007151147A patent/JP2008305937A/ja not_active Withdrawn

-

2008

- 2008-06-02 US US12/131,439 patent/US20080304237A1/en not_active Abandoned

- 2008-06-05 CN CNA2008101082893A patent/CN101321437A/zh active Pending

Cited By (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2013080790A1 (ja) | 2011-11-30 | 2013-06-06 | 株式会社フジクラ | 部品内蔵基板及びその製造方法並びに部品内蔵基板実装体 |

| US9591767B2 (en) | 2011-11-30 | 2017-03-07 | Fujikura Ltd. | Component built-in board and method of manufacturing the same, and component built-in board mounting body |

| US10952310B2 (en) | 2016-11-16 | 2021-03-16 | Murata Manufacturing Co., Ltd. | High-frequency module |

| WO2021140975A1 (ja) | 2020-01-10 | 2021-07-15 | 住友電気工業株式会社 | 高周波増幅器 |

| KR20220124145A (ko) | 2020-01-10 | 2022-09-13 | 스미토모덴키고교가부시키가이샤 | 고주파 증폭기 |

| US11916519B2 (en) | 2020-04-14 | 2024-02-27 | Sumitomo Electric Industries, Ltd. | High frequency amplifier |

| WO2022225314A1 (ko) * | 2021-04-21 | 2022-10-27 | 엘지이노텍 주식회사 | Sip 모듈 |

| WO2023090809A1 (ko) * | 2021-11-18 | 2023-05-25 | 엘지이노텍 주식회사 | Sip 모듈 |

| WO2023090920A1 (ko) * | 2021-11-18 | 2023-05-25 | 엘지이노텍 주식회사 | Sip 모듈 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20080304237A1 (en) | 2008-12-11 |

| CN101321437A (zh) | 2008-12-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2008305937A (ja) | 電子部品内蔵モジュールおよびその製造方法 | |

| US10595413B2 (en) | Board having electronic element, method for manufacturing the same, and electronic element module including the same | |

| CN100463128C (zh) | 半导体芯片埋入基板的三维构装结构及其制作方法 | |

| JP5767338B2 (ja) | 電子デバイス、その製作方法、及び電子デバイスを備えているプリント基板 | |

| KR101065935B1 (ko) | 전자 부품 실장 장치 및 그 제조 방법 | |

| JP5093353B2 (ja) | 部品内蔵モジュールの製造方法及び部品内蔵モジュール | |

| US20060151206A1 (en) | Semiconductor device and manufacturing method therefor | |

| JP2006073651A (ja) | 半導体装置 | |

| JP2010080572A (ja) | 電子装置 | |

| WO2011121779A1 (ja) | マルチチップモジュール、プリント配線基板ユニット、マルチチップモジュールの製造方法およびプリント配線基板ユニットの製造方法 | |

| JP2008218980A (ja) | 電子素子パッケージ及びその製造方法 | |

| US9345125B2 (en) | Wiring substrate | |

| US11177189B2 (en) | Module including heat dissipation structure | |

| JP6639934B2 (ja) | 配線基板、半導体装置及び配線基板の製造方法 | |

| JP2011151048A (ja) | 電子部品の製造方法および電子部品 | |

| JP5411174B2 (ja) | 回路板およびその製造方法 | |

| JP2006294749A (ja) | 高放熱回路基板およびその製造方法 | |

| WO2017208309A1 (ja) | 電子モジュールおよび電子モジュールの製造方法 | |

| JP2007258635A (ja) | 部品内蔵基板の製造方法 | |

| JP2001077290A (ja) | 三次元電子部品用モジュール、三次元電子部品モジュールおよびそれらの製造方法 | |

| JP2006310806A (ja) | 放熱部材、電子部品搭載用基板、電子部品収納用パッケージおよび電子装置 | |

| JP2017085073A (ja) | プリント回路基板及びプリント回路基板の製造方法 | |

| JP2009117489A (ja) | 半導体素子パッケージ及び実装基板 | |

| JP2006135202A (ja) | 電子機器の放熱構造 | |

| US11191150B2 (en) | Electronic component module and method for manufacturing the same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20081107 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100325 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100325 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20101207 |