JP2008278453A - 撮像装置及び撮像システム - Google Patents

撮像装置及び撮像システム Download PDFInfo

- Publication number

- JP2008278453A JP2008278453A JP2007309334A JP2007309334A JP2008278453A JP 2008278453 A JP2008278453 A JP 2008278453A JP 2007309334 A JP2007309334 A JP 2007309334A JP 2007309334 A JP2007309334 A JP 2007309334A JP 2008278453 A JP2008278453 A JP 2008278453A

- Authority

- JP

- Japan

- Prior art keywords

- pixel

- pixels

- signal

- addition

- common

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 230000005484 gravity Effects 0.000 claims abstract description 8

- 238000003384 imaging method Methods 0.000 claims description 56

- 230000003287 optical effect Effects 0.000 claims description 3

- 238000012545 processing Methods 0.000 abstract description 17

- 239000011295 pitch Substances 0.000 abstract 1

- 238000000034 method Methods 0.000 description 16

- 238000010586 diagram Methods 0.000 description 13

- 238000012546 transfer Methods 0.000 description 13

- 239000003990 capacitor Substances 0.000 description 12

- 230000035945 sensitivity Effects 0.000 description 11

- 101000588067 Homo sapiens Metaxin-1 Proteins 0.000 description 6

- 102100031603 Metaxin-1 Human genes 0.000 description 6

- 238000006243 chemical reaction Methods 0.000 description 6

- 101000623878 Homo sapiens Metaxin-2 Proteins 0.000 description 4

- 101000623873 Homo sapiens Metaxin-3 Proteins 0.000 description 4

- 102100023138 Metaxin-2 Human genes 0.000 description 4

- 102100023139 Metaxin-3 Human genes 0.000 description 4

- 101000727837 Rattus norvegicus Reduced folate transporter Proteins 0.000 description 4

- PCTLYGKHPBZRCZ-UKLTVQOFSA-N maitotoxin-3 Chemical compound C[C@H]1CC[C@H]2O[C@@]3(C)C[C@H]4O[C@H]5C[C@H]6O[C@](O)(C[C@@H](O)CO)[C@@H](O)[C@@H](OS(O)(=O)=O)[C@@H]6O[C@@H]5C=C[C@@H]4O[C@@H]3CC[C@@H]2O[C@@H]2C[C@@H]3O[C@]4(C)CC(=C)C[C@](C)(O[C@H]4C[C@H]3O[C@@H]12)[C@@H](O)CC(=O)CC\C=C(/C)C=C PCTLYGKHPBZRCZ-UKLTVQOFSA-N 0.000 description 4

- 238000004891 communication Methods 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 239000000654 additive Substances 0.000 description 1

- 230000000996 additive effect Effects 0.000 description 1

- 230000003321 amplification Effects 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 238000003199 nucleic acid amplification method Methods 0.000 description 1

Images

Landscapes

- Transforming Light Signals Into Electric Signals (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Color Television Image Signal Generators (AREA)

Abstract

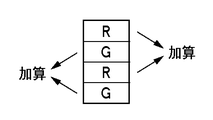

【解決手段】撮像装置は、行方向及び列方向に配列された複数の画素を含むグループが複数配列された画素部と、前記グループ内に配列された前記複数の画素が出力する画素信号のうち、同一色の画素信号を加算する加算部と、を備える。前記加算部は、前記同一色の画素に共通に接続された共通画素アンプMSF’を前記グループ毎に備える。また、前記加算部では、前記グループ内で加算される画素の空間的な重心が前記行方向及び前記列方向の少なくとも一方において等ピッチとなるように共通画素アンプMSF’のゲート部で前記同一色の画素の画素信号を加算する。

【選択図】図4

Description

Claims (7)

- 行方向及び列方向に配列された複数の画素を含むグループが複数配列された画素部と、

前記グループ内に配列された前記複数の画素が出力する画素信号のうち、同一色の画素信号を加算する加算部と、

を備え、

前記加算部は、前記同一色の画素に共通に接続された共通画素アンプを前記グループ毎に備え、前記グループ内で加算される画素の空間的な重心が前記行方向及び前記列方向の少なくとも一方において等ピッチとなるように前記共通画素アンプのゲート部で前記同一色の画素の画素信号を加算することを特徴とする撮像装置。 - 前記加算部は、前記複数の画素のうち、少なくとも1つの行に配列された複数の画素から出力される画素信号を加算しないことを特徴する請求項1に記載の撮像装置。

- 前記加算部は、前記複数の画素のうち、少なくとも1つの列に配列された複数の画素から出力される画素信号を加算しないことを特徴する請求項1又は請求項2記載の撮像装置。

- 前記加算部は、前記共通画素アンプのゲート部で加算された画素信号を複数の前記グループ間で更に加算することを特徴する請求項1乃至請求項3に記載の撮像装置。

- 複数の前記グループの少なくとも1つの一部の画素は、他のグループの一部の画素と共通していることを特徴とする請求項1乃至請求項4のいずれか1項に記載の撮像装置。

- 複数の前記グループの各々は、前記行方向及び前記列方向に2n+1個(nは1以上の整数)ずつ配列された複数の画素を含むことを特徴とする請求項1乃至請求項5のいずれか1項に記載の撮像装置。

- 請求項1乃至請求項6のいずれか1項に記載の撮像装置と、

前記撮像装置へ光を結像する光学系と、

前記撮像装置から出力される信号を記録する記録系と、

システム全体を制御するシステムコントロール回路と、

を備えることを特徴とする撮像システム。

Priority Applications (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007309334A JP2008278453A (ja) | 2007-04-03 | 2007-11-29 | 撮像装置及び撮像システム |

| US12/047,852 US8009211B2 (en) | 2007-04-03 | 2008-03-13 | Image sensing apparatus and image capturing system |

| CN201210074523.1A CN102629994B (zh) | 2007-04-03 | 2008-04-02 | 图像感测设备和图像捕获系统 |

| RU2008112755/09A RU2378791C2 (ru) | 2007-04-03 | 2008-04-02 | Устройство для восприятия изображений и система для захвата изображений |

| CN2008100900813A CN101282484B (zh) | 2007-04-03 | 2008-04-02 | 图像感测设备和图像捕获系统 |

| US13/177,660 US8462241B2 (en) | 2007-04-03 | 2011-07-07 | Image sensing apparatus and image capturing system |

| US13/889,394 US8754971B2 (en) | 2007-04-03 | 2013-05-08 | Image sensing apparatus and image capturing system |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007097630 | 2007-04-03 | ||

| JP2007309334A JP2008278453A (ja) | 2007-04-03 | 2007-11-29 | 撮像装置及び撮像システム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008278453A true JP2008278453A (ja) | 2008-11-13 |

| JP2008278453A5 JP2008278453A5 (ja) | 2011-01-20 |

Family

ID=40014719

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007309334A Pending JP2008278453A (ja) | 2007-04-03 | 2007-11-29 | 撮像装置及び撮像システム |

Country Status (3)

| Country | Link |

|---|---|

| JP (1) | JP2008278453A (ja) |

| CN (2) | CN102629994B (ja) |

| RU (1) | RU2378791C2 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011155395A (ja) * | 2010-01-26 | 2011-08-11 | Canon Inc | 撮像素子及び撮像装置 |

| WO2012114819A1 (ja) | 2011-02-24 | 2012-08-30 | ソニー株式会社 | 撮像装置、および撮像装置制御方法、並びにプログラム |

| JP2019049616A (ja) * | 2017-09-08 | 2019-03-28 | キヤノン株式会社 | 画像処理装置、撮像装置および画像処理装置の制御方法 |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5404194B2 (ja) * | 2009-06-05 | 2014-01-29 | キヤノン株式会社 | 固体撮像素子、撮像システム、および固体撮像素子の駆動方法 |

| JP6390429B2 (ja) * | 2012-12-25 | 2018-09-19 | ソニー株式会社 | 固体撮像素子およびその駆動方法、並びに電子機器 |

| CN105809153A (zh) * | 2016-04-18 | 2016-07-27 | 成都艾德沃传感技术有限公司 | 芯片电路及指纹采集系统 |

| WO2020252754A1 (zh) * | 2019-06-20 | 2020-12-24 | 深圳市汇顶科技股份有限公司 | 读出电路、图像传感器和电子设备 |

| CN110324548B (zh) * | 2019-06-27 | 2021-11-09 | Oppo广东移动通信有限公司 | 一种像素单元电路、信号处理方法及存储介质 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000341699A (ja) * | 1999-05-31 | 2000-12-08 | Canon Inc | カラー撮像装置及びそれを用いた撮像システム |

| JP2005086657A (ja) * | 2003-09-10 | 2005-03-31 | Canon Inc | 撮像装置 |

| JP2005092085A (ja) * | 2003-09-19 | 2005-04-07 | Canon Inc | 焦点検出及び調節方法並びに焦点検出及び調節装置 |

| JP2005210701A (ja) * | 2003-12-25 | 2005-08-04 | Canon Inc | 撮像装置 |

| JP2005244435A (ja) * | 2004-02-25 | 2005-09-08 | Sharp Corp | 増幅型固体撮像装置 |

| JP2006041912A (ja) * | 2004-07-27 | 2006-02-09 | Canon Inc | カラー撮像装置及びカラー撮像システム |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3991543B2 (ja) * | 2000-01-11 | 2007-10-17 | 株式会社日立製作所 | 撮像装置 |

| JP2005045435A (ja) * | 2003-07-25 | 2005-02-17 | Minolta Co Ltd | 撮像素子の駆動方法および撮像装置 |

-

2007

- 2007-11-29 JP JP2007309334A patent/JP2008278453A/ja active Pending

-

2008

- 2008-04-02 RU RU2008112755/09A patent/RU2378791C2/ru not_active IP Right Cessation

- 2008-04-02 CN CN201210074523.1A patent/CN102629994B/zh not_active Expired - Fee Related

- 2008-04-02 CN CN2008100900813A patent/CN101282484B/zh not_active Expired - Fee Related

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000341699A (ja) * | 1999-05-31 | 2000-12-08 | Canon Inc | カラー撮像装置及びそれを用いた撮像システム |

| JP2005086657A (ja) * | 2003-09-10 | 2005-03-31 | Canon Inc | 撮像装置 |

| JP2005092085A (ja) * | 2003-09-19 | 2005-04-07 | Canon Inc | 焦点検出及び調節方法並びに焦点検出及び調節装置 |

| JP2005210701A (ja) * | 2003-12-25 | 2005-08-04 | Canon Inc | 撮像装置 |

| JP2005244435A (ja) * | 2004-02-25 | 2005-09-08 | Sharp Corp | 増幅型固体撮像装置 |

| JP2006041912A (ja) * | 2004-07-27 | 2006-02-09 | Canon Inc | カラー撮像装置及びカラー撮像システム |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011155395A (ja) * | 2010-01-26 | 2011-08-11 | Canon Inc | 撮像素子及び撮像装置 |

| WO2012114819A1 (ja) | 2011-02-24 | 2012-08-30 | ソニー株式会社 | 撮像装置、および撮像装置制御方法、並びにプログラム |

| US8786731B2 (en) | 2011-02-24 | 2014-07-22 | Sony Corporation | Image pickup apparatus and image pickup apparatus control method that generates an image with transformed number of pixels |

| US9001233B2 (en) | 2011-02-24 | 2015-04-07 | Sony Corporation | Image pickup apparatus and image pickup apparatus control method that generates an image with transformed number of pixels |

| JP2019049616A (ja) * | 2017-09-08 | 2019-03-28 | キヤノン株式会社 | 画像処理装置、撮像装置および画像処理装置の制御方法 |

| JP7039221B2 (ja) | 2017-09-08 | 2022-03-22 | キヤノン株式会社 | 画像処理装置、撮像装置および画像処理装置の制御方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN102629994B (zh) | 2015-10-28 |

| RU2378791C2 (ru) | 2010-01-10 |

| CN102629994A (zh) | 2012-08-08 |

| RU2008112755A (ru) | 2009-10-10 |

| CN101282484B (zh) | 2012-05-30 |

| CN101282484A (zh) | 2008-10-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8077232B2 (en) | Imaging device for adding signals including same color component | |

| JP4416753B2 (ja) | 固体撮像装置 | |

| US8462241B2 (en) | Image sensing apparatus and image capturing system | |

| JP3501694B2 (ja) | 撮像装置及びそれを用いた撮像システム | |

| JP2008278453A (ja) | 撮像装置及び撮像システム | |

| US20100245628A1 (en) | Imaging apparatus and imaging system | |

| JP2009044593A (ja) | 撮像装置及び固体撮像素子の駆動方法 | |

| US20050146617A1 (en) | Imaging apparatus for processing noise signal and photoelectric conversion signal | |

| WO2012014553A1 (ja) | 撮像装置及び撮像方法 | |

| JP4677228B2 (ja) | 撮像装置 | |

| WO2013100093A1 (ja) | 撮像装置、撮像装置の制御方法、及び制御プログラム | |

| US9838591B2 (en) | Imaging apparatus and imaging system for generating a signal for focus detection | |

| JP5124549B2 (ja) | 固体撮像素子の動画像信号読出方法及び撮像装置 | |

| JP4613137B2 (ja) | 固体撮像素子 | |

| JP5511205B2 (ja) | 撮像装置及び撮像方法 | |

| JP5089674B2 (ja) | 撮像装置 | |

| JP4667268B2 (ja) | 固体撮像素子 | |

| JP2006041913A (ja) | カラー撮像装置及びカラー撮像システム | |

| JP2015173387A (ja) | 撮像素子、その駆動方法、およびプログラム | |

| JP2010016450A (ja) | 撮像装置 | |

| JP2006041912A (ja) | カラー撮像装置及びカラー撮像システム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20101129 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101201 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120420 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120518 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120717 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130325 |