JP2008016024A - キャッシュされたデータのダイナミック適応フラッシング - Google Patents

キャッシュされたデータのダイナミック適応フラッシング Download PDFInfo

- Publication number

- JP2008016024A JP2008016024A JP2007172478A JP2007172478A JP2008016024A JP 2008016024 A JP2008016024 A JP 2008016024A JP 2007172478 A JP2007172478 A JP 2007172478A JP 2007172478 A JP2007172478 A JP 2007172478A JP 2008016024 A JP2008016024 A JP 2008016024A

- Authority

- JP

- Japan

- Prior art keywords

- write

- data

- back data

- cache memory

- storage array

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0804—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches with main memory updating

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0866—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches for peripheral storage systems, e.g. disk cache

- G06F12/0868—Data transfer between cache memory and other subsystems, e.g. storage devices or host systems

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/26—Using a specific storage system architecture

- G06F2212/261—Storage comprising a plurality of storage devices

- G06F2212/262—Storage comprising a plurality of storage devices configured as RAID

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/50—Control mechanisms for virtual memory, cache or TLB

- G06F2212/502—Control mechanisms for virtual memory, cache or TLB using adaptive policy

Abstract

【解決手段】ライトバックデータのセットが記憶アレイの異なる場所にわたってデータの実質的に均一な分布を維持する目的でキャッシュメモリ内に整列して蓄積される。その後、データの整列されたセットは実質的にライトバックデータの付加セットがホストによりキャッシュメモリへ提供されるレートでキャッシュメモリから記憶アレイへ転送される。好ましくは、各ライトバックデータは複数の隣接データブロックを含み、好ましくは記憶アレイに関してデータの選択された近接範囲内の別個のアクセスコマンドの操作と共に記憶装置に書き込まれる(フラッシュされる)。好ましくは、アレイ内のライトバックデータの各セットに対してストライプデータ記述子(SDD)が維持される。

【選択図】図8

Description

102 ベースデッキ

104 スピンドルモータ

106 回転媒体

108 アクチュエータ

110 リード/ライト・トランスデューサ

112 ボイスコイルモータ

114 フレックス回路アセンブリ

116 印刷回路板

120 ネットワーク・システム

122 記録アレイ

124,126 冗長コントローラ

128 サーバ

130 ファブリック

132,134,136 パーソナルコンピュータ

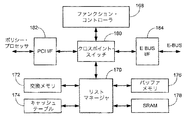

140 アレイコントローラ構成

142,144 インテリジェント記憶プロセッサ

146 中間バス

148,150 ファイバチャネル・サーバリンク

152,154 ファイバチャネル記憶リンク

156,158 ポリシー・プロセッサ

160,162 PCIバス

164,166 アクセスメモリ・モジュール

168 ファンクション・コントローラ

170 リストマネージャ

172 交換メモリブロック

174 キャッシュテーブル・ブロック

176 バッファメモリ・ブロック

178 SRAM

180 クロスポイントスイッチ・モジュール

182 PCIインターフェイス・モジュール

184 E−BUS IFモジュール

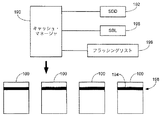

190 キャッシュ・マネージャ

192 ストライプ・データ記述子

194,198 RAIDストライプ

196 SBL

199 フラッシングリスト

200 アレイ

202,204 セル

Claims (19)

- 記憶アレイの場所に関して記憶アレイ内のライトバックデータのセットのアレイを形成するステップと、実質的にライトバックデータの付加セットがホストによりキャッシュメモリへ提供されるレートでライトバックデータの前記セットをキャッシュメモリから記憶アレイへ転送するステップと、を含む方法。

- 請求項1に記載の方法であって、ライトバックデータの各セットは複数の隣接データブロックを含む方法。

- 請求項1に記載の方法であって、転送ステップは記憶アレイのトランスデューサを記録媒体に隣接する選択された場所へ移動させて選択されたアクセスコマンドをサービスするステップと、選択されたアクセスコマンドの選択された場所とライトバックデータの選択されたセットに対する関連場所との近接に関してライトバックデータの選択されたセットをキャッシュメモリから媒体へ転送するステップと、を含む方法。

- 請求項3に記載の方法であって、前記近接はトランスデューサの選択されたシーク長を含む方法。

- 請求項1に記載の方法であって、さらに、アレイ内のライトバックデータの各セットに対してストライプデータ記述子(SDD)を与えるステップを含み、SDDはライトバックデータを記憶アレイへフラッシングするための準備完了として識別する値を含む方法。

- 請求項1に記載の方法であって、キャッシュメモリはライトバックデータのmセットを格納し、蓄積ステップは記憶アレイへのフラッシングに備えてアレイの異なる非隣接場所に関連する前記ライトバックデータのnセットを配列するステップを含み、nはmよりも小さい方法。

- 請求項1に記載の方法であって、さらに、ライトバックデータの前記付加セットがキャッシュメモリへ移されるレートを監視するステップを含み、それに関連して転送ステップを実施して前記キャッシュメモリ内に前記ライトバックデータの実質的に均一な分布を維持する方法。

- 記憶アレイの関連する場所へ転送するのに利用できるライトバックデータのセットを格納するキャッシュメモリと、ライトバックデータの前記セットをキャッシュメモリ内に配列して実質的に均一な分布を記憶アレイを横切って提供し、かつ実質的にライトバックデータの付加セットがホストによりキャッシュメモリへ提供されるレートでライトバックデータの前記セットをキャッシュメモリから記憶アレイへ転送するように構成されたプロセッサと、を含む装置。

- 請求項8に記載の装置であって、プロセッサはライトバックデータのセットを選択的にフラッシングリストへ移すキャッシュ・マネージャを含む装置。

- 請求項8に記載の装置であって、記憶アレイは記録媒体に隣接する選択された場所へ移されて選択されたアクセスコマンドをサービスするように構成されたトランスデューサを含み、プロセッサは選択されたアクセスコマンドの選択された場所とライトバックデータの選択されたセットに対する関連場所との間の近接に関してライトバックデータの選択されたセットをキャッシュメモリから媒体へ転送する装置。

- 請求項10に記載の装置であって、前記近接はトランスデューサの選択されたシーク長を含む装置。

- 請求項8に記載の装置であって、プロセッサはアレイ内のライトバックデータの各セットに対するストライプデータ記述子(SDD)を発生し、SDDはライトバックデータを記憶アレイへのフラッシング準備完了として識別する値を含む装置。

- 請求項8に記載の装置であって、キャッシュメモリはライトバックデータのmセットを格納し、プロセッサは前記ライトバックデータのnセットを記憶アレイフラッシングするために配置し、nはmよりも小さい装置。

- 請求項8に記載の装置であって、プロセッサはさらにライトバックデータの前記付加セットがキャッシュメモリへ移されるレートを監視し、それに関して前記データを転送してキャッシュメモリ内に前記ライトバックデータの実質的に均一な分布を維持する装置。

- 記憶アレイの関連する場所へ転送するのに利用できるライトバックデータの複数のセットを配列するキャッシュメモリと、実質的にライトバックデータの付加セットがホストによりキャッシュメモリへ提供されるレートでライトバックデータの前記セットを前記アレイから記憶アレイへ転送する第1の手段と、を含む装置。

- 請求項15に記載の装置であって、第1の手段はキャッシュ・マネージャを含む装置。

- 請求項15に記載の装置であって、記憶アレイは記録媒体に隣接する選択された場所へ移されて選択されたアクセスコマンドをサービスするように構成されたトランスデューサを含み、第1の手段は選択されたアクセスコマンドの選択された場所とライトバックデータの選択されたセットに対する関連場所との間の近接に関してライトバックデータの選択されたセットをキャッシュメモリから媒体へ転送する装置。

- 請求項17に記載の装置であって、前記近接はトランスデューサの選択されたシーク長を含む装置。

- 請求項15に記載の装置であって、第1の手段はさらにライトバックデータの前記付加セットがキャッシュメモリへ移されるレートを監視し、前記データを転送してプール内にライトバックデータの実質的に均一な分布を維持する装置。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/480,128 US8234457B2 (en) | 2006-06-30 | 2006-06-30 | Dynamic adaptive flushing of cached data |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008016024A true JP2008016024A (ja) | 2008-01-24 |

| JP2008016024A5 JP2008016024A5 (ja) | 2010-08-05 |

Family

ID=38878227

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007172478A Pending JP2008016024A (ja) | 2006-06-30 | 2007-06-29 | キャッシュされたデータのダイナミック適応フラッシング |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8234457B2 (ja) |

| JP (1) | JP2008016024A (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5158576B2 (ja) * | 2007-06-05 | 2013-03-06 | 日本電気株式会社 | 入出力制御システム、入出力制御方法、及び、入出力制御プログラム |

| US8843691B2 (en) * | 2008-06-25 | 2014-09-23 | Stec, Inc. | Prioritized erasure of data blocks in a flash storage device |

| US8924387B2 (en) * | 2009-09-29 | 2014-12-30 | Cleversafe, Inc. | Social networking utilizing a dispersed storage network |

| US9081686B2 (en) * | 2012-11-19 | 2015-07-14 | Vmware, Inc. | Coordinated hypervisor staging of I/O data for storage devices on external cache devices |

| EP2765528B1 (de) | 2013-02-11 | 2018-11-14 | dSPACE digital signal processing and control engineering GmbH | Wahlfreier Zugriff auf Signalwerte eines FPGA zur Laufzeit |

| WO2014122320A2 (de) * | 2013-02-11 | 2014-08-14 | Dspace Digital Signal Processing And Control Engineering Gmbh | Verändern eines signalwerts eines fpga zur laufzeit |

| CN110058786B (zh) * | 2018-01-18 | 2022-12-02 | 伊姆西Ip控股有限责任公司 | 用于控制存储系统中的写请求的方法、装置和计算机程序产品 |

Citations (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6391761A (ja) * | 1986-10-06 | 1988-04-22 | Alps Electric Co Ltd | キヤツシユメモリ制御方法 |

| JPH05100954A (ja) * | 1991-10-09 | 1993-04-23 | Hokkaido Nippon Denki Software Kk | キヤツシユバツフア処理制御方式 |

| JPH06124596A (ja) * | 1991-11-28 | 1994-05-06 | Hitachi Ltd | フラッシュメモリを使用した記憶装置 |

| JPH0855072A (ja) * | 1994-08-12 | 1996-02-27 | Matsushita Electric Ind Co Ltd | ネットワークシステムとデータ処理システムとデータ蓄積方法 |

| JPH10228417A (ja) * | 1996-11-15 | 1998-08-25 | Hyundai Electron America Inc | データ処理システムにおけるメモリリクエスト再順序付け法 |

| JPH11265315A (ja) * | 1997-10-31 | 1999-09-28 | Hewlett Packard Co <Hp> | 様々なdramバンクサイズと複数のインターリービング機構とをサポートする高速でコンパクトなアドレスビット経路指定機構 |

| JPH11328029A (ja) * | 1998-05-18 | 1999-11-30 | Olympus Optical Co Ltd | 情報記録再生装置 |

| JP2003318947A (ja) * | 2002-04-23 | 2003-11-07 | Mitsubishi Electric Corp | 多層メモリ使用交換装置 |

| JP2004213470A (ja) * | 2003-01-07 | 2004-07-29 | Nec Corp | ディスクアレイ装置及びディスクアレイ装置におけるデータ書き込み方法 |

| US20050071550A1 (en) * | 2003-09-29 | 2005-03-31 | International Business Machines Corporation (Ibm) | Increasing through-put of a storage controller by autonomically adjusting host delay |

| US6928518B2 (en) * | 2001-11-01 | 2005-08-09 | Sun Microsystems, Inc. | Disk drive employing adaptive flushing of a write cache |

| US20050182906A1 (en) * | 2004-02-18 | 2005-08-18 | Paresh Chatterjee | Systems and methods for cache synchronization between redundant storage controllers |

| US20060248308A1 (en) * | 2005-04-27 | 2006-11-02 | Dot Hill Systems Corp. | Multiple mode controller method and apparatus |

Family Cites Families (52)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US1485235A (en) * | 1923-09-14 | 1924-02-26 | Mauss Wilhelm | Centrifugal separator and the like |

| BE366538A (ja) * | 1929-01-04 | |||

| US2291117A (en) * | 1939-12-29 | 1942-07-28 | Laval Separator Co De | Centrifugal separator |

| US2688437A (en) * | 1947-12-04 | 1954-09-07 | Saint Gobain | Centrifugal separator |

| US3369742A (en) * | 1965-11-30 | 1968-02-20 | Carl W. Weiland | Discharge valve for centrifuge |

| FR1568746A (ja) * | 1967-06-21 | 1969-05-30 | ||

| CH514358A (fr) * | 1969-08-08 | 1971-10-31 | Termomeccanica Italiana Spa | Dispositif de séparation centrifuge des deux constituants à densité différente d'une émulsion |

| CS153120B1 (ja) * | 1971-01-18 | 1974-02-25 | ||

| US3791575A (en) * | 1971-08-30 | 1974-02-12 | Garrett Corp | Centrifugal separator discharge control system |

| US3797736A (en) * | 1972-04-07 | 1974-03-19 | Westfalia Separator Ag | Method and apparatus for controlling the concentration factor of a discharge |

| FR2180589B1 (ja) * | 1972-04-21 | 1975-03-21 | Loison Robert | |

| US3814307A (en) * | 1973-01-12 | 1974-06-04 | Standard Oil Co | Centrifugal clarifier |

| US3810347A (en) * | 1973-01-16 | 1974-05-14 | Signal Oil & Gas Co | Centrifugal separator for three phase mixture |

| FR2268565B2 (ja) * | 1974-04-25 | 1976-10-15 | Loison Robert | |

| US3930606A (en) * | 1974-05-20 | 1976-01-06 | Rca Corporation | Method and apparatus for securing wires to connector terminals |

| CH584150A5 (ja) * | 1974-09-02 | 1977-01-31 | Escher Wyss Ag | |

| DE2501924C3 (de) * | 1975-01-18 | 1981-03-26 | Westfalia Separator Ag, 59302 Oelde | Vollmantelzentrifuge |

| US4010891A (en) * | 1976-01-08 | 1977-03-08 | Burmah Oil & Gas Company | Vapor removal apparatus for oil/water separator |

| CS188429B1 (en) * | 1976-02-12 | 1979-03-30 | Jan Putterlik | Method of the automatic control of the discharging of the concentrated fraction from from the centrifuge rotor and device for executing the same |

| FR2532198B1 (fr) * | 1982-08-27 | 1985-06-21 | Bertin & Cie | Centrifugeuse a recuperation d'energie |

| JP2834189B2 (ja) | 1989-07-05 | 1998-12-09 | 株式会社日立製作所 | 入出力制御方法 |

| JP3586887B2 (ja) | 1994-06-10 | 2004-11-10 | 松下電器産業株式会社 | 情報記録再生装置およびデータキャッシュ方法 |

| US5829018A (en) | 1994-10-25 | 1998-10-27 | International Business Machines Corporation | Apparatus and method for writing data from a cache to a storage device |

| US5581729A (en) * | 1995-03-31 | 1996-12-03 | Sun Microsystems, Inc. | Parallelized coherent read and writeback transaction processing system for use in a packet switched cache coherent multiprocessor system |

| US6189080B1 (en) * | 1996-09-20 | 2001-02-13 | Emc Corporation | Minimum read rate throughput in a disk cache system |

| US5926834A (en) * | 1997-05-29 | 1999-07-20 | International Business Machines Corporation | Virtual data storage system with an overrun-resistant cache using an adaptive throttle based upon the amount of cache free space |

| US5908376A (en) * | 1997-09-11 | 1999-06-01 | Costner Industries Nevada, Inc. | Self-cleaning rotor for a centrifugal separator |

| US6484234B1 (en) | 1998-06-30 | 2002-11-19 | Emc Corporation | Method and apparatus for efficiently destaging data from a cache to two or more non-contiguous storage locations |

| US6312610B1 (en) * | 1998-07-13 | 2001-11-06 | Phase Inc. | Density screening outer wall transport method for fluid separation devices |

| US6057789A (en) * | 1998-10-29 | 2000-05-02 | Neomagic Corp. | Re-synchronization of independently-clocked audio streams by dynamically switching among 3 ratios for sampling-rate-conversion |

| US6719681B2 (en) * | 1999-08-06 | 2004-04-13 | Econova, Inc. | Methods for centrifugally separating mixed components of a fluid stream |

| US6671766B1 (en) | 2000-01-07 | 2003-12-30 | Storage Technology Corporation | Method and system for implementing memory efficient track aging |

| US6738865B1 (en) | 2000-06-09 | 2004-05-18 | International Business Machines Corporation | Method, system, and program for demoting data from cache based on least recently accessed and least frequently accessed data |

| US6552923B2 (en) * | 2000-06-13 | 2003-04-22 | Texas Instruments Incorporated | SRAM with write-back on read |

| US6658533B1 (en) | 2000-09-21 | 2003-12-02 | Intel Corporation | Method and apparatus for write cache flush and fill mechanisms |

| US7028297B2 (en) | 2000-11-17 | 2006-04-11 | Aristos Logic Corporation | System and method of scalable transaction processing |

| US6618793B2 (en) | 2000-12-18 | 2003-09-09 | Redback Networks, Inc. | Free memory manager scheme and cache |

| DE10114598A1 (de) * | 2001-03-23 | 2002-10-02 | Aventis Pharma Gmbh | CIP-gerechte Ausführung einer Horizontalzentrifuge mit Vollmanteltrommel |

| US6629211B2 (en) | 2001-04-20 | 2003-09-30 | International Business Machines Corporation | Method and system for improving raid controller performance through adaptive write back/write through caching |

| US6789163B2 (en) | 2001-09-17 | 2004-09-07 | Seagate Technology Llc | Optimizing data transfer performance through partial write command purging in a disc drive |

| US6868439B2 (en) | 2002-04-04 | 2005-03-15 | Hewlett-Packard Development Company, L.P. | System and method for supervising use of shared storage by multiple caching servers physically connected through a switching router to said shared storage via a robust high speed connection |

| JP4219633B2 (ja) * | 2002-07-25 | 2009-02-04 | 株式会社日立製作所 | 記憶装置システムのデステージ方法、ディスク制御装置、記憶装置システム、及びプログラム |

| US6978325B2 (en) | 2002-08-29 | 2005-12-20 | International Business Machines Corporation | Transferring data in virtual tape server, involves determining availability of small chain of data, if large chain is not available while transferring data to physical volumes in peak mode |

| WO2004080601A2 (en) * | 2003-03-11 | 2004-09-23 | Phase Inc. | Centrifuge with controlled discharge of dense material |

| US20040205297A1 (en) | 2003-04-14 | 2004-10-14 | Bearden Brian S. | Method of cache collision avoidance in the presence of a periodic cache aging algorithm |

| US7441081B2 (en) * | 2004-12-29 | 2008-10-21 | Lsi Corporation | Write-back caching for disk drives |

| SE528387C2 (sv) * | 2005-03-08 | 2006-10-31 | Alfa Laval Corp Ab | Centrifugalseparator och förfarande för separering av en produkt i åtminstone en relativt tung fas och en relativt lätt fas |

| US20080041772A1 (en) * | 2006-08-17 | 2008-02-21 | Gambro Bct, Inc. | Blood Processing Apparatus with Robust Outflow Process Control |

| US20080272067A1 (en) * | 2007-05-01 | 2008-11-06 | Cavaliere William A | Methods and Apparatus for Classification of Suspended Materials |

| GB0724572D0 (en) * | 2007-12-17 | 2008-01-30 | Specialist Process Technologie | A separation device |

| US7734854B2 (en) * | 2008-01-04 | 2010-06-08 | International Business Machines Corporation | Device, system, and method of handling transactions |

| US20110263405A1 (en) * | 2010-04-22 | 2011-10-27 | Specialist Process Technologies Limited | Separator |

-

2006

- 2006-06-30 US US11/480,128 patent/US8234457B2/en not_active Expired - Fee Related

-

2007

- 2007-06-29 JP JP2007172478A patent/JP2008016024A/ja active Pending

Patent Citations (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6391761A (ja) * | 1986-10-06 | 1988-04-22 | Alps Electric Co Ltd | キヤツシユメモリ制御方法 |

| JPH05100954A (ja) * | 1991-10-09 | 1993-04-23 | Hokkaido Nippon Denki Software Kk | キヤツシユバツフア処理制御方式 |

| JPH06124596A (ja) * | 1991-11-28 | 1994-05-06 | Hitachi Ltd | フラッシュメモリを使用した記憶装置 |

| JPH0855072A (ja) * | 1994-08-12 | 1996-02-27 | Matsushita Electric Ind Co Ltd | ネットワークシステムとデータ処理システムとデータ蓄積方法 |

| US6272600B1 (en) * | 1996-11-15 | 2001-08-07 | Hyundai Electronics America | Memory request reordering in a data processing system |

| JPH10228417A (ja) * | 1996-11-15 | 1998-08-25 | Hyundai Electron America Inc | データ処理システムにおけるメモリリクエスト再順序付け法 |

| JPH11265315A (ja) * | 1997-10-31 | 1999-09-28 | Hewlett Packard Co <Hp> | 様々なdramバンクサイズと複数のインターリービング機構とをサポートする高速でコンパクトなアドレスビット経路指定機構 |

| JPH11328029A (ja) * | 1998-05-18 | 1999-11-30 | Olympus Optical Co Ltd | 情報記録再生装置 |

| US6928518B2 (en) * | 2001-11-01 | 2005-08-09 | Sun Microsystems, Inc. | Disk drive employing adaptive flushing of a write cache |

| JP2003318947A (ja) * | 2002-04-23 | 2003-11-07 | Mitsubishi Electric Corp | 多層メモリ使用交換装置 |

| JP2004213470A (ja) * | 2003-01-07 | 2004-07-29 | Nec Corp | ディスクアレイ装置及びディスクアレイ装置におけるデータ書き込み方法 |

| US20050071550A1 (en) * | 2003-09-29 | 2005-03-31 | International Business Machines Corporation (Ibm) | Increasing through-put of a storage controller by autonomically adjusting host delay |

| US7171516B2 (en) * | 2003-09-29 | 2007-01-30 | International Business Machines Corporation | Increasing through-put of a storage controller by autonomically adjusting host delay |

| US20050182906A1 (en) * | 2004-02-18 | 2005-08-18 | Paresh Chatterjee | Systems and methods for cache synchronization between redundant storage controllers |

| US20060248308A1 (en) * | 2005-04-27 | 2006-11-02 | Dot Hill Systems Corp. | Multiple mode controller method and apparatus |

Also Published As

| Publication number | Publication date |

|---|---|

| US20080005478A1 (en) | 2008-01-03 |

| US8234457B2 (en) | 2012-07-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8363519B2 (en) | Hot data zones | |

| US7743216B2 (en) | Predicting accesses to non-requested data | |

| US7996623B2 (en) | Read ahead storage control | |

| CN104603739B (zh) | 对并行存储的块级访问 | |

| US7814351B2 (en) | Power management in a storage array | |

| JP4933861B2 (ja) | ストレージ制御装置、データ管理システムおよびデータ管理方法 | |

| JP5126621B2 (ja) | 二重アクティブ・コントローラ内のライト・キャッシュ・データのフェイルオーバーおよびフェイルバック | |

| US7761659B2 (en) | Wave flushing of cached writeback data to a storage array | |

| JP5638744B2 (ja) | コマンド・キュー・ローディング | |

| JP5882557B2 (ja) | 要求優先順位シーク・マネージャ | |

| JP2008016024A (ja) | キャッシュされたデータのダイナミック適応フラッシング | |

| JP2006285808A (ja) | ストレージシステム | |

| US8244975B2 (en) | Command queue ordering by flipping active write zones | |

| US10564865B2 (en) | Lockless parity management in a distributed data storage system | |

| JP2005267038A (ja) | ストレージシステムの運用方法 | |

| JP2005293205A (ja) | 記憶制御装置、制御方法、および制御プログラム。 | |

| US7590800B2 (en) | 2D dynamic adaptive data caching | |

| US7032086B2 (en) | System and method for adjusting storage device layout with at least one status for the adjusting | |

| JP2010244532A (ja) | ストレージアレイでミラー化されたキャッシュボリュームを用いることでドライブオーバーヘッドを軽減するシステム | |

| JP5376624B2 (ja) | ホスト適応シーク技術環境 | |

| JP2005539303A (ja) | 電力効率高容量なスケーラブルな記憶システムのための方法および装置 | |

| JP5594942B2 (ja) | 好適なゾーン・スケジューリング | |

| JP2009054050A (ja) | Raid装置、raid装置の制御部およびraid装置のライトバック制御方法 | |

| JP2009070489A (ja) | ストレージ装置及びその制御方法、並びにディスク装置 | |

| US20080034157A1 (en) | Massively parallel data storage and processing system |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100622 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100622 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20100622 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120126 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120207 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120807 |