JP2005293205A - 記憶制御装置、制御方法、および制御プログラム。 - Google Patents

記憶制御装置、制御方法、および制御プログラム。 Download PDFInfo

- Publication number

- JP2005293205A JP2005293205A JP2004107030A JP2004107030A JP2005293205A JP 2005293205 A JP2005293205 A JP 2005293205A JP 2004107030 A JP2004107030 A JP 2004107030A JP 2004107030 A JP2004107030 A JP 2004107030A JP 2005293205 A JP2005293205 A JP 2005293205A

- Authority

- JP

- Japan

- Prior art keywords

- write

- storage

- data

- cache memory

- raid

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0804—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches with main memory updating

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0866—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches for peripheral storage systems, e.g. disk cache

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Memory System Of A Hierarchy Structure (AREA)

Abstract

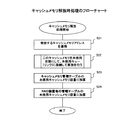

【解決手段】 RAID制御装置1内のキャッシュメモリ2に格納されているデータの複数のRAID装置3へのライトバックをLRU法によって行う手段4と、手段4によって実行されているライトバックの数が少ない装置3を選択して、選択した装置3に対してデータのライトバックを行う手段5とを備える。

【選択図】図1

Description

以上のように本発明によれば、まず記憶制御装置、たとえばRAID制御装置内のキャッシュメモリを複数の記憶装置、例えばRAID装置に対応して分割して割当てることによって、キャッシュメモリの内部がスループット性能の悪い記憶装置に掃き出すべきデータで埋め尽くされることが防止される。

複数の記憶装置を制御する記憶制御装置において、

該記憶制御装置内のキャッシュメモリに格納されているデータの前記複数の記憶装置へのライトバックをLRU法によって行うLRUライトバック手段と、

該LRUライトバック手段によって実行されているライトバックの数が少ない記憶装置を選択して、該選択した記憶装置に対するデータのライトバックを行うライトバックスケジュール処理手段とを備えることを特徴とする記憶制御装置。

前記記憶制御装置において、

前記複数の記憶装置を、該記憶装置が実行しているライトバックの数によって複数のグループに分割した結果を記憶するライトバックグループ管理手段をさらに備え、

前記ライトバックスケジュール処理手段が、ライトバックグループ管理手段の記憶内容に従ってライトバックの数が少ないグループ内の記憶装置を選択することを特徴とする付記1記載の記憶制御装置。

前記記憶制御装置において、

前記複数の記憶装置毎に実行されているライトバックの数を記憶する記憶装置管理手段をさらに備え、

前記ライトバックスケジュール処理手段が、該記憶装置管理手段の記憶内容に従ってライトバックの数が少ない記憶装置を選択することを特徴とする付記1記載の記憶制御装置。

前記記憶制御装置において、

該記憶制御装置内のキャッシュメモリの容量を分割して、前記複数の記憶装置に割当てるキャッシュメモリ割当手段と、

該割当てられた容量の内で該キャッシュメモリにデータが格納されていない未使用領域の容量を記憶装置毎に記憶する記憶装置管理手段とをさらに備え、

前記ライトバックスケジュール処理手段が、該記憶装置管理手段の記憶内容に従って該未使用領域の少ない記憶装置を選択することを特徴とする付記1記載の記憶制御装置。

前記記憶制御装置において、

前記記憶装置に割当てられたキャッシュメモリの容量の内部に格納されているデータのキューを記憶装置毎に管理するキャッシュメモリ管理手段をさらに備え、

前記ライトバックスケジュール処理手段が、選択した記憶装置のキューにおけるLRU位置のデータのライトバックを行うことを特徴とする付記4記載の記憶制御装置。

自装置内のキャッシュメモリに格納されているデータの複数の外部の記憶装置へのライトバックをLRU法によって行うLRUライトバック手段と、

該LRUライトバック手段によって実行されているライトバックの数が少ない記憶装置を選択し、該選択した記憶装置に対するデータのライトバックを行うライトバックスケジュール処理手段とを備える記憶制御装置と、

該記憶制御装置によって制御される複数の記憶装置とによって構成されることを特徴とするデータ記憶システム。

前記記憶装置が複数のディスクを備えるRAID装置であり、

前記記憶制御装置が該複数のRAID装置を制御するRAID制御装置であることを特徴とする付記6記載のデータ記憶システム。

前記記憶制御装置が、前記複数の記憶装置を、該記憶装置が実行しているライトバックの数によって複数のグループに分割した結果を記憶するライトバックグループ管理手段をさらに備え、

前記ライトバックスケジュール処理手段が、ライトバックグループ管理手段の記憶内容に従ってライトバックの数が少ないグループ内の記憶装置を選択することを特徴とする付記6記載のデータ記憶システム。

前記記憶制御装置が、前記複数の記憶装置毎に実行されているライトバックの数を記憶する記憶装置管理手段をさらに備え、

前記ライトバックスケジュール処理手段が、該記憶装置管理手段の記憶内容に従ってライトバックの数が少ない記憶装置を選択することを特徴とする付記6記載のデータ記憶システム。

前記記憶制御装置が、該記憶制御装置内のキャッシュメモリの容量を分割して、前記複数の記憶装置に割当てるキャッシュメモリ割当手段と、

該割当てられた容量の内で該キャッシュメモリにデータが格納されていない未使用領域の容量を記憶装置毎に記憶する記憶装置管理手段とをさらに備え、

前記ライトバックスケジュール処理手段が、該記憶装置管理手段の記憶内容に従って該未使用領域の少ない記憶装置を選択することを特徴とする付記6記載のデータ記憶システム。

前記記憶制御装置が、前記記憶装置に割当てられたキャッシュメモリの容量の内部に格納されているデータのキューを記憶装置毎に管理するキャッシュメモリ管理手段をさらに備え、

前記ライトバックスケジュール処理手段が、選択した記憶装置のキューにおけるLRU位置のデータのライトバックを行うことを特徴とする付記10記載のデータ記憶システム。

複数の記憶装置を制御する記憶制御方法において、

キャッシュメモリに格納されているデータの前記複数の記憶装置側へのライトバックをLRU法によって実行し、

該LRU法によって実行されているライトバックの数が少ない記憶装置を選択して、該選択した記憶装置に対するデータのライトバックを実行することを特徴とする記憶制御方法。

前記記憶制御方法において、

前記複数の記憶装置を、該記憶装置が実行しているライトバックの数によって複数のグループに分割し、

前記記憶装置の選択において、該記憶内容に従ってライトバックの数が少ないグループ内の記憶装置を選択することを特徴とする付記12記載の記憶制御方法。

前記記憶制御方法において、

前記複数の記憶装置毎に実行されているライトバックの数を記憶し、

前記記憶装置の選択において、該記憶内容に従ってライトバックの数が少ない記憶装置を選択することを特徴とする付記12記載の記憶制御方法。

前記記憶制御方法において、

前記記憶制御装置内のキャッシュメモリの容量を分割して、前記複数の記憶装置に割当て、

該割当てられた容量の内で該キャッシュメモリにデータが格納されていない未使用領域の容量を記憶装置毎に記憶し、

前記記憶装置の選択において、該記憶の内容に従って該未使用領域の少ない記憶装置を選択することを特徴とする付記12記載の記憶制御方法。

前記記憶制御方法において、

前記記憶装置に割当てられたキャッシュメモリの容量の内部に格納されているデータのキューを記憶装置毎に管理し、

前記選択した記憶装置のキューにおけるLRU位置のデータのライトバックを行うことを特徴とする付記15記載の記憶制御方法。

複数の記憶装置を制御する計算機によって使用されるプログラムであって、

キャッシュメモリに格納されているデータの前記複数の記憶装置側へのライトバックをLRU法によって実行する手順と、

該LRU法によって実行されているライトバックの数が少ない記憶装置を選択して、該選択した記憶装置に対するデータのライトバックを実行する手順とを計算機に実行させるためのプログラム。

前記記憶装置の選択において、

前記複数の記憶装置を、該記憶装置が実行しているライトバックの数によって複数のグループに分割した結果を記憶するメモリの記憶内容に従ってライトバックの数が少ないグループ内の記憶装置を選択することを特徴とする付記17記載のプログラム。

前記記憶装置の選択において、

前記複数の記憶装置毎に実行されているライトバックの数を記憶するメモリの記憶内容に従ってライトバックの数が少ない記憶装置を選択することを特徴とする付記17記載のプログラム。

前記記憶装置の選択において、

前記記憶制御装置内のキャッシュメモリの容量が分割され、前記複数の記憶装置に割当てられた容量の内で該キャッシュメモリにデータが格納されていない未使用領域の容量を記憶装置毎に記憶するメモリの記憶内容に従って該未使用領域の少ない記憶装置を選択することを特徴とする付記17記載のプログラム。

前記記憶装置に割当てられたキャッシュメモリの容量の内部に格納されているデータのキューが記憶装置毎に管理され、

前記選択した記憶装置のキューにおけるLRU位置のデータのライトバックを行うことを特徴とする付記20記載のプログラム。

複数の記憶装置を制御する計算機によって使用される記憶媒体であって、

キャッシュメモリに格納されているデータの前記複数の記憶装置側へのライトバックをLRU法によって実行するステップと、

該LRU法によって実行されているライトバックの数が少ない記憶装置を選択して、該選択した記憶装置に対するデータのライトバックを実行するステップとを計算機に実行させるプログラムを格納した計算機読出し可能可搬型記憶媒体。

前記記憶装置の選択において、

前記複数の記憶装置を、該記憶装置が実行しているライトバックの数によって複数のグループに分割した結果を記憶するメモリの記憶内容に従ってライトバックの数が少ないグループ内の記憶装置を選択することを特徴とする付記22記載の計算機読出し可能可搬型記憶媒体。

前記記憶装置の選択において、

前記複数の記憶装置毎に実行されているライトバックの数を記憶するメモリの記憶内容に従ってライトバックの数が少ない記憶装置を選択することを特徴とする付記22記載の計算機読出し可能可搬型記憶媒体。

前記記憶装置の選択において、

前記記憶制御装置内のキャッシュメモリの容量が分割され、前記複数の記憶装置に割当てられた容量の内で該キャッシュメモリにデータが格納されていない未使用領域の容量を記憶装置毎に記憶するメモリの記憶内容に従って該未使用領域の少ない記憶装置を選択することを特徴とする付記22記載の計算機読出し可能可搬型記憶媒体。

前記記憶装置に割当てられたキャッシュメモリの容量の内部に格納されているデータのキューが記憶装置毎に管理され、

前記選択した記憶装置のキューにおけるLRU位置のデータのライトバックを行うことを特徴とする付記25記載の計算機読出し可能可搬型記憶媒体。

2 キャッシュメモリ

3 記憶装置

4 LRUライトバック手段

5 ライトバックスケジュール処理手段

10 RAID制御装置

11 ホストコンピュータ(サーバ)

12 RAID装置

13 チャネルアダプタ

14 デバイスアダプタ

15 中央制御部

16 キャッシュメモリ

17 キャッシュメモリ管理テーブル

18 RAID装置毎の管理テーブル

19 ライトバックグループ管理テーブル

20 CPU

21 リード・オンリ・メモリ(ROM)

22 ランダム・アクセス・メモリ(RAM)

23 通信インタフェース

24 記憶装置

25 入出力装置

26 読取装置

27 バス

28 プログラム提供者

29 ネットワーク

30 可搬型記憶媒体

Claims (10)

- 複数の記憶装置を制御する記憶制御装置において、

該記憶制御装置内のキャッシュメモリに格納されているデータの前記複数の記憶装置へのライトバックをLRU法によって行うLRUライトバック手段と、

該LRUライトバック手段によって実行されているライトバックの数が少ない記憶装置を選択して、該選択した記憶装置に対するデータのライトバックを行うライトバックスケジュール処理手段とを備えることを特徴とする記憶制御装置。 - 前記記憶制御装置において、

前記複数の記憶装置を、該記憶装置が実行しているライトバックの数によって複数のグループに分割した結果を記憶するライトバックグループ管理手段をさらに備え、

前記ライトバックスケジュール処理手段が、ライトバックグループ管理手段の記憶内容に従ってライトバックの数が少ないグループ内の記憶装置を選択することを特徴とする請求項1記載の記憶制御装置。 - 前記記憶制御装置において、

前記複数の記憶装置毎に実行されているライトバックの数を記憶する記憶装置管理手段をさらに備え、

前記ライトバックスケジュール処理手段が、該記憶装置管理手段の記憶内容に従ってライトバックの数が少ない記憶装置を選択することを特徴とする請求項1記載の記憶制御装置。 - 前記記憶制御装置において、

該記憶制御装置内のキャッシュメモリの容量を分割して、前記複数の記憶装置に割当てるキャッシュメモリ割当手段と、

該割当てられた容量の内で該キャッシュメモリにデータが格納されていない未使用領域の容量を記憶装置毎に記憶する記憶装置管理手段とをさらに備え、

前記ライトバックスケジュール処理手段が、該記憶装置管理手段の記憶内容に従って該未使用領域の少ない記憶装置を選択することを特徴とする請求項1記載の記憶制御装置。 - 前記記憶制御装置において、

前記記憶装置に割当てられたキャッシュメモリの容量の内部に格納されているデータのキューを記憶装置毎に管理するキャッシュメモリ管理手段をさらに備え、

前記ライトバックスケジュール処理手段が、選択した記憶装置のキューにおけるLRU位置のデータのライトバックを行うことを特徴とする請求項4記載の記憶制御装置。 - 自装置内のキャッシュメモリに格納されているデータの複数の外部の記憶装置へのライトバックをLRU法によって行うLRUライトバック手段と、

該LRUライトバック手段によって実行されているライトバックの数が少ない記憶装置を選択し、該選択した記憶装置に対するデータのライトバックを行うライトバックスケジュール処理手段とを備える記憶制御装置と、

該記憶制御装置によって制御される複数の記憶装置とによって構成されることを特徴とするデータ記憶システム。 - 前記記憶装置が複数のディスクを備えるRAID装置であり、

前記記憶制御装置が該複数のRAID装置を制御するRAID制御装置であることを特徴とする請求項6記載のデータ記憶システム。 - 複数の記憶装置を制御する記憶制御方法において、

キャッシュメモリに格納されているデータの前記複数の記憶装置側へのライトバックをLRU法によって実行し、

該LRU法によって実行されているライトバックの数が少ない記憶装置を選択して、該選択した記憶装置に対するデータのライトバックを実行することを特徴とする記憶制御方法。 - 複数の記憶装置を制御する計算機によって使用されるプログラムであって、

キャッシュメモリに格納されているデータの前記複数の記憶装置側へのライトバックをLRU法によって実行する手順と、

該LRU法によって実行されているライトバックの数が少ない記憶装置を選択して、該選択した記憶装置に対するデータのライトバックを実行する手順とを計算機に実行させるためのプログラム。 - 複数の記憶装置を制御する計算機によって使用される記憶媒体であって、

キャッシュメモリに格納されているデータの前記複数の記憶装置側へのライトバックをLRU法によって実行するステップと、

該LRU法によって実行されているライトバックの数が少ない記憶装置を選択して、該選択した記憶装置に対するデータのライトバックを実行するステップとを計算機に実行させるプログラムを格納した計算機読出し可能可搬型記憶媒体。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004107030A JP4429780B2 (ja) | 2004-03-31 | 2004-03-31 | 記憶制御装置、制御方法、および制御プログラム。 |

| US10/935,080 US7321955B2 (en) | 2004-03-31 | 2004-09-08 | Control device, control method and storage medium recording a control program for controlling write-back schedule of data from cache memory to a plurality of storage devices |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004107030A JP4429780B2 (ja) | 2004-03-31 | 2004-03-31 | 記憶制御装置、制御方法、および制御プログラム。 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005293205A true JP2005293205A (ja) | 2005-10-20 |

| JP4429780B2 JP4429780B2 (ja) | 2010-03-10 |

Family

ID=35055718

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004107030A Expired - Fee Related JP4429780B2 (ja) | 2004-03-31 | 2004-03-31 | 記憶制御装置、制御方法、および制御プログラム。 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7321955B2 (ja) |

| JP (1) | JP4429780B2 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011170447A (ja) * | 2010-02-16 | 2011-09-01 | Fujitsu Ltd | ストレージシステムおよびデータ書込み方法 |

| US8239634B2 (en) | 2007-06-05 | 2012-08-07 | Nec Corporation | Input/output control based on information specifying input/output issuing source and input/output priority |

| US8364893B2 (en) | 2007-08-28 | 2013-01-29 | Fujitsu Limited | RAID apparatus, controller of RAID apparatus and write-back control method of the RAID apparatus |

Families Citing this family (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4819369B2 (ja) * | 2005-02-15 | 2011-11-24 | 株式会社日立製作所 | ストレージシステム |

| US20120124311A1 (en) * | 2009-08-04 | 2012-05-17 | Axxana (Israel) Ltd. | Data Gap Management in a Remote Data Mirroring System |

| US8700852B2 (en) * | 2010-02-03 | 2014-04-15 | International Business Machines Corporation | Processing read and write requests in a storage controller |

| US9335928B2 (en) * | 2011-10-01 | 2016-05-10 | International Business Machines Corporation | Using unused portion of the storage space of physical storage devices configured as a RAID |

| US9836340B2 (en) * | 2011-10-03 | 2017-12-05 | International Business Machines Corporation | Safe management of data storage using a volume manager |

| US9817733B2 (en) * | 2011-10-05 | 2017-11-14 | International Business Machines Corporation | Resource recovery for checkpoint-based high-availability in a virtualized environment |

| EP2859457A4 (en) * | 2012-06-08 | 2016-05-11 | Hewlett Packard Development Co | MEMORY |

| US10037271B1 (en) * | 2012-06-27 | 2018-07-31 | Teradata Us, Inc. | Data-temperature-based control of buffer cache memory in a database system |

| CN102779017B (zh) * | 2012-06-29 | 2016-04-13 | 华中科技大学 | 一种固态盘中数据缓存区的控制方法 |

| CN105103234A (zh) * | 2012-11-20 | 2015-11-25 | 查尔斯·I·派德尔 | 固态驱动器体系结构 |

| US11037625B2 (en) | 2012-11-20 | 2021-06-15 | Thstyme Bermuda Limited | Solid state drive architectures |

| US9778884B2 (en) * | 2013-03-13 | 2017-10-03 | Hewlett Packard Enterprise Development Lp | Virtual storage pool |

| US9201662B2 (en) * | 2013-03-29 | 2015-12-01 | Dell Products, Lp | System and method for pre-operating system memory map management to minimize operating system failures |

| US20140297953A1 (en) * | 2013-03-31 | 2014-10-02 | Microsoft Corporation | Removable Storage Device Identity and Configuration Information |

| US9836413B2 (en) * | 2013-04-03 | 2017-12-05 | International Business Machines Corporation | Maintaining cache consistency in a cache for cache eviction policies supporting dependencies |

| US9824020B2 (en) * | 2013-12-30 | 2017-11-21 | Unisys Corporation | Systems and methods for memory management in a dynamic translation computer system |

| US10031863B2 (en) * | 2014-01-30 | 2018-07-24 | Hewlett Packard Enterprise Development Lp | Access controlled memory region |

| WO2015116078A1 (en) * | 2014-01-30 | 2015-08-06 | Hewlett-Packard Development Company, L.P. | Memory data versioning |

| TWI552162B (zh) * | 2014-07-31 | 2016-10-01 | Zhi-Cheng Xiao | Low power memory |

| US9767024B2 (en) * | 2014-12-18 | 2017-09-19 | Intel Corporation | Cache closure and persistent snapshot in dynamic code generating system software |

| US9824026B2 (en) * | 2014-12-23 | 2017-11-21 | Intel Corporation | Apparatus and method for managing a virtual graphics processor unit (VGPU) |

| US9875037B2 (en) * | 2015-06-18 | 2018-01-23 | International Business Machines Corporation | Implementing multiple raid level configurations in a data storage device |

| US9946512B2 (en) * | 2015-09-25 | 2018-04-17 | International Business Machines Corporation | Adaptive radix external in-place radix sort |

| US9760290B2 (en) * | 2015-09-25 | 2017-09-12 | International Business Machines Corporation | Smart volume manager for storage space usage optimization |

| US9921757B1 (en) * | 2016-03-31 | 2018-03-20 | EMC IP Holding Company LLC | Using an FPGA for integration with low-latency, non-volatile memory |

| US10296460B2 (en) * | 2016-06-29 | 2019-05-21 | Oracle International Corporation | Prefetch bandwidth throttling by dynamically adjusting miss buffer prefetch-dropping thresholds |

| WO2025038232A1 (en) * | 2023-08-15 | 2025-02-20 | Micron Technology, Inc. | Near-cache compute |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3188071B2 (ja) * | 1993-10-14 | 2001-07-16 | 富士通株式会社 | ディスクキャッシュ装置 |

| US5592432A (en) * | 1995-09-05 | 1997-01-07 | Emc Corp | Cache management system using time stamping for replacement queue |

| JPH11288387A (ja) | 1998-12-11 | 1999-10-19 | Fujitsu Ltd | ディスクキャッシュ装置 |

| US6304946B1 (en) * | 1999-07-01 | 2001-10-16 | Emc Corporation | System and method for optimizing cache write backs to disks |

| US6665740B1 (en) * | 1999-11-12 | 2003-12-16 | Emc Corporation | Logical volume selection in a probability-based job scheduler |

| US6594739B1 (en) * | 2001-09-11 | 2003-07-15 | Emc Corporation | Memory system and method of using same |

| US6785771B2 (en) * | 2001-12-04 | 2004-08-31 | International Business Machines Corporation | Method, system, and program for destaging data in cache |

| JP2003196032A (ja) | 2001-12-26 | 2003-07-11 | Nec Corp | ストレージ装置のライトキャッシュ制御方法及びストレージ装置 |

| JP4322068B2 (ja) * | 2003-03-07 | 2009-08-26 | 富士通株式会社 | ストレージシステム及びそのデイスク負荷バランス制御方法 |

| CA2429407C (en) * | 2003-05-23 | 2012-01-03 | Robert Beaumont | Sleeve for toilet flanges and drains |

| US7039785B2 (en) * | 2004-02-24 | 2006-05-02 | Hitachi, Ltd. | Method and apparatus for increasing an amount of memory on demand when monitoring remote mirroring performance |

-

2004

- 2004-03-31 JP JP2004107030A patent/JP4429780B2/ja not_active Expired - Fee Related

- 2004-09-08 US US10/935,080 patent/US7321955B2/en not_active Expired - Fee Related

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8239634B2 (en) | 2007-06-05 | 2012-08-07 | Nec Corporation | Input/output control based on information specifying input/output issuing source and input/output priority |

| US8364893B2 (en) | 2007-08-28 | 2013-01-29 | Fujitsu Limited | RAID apparatus, controller of RAID apparatus and write-back control method of the RAID apparatus |

| JP2011170447A (ja) * | 2010-02-16 | 2011-09-01 | Fujitsu Ltd | ストレージシステムおよびデータ書込み方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US7321955B2 (en) | 2008-01-22 |

| JP4429780B2 (ja) | 2010-03-10 |

| US20050223168A1 (en) | 2005-10-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4429780B2 (ja) | 記憶制御装置、制御方法、および制御プログラム。 | |

| US7475185B2 (en) | Nonvolatile memory system, nonvolatile memory device, memory controller, access device, and method for controlling nonvolatile memory device | |

| US5651132A (en) | Disk array control system | |

| US6665740B1 (en) | Logical volume selection in a probability-based job scheduler | |

| US6675176B1 (en) | File management system | |

| US9495105B2 (en) | System managing a plurality of flash memory devices | |

| US20100011154A1 (en) | Data accessing method for flash memory and storage system and controller using the same | |

| EP2200045A1 (en) | Method of updating contents of a multibit flash memory | |

| EP0727745A1 (en) | Memory control apparatus and its control method | |

| US20070168754A1 (en) | Method and apparatus for ensuring writing integrity in mass storage systems | |

| JP2008015769A (ja) | ストレージシステム及び書き込み分散方法 | |

| JPH10187505A (ja) | 情報記憶システム及び同システムに適用するデータ配置方法 | |

| JP2006227688A (ja) | ストレージシステム | |

| JP2012523624A (ja) | フラッシュメモリデータストレージデバイスにデータを格納するための方法及び装置 | |

| US11128535B2 (en) | Computer system and data management method | |

| JP2002278704A (ja) | 処理最適化方法、コンピュータ、及び記憶装置 | |

| US6748494B1 (en) | Device for controlling access to units of a storage device | |

| JP2007199905A (ja) | 半導体記憶装置の制御方法 | |

| JP2010170295A (ja) | 記憶装置、記憶装置のデータ転送方法 | |

| US6532513B1 (en) | Information recording and reproduction apparatus | |

| CN112748865A (zh) | 用于存储管理的方法、电子设备和计算机程序产品 | |

| JPH08137754A (ja) | ディスクキャッシュ装置 | |

| JP4430092B2 (ja) | Raid装置、raid装置の制御部およびraid装置のライトバック制御方法 | |

| US7676644B2 (en) | Data processing system, storage apparatus and management console | |

| WO2022234740A1 (ja) | 情報処理装置、情報処理システム、および情報処理方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060623 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090519 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090623 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090821 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20091215 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20091216 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121225 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |