JP2007173669A - 多層回路基板及びicパッケージ - Google Patents

多層回路基板及びicパッケージ Download PDFInfo

- Publication number

- JP2007173669A JP2007173669A JP2005371530A JP2005371530A JP2007173669A JP 2007173669 A JP2007173669 A JP 2007173669A JP 2005371530 A JP2005371530 A JP 2005371530A JP 2005371530 A JP2005371530 A JP 2005371530A JP 2007173669 A JP2007173669 A JP 2007173669A

- Authority

- JP

- Japan

- Prior art keywords

- terminal

- capacitor

- package

- power supply

- circuit board

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 239000003990 capacitor Substances 0.000 claims abstract description 273

- 230000002093 peripheral effect Effects 0.000 claims description 6

- 230000007257 malfunction Effects 0.000 abstract description 11

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 29

- 239000011889 copper foil Substances 0.000 description 29

- 230000000694 effects Effects 0.000 description 9

- 239000000758 substrate Substances 0.000 description 6

- 238000010586 diagram Methods 0.000 description 4

- 238000007796 conventional method Methods 0.000 description 3

- 239000004065 semiconductor Substances 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000010030 laminating Methods 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 230000009466 transformation Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1515—Shape

- H01L2924/15158—Shape the die mounting substrate being other than a cuboid

- H01L2924/15159—Side view

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

Landscapes

- Ceramic Capacitors (AREA)

Abstract

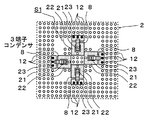

【解決手段】ICパッケージ1と信号層2とグランド層3と電源層4とを備える。ICパッケージ1はBGAタイプの端子群と凹部11とを有している。信号層2は2端子コンデンサ7用の実装スペースS1を有し、この実装スペースS1内に、ICパッケージ1の電源端子12に対応したランド21とこのランド21に対向するランド22とが形成されている。2端子コンデンサ7はランド21,22上に接続されている。これにより、電源端子12は2端子コンデンサ7が接続されたランド21,ビアホール41〜43を通じて電源層4に接続され、2端子コンデンサ7のアース端子72はランド22及びビアホール31を通じてグランド層3に接続される。

【選択図】図1

Description

このため、一般には、コンデンサを基板の電源ラインに配設し、デカップリングコンデンサとして機能させることで、発生したノイズが他の回路に流出することを防ぐと共に、バイパスコンデンサとして機能させることで、電源ピンに電荷を供給し、電源電圧を安定させ、誤作動を防止する。

ところが、端子群がBGAタイプのICでは、多数のコンデンサを基板の表面に実装して、上記機能を確実に発揮させることは、構造上困難である。このため、従来の技術では、コンデンサを基板の裏面であって且つICのほぼ真下に配設することにより、コンデンサの上記機能を可能な限り発揮させるようにしている(例えば、特許文献1参照)。

しかしながら、上述した従来の技術では、コンデンサを基板の裏面に配設した構造をとった場合、インダクタンスの高いビアホールによって基板の表面と裏面をつなぐことになる。このため、電源端子からコンデンサ迄のインダクタンスやコンデンサからグランド層迄のインダクタンスが大きくなり、その結果、ICが誤動作を起こすおそれが高かった。

かかる構成により、外部電源が電源層に入力されると、電源層に接続されたコンデンサに充電される。そして、コンデンサに充電された電荷が、ICパッケージのスイッチング等のタイミングで電源端子を通じてICパッケージに電流として供給される。したがって、電源電圧を安定させるバイパスコンデンサとして機能する。

また、ICパッケージのスイッチング等によって電源端子に生じたノイズ電流は、コンデンサの電源用の電極及びグランド用の電極を通じてグランド層に排出される。したがって、コンデンサは、発生したノイズを除去するデカップリングコンデンサとして機能する。

ところで、ICパッケージに電流が供給されると、ICパッケージの電源端子からコンデンサ迄のインダクタンスと、コンデンサの残留インダクタンスと、コンデンサからグランド層迄のインダクタンスとの和に比例した逆起電力が発生する。

しかし、この発明では、コンデンサを、ICパッケージの裏面と対向するIC実装領域に設けられた実装スペースに配しているので、ICパッケージの電源端子からコンデンサ迄の距離と、コンデンサからグランド層迄の距離が短くなり、これらの間のインダクタンス値が小さくなる。このため、ICパッケージに供給される電流によって生じる逆起電力は、上記した従来の技術で生じる逆起電力に比べて、極めて小さくなる。

かかる構成により、外部電源が電源層に入力されると、電源層に接続された入出力端子を通じて2端子コンデンサに充電される。そして、2端子コンデンサに充電された電荷が入出力端子に接続された電源端子を通じてICパッケージに電流として供給される。

また、ICパッケージの電源端子に生じたノイズ電流は、2端子コンデンサの入出力端子及びアース端子を通じてグランド層に排出される。

かかる構成により、外部電源が電源層に入力されると、電源層に接続された入力端子を通じて3端子コンデンサに充電される。そして、3端子コンデンサに充電された電荷が出力端子に接続された電源端子を通じてICパッケージに電流として供給される。

また、電源端子に生じたノイズ電流は、3端子コンデンサを介さなければ電源層に流出できなくなるため、より高いデカップリング効果を得ることができる。

さらに、この3端子コンデンサの残留インダクタンスは、極めて小さいので、ICパッケージの電源端子からグランド層迄のインダクタンス値をさらに小さくすることができる。

かかる構成により、ICパッケージの電源端子からコンデンサ迄の間のインダクタンス値を小さくすることができる。

かかる構成により、ICパッケージの実装時に、ICパッケージが凹部内に納まって、ICパッケージとコンデンサとの接触を回避することができ、この結果、多層回路基板全体の低背化を図ることができる。

かかる構成により、裏面のほぼ中央部に多くの電源端子を有するICパッケージを用いることで、コンデンサを多くの電源端子に近づけることができる。

かかる構成により、裏面の周縁部に多くの電源端子を有するICパッケージを用いることで、コンデンサを多くの電源端子に近づけることができる。

かかる構成により、電源端子を多層回路基板の電源層に接続し、グランド端子を多層回路基板のグランド層に接続して、ICパッケージを多層回路基板の表面に実装することができる。かかる状態で、外部電源を電源層に入力すると、電源端子を通じて電源層に接続されたコンデンサが充電される。そして、コンデンサに充電された電荷が、電源端子を通じてICパッケージ内に電流として供給される。したがって、コンデンサが、バイパスコンデンサとして機能する。

また、電源端子に生じたノイズ電流は、コンデンサの電源用の電極及びグランド用の電極を通じてグランド端子に至り、グランド端子を通じてグランド層に排出される。したがって、コンデンサが、発生したノイズを除去するデカップリングコンデンサとして機能する。

さらに、コンデンサを、ICパッケージの端子群内に設けられた実装スペースに取り付け、コンデンサの電源用の電極及びグランド用の電極を、電源端子及びグランド端子に直接接続しているので、電源端子からコンデンサ迄のインダクタンスとコンデンサからグランド端子迄のインダクタンスとを極めて小さくすることができる。

かかる構成により、ICパッケージを多層回路基板に実装して、外部電源を電源層に入力すると、外部電源が、電源層に接続された電源端子に入力し、電源端子に接続された入出力端子を通じて2端子コンデンサに充電される。そして、2端子コンデンサに充電された電荷が入出力端子に接続された電源端子を通じてICパッケージ内に電流として供給される。

また、電源端子に生じたノイズ電流は、2端子コンデンサの入出力端子及びアース端子を通じてグランド端子に至り、グランド端子を通じて多層回路基板のグランド層に排出される。

かかる構成により、ICパッケージの電源端子と多層回路基板の電源層を3端子コンデンサを介して接続し、グランド端子を多層回路基板のグランド層に接続して、ICパッケージを多層回路基板の表面に実装することができる。かかる状態で、外部電源を電源層に入力すると、外部電源が、電源層に接続された3端子コンデンサに充電される。そして、3端子コンデンサに充電された電荷が出力端子に接続された電源端子を通じてICパッケージ内に電流として供給される。

また、電源端子に生じたノイズ電流は、3端子コンデンサのアース端子を通じてグランド端子に至り、グランド端子を通じてICパッケージのグランド電極に排出される。

さらに、この3端子コンデンサの残留インダクタンスは、極めて小さいので、電源端子から多層回路基板のグランド層迄のインダクタンス値をさらに小さくすることができる。

かかる構成により、電源端子からコンデンサ迄の間のインダクタンス値をさらに小さくすることができる。

かかる構成により、ICパッケージの複数の電源端子からコンデンサ迄の間のインダクタンス値を小さくすることができる。

かかる構成により、多層回路基板への実装時におけるICパッケージの低背化が可能となる。

かかる構成により、コンデンサを、裏面のほぼ中央部に存する電源端子に近づけることができる。

図3は、この実施例に適用する2端子コンデンサの外観図であり、図4は、2端子コンデンサの等価回路図であり、図5は、2端子コンデンサのランド実装状態を示す平面図であり、図6は、2端子コンデンサを実装スペースに実装した状態を示す平面図である。

図3に示すように、2端子コンデンサ7は、電源用の入出力端子71を一方端部に有し且つグランド用のアース端子72を他方端部に有するチップ型の2端子コンデンサである。

すなわち、この2端子コンデンサ7は、誘電体シートにパターンを印刷して、パターンが交互に向き合うように、複数の誘電体シートを積層して構成したもので、図4に示すように、ノイズ等の高周波電流Iを入出力端子71からアース端子72に通す。

この実施例の多層回路基板が上記の如き積層構造を取ることにより、図7に示すように、ICパッケージ1を信号層2に実装した状態においては、ICパッケージ1の電源端子12がランド21に接続するので、2端子コンデンサ7の入出力端子71が、ICパッケージ1の電源端子12に接続すると共に電源層4にも接続した状態になる。

また、一方、2端子コンデンサ7のアース端子72は、ランド22を通じてグランド層3に接続した状態になる。

図8は、各部材の電気的接続状態を示す概略図であり、図9は、2端子コンデンサの機能を説明するための概略部分拡大断面図である。

図8に示すように、ICパッケージ1を実装した状態では、ICパッケージ1の電源端子12が、2端子コンデンサ7の入出力端子71が固着されたランド21,ビアホール43,孔42,ビアホール41を通じて、電源層4に接続されている。一方、2端子コンデンサ7のアース端子72が固着されたランド22は、ビアホール31を通じてグランド層3に接続されている。

このように、この実施例によれば、ICパッケージ1の電源端子12から2端子コンデンサ7迄のインダクタンスや2端子コンデンサ7からグランド層3迄のインダクタンスが非常に小さい。このため、ICパッケージ1に供給される電流によって生じる逆起電力は、上記した従来の技術で生じる逆起電力に比べて、無視できる程度に小さく、ICパッケージ1に対して安定した電源供給がなされる。

図10は、この発明の第2実施例に係る多層回路基板の要部であるコンデンサの実装スペースを示す平面図であり、図11は、2端子コンデンサを実装スペースに実装した状態を示す平面図であり、図12は、第2実施例の多層回路基板の概略断面図である。

この実施例は、実装スペースの形成位置が、上記第1実施例と異なる。

そして、2端子コンデンサ7の入出力端子71をランド21に接続すると共に、アース端子72をランド22に接続した。

その他の構成、作用及び効果は、上記第1実施例と同様であるので、その記載は省略する。

図13は、この発明の第3実施例の要部である3端子コンデンサの実装状態を示す平面図であり、図14は、第3実施例の多層回路基板の概略断面図である。

この実施例は、図13及び図14に示すように、上記第1実施例で用いた2端子コンデンサ7の代わりに、3端子コンデンサ8を用いた。

図15に示すように、3端子コンデンサ8は、電源用電極としての入力端子81及び出力端子82を両端部に有すると共にグランド用電極としてのアース端子83を中央部に有したチップ型の積層貫通コンデンサである。

この3端子コンデンサ8では、図16に示すように、入力端子81,出力端子82を接続する貫通電極となるパターン84を、誘電体シート80に印刷し、これらの誘電体シート80を積層した。そして、アース端子83を接続するアース電極となるパターン85を誘電体シート80に印刷し、この誘電体シート80をパターン84が印刷された誘電体シート80と交互に積層した。これにより、図17に示すように、電源等の電流Iが入力端子81からパターン84を通じて出力端子82に至るようになっている。また、アース端子83に接続されたパターン85の接地機能により、アース端子83側の残留インダクタンスを低減している。すなわち、3端子コンデンサ8は、残留インダクタンスを2端子コンデンサ7に比べて極めて小さくした構造になっている。

そして、図18に示すように、3端子コンデンサ8の入力端子81,出力端子82及びアース端子83を、かかるランド21,ランド23及びランド22に固着した。このとき、図14に示すように、ランド21がビアホール41〜43を通じて電源層4に接続し、ランド22がビアホール31を通じてグランド層3に接続しているので、3端子コンデンサ8の入力端子81がランド21及びビアホール41〜43を通じて電源層4接続し、アース端子83がランド22及びビアホール31を通じてグランド層3に接続することとなる。したがって、各3端子コンデンサ8を凹部11内に収納した状態で、ICパッケージ1を信号層2に実装すると、ICパッケージ1の電源端子12が電源層4に接続された状態になる。

この図19及び図18に示すように、電源層4は、ビアホール41〜43及びランド21を通じて3端子コンデンサ8の入力端子81に接続され、この3端子コンデンサ8の出力端子82は、ランド23を通じてICパッケージ1の電源端子12に接続されている。そして、3端子コンデンサ8のアース端子83は、ランド22及びビアホール31を通じてグランド層3に接続されている。

また、ICパッケージ1の電源端子12に生じたノイズ電流は、3端子コンデンサ8のアース端子83及びランド22を通じてグランド層3に排出される。

その他の構成、作用及び効果は、上記第1実施例と同様であるので、その記載は省略する。

図20は、この発明の第4実施例の要部である3端子コンデンサの実装状態を示す平面図であり、図21は、第4実施例の多層回路基板の概略断面図である。

この実施例は、図20及び図21に示すように、上記第2実施例で用いた2端子コンデンサ7の代わりに、3端子コンデンサ8を用いた。

そして、3端子コンデンサ8の入力端子81,出力端子82及びアース端子83を、かかるランド21,ランド23及びランド22に固着した。

これにより、図21に示すように、ランド21がビアホール41〜43を通じて電源層4に接続し、ランド22がビアホール31を通じてグランド層3に接続しているので、3端子コンデンサ8の入力端子81がランド21及びビアホール41〜43を通じて電源層4に接続し、アース端子83がランド22及びビアホール31を通じてグランド層3に接続することとなる。したがって、各3端子コンデンサ8を凹部11′内に収納した状態で、ICパッケージ1を信号層2に実装すると、ICパッケージ1の電源端子12が電源層4に接続された状態になる。

その他の構成、作用及び効果は、上記第2及び第3実施例と同様であるので、その記載は省略する。

図22は、この発明の第5実施例に係るICパッケージを示す斜視図であり、図23は、コンデンサの実装状態を示す平面図である。

実装スペースS11を有する凹部11は、端子群9のほぼ中央部であって、電源端子12とグランド端子13の近傍に位置する。具体的には、黒丸で示すように、複数の電源端子12の組を、凹部11の外周に沿ってそれぞれ配置し、複数のグランド端子13の組を、電源端子12の各組に対向するように、凹部11の内周に沿ってそれぞれ配置した。

そして、各組の複数の電源端子12を幅広の銅箔パターン14で電気的に接続すると共に、各組の複数のグランド端子13を幅広の銅箔パターン15で電気的に接続した。

2端子コンデンサ7は、かかるランド部14a,15aに接続されている。

具体的には、その入出力端子71をランド部14aに接続し、アース端子72をランド部15aに接続した状態で、複数の2端子コンデンサ7が凹部11内の実装スペースS11に等間隔で実装されている。

これにより、2端子コンデンサ7の入出力端子71が銅箔パターン14を通じて電源端子12に接続し、アース端子72が銅箔パターン15を通じてグランド端子13に接続した状態になっている。

図24は、この実施例のICパッケージの実装例を示す概略断面図である。

このICパッケージ1−1は、図24に示す多層回路基板100に実装することができる。

多層回路基板100は、上記第1実施例の多層回路基板とほぼ同じ多層構造を成す。

すなわち、多層回路基板100は、ICパッケージ1−1の端子群9の配列に対応したランド群で成る信号層2′を表面に有している。そして、ランド21がビアホール41,孔42及びビアホール43を通じて電源層4に接続しており、ランド22がビアホール31を通じてグランド層3に接続している。

かかる状態で、電源を外部から電源層4に入力すると、電源が、ビアホール41〜43を通じてランド21に印加され、ランド21に接続された電源端子12から銅箔パターン14のランド部14aを通じて2端子コンデンサ7の入出力端子71に至り、2端子コンデンサ7に充電される。そして、2端子コンデンサ7に充電された電荷は、入出力端子71から銅箔パターン14の電源端子12を通じてICパッケージ1内に電流として供給される。すなわち、この実施例の2端子コンデンサ7も、上記第1実施例の2端子コンデンサと同様に、電源電圧を安定させるバイパスコンデンサとして機能する。

また、ICパッケージ1−1の電源端子12に生じたノイズ電流は、銅箔パターン14のランド部14aを通じて入出力端子71から2端子コンデンサ7に入力し、アース端子72から銅箔パターン15のランド部15aを通じてグランド端子13に至る。そして、かかるノイズ電流は、グランド端子13が接続された多層回路基板100のランド22を通じてグランド層3に排出される。すなわち、この2端子コンデンサ7も、発生したノイズを除去するデカップリングコンデンサとして機能する。

図25は、この発明の第6実施例の要部であるコンデンサの実装状態を示す平面図であり、図26は、この実施例のICパッケージの実装例を示す概略断面図である。なお、これらの図において、理解を容易にするため、電源層4に接続させる端子を黒塗りで示した。

この実施例は、上記第5実施例で用いた2端子コンデンサ7の代わりに、3端子コンデンサ8を用いた。

そして、3端子コンデンサ8の入力端子81,出力端子82及びアース端子83を、これら銅箔パターン14,銅箔パターン16及び銅箔パターン15に固着した。

これにより、3端子コンデンサ8の入力端子81が端子12′に接続した状態になり、出力端子82がICパッケージ1−3内部の電源パターン12′′に接続した状態になる。

かかる状態で、外部電源が、電源層4に入力されると、電源層4に接続された端子12′から入力端子81を通じて3端子コンデンサ8に充電される。そして、3端子コンデンサ8に充電された電荷が、出力端子82から銅箔パターン16を通じて、ICパッケージ1−3内部の電源パターン12′′に電流として供給される。

また、電源パターン12′′に生じたノイズ電流は、3端子コンデンサ8のアース端子83を通じてグランド端子13に至り、グランド端子13から多層回路基板100のランド22及びビアホール31を通じてグランド層3に排出される。

その他の構成、作用及び効果は、上記第3及び第5実施例と同様であるので、その記載は省略する。

例えば、上記第実施例では、ロ字状の実装スペースS1,S11や矩形状の実装スペースS2,S12を多層回路基板の信号層2やICパッケージの裏面10に設けた例を示したが、実装スペースの形状,大きさ及び個数は、上記実施例に限定されるものではないことは勿論である。

また、上記実施例では、ICパッケージの裏面10に凹部11,11′を設けた例について説明したが、これらの凹部11,11′を有しないICパッケージを有した多層回路基板やICパッケージ自体をこの発明の範囲から除外する意ではない。

Claims (14)

- 裏面にBGAタイプの端子群を有したICパッケージが表面に実装され且つ電源層とグランド層とが設けられた多層回路基板であって、

上記ICパッケージの裏面と対向するIC実装領域内に、コンデンサの実装スペースを設けて、コンデンサを当該実装スペースに配し、

当該コンデンサの電源用の電極を、上記ICパッケージの電源端子に接続すると共に上記電源層に接続し、グランド用の電極を、上記グランド層に接続した、

ことを特徴とする多層回路基板。 - 請求項1に記載の多層回路基板において、

上記コンデンサは、チップ型の2端子コンデンサであり、

上記電源用の電極は、当該2端子コンデンサの入出力端子であり、

上記グランド用の電極は、当該2端子コンデンサのアース端子である、

ことを特徴とする多層回路基板。 - 請求項1に記載の多層回路基板において、

上記コンデンサは、チップ型の3端子コンデンサであり、

上記電源用の電極は、当該3端子コンデンサの入力端子と出力端子とでなり、当該入力端子が上記電源層に接続すると共に、当該出力端子が上記電源端子に接続し、

上記グランド用の電極は、当該3端子コンデンサのアース端子である、

ことを特徴とする多層回路基板。 - 請求項1ないし請求項3のいずれかに記載の多層回路基板において、

上記コンデンサの実装スペースを、上記ICパッケージの電源端子の近傍に設けた、

ことを特徴とする多層回路基板。 - 請求項1ないし請求項4のいずれかに記載の多層回路基板において、

上記ICパッケージの裏面であって且つ上記コンデンサの実装スペースに対応する個所に、当該ICパッケージとコンデンサとの接触を回避するための凹部を形成した、

ことを特徴とする多層回路基板。 - 請求項1ないし請求項5のいずれかに記載の多層回路基板において、

上記コンデンサの実装スペースを、上記ICパッケージの裏面と対向する上記IC実装領域のほぼ中央部に設けた、

ことを特徴とする多層回路基板。 - 請求項1ないし請求項5のいずれかに記載の多層回路基板において、

上記コンデンサの実装スペースを、上記ICパッケージの裏面と対向する上記IC実装領域の周縁部に1以上設けた、

ことを特徴とする多層回路基板。 - 電源端子とグランド端子とを含むBGAタイプの端子群を裏面に有し且つ多層回路基板の表面に実装されるICパッケージであって、

上記ICパッケージの端子群内に、コンデンサの実装スペースを設けて、コンデンサを当該実装スペースに取り付け、

当該コンデンサの電源用の電極を、上記電源端子に接続すると共に、グランド用の電極を、上記グランド端子に接続した、

ことを特徴とするICパッケージ。 - 請求項8に記載のICパッケージにおいて、

上記コンデンサは、チップ型の2端子コンデンサであり、

上記電源用の電極は、当該2端子コンデンサの入出力端子であり、

上記グランド用の電極は、当該2端子コンデンサのアース端子である、

ことを特徴とするICパッケージ。 - 請求項8に記載のICパッケージにおいて、

上記コンデンサは、チップ型の3端子コンデンサであり、

上記電源用の電極は、当該3端子コンデンサの入力端子と出力端子とでなり、当該入力端子を、上記多層回路基板の電源層に接続すると共に、当該出力端子が、上記電源端子に接続し、

上記グランド用の電極は、当該3端子コンデンサのアース端子である、

ことを特徴とするICパッケージ。 - 請求項8ないし請求項10のいずれかに記載のICパッケージにおいて、

上記コンデンサの実装スペースを、上記電源端子とグランド端子の近傍に設けた、

ことを特徴とするICパッケージ。 - 請求項8ないし請求項10のいずれかに記載のICパッケージにおいて、

互いに電気的に接続された複数の電源端子と互いに電気的に接続された複数のグランド端子とを、上記コンデンサの実装スペースの周囲に配置した、

ことを特徴とするICパッケージ。 - 請求項8ないし請求項12のいずれかに記載のICパッケージにおいて、

上記コンデンサの実装スペースに対応する個所に、上記コンデンサを収納する凹部を形成した、

ことを特徴とするICパッケージ。 - 請求項8ないし請求項13のいずれかに記載のICパッケージにおいて、

上記コンデンサの実装スペースを、上記端子群内のほぼ中央部に設けた、

ことを特徴とするICパッケージ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005371530A JP4817110B2 (ja) | 2005-12-26 | 2005-12-26 | 多層回路基板及びicパッケージ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005371530A JP4817110B2 (ja) | 2005-12-26 | 2005-12-26 | 多層回路基板及びicパッケージ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2007173669A true JP2007173669A (ja) | 2007-07-05 |

| JP4817110B2 JP4817110B2 (ja) | 2011-11-16 |

Family

ID=38299795

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005371530A Expired - Fee Related JP4817110B2 (ja) | 2005-12-26 | 2005-12-26 | 多層回路基板及びicパッケージ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4817110B2 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8304854B2 (en) | 2008-11-13 | 2012-11-06 | Samsung Electro-Mechanics Co., Ltd. | Semiconductor integrated circuit chip, multilayer chip capacitor and semiconductor integrated circuit chip package |

| JPWO2010137379A1 (ja) * | 2009-05-26 | 2012-11-12 | 株式会社村田製作所 | 3端子コンデンサ及び3端子コンデンサ実装構造 |

| JP7584997B2 (ja) | 2019-11-07 | 2024-11-18 | キヤノン株式会社 | 電子モジュール及び電子機器 |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102596756B1 (ko) | 2019-10-04 | 2023-11-02 | 삼성전자주식회사 | PoP 구조의 반도체 패키지 |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6059561U (ja) * | 1983-09-29 | 1985-04-25 | 富士通株式会社 | 半導体装置 |

| JPH06302714A (ja) * | 1993-04-13 | 1994-10-28 | Matsushita Electric Ind Co Ltd | 半導体装置 |

| JPH09130031A (ja) * | 1995-10-27 | 1997-05-16 | Hitachi Ltd | 電子部品の実装方法 |

| JPH09260537A (ja) * | 1996-03-26 | 1997-10-03 | Sumitomo Kinzoku Electro Device:Kk | フリップチップセラミック基板 |

| JPH11121899A (ja) * | 1997-10-20 | 1999-04-30 | Fuji Xerox Co Ltd | 電子部品実装体および電子部品の実装方法 |

| JP2004273475A (ja) * | 2003-03-04 | 2004-09-30 | Canon Inc | 半導体装置 |

| JP2005150283A (ja) * | 2003-11-13 | 2005-06-09 | Fujitsu Ltd | Bgaパッケージ |

| JP2005340534A (ja) * | 2004-05-27 | 2005-12-08 | Kyocera Corp | 積層型配線基板および半導体装置 |

-

2005

- 2005-12-26 JP JP2005371530A patent/JP4817110B2/ja not_active Expired - Fee Related

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6059561U (ja) * | 1983-09-29 | 1985-04-25 | 富士通株式会社 | 半導体装置 |

| JPH06302714A (ja) * | 1993-04-13 | 1994-10-28 | Matsushita Electric Ind Co Ltd | 半導体装置 |

| JPH09130031A (ja) * | 1995-10-27 | 1997-05-16 | Hitachi Ltd | 電子部品の実装方法 |

| JPH09260537A (ja) * | 1996-03-26 | 1997-10-03 | Sumitomo Kinzoku Electro Device:Kk | フリップチップセラミック基板 |

| JPH11121899A (ja) * | 1997-10-20 | 1999-04-30 | Fuji Xerox Co Ltd | 電子部品実装体および電子部品の実装方法 |

| JP2004273475A (ja) * | 2003-03-04 | 2004-09-30 | Canon Inc | 半導体装置 |

| JP2005150283A (ja) * | 2003-11-13 | 2005-06-09 | Fujitsu Ltd | Bgaパッケージ |

| JP2005340534A (ja) * | 2004-05-27 | 2005-12-08 | Kyocera Corp | 積層型配線基板および半導体装置 |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8304854B2 (en) | 2008-11-13 | 2012-11-06 | Samsung Electro-Mechanics Co., Ltd. | Semiconductor integrated circuit chip, multilayer chip capacitor and semiconductor integrated circuit chip package |

| JPWO2010137379A1 (ja) * | 2009-05-26 | 2012-11-12 | 株式会社村田製作所 | 3端子コンデンサ及び3端子コンデンサ実装構造 |

| JP5534566B2 (ja) * | 2009-05-26 | 2014-07-02 | 株式会社村田製作所 | 3端子コンデンサ実装構造 |

| JP7584997B2 (ja) | 2019-11-07 | 2024-11-18 | キヤノン株式会社 | 電子モジュール及び電子機器 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4817110B2 (ja) | 2011-11-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6370010B1 (en) | Multi-layer capacitor, wiring board, and high-frequency circuit | |

| US6327134B1 (en) | Multi-layer capacitor, wiring board, and high-frequency circuit | |

| US7268419B2 (en) | Interposer containing bypass capacitors for reducing voltage noise in an IC device | |

| JP3647307B2 (ja) | プリント配線基板および電子機器 | |

| JP3337018B2 (ja) | 積層コンデンサ、配線基板、デカップリング回路および高周波回路 | |

| WO2010134335A1 (ja) | 表面実装用のデバイスおよびコンデンサー素子 | |

| JP2001167969A (ja) | 三次元搭載用多端子積層セラミックコンデンサ | |

| JP2008537843A (ja) | 内部で重なり合った調整器 | |

| WO2003032389A1 (en) | Voltage conversion module | |

| US7791896B1 (en) | Providing an embedded capacitor in a circuit board | |

| JP5124150B2 (ja) | 多層プリント配線板 | |

| JP2007305642A (ja) | 多層回路基板及び電子装置 | |

| JP5494586B2 (ja) | 電圧変換モジュール | |

| JP4807235B2 (ja) | 電子部品モジュール | |

| US20070062726A1 (en) | Embedded capacitor device having a common coupling area | |

| JP4854345B2 (ja) | コンデンサシート及び電子回路基板 | |

| JP5190811B2 (ja) | 電源モジュール | |

| US8027170B2 (en) | Substrate and electronic device using the same | |

| JP4817110B2 (ja) | 多層回路基板及びicパッケージ | |

| JP2010238826A (ja) | キャパシタ内蔵配線基板 | |

| JP6264721B2 (ja) | 多層配線基板の放熱構造 | |

| JP4893114B2 (ja) | 多層配線基板 | |

| JP5464110B2 (ja) | 電圧変換モジュール | |

| KR100910457B1 (ko) | 내장형 박막 캐패시터 | |

| JP4985852B2 (ja) | 実装型電子回路モジュール |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080910 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100827 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100831 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101101 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110808 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140909 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4817110 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110821 |

|

| LAPS | Cancellation because of no payment of annual fees |