JP2006223598A - 遊技機 - Google Patents

遊技機 Download PDFInfo

- Publication number

- JP2006223598A JP2006223598A JP2005041382A JP2005041382A JP2006223598A JP 2006223598 A JP2006223598 A JP 2006223598A JP 2005041382 A JP2005041382 A JP 2005041382A JP 2005041382 A JP2005041382 A JP 2005041382A JP 2006223598 A JP2006223598 A JP 2006223598A

- Authority

- JP

- Japan

- Prior art keywords

- data

- image

- storage means

- data block

- defective

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Abstract

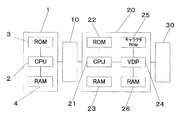

【解決手段】NAND型フラッシュメモリ29は、複数のデータブロックで構成されるとともに、前記複数のデータブロック中に不良データブロックが存在する場合、前記不良データブロックの直前のデータブロックに記憶された画像データの次の画像データが前記不良データブロックを避けた状態で前記不良データブロックの直後のデータブロックに記憶され、調停回路28は、VDP24からの画像データ読み出し要求に応じて前記不良データブロックの後のデータブロックに記憶された画像データの先頭アドレスを前記不良データブロックの前のデータブロックに記憶された画像データの最終アドレスの次のアドレスに変換して出力するようにした。

【選択図】図1

Description

20 表示制御装置

24 画像処理手段

25 画像データ記憶手段

Claims (2)

- 画像表示装置を備えた遊技機において、

前記遊技機には、前記遊技機の遊技状態を制御する主制御装置と、前記主制御装置から出力された演出制御指令信号に基づいて遊技演出を制御する副制御装置と、前記副制御装置から出力された表示制御指令信号に基づいて前記画像表示装置を制御する表示制御装置と、を備え、

前記主制御装置には、前記演出制御指令処理を行う第1の演算処理手段と、遊技制御プログラムが記憶された遊技制御プログラム記憶手段と、遊技制御データが一時記憶される遊技制御データ一時記憶手段と、を備え、

前記遊技制御プログラム記憶手段と前記遊技制御データ一時記憶手段とを前記第1の演算処理手段に接続し、

前記表示制御装置には、表示制御プログラムを実行する第2の演算処理手段と、前記表示制御プログラムが記憶された表示制御プログラム記憶手段と、表示制御用データが一時記憶される表示制御用データ一時記憶手段と、前記画像表示装置に表示される画像の制御を行う画像処理手段と、前記画像を表示するための画像データが記憶された画像データ記憶手段と、前記画像表示装置に表示される画像の表示用データが一時的に記憶される画像表示データ一時記憶手段とを備え、

前記表示制御プログラム記憶手段および前記表示制御用データ一時記憶手段と前記画像処理手段とを前記第2の演算処理手段に接続するとともに、前記画像データ記憶手段と前記画像表示データ一時記憶手段とを前記画像処理手段に接続し、

前記画像データ記憶手段には、NAND型フラッシュメモリと調停回路とを含み、

前記NAND型フラッシュメモリは、複数のデータブロックで構成されるとともに、前記複数のデータブロック中に不良データブロックが存在する場合、前記不良データブロックの直前のデータブロックに記憶された画像データの次の画像データが前記不良データブロックを避けた状態で前記不良データブロックの直後のデータブロックに記憶され、

前記調停回路は、前記画像処理手段からの画像データ読み出し要求に応じて前記不良データブロックの後のデータブロックに記憶された画像データの先頭アドレスを前記不良データブロックの前のデータブロックに記憶された画像データの最終アドレスの次のアドレスに変換して出力することを特徴とする遊技機。 - 前記画像処理手段は前記NAND型フラッシュメモリからのデータ読み出し指令制御を行うNAND型フラッシュメモリ制御回路を含み、

前記画像データ記憶手段から画像データを読み出す際には、複数種類の画像に関するデータを一括して読み出し、

前記一括して読み出した複数種類の画像データを一時記憶して画像処理を行うことを特徴とする請求項1に記載の遊技機。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005041382A JP2006223598A (ja) | 2005-02-17 | 2005-02-17 | 遊技機 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005041382A JP2006223598A (ja) | 2005-02-17 | 2005-02-17 | 遊技機 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011103979A Division JP5165081B2 (ja) | 2011-05-09 | 2011-05-09 | 遊技機 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006223598A true JP2006223598A (ja) | 2006-08-31 |

| JP2006223598A5 JP2006223598A5 (ja) | 2009-12-24 |

Family

ID=36985468

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005041382A Pending JP2006223598A (ja) | 2005-02-17 | 2005-02-17 | 遊技機 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2006223598A (ja) |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008119341A (ja) * | 2006-11-15 | 2008-05-29 | Daiman:Kk | 遊技機 |

| JP2008228955A (ja) * | 2007-03-20 | 2008-10-02 | Daiman:Kk | 遊技機 |

| JP2010137019A (ja) * | 2008-11-17 | 2010-06-24 | Sanyo Product Co Ltd | 遊技機 |

| JP2012130785A (ja) * | 2012-04-09 | 2012-07-12 | Daiichi Shokai Co Ltd | 遊技機 |

| JP2018202260A (ja) * | 2009-06-30 | 2018-12-27 | 株式会社三洋物産 | 遊技機 |

| JP2018202259A (ja) * | 2018-10-09 | 2018-12-27 | 株式会社三洋物産 | スロットマシン及び遊技機 |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08314798A (ja) * | 1995-05-17 | 1996-11-29 | Seiko Epson Corp | 半導体集積回路およびゲーム機用カートリッジ |

| JP2000268194A (ja) * | 1999-03-18 | 2000-09-29 | Airemu Software Engineering Kk | 画像表示方法およびその装置並びに遊技機 |

| JP2000330876A (ja) * | 1999-04-27 | 2000-11-30 | Samsung Electronics Co Ltd | メモリ装置のプログラム方法 |

| JP2001070590A (ja) * | 1999-09-07 | 2001-03-21 | Sankyo Kk | 遊技機 |

| JP2003047729A (ja) * | 2001-08-06 | 2003-02-18 | Daidoo:Kk | 遊技機 |

| JP2004057309A (ja) * | 2002-07-25 | 2004-02-26 | Sankyo Kk | 遊技機 |

| JP2004103162A (ja) * | 2002-09-11 | 2004-04-02 | Fujitsu Ltd | Nand型フラッシュメモリ |

| JP2004154421A (ja) * | 2002-11-07 | 2004-06-03 | Daiman:Kk | Romの異常検知装置 |

-

2005

- 2005-02-17 JP JP2005041382A patent/JP2006223598A/ja active Pending

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08314798A (ja) * | 1995-05-17 | 1996-11-29 | Seiko Epson Corp | 半導体集積回路およびゲーム機用カートリッジ |

| JP2000268194A (ja) * | 1999-03-18 | 2000-09-29 | Airemu Software Engineering Kk | 画像表示方法およびその装置並びに遊技機 |

| JP2000330876A (ja) * | 1999-04-27 | 2000-11-30 | Samsung Electronics Co Ltd | メモリ装置のプログラム方法 |

| JP2001070590A (ja) * | 1999-09-07 | 2001-03-21 | Sankyo Kk | 遊技機 |

| JP2003047729A (ja) * | 2001-08-06 | 2003-02-18 | Daidoo:Kk | 遊技機 |

| JP2004057309A (ja) * | 2002-07-25 | 2004-02-26 | Sankyo Kk | 遊技機 |

| JP2004103162A (ja) * | 2002-09-11 | 2004-04-02 | Fujitsu Ltd | Nand型フラッシュメモリ |

| JP2004154421A (ja) * | 2002-11-07 | 2004-06-03 | Daiman:Kk | Romの異常検知装置 |

Cited By (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008119341A (ja) * | 2006-11-15 | 2008-05-29 | Daiman:Kk | 遊技機 |

| JP2008228955A (ja) * | 2007-03-20 | 2008-10-02 | Daiman:Kk | 遊技機 |

| JP2010137019A (ja) * | 2008-11-17 | 2010-06-24 | Sanyo Product Co Ltd | 遊技機 |

| JP2013144211A (ja) * | 2008-11-17 | 2013-07-25 | Sanyo Product Co Ltd | 遊技機 |

| JP2015134285A (ja) * | 2008-11-17 | 2015-07-27 | 株式会社三洋物産 | 遊技機 |

| JP2021107030A (ja) * | 2008-11-17 | 2021-07-29 | 株式会社三洋物産 | 遊技機 |

| JP2018202260A (ja) * | 2009-06-30 | 2018-12-27 | 株式会社三洋物産 | 遊技機 |

| JP2012130785A (ja) * | 2012-04-09 | 2012-07-12 | Daiichi Shokai Co Ltd | 遊技機 |

| JP2018202259A (ja) * | 2018-10-09 | 2018-12-27 | 株式会社三洋物産 | スロットマシン及び遊技機 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5847971B1 (ja) | 遊技機 | |

| JP2006223598A (ja) | 遊技機 | |

| JP2009022607A (ja) | 遊技機 | |

| JP2005087542A (ja) | 遊技機 | |

| JP2012196554A (ja) | 遊技機 | |

| JP5098362B2 (ja) | 画像表示装置、および遊技機 | |

| JP5092100B2 (ja) | 遊技機用信号処理システム、遊技機 | |

| JP2010042299A (ja) | 遊技機 | |

| JP4512733B2 (ja) | 遊技機 | |

| JP2005230057A (ja) | 遊技機 | |

| JP2006223598A5 (ja) | ||

| JP5165081B2 (ja) | 遊技機 | |

| JP2004236825A (ja) | 表示制御方法、表示制御装置および遊技機 | |

| JP2021083848A5 (ja) | ||

| JP2004329650A (ja) | 遊技機用表示ユニットおよびそれを用いた遊技機 | |

| JP2005027796A (ja) | 遊技機、および、その画像表示装置 | |

| JP2005208684A (ja) | 遊技機 | |

| JP2011133651A (ja) | 設定制御装置、および設定制御装置の動作方法 | |

| JP2005237711A (ja) | 遊技機 | |

| JP4837059B2 (ja) | 遊技機 | |

| JP2008228955A (ja) | 遊技機 | |

| JP2021083909A5 (ja) | ||

| JP2021083858A5 (ja) | ||

| JP2021083912A5 (ja) | ||

| JP2008079753A (ja) | 遊技機 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080201 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20090318 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091016 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20091016 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20091019 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100922 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101026 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101224 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110308 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110509 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110816 |