JP2006173634A - ピクセルアレイを備えるcmosイメージセンサー - Google Patents

ピクセルアレイを備えるcmosイメージセンサー Download PDFInfo

- Publication number

- JP2006173634A JP2006173634A JP2005363713A JP2005363713A JP2006173634A JP 2006173634 A JP2006173634 A JP 2006173634A JP 2005363713 A JP2005363713 A JP 2005363713A JP 2005363713 A JP2005363713 A JP 2005363713A JP 2006173634 A JP2006173634 A JP 2006173634A

- Authority

- JP

- Japan

- Prior art keywords

- unit

- pixel

- pattern

- light receiving

- image sensing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/011—Manufacture or treatment of image sensors covered by group H10F39/12

- H10F39/024—Manufacture or treatment of image sensors covered by group H10F39/12 of coatings or optical elements

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/011—Manufacture or treatment of image sensors covered by group H10F39/12

- H10F39/014—Manufacture or treatment of image sensors covered by group H10F39/12 of CMOS image sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/10—Integrated devices

- H10F39/12—Image sensors

- H10F39/18—Complementary metal-oxide-semiconductor [CMOS] image sensors; Photodiode array image sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/803—Pixels having integrated switching, control, storage or amplification elements

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/805—Coatings

- H10F39/8057—Optical shielding

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/811—Interconnections

Landscapes

- Solid State Image Pick-Up Elements (AREA)

Abstract

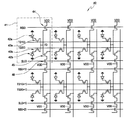

【解決手段】追加的な光遮蔽層の必要なしでピクセルアレイにかけてピクセル−ピクセルの間感度の均一度を向上させることができるように構造化された単位ピクセルを含む固体撮像CMOSアクティブピクセルセンサー素子が提供される。例えば、対称的なレイアウトパターンの単位ピクセルが形成される。一つ以上の下部レベルBEOL金属配線層が対称的にパターンされ配列されて感光領域に到達する入射光の量の均衡を合わせる光遮蔽層に動作するようにデザインされる。これにより、感光領域の露出面積を最大化してピクセル感度を増加させるだけではなく、ピクセル内の各フォトダイオードの感度を均一に維持できる。

【選択図】図7A

Description

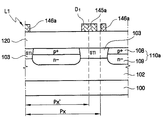

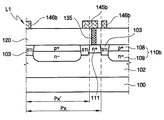

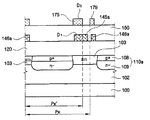

51:ピクセル

51a,51b:ピクセルユニット

110a,11b:フォトダイオード

111:ドーピング領域

131,132,133,134,135,136,137a,137b,138,139:ビア

141,142:トランスファーゲート調節ライン

143:リセットゲート調節ライン

144:行選択ゲート調節ライン

145a,145b,149:金属パッド

146a,146b:配線

C:中心線

D1:ダミー

D3,D4:突出部

L1:第1のレベル金属配線パターン

Claims (62)

- 半導体基板に形成された複数の単位ピクセルを含むピクセルアレイであって、前記各単位ピクセルは、複数の読み出し素子及び少なくとも一つの受光素子を含むピクセルアレイ;および

前記ピクセルアレイ上に形成され、前記単位ピクセル内の読み出し素子を電気的に連結する第1の配線パターンを形成する第1の配線層;

を含み、

前記第1の配線層は、前記各単位ピクセルに入射される光を遮断する光学的ブロッキングであって前記ピクセルアレイの各受光素子の感度を実質的に同一に維持することを特徴とするイメージセンシング素子。 - 前記第1の配線層上に形成され、電源電圧ラインを含む第2の配線パターンを含む第2の配線層をさらに含み、

前記第2の配線層は、前記各単位ピクセルに入射される光を遮断する光学的ブロッキングであって前記ピクセルアレイの各受光素子の感度を実質的に同一に維持することを特徴とする請求項1に記載のイメージセンシング素子。 - 前記第1の配線パターンは、前記各単位ピクセル毎に反復される第1の単位パターンを含み、

前記第2の配線パターンは、前記各単位ピクセル毎に反復される第2の単位パターンを含むことを特徴とする請求項2に記載のイメージセンシング素子。 - 前記各単位ピクセル別前記第1及び第2の単位パターンは、前記各単位ピクセル内に同一なサイズ及び形態の開口部を限定するように配列されて前記各単位ピクセルの受光領域を露出させ、

前記各単位ピクセルの受光領域は、前記単位ピクセルの受光素子を含むこと

を特徴とする請求項3に記載のイメージセンシング素子。 - 前記各ピクセルの受光領域は、前記受光素子を含むアクティブ領域に隣接した非アクティブ領域の少なくとも一部を含むことを特徴とする請求項4に記載のイメージセンシング素子。

- 前記第1の配線パターンは、ダミー突出パターンを備えるピクセル調節ラインを含むことを特徴とする請求項1に記載のイメージセンシング素子。

- 前記第2の配線パターンは、ダミー突出パターンを備えるピクセルI/Oラインを含むことを特徴とする請求項2に記載のイメージセンシング素子。

- 前記電源電圧ラインは、ダミー突出パターンを含むこと

を特徴とする請求項2に記載のイメージセンシング素子。 - 前記単位ピクセルは、共有受光素子枠組を含むことを特徴とする請求項1に記載のイメージセンシング素子。

- 前記各単位ピクセルは、第1のサブピクセルユニット及び第2のサブピクセルユニットを含む共有単位ピクセルであり、

前記第1の配線パターンは、前記ピクセルアレイの各単位ピクセル毎に反復される第1の単位パターンを含み、

前記第1の単位パターンは、前記ピクセルアレイ内の各単位ピクセルのサブピクセルユニット毎に反復され、パッドパターンを含むサブユニットパターンを含み、前記パッドパターンは、前記第1のサブピクセルユニット毎に分離されたパッドパターンであり、前記パッドパターンは、前記第2のサブピクセルユニット毎に前記第2のサブピクセルユニットの読み出し素子に連結された電気的なコンタクトパッドであることを特徴とする請求項1に記載のイメージセンシング素子。 - 前記第1及び第2のサブピクセルユニットのサブユニットパターンは、鏡像イメージパターンであること

を特徴とする請求項1に記載のイメージセンシング素子。 - 半導体基板に形成された複数の単位ピクセルを含むピクセルアレイであって、前記各単位ピクセルは、複数の読み出し素子及び少なくとも一つの受光素子を含むピクセルアレイ;および

前記ピクセルアレイ上に形成されて前記ピクセルアレイの各受光素子の感度を同一にし、読み出し素子を連結するための配線パターン及びダミーパターンを含む第1の光学的ブロッキング層;を含むことを特徴とするイメージセンシング素子。 - 前記配線及びダミーパターンは、前記各単位ピクセル毎に反復される単位パターンを含むことを特徴とする請求項12に記載のイメージセンシング素子。

- 前記ダミーパターンは、電気的に分離されたダミーパターンを含むことを特徴とする請求項12に記載のイメージセンシング素子。

- 前記ダミーパターンは、前記配線パターンに連結されたダミーパターンを含むことを特徴とする請求項12に記載のイメージセンシング素子。

- 前記ダミーパターンは、電気的に分離されたダミーパターンと前記配線パターンに連結されたダミーパターンとを含むことを特徴とする請求項12に記載のイメージセンシング素子。

- 前記ダミーパターンは、前記ピクセルアレイの素子分離領域上に整列されたことを特徴とする請求項12に記載のイメージセンシング素子。

- 前記第1の光学的ブロッキング層上に形成されて前記ピクセルアレイの各受光素子の感度を実質的に同一に維持する第2の光学的ブロッキング層をさらに含み、前記第2の光学的ブロッキング層は、電源電圧ラインを含む配線パターンを含むことを特徴とする請求項12に記載のイメージセンシング素子。

- 前記第1の光学的ブロッキング層は、前記ピクセルアレイ内の各単位ピクセル毎に反復される第1の単位パターンを含み、前記第2の光学的ブロッキング層は、前記ピクセルアレイ内の各単位ピクセル毎に反復される第2の単位パターンを含むことを特徴とする請求項18に記載のイメージセンシング素子。

- 前記各単位ピクセル別前記第1及び第2の単位パターンは、前記各単位ピクセル別前記第1及び第2の単位パターンは、前記各単位ピクセル内に同一なサイズ及び形態の開口部を限定するように配列されて前記各単位ピクセルの受光領域を露出させ、

前記各単位ピクセルの受光領域は、前記単位ピクセルの受光素子を含むアクティブ領域を含むことを特徴とする請求項19に記載のイメージセンシング素子。 - 前記各ピクセルの受光領域は、前記受光素子を含むアクティブ領域に隣接した非アクティブ領域の少なくとも一部を含むことを特徴とする請求項20に記載のイメージセンシング素子。

- 前記各単位ピクセルは、第1のサブピクセルユニット及び第2のサブピクセルユニットを含む共有単位ピクセルであり、

前記第1の光学的ブロッキング層は、前記ピクセルアレイの各単位ピクセル毎に反復される第1の単位パターンを含み、

前記第1の単位パターンは、前記ピクセルアレイ内の各単位ピクセルのサブピクセルユニット毎に反復され、パッドパターンを含むサブユニットパターンを含み、前記パッドパターンは、前記第1のサブピクセルユニット毎に分離されたパッドパターンであり、前記パッドパターンは、前記第2のサブピクセルユニット毎に前記第2のサブピクセルユニットの読み出し素子に連結された電気的なコンタクトパッドであることを特徴とする請求項12に記載のイメージセンシング素子。 - 前記第1及び第2のサブピクセルユニットのサブユニットパターンは、鏡像イメージパターンであることを特徴とする請求項22に記載のイメージセンシング素子。

- 半導体基板に形成された複数の単位ピクセルを含むピクセルアレイであって、前記各単位ピクセルは、同一レイアウトパターンを備え、前記レイアウトパターンは、受光素子領域、複数の読み出し素子領域及び前記受光素子領域及び読み出し素子領域を取り囲む素子分離領域を含むピクセルアレイ;および

前記ピクセルアレイ上に形成された第1の金属層であって、前記第1の金属層は前記ピクセルアレイ内の読み出し素子の間を連結する配線を構成する金属ラインを含む第1の金属層を含み、前記第1の金属層は前記ピクセルアレイ内の各単位ピクセル毎に反復される第1の単位パターンを含み、前記第1の単位パターンは前記各単位ピクセル毎に受光素子領域を取り囲む素子分離領域の同一な面積に配列された各単位ピクセルの光学的ブロッキング層であることを特徴とするイメージセンシング素子。 - 前記第1の単位パターンは、ダミー金属ラインであることを特徴とする請求項24に記載のイメージセンシング素子。

- 前記受光素子領域は、互いに隣接して配列された第1及び第2のフォトダイオード領域を含むことを特徴とする請求項24に記載のイメージセンシング素子。

- 前記第1の単位パターンは、鏡像イメージパターンであることを特徴とする請求項26に記載のイメージセンシング素子。

- 前記第1の金属層上に形成された第2の金属層をさらに含み、

前記第2の金属層は、単位ピクセルのI/Oラインを形成する金属ラインを含み、

前記第2の金属層は、前記ピクセルアレイ内の各単位ピクセル毎に反復される第2の単位パターンを含み、前記第2の単位パターンは、前記各単位ピクセルの受光素子を取り囲む素子分離領域の同一な面積に配列されたことを特徴とする請求項24に記載のイメージセンシング素子。 - 前記第2の単位パターンは、ダミー金属ラインを含むことを特徴とする請求項28に記載のイメージセンシング素子。

- 第2のユニットパターンは、鏡像イメージパターンを含むことを特徴とする請求項28に記載のイメージセンシング素子。

- 前記各単位ピクセルは、共有受光素子枠組を含むことを特徴とする請求項24に記載のイメージセンシング素子。

- 前記各単位ピクセルの第1及び第2のユニットパターンは、各ユニットピクセルに同一なサイズ及び形態の開口部を限定するように配列されて前記各単位ピクセルの受光領域を露出させ、

前記各単位ピクセルの受光領域は、前記単位ピクセルの受光素子を含むアクティブ領域を含むことを特徴とするイメージセンシング素子。 - 前記各ピクセルの受光領域は、前記受光素子領域を取り囲む素子分離領域の少なくとも一部を含むことを特徴とする請求項32に記載のイメージセンシング素子。

- 前記各単位ピクセルは、第1のサブピクセルユニット及び第2のサブピクセルユニットを含む共有単位ピクセルであり、

前記第1の配線パターンは、前記ピクセルアレイの各単位ピクセル毎に反復される第1の単位パターンを含み、

前記第1の単位パターンは、前記ピクセルアレイ内の各単位ピクセルのサブピクセルユニット毎に反復され、パッドパターンを含むサブユニットパターンを含み、前記パッドパターンは、前記第1のサブピクセルユニット毎に分離されたパッドパターンであり、前記パッドパターンは、前記第2のサブピクセルユニット毎に前記第2のサブピクセルユニットの読み出し素子に連結された電気的なコンタクトパッドであることを特徴とする請求項24に記載のイメージセンシング素子。 - 前記第1及び第2のサブユニットパターンは、鏡像イメージパターンであることを特徴とする請求項34に記載のイメージセンシング素子。

- 前記各第1のサブピクセルユニットは、前記分離されたダミーパッドパターンに連結されたダミーコンタクトプラグを含み、前記ダミーコンタクトプラグは、前記第2のサブピクセルユニットの読み出し素子を前記パッドパターンに連結するコンタクトプラグに対応することを特徴とする請求項34に記載のイメージセンシング素子。

- 半導体基板に形成された複数の単位ピクセルを含むピクセルアレイであって、前記各単位ピクセルは、複数の読み出し素子及び少なくとも一つの受光素子を含むピクセルアレイを形成し、

前記ピクセルアレイ上に前記単位ピクセル内の読み出し素子を電気的に連結する第1の配線パターンを形成する第1の配線層であって、前記第1の配線層は、前記各単位ピクセルに入射される光を遮断する光学的ブロッキングであって前記ピクセルアレイの各受光素子の感度を実質的に同一に維持する前記第1の配線層を形成することを含むことを特徴とするイメージセンシング素子の製造方法。 - 前記第1の配線層上に電源電圧ラインを含む第2の配線パターンを含む第2の配線層を形成することをさらに含み、前記第2の配線層は、前記各単位ピクセルに入射される光を遮断する光学的ブロッキングであって前記ピクセルアレイの各受光素子の感度を実質的に同一に維持することを特徴とする請求項37に記載のイメージセンシング素子の製造方法。

- 前記第1の配線パターンは、前記各単位ピクセル毎に反復される第1の単位パターンを含み、

前記第2の配線パターンは、前記各単位ピクセル毎に反復される第2の単位パターンを含むことを特徴とする請求項38に記載のイメージセンシング素子の製造方法。 - 前記各単位ピクセル別前記第1及び第2の単位パターンは、前記各単位ピクセル内に同一なサイズ及び形態の開口部を限定するように配列されて前記各単位ピクセルの受光領域を露出させ、

前記各単位ピクセルの受光領域は、前記単位ピクセルの受光素子を含むアクティブ領域を含むことを特徴とする請求項39に記載のイメージセンシング素子の製造方法。 - 前記各ピクセルの受光領域は、前記受光素子を含むアクティブ領域に隣接した非アクティブ領域の少なくとも一部を含むことを特徴とする請求項40に記載のイメージセンシング素子の製造方法。

- 前記第1の配線パターンは、ダミー突出パターンを備えるピクセル調節ラインを含むことを特徴とする請求項37に記載のイメージセンシング素子の製造方法。

- 前記第2の配線パターンは、ダミー突出パターンを備えるピクセルI/Oラインを含むことを特徴とする請求項38に記載のイメージセンシング素子の製造方法。

- 前記電源電圧ラインは、ダミー突出パターンを備えることを特徴とする請求項38に記載のイメージセンシング素子の製造方法。

- 前記単位ピクセルは、共有受光素子枠組を含むことを特徴とする請求項37に記載のイメージセンシング素子の製造方法。

- 前記各単位ピクセルを形成することは、第1のサブピクセルユニット及び第2のサブピクセルユニットを含む共有単位ピクセルを形成することであり、

前記第1の配線パターンは、前記ピクセルアレイの各単位ピクセル毎に反復される第1の単位パターンを含み、

前記第1の単位パターンは、前記ピクセルアレイ内の各単位ピクセルのサブピクセルユニット毎に反復され、パッドパターンを含むサブユニットパターンを含み、前記パッドパターンは、前記第1のサブピクセルユニット毎に分離されたパッドパターンであり、前記パッドパターンは、前記第2のサブピクセルユニット毎に前記第2のサブピクセルユニットの読み出し素子に連結された電気的なコンタクトパッドであることを特徴とする請求項37に記載のイメージセンシング素子の製造方法。 - 前記第1及び第2のサブピクセルユニットのサブユニットパターンは、鏡像イメージパターンであることを特徴とする請求項46に記載のイメージセンシング素子の製造方法。

- 半導体基板に形成された複数の単位ピクセルを含むピクセルアレイであって、前記各単位ピクセルは、複数の読み出し素子及び少なくとも一つの受光素子を含むピクセルアレイを形成し、

前記ピクセルアレイ上に前記ピクセルアレイの各受光素子の感度を同一にし、読み出し素子を連結するための配線パターン及びダミーパターンを含む第1の光学的ブロッキング層を形成することを特徴とするイメージセンシング素子の製造方法。 - 前記配線及びダミーパターンは、前記各単位ピクセル毎に反復される単位パターンを含むことを特徴とする請求項48に記載のイメージセンシング素子の製造方法。

- 前記ダミーパターンは、電気的に分離されたダミーパターンを含むことを特徴とする請求項48に記載のイメージセンシング素子の製造方法。

- 前記ダミーパターンは、前記配線パターンに連結されたダミーパターンを含むことを特徴とする請求項48に記載のイメージセンシング素子の製造方法。

- 前記ダミーパターンは、電気的に分離されたダミーパターンと前記配線パターンに連結されたダミーパターンとを含むことを特徴とする請求項48に記載のイメージセンシング素子の製造方法。

- 前記ダミーパターンは、前記ピクセルアレイの素子分離領域上に整列されたことを特徴とする請求項48に記載のイメージセンシング素子の製造方法。

- 前記第1の光学的ブロッキング層上に前記ピクセルアレイの各受光素子の感度を実質的に同一に維持する第2の光学的ブロッキング層をさらに形成し、前記第2の光学的ブロッキング層は、電源電圧ラインを含む配線パターンを含むことを特徴とする請求項48に記載のイメージセンシング素子の製造方法。

- 前記第1の光学的ブロッキング層は、前記ピクセルアレイ内の各単位ピクセル毎に反復される第1の単位パターンを含み、前記第2の光学的ブロッキング層は、前記ピクセルアレイ内の各単位ピクセル毎に反復される第2の単位パターンを含むことを特徴とする請求項54に記載のイメージセンシング素子の製造方法。

- 前記各単位ピクセル別前記第1及び第2の単位パターンは、前記各単位ピクセル別前記第1及び第2の単位パターンが前記各単位ピクセル内に同一なサイズ及び形態の開口部を限定するように配列して、前記各単位ピクセルの受光領域を露出させ、前記各単位ピクセルの受光領域は、前記単位ピクセルの受光素子を含むアクティブ領域を含むことを特徴とする請求項55に記載のイメージセンシング素子の製造方法。

- 前記各単位ピクセルを形成することは、第1のサブピクセルユニット及び第2のサブピクセルユニットを含む共有単位ピクセルを形成することであり、

前記第1の光学的ブロッキング層は、前記ピクセルアレイの各単位ピクセル毎に反復される第1の単位パターンを含み、

前記第1の単位パターンは、前記ピクセルアレイ内の各単位ピクセルのサブピクセルユニット毎に反復され、パッドパターンを含むサブユニットパターンを含み、前記パッドパターンは、前記第1のサブピクセルユニット毎に分離されたパッドパターンであり、前記パッドパターンは、前記第2のサブピクセルユニット毎に前記第2のサブピクセルユニットの読み出し素子に連結された電気的なコンタクトパッドであることを特徴とする請求項48に記載のイメージセンシング素子の製造方法。 - 前記第1及び第2のサブピクセルユニットのサブユニットパターンは、鏡像イメージパターンであることを特徴とする請求項57に記載のイメージセンシング素子の製造方法。

- 半導体基板に複数の単位ピクセルを含むピクセルアレイを形成し、前記各単位ピクセルは、同一レイアウトパターンを備え、前記レイアウトパターンは、受光素子領域、複数の読み出し素子領域及び前記受光素子領域及び読み出し素子領域を取り囲む素子分離領域を含むピクセルアレイを形成し、

前記ピクセルアレイ上に前記ピクセルアレイ内の読み出し素子の間を連結する配線を構成する金属ラインを含む第1の金属層を形成することを含み、

前記第1の金属層は前記ピクセルアレイ内の各単位ピクセル毎に反復される第1の単位パターンを含み、前記第1の単位パターンは前記各単位ピクセル毎に受光素子領域を取り囲む素子分離領域の同一な面積に配列された各単位ピクセルの光学的ブロッキング層であることを特徴とするイメージセンシング素子の製造方法。 - 前記各単位ピクセルを形成することは、第1のサブピクセルユニット及び第2のサブピクセルユニットを含む共有単位ピクセルを形成することであり、

前記第1の配線パターンは、前記ピクセルアレイの各単位ピクセル毎に反復される第1の単位パターンを含み、

前記第1の単位パターンは、前記ピクセルアレイ内の各単位ピクセルのサブピクセルユニット毎に反復され、パッドパターンを含むサブユニットパターンを含み、前記パッドパターンは、前記第1のサブピクセルユニット毎に分離されたパッドパターンであり、前記パッドパターンは、前記第2のサブピクセルユニット毎に前記第2のサブピクセルユニットの読み出し素子に連結された電気的なコンタクトパッドであることを特徴とする請求項59に記載のイメージセンシング素子の製造方法。 - 前記第1及び第2のサブユニットパターンは、鏡像イメージパターンであることを特徴とする請求項60に記載のイメージセンシング素子の製造方法。

- 前記各第1のサブピクセルユニットは、前記分離されたダミーパッドパターンに連結されたダミーコンタクトプラグを含み、前記ダミーコンタクトプラグは、前記第2のサブピクセルユニットの読み出し素子を前記パッドパターンに連結するコンタクトプラグに対応することを特徴とする請求項60に記載のイメージセンシング素子の製造方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020040107181A KR100690880B1 (ko) | 2004-12-16 | 2004-12-16 | 픽셀별 광감도가 균일한 이미지 센서 및 그 제조 방법 |

| US11/264,437 US7710477B2 (en) | 2004-12-16 | 2005-11-01 | CMOS image sensors having pixel arrays with uniform light sensitivity |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006173634A true JP2006173634A (ja) | 2006-06-29 |

| JP2006173634A5 JP2006173634A5 (ja) | 2009-02-05 |

Family

ID=36673962

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005363713A Pending JP2006173634A (ja) | 2004-12-16 | 2005-12-16 | ピクセルアレイを備えるcmosイメージセンサー |

Country Status (3)

| Country | Link |

|---|---|

| JP (1) | JP2006173634A (ja) |

| DE (1) | DE102005060518B4 (ja) |

| TW (1) | TWI282621B (ja) |

Cited By (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008235748A (ja) * | 2007-03-23 | 2008-10-02 | Seiko Epson Corp | 固体撮像装置 |

| JP2010067774A (ja) * | 2008-09-10 | 2010-03-25 | Canon Inc | 光電変換装置及び撮像システム |

| JP2012199583A (ja) * | 2005-09-12 | 2012-10-18 | Intellectual Venturesii Llc | 光干渉を減少させたイメージセンサ |

| JP2012212940A (ja) * | 2012-07-26 | 2012-11-01 | Canon Inc | 光電変換装置および光電変換装置を用いた撮像システム |

| US8415602B2 (en) | 2008-11-25 | 2013-04-09 | Sony Corporation | Solid-state imaging device and electronic apparatus having an element isolator in a semiconductor substrate |

| JP2013089880A (ja) * | 2011-10-20 | 2013-05-13 | Canon Inc | 固体撮像装置およびカメラ |

| US8638379B2 (en) | 2008-12-22 | 2014-01-28 | Sony Corporation | Solid-state image pickup device with shared amplifier nearest pixel corresponding to shortest light wavelength and electronic apparatus using the same |

| JP2015527570A (ja) * | 2012-06-20 | 2015-09-17 | コーニンクレッカ フィリップス エヌ ヴェ | X線検出器のピクセルレイアウト |

| US9900530B2 (en) | 2014-12-15 | 2018-02-20 | Canon Kabushiki Kaisha | Image sensing system |

| JP2020077879A (ja) * | 2010-08-27 | 2020-05-21 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| KR20200119672A (ko) * | 2019-04-10 | 2020-10-20 | 삼성전자주식회사 | 공유 픽셀들을 포함하는 이미지 센서 |

| CN112038379A (zh) * | 2019-11-27 | 2020-12-04 | 友达光电股份有限公司 | 像素阵列基板 |

| CN113410176A (zh) * | 2020-03-16 | 2021-09-17 | 合肥晶合集成电路股份有限公司 | Oled器件及其制造方法 |

| JP2021528653A (ja) * | 2018-06-29 | 2021-10-21 | オスラム オプト セミコンダクターズ ゲゼルシャフト ミット ベシュレンクテル ハフツングOsram Opto Semiconductors GmbH | 周囲光検出器、検出器アレイ、および方法 |

| JP2023099593A (ja) * | 2017-12-13 | 2023-07-13 | パナソニックIpマネジメント株式会社 | 撮像装置 |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9235285B2 (en) | 2013-05-13 | 2016-01-12 | Himax Technologies Limited | Pixel matrix, touch display device and drving method thereof |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH1140539A (ja) * | 1997-07-18 | 1999-02-12 | Mitsuteru Kimura | フローティング部を有する半導体装置及びフローティング単結晶薄膜の形成方法 |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000124438A (ja) * | 1998-10-19 | 2000-04-28 | Toshiba Corp | 固体撮像装置 |

| JP2004104203A (ja) * | 2002-09-05 | 2004-04-02 | Toshiba Corp | 固体撮像装置 |

-

2005

- 2005-12-12 DE DE102005060518.4A patent/DE102005060518B4/de active Active

- 2005-12-16 JP JP2005363713A patent/JP2006173634A/ja active Pending

- 2005-12-16 TW TW094144658A patent/TWI282621B/zh active

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH1140539A (ja) * | 1997-07-18 | 1999-02-12 | Mitsuteru Kimura | フローティング部を有する半導体装置及びフローティング単結晶薄膜の形成方法 |

Cited By (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8698266B2 (en) | 2005-09-12 | 2014-04-15 | Intellectual Ventures Ii Llc | Image sensor with decreased optical interference between adjacent pixels |

| JP2012199583A (ja) * | 2005-09-12 | 2012-10-18 | Intellectual Venturesii Llc | 光干渉を減少させたイメージセンサ |

| JP2008235748A (ja) * | 2007-03-23 | 2008-10-02 | Seiko Epson Corp | 固体撮像装置 |

| JP2010067774A (ja) * | 2008-09-10 | 2010-03-25 | Canon Inc | 光電変換装置及び撮像システム |

| US8415602B2 (en) | 2008-11-25 | 2013-04-09 | Sony Corporation | Solid-state imaging device and electronic apparatus having an element isolator in a semiconductor substrate |

| US8638379B2 (en) | 2008-12-22 | 2014-01-28 | Sony Corporation | Solid-state image pickup device with shared amplifier nearest pixel corresponding to shortest light wavelength and electronic apparatus using the same |

| JP2020077879A (ja) * | 2010-08-27 | 2020-05-21 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2013089880A (ja) * | 2011-10-20 | 2013-05-13 | Canon Inc | 固体撮像装置およびカメラ |

| JP2015527570A (ja) * | 2012-06-20 | 2015-09-17 | コーニンクレッカ フィリップス エヌ ヴェ | X線検出器のピクセルレイアウト |

| JP2012212940A (ja) * | 2012-07-26 | 2012-11-01 | Canon Inc | 光電変換装置および光電変換装置を用いた撮像システム |

| US9900530B2 (en) | 2014-12-15 | 2018-02-20 | Canon Kabushiki Kaisha | Image sensing system |

| JP7641546B2 (ja) | 2017-12-13 | 2025-03-07 | パナソニックIpマネジメント株式会社 | 撮像装置 |

| JP2023099593A (ja) * | 2017-12-13 | 2023-07-13 | パナソニックIpマネジメント株式会社 | 撮像装置 |

| JP2021528653A (ja) * | 2018-06-29 | 2021-10-21 | オスラム オプト セミコンダクターズ ゲゼルシャフト ミット ベシュレンクテル ハフツングOsram Opto Semiconductors GmbH | 周囲光検出器、検出器アレイ、および方法 |

| JP7186247B2 (ja) | 2018-06-29 | 2022-12-08 | エイエムエス-オスラム インターナショナル ゲーエムベーハー | 周囲光検出器、検出器アレイ、および方法 |

| KR102609559B1 (ko) | 2019-04-10 | 2023-12-04 | 삼성전자주식회사 | 공유 픽셀들을 포함하는 이미지 센서 |

| KR20200119672A (ko) * | 2019-04-10 | 2020-10-20 | 삼성전자주식회사 | 공유 픽셀들을 포함하는 이미지 센서 |

| US12328961B2 (en) | 2019-04-10 | 2025-06-10 | Samsung Electronics Co., Ltd. | Image sensor including shared pixels |

| CN112038379B (zh) * | 2019-11-27 | 2023-06-30 | 友达光电股份有限公司 | 像素阵列基板 |

| CN112038379A (zh) * | 2019-11-27 | 2020-12-04 | 友达光电股份有限公司 | 像素阵列基板 |

| CN113410176A (zh) * | 2020-03-16 | 2021-09-17 | 合肥晶合集成电路股份有限公司 | Oled器件及其制造方法 |

| CN113410176B (zh) * | 2020-03-16 | 2023-10-27 | 合肥晶合集成电路股份有限公司 | Oled器件及其制造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| TWI282621B (en) | 2007-06-11 |

| DE102005060518B4 (de) | 2015-02-19 |

| DE102005060518A1 (de) | 2006-08-03 |

| TW200627637A (en) | 2006-08-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7710477B2 (en) | CMOS image sensors having pixel arrays with uniform light sensitivity | |

| US7535037B2 (en) | Solid state image sensor devices having non-planar transistors | |

| JP3759435B2 (ja) | X−yアドレス型固体撮像素子 | |

| JP3722367B2 (ja) | 固体撮像素子の製造方法 | |

| US7498650B2 (en) | Backside illuminated CMOS image sensor with pinned photodiode | |

| KR100278285B1 (ko) | 씨모스 이미지센서 및 그 제조방법 | |

| US20080170149A1 (en) | Solid-state imager and solid-state imaging device | |

| JP5361110B2 (ja) | 非平面トランジスタを有する固体イメージセンサ素子及びその製造方法 | |

| JP2012094719A (ja) | 固体撮像装置、固体撮像装置の製造方法、及び電子機器 | |

| JP2000312024A (ja) | 受光素子及びそれを有する光電変換装置 | |

| JP2006173634A (ja) | ピクセルアレイを備えるcmosイメージセンサー | |

| JP2008546215A (ja) | 延長した埋込コンタクトを用いた、イメージャのクロストークおよび画素ノイズの低減 | |

| JP4124190B2 (ja) | X−yアドレス型固体撮像素子 | |

| JP4987749B2 (ja) | 固体撮像素子の製造方法 | |

| JP2000091550A (ja) | 固体撮像装置およびその製造方法 | |

| JP5534081B2 (ja) | 固体撮像素子の製造方法 | |

| JP4987748B2 (ja) | X−yアドレス型固体撮像素子 | |

| JP5316667B2 (ja) | 固体撮像素子の製造方法 | |

| JP5252100B2 (ja) | 固体撮像素子 | |

| JP2012099843A (ja) | 固体撮像素子 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081216 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20081216 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120321 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120611 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120626 |