JP2006032729A - 不揮発性メモリとその製造方法 - Google Patents

不揮発性メモリとその製造方法 Download PDFInfo

- Publication number

- JP2006032729A JP2006032729A JP2004210641A JP2004210641A JP2006032729A JP 2006032729 A JP2006032729 A JP 2006032729A JP 2004210641 A JP2004210641 A JP 2004210641A JP 2004210641 A JP2004210641 A JP 2004210641A JP 2006032729 A JP2006032729 A JP 2006032729A

- Authority

- JP

- Japan

- Prior art keywords

- metal oxide

- electrodes

- electrode

- electric field

- state

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Abstract

【課題】 対向する電極間に電気抵抗値が変化する金属酸化物を設け、低消費電力で駆動する低コスト、大記憶容量の低クロストークの特に携帯用機器のメモリとして最適な不揮発性メモリとその製造方法を提供する。

【解決手段】 本発明の不揮発性メモリの製造方法は、対向する電極間に未結晶状態又は不完全な結晶化状態の金属酸化物を設け、前記電極間に高電界エネルギーを印加することにより、発生するジュール熱のエネルギーによって結晶化した金属酸化物からなるメモリ・セル(メモリ領域)を形成する。

【選択図】 図3

【解決手段】 本発明の不揮発性メモリの製造方法は、対向する電極間に未結晶状態又は不完全な結晶化状態の金属酸化物を設け、前記電極間に高電界エネルギーを印加することにより、発生するジュール熱のエネルギーによって結晶化した金属酸化物からなるメモリ・セル(メモリ領域)を形成する。

【選択図】 図3

Description

本発明は、特に、ゾル−ゲル法や有機金属分解法(MOD)により作製された金属酸化物を用いた不揮発性メモリとその製造方法に関する。

近年、高度情報化社会の急激な進展により、高速、大容量の情報に関するデータを扱う機器やシステムが必要となってきている。そして、そのデータを高速で保存するための素子として、不揮発性のメモリが注目されている。

前記不揮発性メモリとして、フラッシュメモリや強誘電体メモリ(以下、FRAMと称す)が既に市場に投入され、携帯電話機やデジタルカメラ(以下、DSCと称す)等のメモリカードに使用されている。そして、その1MBバイト当りの単価は既に0.15米ドルを切り、年率2倍の大容量化と低コスト化が実現されてきている。なお、これまでメモリカードは、デジタルオーディオプレーヤ等の携帯型オーディオ機器やDSC向けのデータ格納用の記録媒体として使用され、その市場が拡大してきた。

そして、最近では、例えば、DVDレコーダでテレビジョン放送番組を録画した画像信号をメモリカードに記録し、そのメモリカードを携帯電話機や携帯型情報機器等に装着してこれらの機器に備えられた表示部で画像再生する、というようにメモリカードが機器間でのデータ交換に用いるブリッジ媒体として多く使用されるようになってきており、これは有線や無線のネットワークを代替するもので、ネットワークを使う場合と比較して、ユーザがより直接媒体としてリアルな操作で扱え、携帯電話機等の有料ネットワークを使用してデータを送受信する場合に比べてランニングコストが安価であるという利点がある。

更に、データ格納用メモリだけではなく、アプリケーション・ソフトウェアやハードウェアの機能を搭載したメモリカードの開発も検討されつつあり、このようなメモリカードが商品化されるとメモリやソフトウェアばかりか、ハードウェアも機器に搭載しておく必要がなくなり、機器の小型、軽量、薄型化が可能になる。

このような背景から、不揮発性メモリには、更なるビットコストの低減化(大容量化、低コスト化)、及び高速化が求められている。

ここで、特許文献1にはクロスポイントメモリ構造を有する不揮発性メモリが開示されている。この特許文献1に開示のものは、基板上に設けられた複数の下部電極と、該下部電極と直交して、その下部電極上に設けられた複数の上部電極との間に外部影響(特に電気的パルス)により電気的抵抗特性が変化するペロブスカイト材料を設けた不揮発性メモリであり、クロストークを低減したクロスポイントメモリ構造を有する不揮発性メモリである。

以下に、図11を用いてこのクロスポイントメモリ構造を有する不揮発性メモリについて説明する。

図11において、基板121上に形成された下部電極122と直交して、上部電極123が配置されており、この下部電極122と上部電極123との間にペロブスカイト材料からなるメモリビット124が形成されている。前記メモリビット124は下部電極122と上部電極123が交差するすべての場所に形成されている。また、前記メモリビット124の間には酸化物からなる絶縁材料125が形成されている。

このクロスポイントメモリ構造を有する不揮発性メモリの製造方法は、以下の(a)〜(g)の工程で製造される。

(a)半導体基板を提供する工程

(b)複数の下部電極を形成する工程

(c)下部電極上に酸化物絶縁材料を形成する工程

(d)下部電極に対する開口部をエッチングする工程

(e)下部電極及び酸化物絶縁材料の上にペロブスカイト材料の層を形成する工程

(f)ペロブスカイト材料の層を研磨し、ペロブスカイト材料を開口部に残し、メモリビットを形成する工程

(g)ペロブスカイト材料の層上に複数の上部電極を形成する工程

(b)複数の下部電極を形成する工程

(c)下部電極上に酸化物絶縁材料を形成する工程

(d)下部電極に対する開口部をエッチングする工程

(e)下部電極及び酸化物絶縁材料の上にペロブスカイト材料の層を形成する工程

(f)ペロブスカイト材料の層を研磨し、ペロブスカイト材料を開口部に残し、メモリビットを形成する工程

(g)ペロブスカイト材料の層上に複数の上部電極を形成する工程

一方、ペロブスカイト材料等の金属酸化物の薄膜を形成する方法として、従来より、真空蒸着法、スパッタリング法、分子線エピタキシャル成長法(MBE)、クラスターイオンビーム法(ICB)、レーザアブレーション法等の真空中で行う物理堆積法(PVD)、気相化学輸送法、有機金属堆積輸送法(MOCVD)、プラズマCVD法、金属気相化学反応法等の気相化学堆積法(CVD)、及び融液、溶液を用いる液相エピタキシャル法(LPE)、印刷焼結法、ゾル−ゲル法、有機金属分解法(MOD)、スプレー法等の液体塗布焼結法が実用化されている。

これら各々の方法については、いくつかの問題点がある。例えば、真空蒸着法等の物理堆積法(PVD)は、製造系全体を10-2Pa以下の高真空に保つ必要があり、また、蒸発源から飛来する蒸発粒子に指向性があるために、薄膜形成される材料の大きさや形状に制限がある。さらに、化学堆積法(CVD)もPVD法と同様に通常は真空環境で製造するため、減圧する必要があり、又、製造する金属酸化物の種類によっては人体に危険な有毒ガスを使用する場合もある。

一方、液相薄膜形成法である液体塗布焼結法は、上述したPVD法やCVD法等の気相薄膜製造法のように制約の多い特殊な真空設備を必要とすることなく、大気中で簡単に薄膜を形成することができるため、経済的であり、また、凸凹の複雑な形状でも成膜が可能であるという特徴を有する。そして、この液体塗布焼結法の一種であるゾル−ゲル法や有機金属分解法(MOD)は比較的低温において、大面積にわたって均一で良質の金属酸化物薄膜を短時間で形成することができる。

特開2003−68983号公報

しかしながら、従来のクロスポイントメモリ構造を有する不揮発性メモリは、クロストークを低減させるために、下部電極と上部電極が交差する位置にのみメモリビットを配置させる必要があり、このため下部電極上に酸化物絶縁材料を形成する工程、下部電極に対する開口部をエッチングする工程、及びペロブスカイト材料の層を研磨し、ペロブスカイト材料を開口部に残し、メモリビットを形成する工程等の煩雑な製造工程を必要とし、このため製造コストが高くなり、ビットコストを下げることが困難であった。

本発明は、低消費電力で駆動する低コスト、大記憶容量の低クロストークの不揮発性メモリとこれを簡単に製造することができる製造方法を提供することにある。

本発明の不揮発性メモリの製造方法は、未結晶状態又は不完全な結晶化状態の金属酸化物に高電界エネルギーを印加することにより、その未結晶状態又は不完全な結晶化状態の金属酸化物を結晶化することを特徴とするものであり、具体的には基板の上に配置された下部電極と前記下部電極に対向して配置された上部電極との間に未結晶状態又は不完全な結晶化状態の金属酸化物を設け、前記下部電極と上部電極の間に高電界エネルギーを印加することにより、前記金属酸化物を結晶化することを特徴とする。

又、本発明の不揮発性メモリの製造方法は、基板の上に略同一平面内で間隔をおいて平行に配置された複数の下部電極と、この下部電極と概ね直交し、かつ対向する複数の上部電極との間に、未結晶状態又は不完全な結晶化状態の金属酸化物を設け、前記下部電極と上部電極の間に高電界エネルギーを印加することにより、前記金属酸化物を結晶化することを特徴とする。

さらに、本発明の不揮発性メモリの製造方法は、基板の上に略同一平面内で間隔をおいて平行に複数の第1の電極を配置し、前記第1の電極の上に未結晶状態又は不完全な結晶化状態の第1の金属酸化物を設け、前記第1の金属酸化物の上に前記第1の複数の電極と概ね直交し、かつ対向する複数の第2の電極を配置し、前記第2の電極の上に未結晶状態又は不完全な結晶化状態の第2の金属酸化物を設け、前記第2の金属酸化物の上に前記第2の複数の電極と概ね直交し、かつ対向する複数の第3の電極を配置し、前記第1の電極と第2の電極の間及び第2の電極と第3の電極の間に高電界エネルギーを印加することにより、前記第1及び第2の金属酸化物を結晶化し、複数段の不揮発性メモリを製造することを特徴とする。

又、本発明は、未結晶状態又は不完全な結晶化状態の金属酸化物は有機金属化合物、金属アルコキシド、又は有機酸塩と有機溶剤を混合したゾル−ゲル液からなる塗膜であることを特徴とする。

又、本発明は、対向する電極間への高電界エネルギーの印加によりその対向する電極の少なくとも一方の電極に設けた電界集中部からの電界によるジュール熱によって未結晶状態又は不完全な結晶化状態の金属酸化物を結晶化することを特徴とする。

さらに、本発明は、未結晶状態又は不完全な結晶化状態の金属酸化物の結晶化は、対向する電極の少なくとも一方の電極に設けた突起からなる電界集中部からの電界によるジュール熱によって行うようにしたことを特徴とする。

又、本発明は、未結晶状態又は不完全な結晶化状態の金属酸化物の結晶化は、電極自体の断面形状を台形、三角形、矩形、多角形、略半円形、略半楕円形、又はこれらの形状の組み合わせあるいは合成した電界集中部からの電界によるジュール熱によって行うようにしたことを特徴とする。

又、本発明は、金属酸化物の未結晶化部分を有機溶剤で除去することを特徴とする。

又、本発明は、対向する電極間に、高電界エネルギーの印加によるジュール熱により結晶化した金属酸化物からなるメモリ・セルを設けた不揮発性メモリである。

又、本発明の不揮発性メモリに用いる金属酸化物は可変抵抗材料であることが好ましい。

本発明に係る不揮発性メモリの製造方法によれば、金属酸化物の未結晶状態又は不完全な結晶化状態で、対向する電極間に高電界エネルギーを印加することにより、そこに発生するジュール熱のエネルギーによって金属酸化物を結晶化し、メモリ・セル(メモリ領域)を形成するようにしたため、低クロストークで大記憶容量の不揮発性メモリの生産コストが安価になり、従って、ビットコストが低減するという効果を有する。さらに、この製造方法により製造された不揮発性メモリは、低消費電力駆動が可能であるという効果が得られる。

以下、本発明の実施の形態に係る不揮発性メモリについて、図面を用いて説明する。

(実施の形態1)

図1は、本発明の実施の形態1に係る不揮発性メモリ10の構成を示す断面図であり、図2は、その製造途中の不揮発性メモリの構成を示す断面図である。

図1は、本発明の実施の形態1に係る不揮発性メモリ10の構成を示す断面図であり、図2は、その製造途中の不揮発性メモリの構成を示す断面図である。

まず、図1に示すように、シリコン、又は表面がシリコン酸化物で被覆されたシリコン等の基板11の上に、下部電極12が配置され、その上に電気的手段により電気抵抗値が変化する金属酸化物(可変抵抗材料)からなるメモリ・セル13が形成され、更にその上に上部電極14が設けられている。前記下部電極12と上部電極14の中央部には互いの先端平面が対面する円錐台形状(断面形状が台形)の突起12a、14aが一体に設けられており、前記金属酸化物からなるメモリ・セル13はこの突起12a、14aの対面する先端平面部分に接触した状態で形成されている。

前記突起12a、14aは電極12、14と同質材料であっても異質材料であってもよく、電極12、14の形成材料によりその形成と同時に設けてもよく、或いは電極12、14とは別に設けて一体化してもよい。

そして、前記下部電極12と上部電極14は、ワード線又はビット線と接続されるが、その電極自体がワード線又はビット線で形成されるようにしてもよい。なお、下部電極12がワード線自体であるかワード線と接続される場合は、上部電極14がビット線自体であるかビット線と接続される。その逆の場合は、下部電極12がビット線自体であるかビット線と接続され、上部電極14がワード線自体であるかワード線と接続される。

上記不揮発性メモリ10の製造は、図2に示すように、まずシリコン、又は表面がシリコン酸化物で被覆されたシリコン等の基板11の上にスパッタリング法や真空蒸着法等の薄膜形成方法あるいは印刷法等により下部電極12とともに突起12aを形成し、その上に、有機金属化合物、金属アルコキシド、又は有機酸塩と有機溶剤を混合したゾル−ゲル液を滴下し、これをスピンコーティング法又はディップコーティング法で塗膜23を形成する。そして、この塗膜23を100〜400℃の温度で乾燥又は仮焼して溶媒を除去する。前記塗布後の塗膜23を乾燥又は仮焼して得られた薄膜は構成元素が単に混ざり合っただけのもので、未結晶状態又は不完全な結晶化状態であり、結晶化した金属酸化物にはなっていない。

その後、前記塗膜23の上面に前記突起14aの形状に対応する逆台形状の凹部を切削等の方法により形成し、この凹部が形成された状態で塗膜23上に前記下部電極12と同様の方法により突起12aと塗膜23を介して対面する突起14aとともに上部電極14を形成する。そして、下部電極12と上部電極14の間に高電界エネルギーを印加すると、図2に破線で示すように下部電極12と上部電極14の突起12a、14aの先端平面部分に電界25が集中する。この突起12a、14aからなる電界集中部における電界25によってジュール熱が発生し、その熱によって塗膜23に化学反応と結晶化を促進させ、結晶化した金属酸化物を形成する。この金属酸化物の結晶化される領域は電界25の分布形状に倣う。

前記のように、下部電極12と上部電極14の間に電界25の分布形状を反映した部分のみ結晶化した金属酸化物が生成され、その後未結晶化部分を有機溶剤で除去することにより、図1に示すように突起12a、14aの対面する先端平面部分に接触した金属酸化物からなるメモリ・セル13を形成することができる。なお、前記未結晶化部分を除去する有機溶剤は、前記ゾル−ゲル液に用いた有機溶剤と同じものであることが好ましい。

上記のようにして製造された不揮発性メモリ10の両電極間に電気的手段により電圧パルスあるいは電流パルス等を印加することにより、電極の突起部分12a、14aと接触しているメモリ・セル13の電気抵抗値を変化させ、その高抵抗状態を論理“0”に、低抵抗状態を論理“1”に関連付けることによってデジタル情報を保存することができる。

上記の不揮発性メモリ10は、電極の突起12a、14a部分にのみ接触して金属酸化物からなるメモリ・セル13を設けているため、電極間に電界を印加すると、その突起部分に電界が集中し、メモリ・セル13を低消費電力で駆動させることが可能となる。

(実施の形態2)

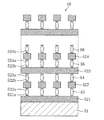

次に、本発明の実施の形態2に係るクロスポイントメモリ構造を有する不揮発性メモリについて図3及び図4を用いて説明する。図3は実施の形態2に係る不揮発性メモリ30の構成を示す断面図であり、図4はその製造途中の不揮発性メモリの構成を示す断面図である。

次に、本発明の実施の形態2に係るクロスポイントメモリ構造を有する不揮発性メモリについて図3及び図4を用いて説明する。図3は実施の形態2に係る不揮発性メモリ30の構成を示す断面図であり、図4はその製造途中の不揮発性メモリの構成を示す断面図である。

この不揮発性メモリ30は、シリコン、又は表面がシリコン酸化物で被覆されたシリコン等の基板31の上に、略同一平面内で間隔をおいて平行に、複数の下部電極32が配置され、その複数の下部電極32の上方に略同一平面内で間隔をおいて平行に配置した複数の上部電極34を設け、前記複数の下部電極32と複数の上部電極34は、概ね互いに直交して配置されている。そして互いに交差する領域の中央部にはそれぞれ互いの先端面が対面する断面形状が台形の突起32a、34aが設けられている。金属酸化物からなるメモリ・セル33は前記各突起32a、34aの対面する先端平面部分に接触した状態で形成されている。

前記各突起32a、34aは電極32、34と同質材料であっても、異質材料であってもよく、電極32、34の形成時にその材料で同時に形成してもよく、或いは電極32、34とは別に設けて一体化してもよい。

そして、前記下部電極32と上部電極34は、上記実施の形態1と同様に、ワード線又はビット線と接続されるが、その電極自体がワード線又はビット線で形成されるようにしてもよい。なお、下部電極32がワード線自体で形成されているかワード線と接続される場合は、上部電極34がビット線自体で形成されるかビット線と接続される。その逆の場合は、下部電極32がビット線自体で形成されるかビット線と接続され、上部電極34がワード線自体で形成されるかワード線と接続される。

上記不揮発性メモリ30の製造は、図4に示すように、シリコン、又は表面がシリコン酸化物で被覆されたシリコン等の基板31の上に、略同一平面内で間隔をおいて平行に複数の下部電極32とともに各突起32aを形成し、その上に有機金属化合物、金属アルコキシド、又は有機酸塩と有機溶剤を混合したゾル−ゲル液を滴下してスピンコーティング法又はディップコーティング法で塗膜43を形成し、そして前記塗膜43を100〜400℃の温度で乾燥又は仮焼することにより溶媒を除去する。前記塗膜43を乾燥又は仮焼して得られた薄膜は、構成元素が単に混ざり合っただけのもので、未結晶状態又は不完全な結晶化状態であり、結晶化した金属酸化物にはなっていない。

その後、前記塗膜43の上面に突起34aの形状と対応する形状の凹部を形成し、この凹部を形成後、塗膜43上に下部電極32と概ね互いに直交して、複数の上部電極34と突起34aを形成する。なお、各電極及び凹部、各突起の形成は上記実施の形態1で説明した方法と同様の方法により形成される。

そして、下部電極32と上部電極34の間に高電界エネルギーを印加すると、図4に破線で示すように下部電極32と上部電極34の各突起32a、34aの先端平面部分に電界45が集中する。この各突起32a、34aからなる電界集中部における電界45によってジュール熱が発生し、その熱によって塗膜43に化学反応と結晶化を促進させ、結晶化した金属酸化物を形成する。この金属酸化物の結晶化される領域は電界45の分布形状に倣う。

前記のように、下部電極32と上部電極34の間に電界45の分布形状を反映した部分のみ結晶化した金属酸化物が生成され、その後未結晶化部分を有機溶剤で除去することにより、図3に示すように各突起32a、34aの対面する先端平面部分に接触した複数の金属酸化物からなるメモリ・セル33を形成することができる。なお、前記未結晶化部分を除去する有機溶剤は、前記ゾル−ゲル液に用いた有機溶剤と同じものであることが好ましい。

上記の製造方法で製造されたクロスポイントメモリ構造を有する不揮発性メモリ30は、前記のように、基板31の上に略同一平面内で間隔をおいて平行に、複数の下部電極32が配置され、その上に電気抵抗値が変化する金属酸化物(可変抵抗材料)からなるメモリ・セル33が形成され、さらに、その上に複数の上部電極34が設けられている。そして、下部電極32と上部電極34は概ね互いに直交して配置され、かつ互いに交差する電極の領域において各金属酸化物と接触する面に断面形状が台形の突起32a、34aが設けられた構造である。

そして、任意の電極間に電圧パルスあるいは電流パルス等を電気的手段により印加することによって、その電界を印加した電極の突起32a、34aと接触している金属酸化物からなるメモリ・セル33の電気抵抗値を変化させ、その電気抵抗値が高抵抗状態を論理“0”に、低抵抗状態を論理“1”に関連付けることによって、デジタル情報を保存することができる。

上記のように、各メモリ・セル33とは各電極の突起32a、34aのみが接触するようにしているため、電極間に電界を印加すると、その突起部分に電界が集中する。そのため、クロストークの影響を受けず、低消費電力で駆動することが可能となる。

そして、前記金属酸化物の未結晶化部分が除去されて、メモリ・セル33は個々に独立した柱状に形成されているため、メモリ・セル33間のクロストークの影響を受けることがない。従って、電極の間隔が極めて狭く配置されても、メモリ・セル間のクロストークの影響を回避できるという効果を有する。

このクロスポイントメモリ構造を有するクロストークの影響を受けない不揮発性メモリは、従来の不揮発性メモリのように、下部電極と上部電極が交差する位置にペロブスカイト材料等の金属酸化物を開口部に残して、メモリビットを形成する工程が必要なくなり、製造プロセスコストが安くなり、ビットあたりのコストを下げることができる。

(実施の形態3)

本発明の実施の形態3に係る三次元構造を有する不揮発性メモリについて図5及び図6を用いて説明する。図5は実施の形態3に係る不揮発性メモリ50の構成を示す断面図であり、図6はその製造途中の不揮発性メモリ50の構成を示す断面図である。

本発明の実施の形態3に係る三次元構造を有する不揮発性メモリについて図5及び図6を用いて説明する。図5は実施の形態3に係る不揮発性メモリ50の構成を示す断面図であり、図6はその製造途中の不揮発性メモリ50の構成を示す断面図である。

この不揮発性メモリ50は、シリコン又は表面がシリコン酸化物で被覆されたシリコン等の基板51の上に、複数の棒状の電極を、それぞれ間隔をおいて平行に、かつ略同一平面内に配した電極群を紙面と直角方向に、又紙面の左右方向にそれぞれ交互に積層状態に配置し、そして、これらの電極において、奇数番号の段にある電極521、523・・・と偶数番号の段にある電極522、524・・・は、概ね互いに直交し、かつ、前記各電極の互いに交差する領域の各中央部には互いの先端面が対面する断面形状が台形の突起521a、522a、522b、523a、523b、524a、524b・・・が設けられている。

そして、前記各奇数番号の段の電極と偶数番号の段の電極にそれぞれ設けた対をなす互いに対面する突起521aと522aとの間、522bと523aとの間、523bと524aとの間・・・に、これらの電極の先端面に接触した状態で電気抵抗値が変化する金属酸化物(可変抵抗材料)からなるメモリ・セル53、54、55、56・・・がそれぞれ形成されている。

なお、この図5に示す例では、最上段の電極は偶数番号の段の電極を示しているが、最上段の電極は奇数番号の段の電極であってもよく、互いに対向する奇数番号の段の電極と偶数番号の段の電極の突起部分が共にこれらの電極の間に設けられた金属酸化物からなるメモリ・セルと接続している三次元構造を有する不揮発性メモリである。

前記突起は電極と同質材料であっても、異質材料であってもよく、その電極の形成時にその材料により連続形成しても、或いは電極とは別に設けて一体化してもよい。なお、このことは前述の各実施の形態と同様であり、又、後述の実施の形態4においても同様である。

そして、前記各電極は、上記実施の形態1及び2と同様に、それ自体がワード線又はビット線そのもので形成されるか、あるいはワード線又はビット線とは別に形成されてこれらと接続されている。なお、奇数番号の段にある電極が、ワード線そのものに形成されているかワード線と接続されている場合は、偶数番号の段にある電極が、ビット線そのもので形成されるかビット線と接続されている。その逆の場合は、奇数番号の段にある電極が、ビット線そのものに形成されているかビット線と接続され、偶数番号の段にある電極が、ワード線そのものに形成されているかワード線と接続される。

上記三次元構造を有する不揮発性メモリ50の製造は図6に示すように、シリコン、又は表面がシリコン酸化物で被覆されたシリコン等の基板51の上に、略同一平面内で間隔をおいて平行に複数の電極521を突起521aとともに形成し、その上に有機金属化合物、金属アルコキシド、又は有機酸塩と有機溶剤を混合したゾル−ゲル液を滴下してスピンコーティング法又はディップコーティング法で塗膜631を形成し、これを100〜400℃の温度で乾燥又は仮焼して溶媒を除去する。前記塗膜631を乾燥又は仮焼して得られた薄膜は、構成元素が単に混ざり合っただけのもので、この例においても塗膜631は未結晶状態又は不完全な結晶化状態であり、結晶化した金属酸化物にはなっていない。

その後、塗膜631の上面に突起522aの形状に対応する凹部を形成し、そして塗膜631上に電極521と概ね互いに直交し、間隔をおいて平行に複数の電極522を突起522aとともに形成し、さらにその上に、上記と同様に有機金属化合物、金属アルコキシド、又は有機酸塩と有機溶剤を混合したゾル−ゲル液を滴下してスピンコーティング法又はディップコーティング法で塗膜632を形成し、この塗膜632を100〜400℃の温度で乾燥又は仮焼して溶媒を除去する。

さらにその後、塗膜632の上面に電極523の突起523aに対応する形状の凹部を形成した後、塗膜632上に電極522と概ね互いに直交する複数の電極523を突起523aとともに間隔をおいて平行に形成し、その上に、有機金属化合物、金属アルコキシド、又は有機酸塩と有機溶剤を混合したゾル−ゲル液を滴下してスピンコーティング法又はディップコーティング法で塗膜633を形成し、この塗膜633を100〜400℃の温度で乾燥又は仮焼して溶媒を除去する。なお、この例における各電極、各突起及び各凹部の形成は上記実施の形態1、2と同様の方法により形成される。

上記の電極形成工程、塗膜形成工程、乾燥又は仮焼工程を繰り返し、図6に示す三次元構造体を作製する。このようにして作成された三次元構造体は基板51の上に、略同一平面内で間隔をおいて平行に配された複数の電極が塗膜を介して交互に概ね互いに直交して積み上げられた形となる。すなわち、奇数番号の段にある電極521、523・・・と偶数番号の段にある電極522、524・・・は概ね互いに直交し、そしてこれらの電極の間に塗膜631、632、633、634・・・が設けられ、かつ各突起521a、522a、522b、523a、523b、524a、524b・・・が塗膜631、632、633、634・・・に埋設された構造になる。なお、前記塗膜632、633、634・・・は塗膜631と同様に未結晶状態又は不完全な結晶化状態であり、結晶化した金属酸化物にはなっていない。

次に、上記それぞれの電極間に高電界エネルギーを印加すると、図6に破線で示すように各電極間において各突起の先端平面部分に電界65が集中する。この各突起からなる電界集中部における電界65によってジュール熱が発生し、その熱によって塗膜631、632、633、634・・・に化学反応と結晶化を促進させ、結晶化した金属酸化物を形成する。この金属酸化物の結晶化される領域は電界65の分布形状に倣う。

前記のように、電極間に電界65の分布形状を反映した部分のみ結晶化した金属酸化物が生成され、その後未結晶化部分を有機溶剤で除去することにより、図5に示すように各突起の対面する先端平面部分に接触した金属酸化物からなるメモリ・セル53、54、55、56・・・を形成することができる。なお、前記未結晶化部分を除去する有機溶剤は、前記ゾル−ゲル液に用いた有機溶剤と同じものであることが好ましい。

なお、図5では最上段の電極は偶数番号の段にある電極の場合を示しているが、最上段の電極は奇数番号の段にある電極であってもよく、最下段の電極521と最上段の電極を除き、奇数番号の段にある電極と偶数番号の段にある電極の突起部分が共にこの電極の両面に設けられた金属酸化物と接続している三次元構造を有するものであればよい。

そして、任意の電極間に電圧パルスあるいは電流パルス等を電気的手段により印加することによって、その電界を印加した電極の突起と接触している金属酸化物からなるメモリ・セルの電気抵抗値を変化させ、その電気抵抗値が高抵抗状態を論理“0”に、低抵抗状態を論理“1”に関連付けることによって、デジタル情報を保存することができる。

上記のように、各メモリ・セルは、各電極の突起のみと接触するようにしているため、電極間に電界を印加するとその突起部分に電界が集中する。そのため、クロストークの影響を受けず、低消費電力で駆動することが可能となる。

そして、この実施の形態3においても前記金属酸化物の未結晶化部分が除去されて、メモリ・セル53、54、55、56・・・は個々に独立した柱状に形成されているため、そのメモリ・セル間のクロストークの影響を受けることがないので、電極の間隔が極めて狭く配置されても、メモリ・セル間のクロストークの影響を回避できるという効果を有する。

従って、この三次元構造を有するクロストークの影響を受けない不揮発性メモリにおいても、従来の不揮発性メモリのように、対向する電極が交差する位置にペロブスカイト材料等の金属酸化物を開口部に残してメモリビットを形成する工程を必要とせず、製造プロセスコストが安くなり、ビットあたりのコストを下げることができ、そして、三次元構造を有しているため、大記憶容量で低消費電力駆動の不揮発メモリを提供することができる。

なお、実施の形態1、2、及び3においては、突起を下部電極と上部電極、又は奇数番号の段にある電極と偶数番号の段にある電極、すなわち、対向する電極の金属酸化物と接触する双方の電極にそれぞれ設けたものについて説明したが、これは対向する電極の少なくとも一方の電極に金属酸化物、すなわちメモリ・セルと接触する状態で設けてもその突起部分は電界集中部となってここに電界が集中するため、このような構成によっても同様の効果を有する。

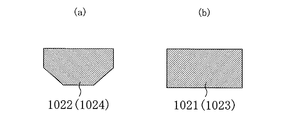

又、実施の形態1、2、及び3においては、電極の突起の断面形状が台形の場合について述べたが、この断面形状は台形に限られるものではなく、三角形、矩形、多角形、略半円形、略半楕円形、又はこれらの形状を組み合わせた形状であってもよく、電極間に電界を印加した時に、電界が集中する形状の電界集中部であればよい。

(実施の形態4)

ここで、電界集中部を形成する突起の形状の例として、突起の断面形状が台形以外のものについて図7に示す。図7(a)は電極の突起の断面形状が三角形の場合、図7(b)は電極の突起の断面形状が略半楕円形の場合である。図7の符号72は電極、72a及び72bはこの電極72に設けられた突起である。

ここで、電界集中部を形成する突起の形状の例として、突起の断面形状が台形以外のものについて図7に示す。図7(a)は電極の突起の断面形状が三角形の場合、図7(b)は電極の突起の断面形状が略半楕円形の場合である。図7の符号72は電極、72a及び72bはこの電極72に設けられた突起である。

(実施の形態5)

次に、本発明の実施の形態5に係る不揮発性メモリについて図8を用いて説明する。図8は実施の形態5に係る不揮発性メモリの1つのメモリ・セル部分の斜視図である。

次に、本発明の実施の形態5に係る不揮発性メモリについて図8を用いて説明する。図8は実施の形態5に係る不揮発性メモリの1つのメモリ・セル部分の斜視図である。

断面形状が六角形の互いに直交する電極81及び電極82に突起は設けられず、実施の形態2及び3と同様の製造方法でその電極81と82の間に金属酸化物からなるメモリ・セル83が形成されている。このメモリ・セル83の形状は、その形成工程において電極81、82の間に高電界エネルギーを印加した時の電界分布の形状を反映している。

このように、電極に突起を設けなくても、電極と金属酸化物とが接触している部分に電界が集中する電極形状であればよく、その断面形状は、台形、三角形、矩形、多角形、略半円形、略半楕円形、又はこれらの図形の組み合わせ形状や合成した形状であってもよい。

上記各実施の形態において、塗膜を形成するゾルーゲル液に混合する有機溶剤としては、例えばエタノールやプロパノール等が用いられる。

(実施の形態6)

本発明の実施の形態6に係る三次元構造を有する不揮発性メモリについて図9及び図10を用いて説明する。図9は実施の形態6に係る不揮発性メモリ100の構成を示す断面図であり、図10(a)及び(b)はそれぞれ電極の断面図である。

本発明の実施の形態6に係る三次元構造を有する不揮発性メモリについて図9及び図10を用いて説明する。図9は実施の形態6に係る不揮発性メモリ100の構成を示す断面図であり、図10(a)及び(b)はそれぞれ電極の断面図である。

この不揮発性メモリ100はシリコン、又は表面がシリコン酸化物で被覆されたシリコン等の基板101の上に、略同一平面内で間隔をおいて平行に、複数の電極1021をスパッタリング法等により配列形成し、その上に、真空蒸着法、スパッタリング法、分子線エピタキシャル成長法(MBE)、クラスターイオンビーム法(ICB)、レーザアブレーション法等の真空中で行う物理堆積法(PVD)により、未結晶化状態又は不完全な結晶化状態の金属酸化物1031の薄膜が形成されている。

その後、前記金属酸化物1031の上面に溝加工を施し、その溝内に電極1021と概ね互いに直交する複数の電極1022を上記電極1021と同様の方法により平行に形成し、さらに、その上に金属酸化物1032の薄膜を前記金属酸化物1031と同様の方法により形成する。前記溝加工は、機械加工、レーザ光照射あるいは光、イオンビーム、電子線等を用いて切削等により行われる。

さらに、上記金属酸化物1032の上に最下段の電極1021と同様の方法により略同一平面内で間隔をおいて平行に、複数の電極1023を配列形成し、その電極1023の上に上記と同様の方法により未結晶化状態又は不完全な結晶化状態の金属酸化物1033の薄膜、電極1024を形成し、以下前記の方法の繰り返しによって多層構造に順次積層する。

ここで、電極形状については、電極1021、1023・・・を図10(b)に示すように断面形状が矩形の四角柱であり、電極1022、1024・・・は図10(a)に示すように断面形状が六角形の六角柱であり、その各六角柱の狭幅の平坦面が電極1021、1023・・・と対面するように配置され、これにより対向する電極の直交部分に電界が集中する。なお、電極1022、1024・・・の形状は前記溝の加工形状に倣うため、その溝の形状が六角柱を形成する形状に加工される。

そして、前記電極形成のための溝加工工程、電極形成工程、金属酸化物薄膜形成工程を繰り返して積層構造に形成した後、各電極間に高電界エネルギーを印加してジュール熱を発生させ、金属酸化物の結晶化を促進させて、対向する電極が交差する部分に結晶化した金属酸化物からなるメモリ・セル領域103、104・・・を形成する。

前記の製造方法で製造された三次元構造を有する不揮発性メモリ100は、基板101の上に、略同一平面内で間隔をおいて平行に、複数の電極が配置され、この電極は段を有し、奇数番号の段にある電極1021、1023・・・と偶数番号の段にある電極1022、1024・・・は、概ね互いに直交し、対向する電極間に電気的手段により電圧パルスあるいは電流パルス等を印加することにより、金属酸化物からなるメモリ・セル領域103、104・・・の電気抵抗値が変化する。

そして、前記各電極は、上記各実施の形態と同様に、それ自体がワード線又はビット線そのもので形成されるか、あるいはワード線又はビット線とは別に形成されてこれらと接続されている。なお、奇数番号の段にある電極が、ワード線そのものに形成されているかワード線と接続されている場合は、偶数番号の段にある電極が、ビット線そのもので形成されるかビット線と接続されている。その逆の場合は、奇数番号の段にある電極が、ビット線そのものに形成されているかビット線と接続され、偶数番号の段にある電極が、ワード線そのものに形成されているかワード線と接続される。

そして、任意の電極間に電圧パルスあるいは電流パルス等の電界を電気的手段により印加することにより、電極と接触しているメモリ・セル領域103、104・・・の金属酸化物の電気抵抗値を変化させ、その電気抵抗値が高抵抗状態を論理“0”に、低抵抗状態を論理“1”に関連付けることによって、デジタル情報を保存することができる。

なお、上記のように電極1022、1024・・・の断面形状を六角形とした構成により、電極間に電界を印加すると、電極1021、1023・・・に対面する電極1022、1024・・・の先端面部分に電界が集中するため、クロストークの影響を受けず、低消費電力で駆動させることが可能となる。

そして、この実施の形態6においては、金属酸化物が個々に独立した柱状に結晶化された部分がメモリ・セル領域として機能するため、そのメモリ・セル領域間のクロストークの影響を受けることがなく、電極の間隔が極めて狭く配置されても、メモリ・セル領域間のクロストークの影響を回避できるという効果を有する。

この三次元構造を有するクロストークの影響を受けない不揮発性メモリは、従来の不揮発性メモリのように、対向する電極が交差する位置にペロブスカイト材料等の金属酸化物を開口部に残して、メモリビットを形成する工程が必要なくなり、製造プロセスコストが安くなるため、ビットコストを下げることができる。さらに、三次元構造を有しているため、大記憶容量で、低消費電力駆動の不揮発性メモリを提供することができる。

上記では、電極1022、1024・・・の断面形状が六角形の場合について述べたが、この断面形状は六角形に限られるものではなく、三角形、矩形、多角形、略半円形、略半楕円形、又はこれらの形状を組み合わせた形状あるいは合成した形状であってもよく、電極間に電界を印加した時に、電界が集中する電界集中形状であればよい。

なお、上記各実施の形態における金属酸化物は、電圧パルスあるいは電流パルスの印加、直流電圧あるいは直流電流の印加、交流電圧あるいは交流電流の印加等により電気抵抗値が変化する金属酸化物(可変抵抗材料)であればよく、ペロブスカイト型構造、イルメナイト型構造、あるいはスピネル型構造等の結晶構造を有するものが好ましく、ペロブスカイト型構造を有する場合は、強誘電体材料、超巨大磁気抵抗(CMR)材料、及び高温超伝導(HTSC)材料の内、少なくとも何れかであり、特に、チタン酸ストロンチウムバリウム、ジルコン酸ストロンチウム、マンガン酸カルシウムプラセオジウム、コバルト酸バリウムカルシウムガドリニウムの内、少なくとも何れかであることが好ましい。さらに、クロム、バナジウム、スカンジウム又は他の遷移金属の内、少なくとも一種以上の添加元素を含有していてもよい。

金属酸化物がイルメナイト型構造を有する場合は、強誘電体材料であることが好ましく、マグネシウム、インジウム、スカンジウム、亜鉛、銅、鉄の内、少なくとも一種以上の添加元素を含有するニオブ酸リチウム又はタンタル酸リチウムである。

又、金属酸化物がペロブスカイト型構造、又はイルメナイト型構造を有する場合の添加元素の濃度は、0mol%を超え10mol%以下であることが好ましい。

又、金属酸化物がスピネル型構造を有する場合は、チタン酸マグネシウム、マグネシウム酸クロム、クロム酸ニッケル、マグネシウム酸アルミニウム、バナジウム酸アルミニウム、コバルト酸鉄の内、少なくとも何れかであることが好ましい。

なお、各実施の形態における電極は、金属酸化物と化合物を形成しない材料、あるいは金属酸化物と拡散又は化学反応しない材料であり、プラチナ、金、銀、銅、イリジウム、ルテニウム、アルミニウムの内、少なくとも何れかであることが好ましい。

又、各実施の形態における電極及び金属酸化物の厚みは、10nm〜1μmが好ましい。

なお、各実施の形態における基板はシリコンに限定するものではなく、アルミン酸ランタン、ニオブ酸リチウム、窒化チタン、又は他の材料の非晶質、多結晶又は単結晶のいずれかである任意の適切な基板材料である。

又、各実施の形態において、基板と下部電極又は最下段の電極の間には、チタン又はタンタル等の酸化し易い材料、或いはチタン酸化物やタンタル酸化物等からなる密着層を形成してもよく、この密着層の厚みは、10nm〜100nmが好ましい。さらに、上部電極又は最上段の電極はアルミニウム酸化物又はシリコン酸化物等の絶縁体で被覆し、内部を保護することが好ましく、不揮発性メモリ素子の信頼性を高めることができる。

本発明は、低消費電力で駆動する低コスト、大記憶容量の低クロストークの不揮発性メモリとその製造方法を提供するもので、大きな情報量を扱う特に携帯用機器のメモリとして最適である。

10、30、50、100 不揮発性メモリ

11、31、51、101 基板

12、32 下部電極

14、34 上部電極

521、522、523、524、72、81、82、1021、1022、1023、1024 電極

23、43、631、632、633、634 塗膜

13、33、53、54、55、56 メモリ・セル(金属酸化物)

25、45、65 電界

12a、14a、32a、34a、72a、72b、521a、522a、522b、523a、523b、524a、524b 突起

11、31、51、101 基板

12、32 下部電極

14、34 上部電極

521、522、523、524、72、81、82、1021、1022、1023、1024 電極

23、43、631、632、633、634 塗膜

13、33、53、54、55、56 メモリ・セル(金属酸化物)

25、45、65 電界

12a、14a、32a、34a、72a、72b、521a、522a、522b、523a、523b、524a、524b 突起

Claims (10)

- 基板の上に配置された下部電極と前記下部電極に対向して配置された上部電極との間に未結晶状態又は不完全な結晶化状態の金属酸化物を設け、前記下部電極と上部電極の間に高電界エネルギーを印加することにより、前記金属酸化物を結晶化することを特徴とする不揮発性メモリの製造方法。

- 基板の上に略同一平面内で間隔をおいて平行に配置された複数の下部電極とこの下部電極と概ね直交し、かつ対向する複数の上部電極との間に、未結晶状態又は不完全な結晶化状態の金属酸化物を設け、前記下部電極と上部電極の間に高電界エネルギーを印加することにより、前記金属酸化物を結晶化することを特徴とする不揮発性メモリの製造方法。

- 基板の上に略同一平面内で間隔をおいて平行に複数の第1の電極を配置し、前記第1の電極の上に未結晶状態又は不完全な結晶化状態の第1の金属酸化物を設け、前記第1の金属酸化物の上に前記第1の複数の電極と概ね直交し、かつ対向する複数の第2の電極を配置し、前記第2の電極の上に未結晶状態又は不完全な結晶化状態の第2の金属酸化物を設け、前記第2の金属酸化物の上に前記第2の複数の電極と概ね直交し、かつ対向する複数の第3の電極を配置し、前記第1の電極と第2の電極の間及び第2の電極と第3の電極の間に高電界エネルギーを印加することにより、前記第1及び第2の金属酸化物を結晶化し、複数段の不揮発性メモリを製造することを特徴とする不揮発性メモリの製造方法。

- 未結晶状態又は不完全な結晶化状態の金属酸化物は有機金属化合物、金属アルコキシド、又は有機酸塩と有機溶剤を混合したゾル−ゲル液からなる塗膜であることを特徴とする請求項1から請求項3のいずれかに記載の不揮発性メモリの製造方法。

- 対向する電極間への高電界エネルギーの印加によりその対向する電極の少なくとも一方の電極に設けた電界集中部からの電界によるジュール熱によって未結晶状態又は不完全な結晶化状態の金属酸化物を結晶化することを特徴とする請求項1から請求項4のいずれかに記載の不揮発性メモリの製造方法。

- 未結晶状態又は不完全な結晶化状態の金属酸化物の結晶化は、対向する電極の少なくとも一方の電極に設けた突起からなる電界集中部からの電界によるジュール熱によって行うようにしたことを特徴とする請求項1から請求項5のいずれかに記載の不揮発性メモリの製造方法。

- 未結晶状態又は不完全な結晶化状態の金属酸化物の結晶化は、電極自体の断面形状を台形、三角形、矩形、多角形、略半円形、略半楕円形、又はこれらの形状の組み合わせあるいは合成した電界集中部からの電界によるジュール熱によって行うようにしたことを特徴とする請求項5に記載の不揮発性メモリの製造方法。

- 金属酸化物の未結晶化部分を有機溶剤で除去することを特徴とする請求項5から請求項7のいずれかに記載の不揮発性メモリの製造方法。

- 対向する電極間に、高電界エネルギーの印加によるジュール熱により結晶化した金属酸化物からなるメモリ・セルを設けたことを特徴とする不揮発性メモリ。

- 金属酸化物が可変抵抗材料からなることを特徴とする請求項9に記載の不揮発性メモリ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004210641A JP2006032729A (ja) | 2004-07-16 | 2004-07-16 | 不揮発性メモリとその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004210641A JP2006032729A (ja) | 2004-07-16 | 2004-07-16 | 不揮発性メモリとその製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2006032729A true JP2006032729A (ja) | 2006-02-02 |

Family

ID=35898695

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004210641A Pending JP2006032729A (ja) | 2004-07-16 | 2004-07-16 | 不揮発性メモリとその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2006032729A (ja) |

Cited By (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008310858A (ja) * | 2007-06-12 | 2008-12-25 | Toshiba Corp | 情報記録再生装置 |

| JP2009218259A (ja) * | 2008-03-07 | 2009-09-24 | Toshiba Corp | 不揮発性記憶装置及びその製造方法 |

| WO2009122601A1 (ja) * | 2008-03-31 | 2009-10-08 | 株式会社 東芝 | 不揮発性記憶装置及びその製造方法 |

| WO2010014974A2 (en) * | 2008-08-01 | 2010-02-04 | President And Fellows Of Harvard College | Phase transition devices and smart capacitive devices |

| JP2010067942A (ja) * | 2008-08-13 | 2010-03-25 | Toshiba Corp | 不揮発性半導体記憶装置及びその製造方法 |

| EP2324503A2 (en) * | 2008-08-21 | 2011-05-25 | Micron Technology, Inc. | Memory devices and methods of forming the same |

| WO2012040015A2 (en) * | 2010-09-22 | 2012-03-29 | Bridgelux, Inc. | Led- based replacement for fluorescent light source |

| WO2012054155A3 (en) * | 2010-10-21 | 2012-06-07 | Micron Technology, Inc. | Integrated circuitry comprising nonvolatile memory cells and methods of forming a nonvolatile memory cell |

| US8411477B2 (en) | 2010-04-22 | 2013-04-02 | Micron Technology, Inc. | Arrays of vertically stacked tiers of non-volatile cross point memory cells, methods of forming arrays of vertically stacked tiers of non-volatile cross point memory cells, and methods of reading a data value stored by an array of vertically stacked tiers of non-volatile cross point memory cells |

| US8427859B2 (en) | 2010-04-22 | 2013-04-23 | Micron Technology, Inc. | Arrays of vertically stacked tiers of non-volatile cross point memory cells, methods of forming arrays of vertically stacked tiers of non-volatile cross point memory cells, and methods of reading a data value stored by an array of vertically stacked tiers of non-volatile cross point memory cells |

| US8431458B2 (en) | 2010-12-27 | 2013-04-30 | Micron Technology, Inc. | Methods of forming a nonvolatile memory cell and methods of forming an array of nonvolatile memory cells |

| US8537592B2 (en) | 2011-04-15 | 2013-09-17 | Micron Technology, Inc. | Arrays of nonvolatile memory cells and methods of forming arrays of nonvolatile memory cells |

| US8674336B2 (en) | 2008-04-08 | 2014-03-18 | Micron Technology, Inc. | Non-volatile resistive oxide memory cells, non-volatile resistive oxide memory arrays, and methods of forming non-volatile resistive oxide memory cells and memory arrays |

| US8681531B2 (en) | 2011-02-24 | 2014-03-25 | Micron Technology, Inc. | Memory cells, methods of forming memory cells, and methods of programming memory cells |

| US8753949B2 (en) | 2010-11-01 | 2014-06-17 | Micron Technology, Inc. | Nonvolatile memory cells and methods of forming nonvolatile memory cells |

| US8791447B2 (en) | 2011-01-20 | 2014-07-29 | Micron Technology, Inc. | Arrays of nonvolatile memory cells and methods of forming arrays of nonvolatile memory cells |

| US8811063B2 (en) | 2010-11-01 | 2014-08-19 | Micron Technology, Inc. | Memory cells, methods of programming memory cells, and methods of forming memory cells |

| JP2014523647A (ja) * | 2011-07-01 | 2014-09-11 | マイクロン テクノロジー, インク. | メモリセル構造 |

| US8976566B2 (en) | 2010-09-29 | 2015-03-10 | Micron Technology, Inc. | Electronic devices, memory devices and memory arrays |

| US9111788B2 (en) | 2008-06-18 | 2015-08-18 | Micron Technology, Inc. | Memory device constructions, memory cell forming methods, and semiconductor construction forming methods |

| US9343145B2 (en) | 2008-01-15 | 2016-05-17 | Micron Technology, Inc. | Memory cells, memory cell programming methods, memory cell reading methods, memory cell operating methods, and memory devices |

| US9343665B2 (en) | 2008-07-02 | 2016-05-17 | Micron Technology, Inc. | Methods of forming a non-volatile resistive oxide memory cell and methods of forming a non-volatile resistive oxide memory array |

| US9412421B2 (en) | 2010-06-07 | 2016-08-09 | Micron Technology, Inc. | Memory arrays |

| US9454997B2 (en) | 2010-12-02 | 2016-09-27 | Micron Technology, Inc. | Array of nonvolatile memory cells having at least five memory cells per unit cell, having a plurality of the unit cells which individually comprise three elevational regions of programmable material, and/or having a continuous volume having a combination of a plurality of vertically oriented memory cells and a plurality of horizontally oriented memory cells; array of vertically stacked tiers of nonvolatile memory cells |

| US9577186B2 (en) | 2008-05-02 | 2017-02-21 | Micron Technology, Inc. | Non-volatile resistive oxide memory cells and methods of forming non-volatile resistive oxide memory cells |

| WO2022235221A1 (en) * | 2021-05-07 | 2022-11-10 | Nanyang Technological University | Methods of preparing crystalline mesoporous metal oxides, metal oxide-carbon and carbon structures |

-

2004

- 2004-07-16 JP JP2004210641A patent/JP2006032729A/ja active Pending

Cited By (80)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8018762B2 (en) | 2007-06-12 | 2011-09-13 | Kabushiki Kaisha Toshiba | Information recording and reproducing apparatus |

| JP2008310858A (ja) * | 2007-06-12 | 2008-12-25 | Toshiba Corp | 情報記録再生装置 |

| US9805792B2 (en) | 2008-01-15 | 2017-10-31 | Micron Technology, Inc. | Memory cells, memory cell programming methods, memory cell reading methods, memory cell operating methods, and memory devices |

| US11393530B2 (en) | 2008-01-15 | 2022-07-19 | Micron Technology, Inc. | Memory cells, memory cell programming methods, memory cell reading methods, memory cell operating methods, and memory devices |

| US10790020B2 (en) | 2008-01-15 | 2020-09-29 | Micron Technology, Inc. | Memory cells, memory cell programming methods, memory cell reading methods, memory cell operating methods, and memory devices |

| US9343145B2 (en) | 2008-01-15 | 2016-05-17 | Micron Technology, Inc. | Memory cells, memory cell programming methods, memory cell reading methods, memory cell operating methods, and memory devices |

| US10262734B2 (en) | 2008-01-15 | 2019-04-16 | Micron Technology, Inc. | Memory cells, memory cell programming methods, memory cell reading methods, memory cell operating methods, and memory devices |

| JP2009218259A (ja) * | 2008-03-07 | 2009-09-24 | Toshiba Corp | 不揮発性記憶装置及びその製造方法 |

| WO2009122601A1 (ja) * | 2008-03-31 | 2009-10-08 | 株式会社 東芝 | 不揮発性記憶装置及びその製造方法 |

| JP2009246309A (ja) * | 2008-03-31 | 2009-10-22 | Toshiba Corp | 不揮発性記憶装置及びその製造方法 |

| US8674336B2 (en) | 2008-04-08 | 2014-03-18 | Micron Technology, Inc. | Non-volatile resistive oxide memory cells, non-volatile resistive oxide memory arrays, and methods of forming non-volatile resistive oxide memory cells and memory arrays |

| US9577186B2 (en) | 2008-05-02 | 2017-02-21 | Micron Technology, Inc. | Non-volatile resistive oxide memory cells and methods of forming non-volatile resistive oxide memory cells |

| US9257430B2 (en) | 2008-06-18 | 2016-02-09 | Micron Technology, Inc. | Semiconductor construction forming methods |

| US9111788B2 (en) | 2008-06-18 | 2015-08-18 | Micron Technology, Inc. | Memory device constructions, memory cell forming methods, and semiconductor construction forming methods |

| US9666801B2 (en) | 2008-07-02 | 2017-05-30 | Micron Technology, Inc. | Methods of forming a non-volatile resistive oxide memory cell and methods of forming a non-volatile resistive oxide memory array |

| US9343665B2 (en) | 2008-07-02 | 2016-05-17 | Micron Technology, Inc. | Methods of forming a non-volatile resistive oxide memory cell and methods of forming a non-volatile resistive oxide memory array |

| WO2010014974A3 (en) * | 2008-08-01 | 2010-04-29 | President And Fellows Of Harvard College | Phase transition devices and smart capacitive devices |

| WO2010014974A2 (en) * | 2008-08-01 | 2010-02-04 | President And Fellows Of Harvard College | Phase transition devices and smart capacitive devices |

| JP2010067942A (ja) * | 2008-08-13 | 2010-03-25 | Toshiba Corp | 不揮発性半導体記憶装置及びその製造方法 |

| US9748475B2 (en) | 2008-08-21 | 2017-08-29 | Ovonyx Memory Technology, Llc | Memory devices including phase change material elements |

| US11050019B2 (en) | 2008-08-21 | 2021-06-29 | Ovonyx Memory Technology, Llc | Memory devices including phase change material elements |

| EP2455971A1 (en) * | 2008-08-21 | 2012-05-23 | Micron Technology, Inc. | Memory devices and methods of forming the same |

| US8124955B2 (en) | 2008-08-21 | 2012-02-28 | Micron Technology, Inc. | Memory devices and methods of forming the same |

| EP2324503A4 (en) * | 2008-08-21 | 2011-11-30 | Micron Technology Inc | MEMORY DEVICES AND MANUFACTURING METHOD THEREFOR |

| EP2324503A2 (en) * | 2008-08-21 | 2011-05-25 | Micron Technology, Inc. | Memory devices and methods of forming the same |

| US8987045B2 (en) | 2008-08-21 | 2015-03-24 | Micron Technology, Inc. | Methods of forming a memory device |

| US10312437B2 (en) | 2008-08-21 | 2019-06-04 | Ovonyx Memory Technology, Llc | Memory devices including phase change material elements |

| US8427859B2 (en) | 2010-04-22 | 2013-04-23 | Micron Technology, Inc. | Arrays of vertically stacked tiers of non-volatile cross point memory cells, methods of forming arrays of vertically stacked tiers of non-volatile cross point memory cells, and methods of reading a data value stored by an array of vertically stacked tiers of non-volatile cross point memory cells |

| US8760910B2 (en) | 2010-04-22 | 2014-06-24 | Micron Technology, Inc. | Arrays of vertically stacked tiers of non-volatile cross point memory cells, methods of forming arrays of vertically stacked tiers of non-volatile cross point memory cells, and methods of reading a data value stored by an array of vertically stacked tiers of non-volatile cross point memory cells |

| US9036402B2 (en) | 2010-04-22 | 2015-05-19 | Micron Technology, Inc. | Arrays of vertically stacked tiers of non-volatile cross point memory cells |

| US8743589B2 (en) | 2010-04-22 | 2014-06-03 | Micron Technology, Inc. | Arrays of vertically stacked tiers of non-volatile cross point memory cells and methods of reading a data value stored by an array of vertically stacked tiers of non-volatile cross point memory cells |

| US8542513B2 (en) | 2010-04-22 | 2013-09-24 | Micron Technology, Inc. | Arrays of vertically stacked tiers of non-volatile cross point memory cells, methods of forming arrays of vertically stacked tiers of non-volatile cross point memory cells, and methods of reading a data value stored by an array of vertically stacked tiers of non-volatile cross point memory cells |

| US8411477B2 (en) | 2010-04-22 | 2013-04-02 | Micron Technology, Inc. | Arrays of vertically stacked tiers of non-volatile cross point memory cells, methods of forming arrays of vertically stacked tiers of non-volatile cross point memory cells, and methods of reading a data value stored by an array of vertically stacked tiers of non-volatile cross point memory cells |

| US10656231B1 (en) | 2010-06-07 | 2020-05-19 | Micron Technology, Inc. | Memory Arrays |

| US9697873B2 (en) | 2010-06-07 | 2017-07-04 | Micron Technology, Inc. | Memory arrays |

| US9887239B2 (en) | 2010-06-07 | 2018-02-06 | Micron Technology, Inc. | Memory arrays |

| US9989616B2 (en) | 2010-06-07 | 2018-06-05 | Micron Technology, Inc. | Memory arrays |

| US10241185B2 (en) | 2010-06-07 | 2019-03-26 | Micron Technology, Inc. | Memory arrays |

| US9412421B2 (en) | 2010-06-07 | 2016-08-09 | Micron Technology, Inc. | Memory arrays |

| US10613184B2 (en) | 2010-06-07 | 2020-04-07 | Micron Technology, Inc. | Memory arrays |

| US10746835B1 (en) | 2010-06-07 | 2020-08-18 | Micron Technology, Inc. | Memory arrays |

| US10859661B2 (en) | 2010-06-07 | 2020-12-08 | Micron Technology, Inc. | Memory arrays |

| US8668361B2 (en) | 2010-09-22 | 2014-03-11 | Bridgelux, Inc. | LED-based replacement for fluorescent light source |

| US9599287B2 (en) | 2010-09-22 | 2017-03-21 | Bridgelux, Inc. | LED-based replacement for fluorescent light source |

| US10132450B2 (en) | 2010-09-22 | 2018-11-20 | Bridgelux Inc. | LED-based replacement for fluorescent light source |

| US10551008B2 (en) | 2010-09-22 | 2020-02-04 | Bridgelux Inc. | LED-based replacement for fluorescent light source |

| US11846394B2 (en) | 2010-09-22 | 2023-12-19 | Bridgelux, Inc. | LED-based replacement for fluorescent light source |

| WO2012040015A3 (en) * | 2010-09-22 | 2012-06-07 | Bridgelux, Inc. | Led- based replacement for fluorescent light source |

| US11428371B2 (en) | 2010-09-22 | 2022-08-30 | Bridgelux, Inc. | LED-based replacement for fluorescent light source |

| WO2012040015A2 (en) * | 2010-09-22 | 2012-03-29 | Bridgelux, Inc. | Led- based replacement for fluorescent light source |

| US8976566B2 (en) | 2010-09-29 | 2015-03-10 | Micron Technology, Inc. | Electronic devices, memory devices and memory arrays |

| US8759809B2 (en) | 2010-10-21 | 2014-06-24 | Micron Technology, Inc. | Integrated circuitry comprising nonvolatile memory cells having platelike electrode and ion conductive material layer |

| WO2012054155A3 (en) * | 2010-10-21 | 2012-06-07 | Micron Technology, Inc. | Integrated circuitry comprising nonvolatile memory cells and methods of forming a nonvolatile memory cell |

| US9245964B2 (en) | 2010-10-21 | 2016-01-26 | Micron Technology, Inc. | Integrated circuitry comprising nonvolatile memory cells and methods of forming a nonvolatile memory cell |

| US9705078B2 (en) | 2010-10-21 | 2017-07-11 | Micron Technology, Inc. | Integrated circuitry comprising nonvolatile memory cells and methods of forming a nonvolatile memory cell |

| US8883604B2 (en) | 2010-10-21 | 2014-11-11 | Micron Technology, Inc. | Integrated circuitry comprising nonvolatile memory cells and methods of forming a nonvolatile memory cell |

| US8811063B2 (en) | 2010-11-01 | 2014-08-19 | Micron Technology, Inc. | Memory cells, methods of programming memory cells, and methods of forming memory cells |

| US8753949B2 (en) | 2010-11-01 | 2014-06-17 | Micron Technology, Inc. | Nonvolatile memory cells and methods of forming nonvolatile memory cells |

| US9117998B2 (en) | 2010-11-01 | 2015-08-25 | Micron Technology, Inc. | Nonvolatile memory cells and methods of forming nonvolatile memory cells |

| US9406878B2 (en) | 2010-11-01 | 2016-08-02 | Micron Technology, Inc. | Resistive memory cells with two discrete layers of programmable material, methods of programming memory cells, and methods of forming memory cells |

| US8796661B2 (en) | 2010-11-01 | 2014-08-05 | Micron Technology, Inc. | Nonvolatile memory cells and methods of forming nonvolatile memory cell |

| US9454997B2 (en) | 2010-12-02 | 2016-09-27 | Micron Technology, Inc. | Array of nonvolatile memory cells having at least five memory cells per unit cell, having a plurality of the unit cells which individually comprise three elevational regions of programmable material, and/or having a continuous volume having a combination of a plurality of vertically oriented memory cells and a plurality of horizontally oriented memory cells; array of vertically stacked tiers of nonvolatile memory cells |

| US9034710B2 (en) | 2010-12-27 | 2015-05-19 | Micron Technology, Inc. | Methods of forming a nonvolatile memory cell and methods of forming an array of nonvolatile memory cells |

| US8431458B2 (en) | 2010-12-27 | 2013-04-30 | Micron Technology, Inc. | Methods of forming a nonvolatile memory cell and methods of forming an array of nonvolatile memory cells |

| US8652909B2 (en) | 2010-12-27 | 2014-02-18 | Micron Technology, Inc. | Methods of forming a nonvolatile memory cell and methods of forming an array of nonvolatile memory cells array of nonvolatile memory cells |

| US8791447B2 (en) | 2011-01-20 | 2014-07-29 | Micron Technology, Inc. | Arrays of nonvolatile memory cells and methods of forming arrays of nonvolatile memory cells |

| US9093368B2 (en) | 2011-01-20 | 2015-07-28 | Micron Technology, Inc. | Nonvolatile memory cells and arrays of nonvolatile memory cells |

| US8681531B2 (en) | 2011-02-24 | 2014-03-25 | Micron Technology, Inc. | Memory cells, methods of forming memory cells, and methods of programming memory cells |

| US9424920B2 (en) | 2011-02-24 | 2016-08-23 | Micron Technology, Inc. | Memory cells, methods of forming memory cells, and methods of programming memory cells |

| US9257648B2 (en) | 2011-02-24 | 2016-02-09 | Micron Technology, Inc. | Memory cells, methods of forming memory cells, and methods of programming memory cells |

| US9184385B2 (en) | 2011-04-15 | 2015-11-10 | Micron Technology, Inc. | Arrays of nonvolatile memory cells and methods of forming arrays of nonvolatile memory cells |

| US8537592B2 (en) | 2011-04-15 | 2013-09-17 | Micron Technology, Inc. | Arrays of nonvolatile memory cells and methods of forming arrays of nonvolatile memory cells |

| US8854863B2 (en) | 2011-04-15 | 2014-10-07 | Micron Technology, Inc. | Arrays of nonvolatile memory cells and methods of forming arrays of nonvolatile memory cells |

| JP2014523647A (ja) * | 2011-07-01 | 2014-09-11 | マイクロン テクノロジー, インク. | メモリセル構造 |

| US10608178B2 (en) | 2011-07-01 | 2020-03-31 | Micron Technology, Inc. | Memory cell structures |

| US9755144B2 (en) | 2011-07-01 | 2017-09-05 | Micron Technology, Inc. | Memory cell structures |

| US9070874B2 (en) | 2011-07-01 | 2015-06-30 | Micron Technology, Inc. | Memory cell structures |

| US9385315B2 (en) | 2011-07-01 | 2016-07-05 | Micron Technology, Inc. | Memory cell structures |

| KR101535763B1 (ko) * | 2011-07-01 | 2015-07-09 | 마이크론 테크놀로지, 인크 | 메모리 셀 구조들 |

| WO2022235221A1 (en) * | 2021-05-07 | 2022-11-10 | Nanyang Technological University | Methods of preparing crystalline mesoporous metal oxides, metal oxide-carbon and carbon structures |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2006032729A (ja) | 不揮発性メモリとその製造方法 | |

| US8546861B2 (en) | Resistance change memory device with three-dimensional structure, and device array, electronic product and manufacturing method therefor | |

| US7580276B2 (en) | Nonvolatile memory element | |

| US8513639B2 (en) | Resistive-switching memory and fabrication method thereof | |

| WO2005041303A1 (ja) | 抵抗変化素子、その製造方法、その素子を含むメモリ、およびそのメモリの駆動方法 | |

| JP4880894B2 (ja) | 半導体記憶装置の構造及びその製造方法 | |

| JP2006060232A (ja) | 不揮発性メモリ素子及びその製造方法 | |

| JP2004273656A (ja) | Epir素子及びそれを利用した半導体装置 | |

| US20110073927A1 (en) | Non-volatile memory device and method for manufacturing the same | |

| CN113948520A (zh) | 一种氧化铪基铁电电容及其制备方法 | |

| US11869928B2 (en) | Dual hydrogen barrier layer for memory devices | |

| JP2005123361A (ja) | 抵抗変化型不揮発性メモリおよびその製造方法ならびに抵抗変化層の形成方法 | |

| JP5300839B2 (ja) | 情報記録再生装置 | |

| JP2006032728A (ja) | 不揮発性メモリ | |

| JPH11233733A (ja) | 電子部品及びその製造方法 | |

| JP4939414B2 (ja) | 可変抵抗素子 | |

| JP2005236003A (ja) | 抵抗変化型不揮発性メモリ、抵抗変化型不揮発性メモリの製造方法、記録方法、再生方法、消去方法、抵抗変化材料微細構造体および抵抗変化材料微細構造体の製造方法 | |

| JP2004096050A (ja) | 強誘電体デバイスの作製方法、およびそれを用いた強誘電体メモリ、圧電素子、インクジェット式ヘッドおよびインクジェットプリンタ | |

| JP4238248B2 (ja) | 可変抵抗素子を備えた不揮発性半導体記憶装置の製造方法 | |

| JP2006344876A (ja) | 不揮発性記憶素子とその製造方法 | |

| KR101401221B1 (ko) | 결정질 산화막을 포함한 저항 메모리 소자 및 이의 제조 방법 | |

| TWI229891B (en) | Semiconductor device and method of manufacturing the same | |

| JP2005347468A (ja) | 不揮発性メモリ | |

| JP2005213105A (ja) | 多結晶金属酸化物薄膜とその製造方法及び不揮発性メモリ | |

| TWI463641B (zh) | Ultra - high density resistive memory structure and its manufacturing method |