JP2006030336A - 画像表示装置及びその駆動方法と走査線駆動回路 - Google Patents

画像表示装置及びその駆動方法と走査線駆動回路 Download PDFInfo

- Publication number

- JP2006030336A JP2006030336A JP2004205539A JP2004205539A JP2006030336A JP 2006030336 A JP2006030336 A JP 2006030336A JP 2004205539 A JP2004205539 A JP 2004205539A JP 2004205539 A JP2004205539 A JP 2004205539A JP 2006030336 A JP2006030336 A JP 2006030336A

- Authority

- JP

- Japan

- Prior art keywords

- scanning line

- circuit

- driving

- data

- pulse

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Abstract

【解決手段】画素アレイ部12は、行状の走査線DSLと、列状のデータ線DTLと、両者が交差する部分に配された行列状の画素11とを備えている。データ線駆動回路14は、システム回路16から供給されたデータ信号を各データ線DTLに分配する。走査線駆動回路13は、各走査線DSLに順次駆動パルスDSを出力して画素11を線順次で選択し、以って該分配されたデータ信号に基き駆動パルスDSの時間幅だけ画素11を駆動して画素アレイ部12に画像を表示する。走査線駆動回路13は、各走査線DSLに順次出力する駆動パルスDSの時間幅を各走査線DSLごと独立に可変制御可能であり、以って走査線単位で各画素11の駆動時間を制御する。

【選択図】図1

Description

Claims (9)

- 画素アレイ部と、データ線駆動回路と、走査線駆動回路と、システム回路とを含み、

前記画素アレイ部は、行状の走査線と、列状のデータ線と、両者が交差する部分に配された行列状の画素とを備え、

前記データ線駆動回路は、該システム回路から供給されたデータ信号を各データ線に分配し、

前記走査線駆動回路は、該システム回路から供給される制御信号に応じて動作し、各走査線に順次駆動パルスを出力して画素を線順次で選択し、

以って該分配されたデータ信号に基き該駆動パルスの時間幅だけ画素を駆動して該画素アレイ部に画像を表示する画像表示装置において、

前記走査線駆動回路は、各走査線に順次出力する駆動パルスの時間幅を各走査線ごと独立に可変制御可能であり、以って走査線単位で各画素の駆動時間を制御することを特徴とする画像表示装置。 - 前記システム回路はスタートパルス、クロック信号及び補正データを含む制御信号を該走査線駆動回路に供給し、

前記走査線駆動回路は、シフトレジスタ回路と出力時間設定回路とバッファ回路とを含んでおり、

前記シフトレジスタ回路は、該クロック信号に応じて該スタートパルスを順次転送し、以って該シフトレジスタ回路の各段から順次駆動パルスを出力し、

前記出力時間設定回路は、該補正データに応じて各駆動パルスの時間幅を個々に設定し、

前記バッファ回路は、時間幅の設定された各駆動パルスを各走査線に出力することを特徴とする請求項1記載の画像表示装置。 - 前記画素アレイ部は画素毎に発光素子を含んで発光面を構成し、各発光素子はデータ信号に応じた輝度で発光し且つ駆動パルスの時間幅に応じた時間分発光を持続して該発光面に画像を表示することを特徴とする請求項1記載の画像表示装置。

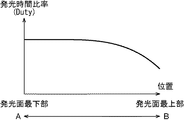

- 前記発光面は、該発光素子の発光によって熱を発生し更に発生した熱の放散により、発光面の走査線と直交する上下方向に温度分布のムラが生じ、

前記走査線駆動回路は、該温度分布のムラを緩和するように各駆動パルスの時間幅を制御することを特徴とする請求項3記載の画像表示装置。 - 前記発光面は、その温度分布が上部に比べて下部が低く、前記走査線駆動回路は上部の走査線に出力する駆動パルスに比べて下部の走査線に出力する駆動パルスの時間幅を長くし、以って下部の発熱量を増やして温度分布のムラを緩和することを特徴とする請求項4記載の画像表示装置。

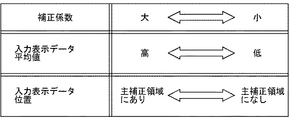

- 前記システム回路は、外部から入力された多階調の画像をフレーム単位で表すデータ信号からフレーム階調平均値を検出する情報検出手段と、

前記情報検出手段から得られたフレーム階調平均値に応じて、該補正データのレベルを制御する補正レベル制御回路とを有することを特徴とする請求項2記載の画像表示装置。 - 外部から入力されたオブジェクトを含む画像を表すデータ信号から、該画素アレイ部における該オブジェクトの位置を抽出する情報検出手段と、

前記情報検出手段から得られたオブジェクトの位置に応じて、該補正データのレベルを制御する補正レベル制御回路とを有することを特徴とする請求項2記載の画像表示装置。 - 行状の走査線と列状のデータ線と両者が交差する部分に配された行列状の画素とを備える画素アレイに、各データ線を介しデータ信号を供給して画像を表示する画像表示装置の走査線を駆動するために用いる走査線駆動回路であって、

外部から供給される制御信号に応じて動作し、各走査線に順次駆動パルスを出力して画素を線順次で選択し、

各データ線を介して供給された該データ信号に基き該駆動パルスの時間幅だけ選択された画素を駆動して該画素アレイに画像を表示する際、

各走査線に順次出力する駆動パルスの時間幅を各走査線ごと独立に可変制御可能であり、以って走査線単位で各画素の駆動時間を制御することを特徴とする走査線駆動回路。 - 行状の走査線と、列状のデータ線と、両者が交差する部分に配された行列状の画素とを備えた画像表示装置の駆動方法であって、

外部から供給されたデータ信号を各データ線に分配するデータ線駆動手順と、

外部から供給される制御信号に応じ、各走査線に順次駆動パルスを出力して画素を線順次で選択する走査線駆動手順とを行い、

以って該分配されたデータ信号に基き該駆動パルスの時間幅だけ画素を駆動して画像を表示する際、

前記走査線駆動手順は、各走査線に順次出力する駆動パルスの時間幅を各走査線ごと独立に可変制御可能であり、以って走査線単位で各画素の駆動時間を制御することを特徴とする画像表示装置の駆動方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004205539A JP2006030336A (ja) | 2004-07-13 | 2004-07-13 | 画像表示装置及びその駆動方法と走査線駆動回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004205539A JP2006030336A (ja) | 2004-07-13 | 2004-07-13 | 画像表示装置及びその駆動方法と走査線駆動回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006030336A true JP2006030336A (ja) | 2006-02-02 |

| JP2006030336A5 JP2006030336A5 (ja) | 2007-08-16 |

Family

ID=35896805

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004205539A Pending JP2006030336A (ja) | 2004-07-13 | 2004-07-13 | 画像表示装置及びその駆動方法と走査線駆動回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2006030336A (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2013129612A1 (ja) * | 2012-02-29 | 2013-09-06 | 昭和電工株式会社 | エレクトロルミネッセント素子の製造方法 |

| WO2013129615A1 (ja) * | 2012-02-29 | 2013-09-06 | 昭和電工株式会社 | 有機電界発光素子の製造方法 |

| KR20130117061A (ko) * | 2012-04-17 | 2013-10-25 | 삼성디스플레이 주식회사 | 유기전계발광 표시장치 및 그의 구동방법 |

| WO2023017912A1 (ko) * | 2021-08-09 | 2023-02-16 | 삼성전자주식회사 | 디스플레이 장치 및 그 제어 방법 |

Citations (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH096283A (ja) * | 1995-06-16 | 1997-01-10 | Fujitsu Ltd | プラズマディスプレイパネルの温度補償方法及び装置、プラズマディスプレイパネルの加熱防止方法及び装置並びにこれらを用いたプラズマディスプレイ表示装置 |

| JPH09288467A (ja) * | 1996-04-22 | 1997-11-04 | Nisshin:Kk | 電子式表示パネルのパネル温調方法および電子式表示パネル |

| JPH11194745A (ja) * | 1998-01-07 | 1999-07-21 | Mitsubishi Electric Corp | ディスプレイ装置 |

| JPH11231828A (ja) * | 1998-02-16 | 1999-08-27 | Mitsubishi Electric Corp | プラズマディスプレイ装置 |

| JP2000122606A (ja) * | 1998-10-19 | 2000-04-28 | Mitsubishi Electric Corp | Pdp表示装置 |

| JP2001013923A (ja) * | 1999-06-28 | 2001-01-19 | Toppan Printing Co Ltd | 有機エレクトロルミネッセンス表示素子およびその駆動方法 |

| JP2001060076A (ja) * | 1999-06-17 | 2001-03-06 | Sony Corp | 画像表示装置 |

| JP2001109426A (ja) * | 1999-10-04 | 2001-04-20 | Matsushita Electric Ind Co Ltd | 表示装置およびその輝度制御方法 |

| JP2001134197A (ja) * | 1999-11-04 | 2001-05-18 | Matsushita Electric Ind Co Ltd | 表示パネルの温度補償装置および温度補償方法 |

| JP2002175046A (ja) * | 2000-12-07 | 2002-06-21 | Sony Corp | 画像表示装置 |

| JP2005283823A (ja) * | 2004-03-29 | 2005-10-13 | Seiko Epson Corp | 電気光学装置、その駆動回路および駆動方法、ならびに電子機器 |

-

2004

- 2004-07-13 JP JP2004205539A patent/JP2006030336A/ja active Pending

Patent Citations (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH096283A (ja) * | 1995-06-16 | 1997-01-10 | Fujitsu Ltd | プラズマディスプレイパネルの温度補償方法及び装置、プラズマディスプレイパネルの加熱防止方法及び装置並びにこれらを用いたプラズマディスプレイ表示装置 |

| JPH09288467A (ja) * | 1996-04-22 | 1997-11-04 | Nisshin:Kk | 電子式表示パネルのパネル温調方法および電子式表示パネル |

| JPH11194745A (ja) * | 1998-01-07 | 1999-07-21 | Mitsubishi Electric Corp | ディスプレイ装置 |

| JPH11231828A (ja) * | 1998-02-16 | 1999-08-27 | Mitsubishi Electric Corp | プラズマディスプレイ装置 |

| JP2000122606A (ja) * | 1998-10-19 | 2000-04-28 | Mitsubishi Electric Corp | Pdp表示装置 |

| JP2001060076A (ja) * | 1999-06-17 | 2001-03-06 | Sony Corp | 画像表示装置 |

| JP2001013923A (ja) * | 1999-06-28 | 2001-01-19 | Toppan Printing Co Ltd | 有機エレクトロルミネッセンス表示素子およびその駆動方法 |

| JP2001109426A (ja) * | 1999-10-04 | 2001-04-20 | Matsushita Electric Ind Co Ltd | 表示装置およびその輝度制御方法 |

| JP2001134197A (ja) * | 1999-11-04 | 2001-05-18 | Matsushita Electric Ind Co Ltd | 表示パネルの温度補償装置および温度補償方法 |

| JP2002175046A (ja) * | 2000-12-07 | 2002-06-21 | Sony Corp | 画像表示装置 |

| JP2005283823A (ja) * | 2004-03-29 | 2005-10-13 | Seiko Epson Corp | 電気光学装置、その駆動回路および駆動方法、ならびに電子機器 |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2013129612A1 (ja) * | 2012-02-29 | 2013-09-06 | 昭和電工株式会社 | エレクトロルミネッセント素子の製造方法 |

| WO2013129615A1 (ja) * | 2012-02-29 | 2013-09-06 | 昭和電工株式会社 | 有機電界発光素子の製造方法 |

| US9082980B2 (en) | 2012-02-29 | 2015-07-14 | Showa Denko K.K. | Manufacturing method for electroluminescent element |

| KR20130117061A (ko) * | 2012-04-17 | 2013-10-25 | 삼성디스플레이 주식회사 | 유기전계발광 표시장치 및 그의 구동방법 |

| KR101895996B1 (ko) | 2012-04-17 | 2018-09-07 | 삼성디스플레이 주식회사 | 유기전계발광 표시장치 및 그의 구동방법 |

| WO2023017912A1 (ko) * | 2021-08-09 | 2023-02-16 | 삼성전자주식회사 | 디스플레이 장치 및 그 제어 방법 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9966007B2 (en) | Organic light emitting display and method for controlling emission thereof | |

| US10733933B2 (en) | Pixel driving circuit and driving method thereof, display panel and display device | |

| US7944412B2 (en) | Semiconductor device, display apparatus, and display apparatus driving method | |

| JP4737221B2 (ja) | 表示装置 | |

| JP3570394B2 (ja) | アクティブマトリクス型表示装置およびアクティブマトリクス型有機エレクトロルミネッセンス表示装置、並びにそれらの駆動方法 | |

| US11380246B2 (en) | Electroluminescent display device having pixel driving | |

| JP2010008521A (ja) | 表示装置 | |

| US20090243978A1 (en) | Display apparatus | |

| KR20080084730A (ko) | 화소 회로 및 표시 장치와 그 구동 방법 | |

| JP2005099714A (ja) | 電気光学装置、電気光学装置の駆動方法および電子機器 | |

| JP2006065148A (ja) | 表示装置及びその駆動方法 | |

| JP2011112723A (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| JP2015025978A (ja) | 駆動回路、表示装置、及び駆動方法 | |

| JP4274070B2 (ja) | 表示装置及びその駆動方法 | |

| JP2011112722A (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| JP2005164894A (ja) | 画素回路及び表示装置とこれらの駆動方法 | |

| US11100870B2 (en) | Display device | |

| JP2010008522A (ja) | 表示装置 | |

| JP2009109784A (ja) | 画像表示装置 | |

| JP2011022462A (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| JP2005070761A (ja) | 画像表示装置とその製造方法 | |

| JP2010276783A (ja) | アクティブマトリクス型表示装置 | |

| JP2006030336A (ja) | 画像表示装置及びその駆動方法と走査線駆動回路 | |

| KR20090087796A (ko) | 능동 유기 발광 다이오드 디스플레이 | |

| JP2005321684A (ja) | 映像表示装置および映像表示方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070703 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070703 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20090223 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20090223 |

|

| RD05 | Notification of revocation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7425 Effective date: 20090225 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100817 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101008 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110419 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110809 |