JP2005333107A - 半導体装置、画像表示装置および半導体装置の製造方法 - Google Patents

半導体装置、画像表示装置および半導体装置の製造方法 Download PDFInfo

- Publication number

- JP2005333107A JP2005333107A JP2005037949A JP2005037949A JP2005333107A JP 2005333107 A JP2005333107 A JP 2005333107A JP 2005037949 A JP2005037949 A JP 2005037949A JP 2005037949 A JP2005037949 A JP 2005037949A JP 2005333107 A JP2005333107 A JP 2005333107A

- Authority

- JP

- Japan

- Prior art keywords

- region

- impurity

- impurity region

- semiconductor layer

- forming

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/01—Manufacture or treatment

- H10D86/021—Manufacture or treatment of multiple TFTs

- H10D86/0221—Manufacture or treatment of multiple TFTs comprising manufacture, treatment or patterning of TFT semiconductor bodies

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/031—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT]

- H10D30/0312—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT] characterised by the gate electrodes

- H10D30/0314—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT] characterised by the gate electrodes of lateral top-gate TFTs comprising only a single gate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/031—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT]

- H10D30/0321—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT] comprising silicon, e.g. amorphous silicon or polysilicon

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6704—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device

- H10D30/6713—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device characterised by the properties of the source or drain regions, e.g. compositions or sectional shapes

- H10D30/6715—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device characterised by the properties of the source or drain regions, e.g. compositions or sectional shapes characterised by the doping profiles, e.g. having lightly-doped source or drain extensions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6729—Thin-film transistors [TFT] characterised by the electrodes

- H10D30/673—Thin-film transistors [TFT] characterised by the electrodes characterised by the shapes, relative sizes or dispositions of the gate electrodes

- H10D30/6733—Multi-gate TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

Landscapes

- Thin Film Transistor (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005037949A JP2005333107A (ja) | 2004-04-21 | 2005-02-15 | 半導体装置、画像表示装置および半導体装置の製造方法 |

| US11/109,818 US20050253195A1 (en) | 2004-04-21 | 2005-04-20 | Semiconductor device and image display device |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004125489 | 2004-04-21 | ||

| JP2005037949A JP2005333107A (ja) | 2004-04-21 | 2005-02-15 | 半導体装置、画像表示装置および半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005333107A true JP2005333107A (ja) | 2005-12-02 |

| JP2005333107A5 JP2005333107A5 (enExample) | 2007-02-15 |

Family

ID=35308599

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005037949A Pending JP2005333107A (ja) | 2004-04-21 | 2005-02-15 | 半導体装置、画像表示装置および半導体装置の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US20050253195A1 (enExample) |

| JP (1) | JP2005333107A (enExample) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010245484A (ja) * | 2009-03-17 | 2010-10-28 | Ricoh Co Ltd | Mosトランジスタおよび該mosトランジスタを内蔵した半導体装置ならびに該半導体装置を用いた電子機器 |

| JP2015005728A (ja) * | 2013-06-21 | 2015-01-08 | 上海和輝光電有限公司Everdisplay Optronics (Shanghai) Limited | 薄膜トランジスタ |

| JPWO2016175086A1 (ja) * | 2015-04-28 | 2018-02-01 | シャープ株式会社 | 半導体装置及びその製造方法 |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005311037A (ja) * | 2004-04-21 | 2005-11-04 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| JP2006269808A (ja) * | 2005-03-24 | 2006-10-05 | Mitsubishi Electric Corp | 半導体装置および画像表示装置 |

| US20070052021A1 (en) * | 2005-08-23 | 2007-03-08 | Semiconductor Energy Laboratory Co., Ltd. | Transistor, and display device, electronic device, and semiconductor device using the same |

| KR101414926B1 (ko) | 2009-07-18 | 2014-07-04 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 반도체 장치 제조 방법 |

| GB2524486A (en) * | 2014-03-24 | 2015-09-30 | Cambridge Silicon Radio Ltd | Ultra low power transistor for 40nm processes |

| WO2015151337A1 (ja) * | 2014-03-31 | 2015-10-08 | 株式会社 東芝 | 薄膜トランジスタ、半導体装置及び薄膜トランジスタの製造方法 |

| CN106611764B (zh) * | 2015-10-27 | 2019-12-10 | 群创光电股份有限公司 | 显示设备 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000332257A (ja) * | 1999-03-12 | 2000-11-30 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| JP2002190479A (ja) * | 2000-09-22 | 2002-07-05 | Semiconductor Energy Lab Co Ltd | 半導体表示装置及びその作製方法 |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6306694B1 (en) * | 1999-03-12 | 2001-10-23 | Semiconductor Energy Laboratory Co., Ltd. | Process of fabricating a semiconductor device |

-

2005

- 2005-02-15 JP JP2005037949A patent/JP2005333107A/ja active Pending

- 2005-04-20 US US11/109,818 patent/US20050253195A1/en not_active Abandoned

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000332257A (ja) * | 1999-03-12 | 2000-11-30 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| JP2002190479A (ja) * | 2000-09-22 | 2002-07-05 | Semiconductor Energy Lab Co Ltd | 半導体表示装置及びその作製方法 |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010245484A (ja) * | 2009-03-17 | 2010-10-28 | Ricoh Co Ltd | Mosトランジスタおよび該mosトランジスタを内蔵した半導体装置ならびに該半導体装置を用いた電子機器 |

| JP2015005728A (ja) * | 2013-06-21 | 2015-01-08 | 上海和輝光電有限公司Everdisplay Optronics (Shanghai) Limited | 薄膜トランジスタ |

| US9401376B2 (en) | 2013-06-21 | 2016-07-26 | Everdisplay Optronics (Shanghai) Limited | Thin film transistor and active matrix organic light emitting diode assembly and method for manufacturing the same |

| JPWO2016175086A1 (ja) * | 2015-04-28 | 2018-02-01 | シャープ株式会社 | 半導体装置及びその製造方法 |

| US10468533B2 (en) | 2015-04-28 | 2019-11-05 | Sharp Kabushiki Kaisha | Semiconductor device and method for manufacturing same |

Also Published As

| Publication number | Publication date |

|---|---|

| US20050253195A1 (en) | 2005-11-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6995048B2 (en) | Thin film transistor and active matrix type display unit production methods therefor | |

| KR100288039B1 (ko) | 표시장치 및 전기광학장치 | |

| JP2011518434A (ja) | 薄膜トランジスタおよびアクティブマトリクスディスプレイ | |

| JP2009016469A (ja) | 半導体装置およびその製造方法 | |

| WO2016175086A1 (ja) | 半導体装置及びその製造方法 | |

| CN1909249B (zh) | 具有薄膜晶体管的半导体器件及其制造方法 | |

| TWI447916B (zh) | 顯示裝置 | |

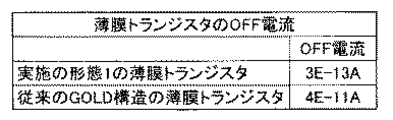

| KR100727714B1 (ko) | 반도체 장치 및 화상 표시 장치 | |

| JP2005333107A (ja) | 半導体装置、画像表示装置および半導体装置の製造方法 | |

| JP4232675B2 (ja) | 半導体装置の製造方法 | |

| JP2004040108A (ja) | Ldd構造を有する薄膜トランジスタとその製造方法 | |

| JP2005311037A (ja) | 半導体装置およびその製造方法 | |

| JP3643025B2 (ja) | アクティブマトリクス型表示装置およびその製造方法 | |

| JP2004327979A (ja) | 薄膜トランジスター及びこれを利用した表示装置 | |

| JP4641741B2 (ja) | 半導体装置 | |

| JPH05275701A (ja) | 薄膜トランジスタ | |

| JPH0864795A (ja) | 薄膜トランジスタ及びイメージセンサ | |

| JP5414712B2 (ja) | 半導体装置 | |

| JP2007142082A (ja) | 表示装置およびその製造方法 | |

| KR100473237B1 (ko) | 박막트랜지스터와 그 제조방법 및 그것을 사용한액정표시장치 | |

| JP5337414B2 (ja) | 表示装置およびその製造方法 | |

| JP3469183B2 (ja) | 液晶表示装置 | |

| JP2005064123A (ja) | 薄膜トランジスタおよび表示装置 | |

| KR100191786B1 (ko) | 박막트랜지스터의 제조방법 | |

| JP2004064056A (ja) | 半導体集積回路の作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061226 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061226 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100318 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100330 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100525 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110405 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110530 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120110 |