JP2005294851A - 低温ポリシリコンtft構造及びそのチャネル層の製造方法 - Google Patents

低温ポリシリコンtft構造及びそのチャネル層の製造方法 Download PDFInfo

- Publication number

- JP2005294851A JP2005294851A JP2005108557A JP2005108557A JP2005294851A JP 2005294851 A JP2005294851 A JP 2005294851A JP 2005108557 A JP2005108557 A JP 2005108557A JP 2005108557 A JP2005108557 A JP 2005108557A JP 2005294851 A JP2005294851 A JP 2005294851A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- thin film

- low

- region

- temperature polysilicon

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6729—Thin-film transistors [TFT] characterised by the electrodes

- H10D30/673—Thin-film transistors [TFT] characterised by the electrodes characterised by the shapes, relative sizes or dispositions of the gate electrodes

- H10D30/6733—Multi-gate TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/031—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT]

- H10D30/0312—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT] characterised by the gate electrodes

- H10D30/0314—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT] characterised by the gate electrodes of lateral top-gate TFTs comprising only a single gate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/031—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT]

- H10D30/0321—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT] comprising silicon, e.g. amorphous silicon or polysilicon

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6729—Thin-film transistors [TFT] characterised by the electrodes

- H10D30/673—Thin-film transistors [TFT] characterised by the electrodes characterised by the shapes, relative sizes or dispositions of the gate electrodes

- H10D30/6731—Top-gate only TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6741—Group IV materials, e.g. germanium or silicon carbide

- H10D30/6743—Silicon

- H10D30/6745—Polycrystalline or microcrystalline silicon

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6757—Thin-film transistors [TFT] characterised by the structure of the channel, e.g. transverse or longitudinal shape or doping profile

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/40—Crystalline structures

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/01—Manufacture or treatment

- H10D86/021—Manufacture or treatment of multiple TFTs

- H10D86/0251—Manufacture or treatment of multiple TFTs characterised by increasing the uniformity of device parameters

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P34/00—Irradiation with electromagnetic or particle radiation of wafers, substrates or parts of devices

- H10P34/40—Irradiation with electromagnetic or particle radiation of wafers, substrates or parts of devices with high-energy radiation

- H10P34/42—Irradiation with electromagnetic or particle radiation of wafers, substrates or parts of devices with high-energy radiation with electromagnetic radiation, e.g. laser annealing

Landscapes

- Thin Film Transistor (AREA)

- Recrystallisation Techniques (AREA)

Abstract

【課題】 低温ポリシリコンTFT構造を提供する。

【解決手段】 低温ポリシリコンTFT構造であって、主にキャップ層、ポリシリコン薄膜及びゲートからなる。キャップ層は基板上方に配置され、基板との間に隙間領域がある。ポリシリコン薄膜はキャップ層上に配置され、チャネル領域とチャネル領域の両側に位置するソース/ドレイン領域とに分けられる。チャネル領域は隙間領域の上に位置する。また、ゲートはチャネル領域上方に配置される。チャネル領域の下に隙間領域があるため、レーザアニール工程を行う際、該隙間領域の熱伝導係数が小さく、シリコン原子の再結晶時間がより長くなり、チャネル領域内でより大きい結晶粒を形成して、チャネル領域中にある結晶粒界を減少させる。且つ、ポリシリコン薄膜における結晶粒の粒子配向がすべてトランジスタにおける電子の伝達方向と平行するので、トランジスタの電気特性を向上することができる。

【選択図】 図3

【解決手段】 低温ポリシリコンTFT構造であって、主にキャップ層、ポリシリコン薄膜及びゲートからなる。キャップ層は基板上方に配置され、基板との間に隙間領域がある。ポリシリコン薄膜はキャップ層上に配置され、チャネル領域とチャネル領域の両側に位置するソース/ドレイン領域とに分けられる。チャネル領域は隙間領域の上に位置する。また、ゲートはチャネル領域上方に配置される。チャネル領域の下に隙間領域があるため、レーザアニール工程を行う際、該隙間領域の熱伝導係数が小さく、シリコン原子の再結晶時間がより長くなり、チャネル領域内でより大きい結晶粒を形成して、チャネル領域中にある結晶粒界を減少させる。且つ、ポリシリコン薄膜における結晶粒の粒子配向がすべてトランジスタにおける電子の伝達方向と平行するので、トランジスタの電気特性を向上することができる。

【選択図】 図3

Description

本発明はTFT構造及びそのチャネル層の製造方法に係り、特に低温ポリシリコンTFT構造及びそのチャネル層の製造方法に係る。

大部分の電子素子は、素子を駆動するためのスイッチを必要とする。アクティブ駆動の表示素子を例にあげると、通常はTFT(Thin Film Transistor)を駆動スイッチとしている。そして、TFTはチャネル領域の材質により、アモルファスシリコンTFTと、ポリシリコンTFTとに分けられる。ポリシリコンTFTは、アモルファスTFTに比べてその消費電力が小さく且つ電子移動度が大きいので、次第に市場において注目を集めている。

早期のポリシリコンTFTのプロセス温度は摂氏1000度に達するため、基板材質の選択が大幅に限定されていた。然し、近年レーザ技術の発展により、プロセス温度は摂氏600度以下にまで降下し、このプロセスで形成されたポリシリコンTFTは、低温ポリシリコンTFTとも呼ばれる。

低温ポリシリコンTFTにおいて、ポリシリコン薄膜の形成方法は、先ず基板上にアモルファスシリコン薄膜を形成し、その後アモルファスシリコンを溶融させ、再結晶させてポリシリコン薄膜を形成する。図1A及び図1Bは従来の低温ポリシリコン薄膜の製造フロー断面図である。一般に常用されるレーザアニ−ルプロセス(Laser Annealing Process)はエキシマレーザアニ−ル(Excimer Laser Annealing、以下ELAプロセスという)である。図1Aに示すとおり、基板100上にアモルファスシリコン薄膜102を形成した後、エキシマレーザアニ−ルビーム106によりレーザアニ−ルプロセスを行ってアモルファスシリコン102を溶融させ、図1Bのように、シリコン分子を再結晶させてポリシリコン薄膜102aを形成する。

然しながら、ELAプロセスにより形成されたポリシリコン薄膜102aは、結晶粒の大きさが小さすぎ、且つサイズの均一性(uniformity)が良くないので、ポリシリコン薄膜102aには多くの結晶粒界が存在して、ポリシリコン薄膜102aのチャネル領域における電子の移動度が僅か100〜200cm2/V-secであるので、薄膜トランジスタの機能にかなり大きな影響を与える。

上記の問題を解決するために、従来は逐次的横方向結晶化(Sequential Lateral Solidification, SLS)と呼ばれるレーザアニール工程を提供する。図2A及び2Bは、もう一つの従来の低温ポリシリコン薄膜の製造フロー断面図を示す。

図2Aに示すように、SLSプロセスはマスク104でアモルファスシリコン薄膜102がレーザビーム106に照射される範囲を画定して、一部領域内のアモルファスシリコン薄膜102、即ち領域110内のアモルファスシリコン薄膜102を溶融する。あるSLSプロセスにおいて、マスク104は基台により制御されて移動し、レーザビームにマスク104上のホール108を透過させて領域110における全てのアモルファスシリコン薄膜102を照射する。

図2Bに示すとおり、一定の時間が経過すると、溶融されたアモルファスシリコン薄膜102(つまり、領域110内のアモルファスシリコン薄膜102)は、溶融していないアモルファスシリコン薄膜102を結晶核として横方向に成長し、領域110内においてポリシリコン薄膜202aを形成する。

図2Bから分かるように、SLSプロセスにより結晶粒サイズがより大きいポリシリコン薄膜202aを形成することができる。つまり、SLSプロセスにより形成されたポリシリコン薄膜202aにおける結晶粒界が少ないので、SLSプロセスと従来のELAプロセスを比較すると、SLSプロセスはポリシリコン薄膜における電子の移動度を高くするだけでなく、薄膜トランジスタの機能を高めることができ、ポリシリコン薄膜の粒子配向を比較的一致させることができる。

然しながら、SLSプロセスで使用する機器設備は比較的高価なもので、従来のELAプロセスに比べ特殊なマスクを余分に使用しなければならないため、トランジスタ全体の製造コストが高くなる。また、SLSプロセスでは、やはりポリシリコン薄膜を形成する所要時間を減少することができない。

そこで、本発明の目的は低温ポリシリコンTFT構造であって、そのチャネル層における結晶粒がより均一なサイズを有し、且つ結晶粒界がより少なく、トランジスタにより好ましい素子特性をもたせることができる低温ポリシリコンTFT構造を提供する。

本発明のもう一つの目的は、低温ポリシリコンTFT構造のチャネル層の製造方法を提供し、トランジスタのチャネル領域における結晶粒の大小及びその粒子配向を制御することにより、チャネル領域における電子の移動度を向上させる。この他、該製造方法が使用するプロセス設備は、従来のプロセス設備と相容性があるので、製造コストを節約することができる。

上記の目的を達成するために、本発明は、基板上に配置するのに適した低温ポリシリコンTFT構造を提供する。当該低温ポリシリコンTFT構造は、主にキャップ層、ポリシリコン薄膜及びゲートからなる。このうち、キャップ層は基板上方に配置され、基板との間に隙間領域がある。ポリシリコン薄膜は、キャップ層上に配置されて、チャネル領域とチャネル領域の両側に位置するソース/ドレイン領域とに分けられる。チャネル領域は隙間領域の上に位置して、且つチャネル領域内のポリシリコン薄膜はトランジスタのチャネル層として、ゲートはチャネル領域上方に配置される。

本発明の実施形態によれば、当該低温ポリシリコンTFTは、更に基板上に配置され、キャップ層と基板との間に位置し、基板における不純物が製造プロセスにおいて、予期しない拡散を起こして素子の機能に影響するのを防ぐ緩衝層を備える。本実施形態において、隙間領域は、例えばキャップ層と緩衝層との間に位置し、隙間領域の熱伝導係数は、緩衝層及び基板の熱伝導係数より低い。

本発明の実施形態によれば、この低温ポリシリコンTFT構造は、ポリシリコン薄膜上に配置されたゲート絶縁層を、更に備える。

本発明の実施形態によれば、チャネル領域内のポリシリコン薄膜の結晶粒は、例えばソース/ドレイン領域内のポリシリコン薄膜の結晶粒より大きいので、トランジスタがより高い駆動電流とより低い漏れ電流を有する。この他、チャネル領域中にある結晶粒の大きさがより大きいため、その内部の結晶粒界の数も、ソース/ドレイン領域中にある結晶粒界の数より少なく、電子はチャネル領域において、電界を受けて移動できるが結晶粒界に散乱されにくく、従ってよりよい電子移動度を有する。また、ゲートの幅はチャネル領域の結晶粒のサイズより小さいのが好ましい。この他、別の実施形態においては、ゲートは、例えばダブルゲート構造であって、電子が直接チャネル中央にある唯一の結晶粒界の影響を受けるのを減少させて、顕かにトランジスタの機能を向上させることができる。

本発明の実施形態による低温ポリシリコンTFTは、誘電層、ソース/ドレインコンタクトホール及びソース/ドレイン導電層と、を更に備える。このうち、誘電層はポリシリコン薄膜上に配置されてゲートを被覆する。ソース/ドレインコンタクトホールは、全て誘電層及びゲート絶縁層中に配置され、ソース/ドレイン領域と電気的接続する。また、ソース/ドレイン導電層は、誘電層上に配置されソース/ドレインコンタクトホールを埋めて、ソース/ドレイン領域と電気的接続する。

本発明は、低温ポリシリコンTFTのチャネル層の製造方法も提供する。該方法は、まず基板上方に犠牲層を形成し、犠牲層上にキャップ層及びアモルファスシリコン薄膜を順に形成する。次に、犠牲層を除去して、基板とキャップ層との間に隙間領域を形成する。その後、アモルファスシリコン薄膜を溶融して再結晶させ、隙間領域上方のキャップ層上にポリシリコンチャネル層を形成する。

本発明の実施形態によれば、該方法は、犠牲層を形成する前に、まず基板上に緩衝層を形成して、基板における不純物が製造プロセス中に予期しない拡散を起こすのを防ぐ。その後、犠牲層を緩衝層上に形成する。

本発明の実施形態によれば、犠牲層を除去する方法は、例えば既に形成された構造をエッチング液に浸すウェットエッチングにより行われる。このステップにおいて、犠牲層のエッチング速度はその他の膜層のエッチング速度より大きい。

本発明の実施形態によれば、アモルファスシリコン薄膜を溶融した後再結晶させてポリシリコンチャネル層を形成するステップは、先ずエキシマレーザ(Excimer Laser)によりアモルファスシリコン薄膜を照射して、アモルファスシリコン薄膜を溶融して液態のシリコン材料にする。次に、アニ−ルプロセスを行ってシリコン材料における結晶粒を新たに配列させてポリシリコン薄膜を形成する。このうち、隙間領域上方に位置するポリシリコン薄膜はポリシリコンチャネル層であり、ポリシリコンチャネル層でのシリコン結晶粒は、ポリシリコン薄膜が他の領域内でのシリコン結晶粒より大きい。

本発明により形成されたポリシリコン薄膜における結晶粒の粒子配向は、全てトランジスタが作動状態における電子伝送の方向と平行となり、電子のチャネル領域における移動度を改善して、トランジスタの電気特性を向上させることができる。

以下で本発明のその他の目的、特徴を更に明らかにするために、図面を参照しながら実施形態をあげて説明する。

以上の説明から、本発明の低温ポリシリコンTFTは次の特徴を有する。

1. トランジスタのチャネル中にある結晶粒のサイズがより大きく、且つ均一性がより良いので、本発明のトランジスタはより高い駆動電流及び高電子移動度を有する。

2. 本発明の製造プロセスにより形成されたポリシリコン薄膜では、結晶粒の粒子配向がすべてトランジスタ内の電子伝達方向に平行するので、本発明によれば、電子のチャネル領域における移動度を改善して、トランジスタの電気特性を向上させる。

3. トランジスタのチャネル領域の幅と長さは、犠牲層の幅と長さで決まる。従って、チャネル領域の幅、長さの比は実際の製造プロセスによって犠牲層の大きさを調整でき、製造プロセスの適応性が良い。

4. 本発明のプロセス設備と、従来のプロセス設備は相容性があり、例えば従来のエキシマレーザアニール工程の設備により逐次的横方向結晶化工程のレベルに達することができ、つまり本発明により製品品質を向上できると同時に、プロセス設備のコストを節約して、最大の生産利潤に達することができる。

本発明は、アモルファスシリコン薄膜をポリシリコン薄膜に転換する前に、先ずアモルファスシリコン薄膜の、後続工程においてポリシリコンチャネルにする予定の領域下方の犠牲層を除去して、熱伝導性が両側より低い隙間領域を形成することにより、該隙間領域上方のシリコン結晶粒の結晶速度が両側領域内のシリコン結晶粒の結晶速度より遅く、結晶粒を両側から中央に向かって横方向に成長させ、かつチャネル領域により大きい結晶粒を成長させる。

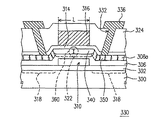

図3は、本発明の第1実施形態に係る低温ポリシリコンTFTの断面図である。図3に示すように、本発明の低温ポリシリコンTFT330は、主に基板300、キャップ層306、ポリシリコン薄膜308a、ゲート316及びソース/ドレイン導電層336からなる。このうち、キャップ層306は基板300上に配置され、本実施形態においては、基板における不純物が製造プロセス中に予期しない拡散を生じて素子の機能に影響することを防ぐよう、基板300上に、例えばキャップ層306と基板300との間にある緩衝層302を配置する。

特に、キャップ層306と緩衝層302との間に、更に隙間領域310を有する。隙間領域310内には、例えば熱伝導係数がより低い空気若しくはその他のガスがある。

ポリシリコン薄膜308aはキャップ層306上に配置され、チャネル領域322と不純物のドープされたソース/ドレイン領域318に分けられる。このうちチャネル領域322は隙間領域310の上に位置し、チャネル領域322内のポリシリコン薄膜308aが、低温ポリシリコンTFT330のポリシリコンチャネル層である。ゲート316はポリシリコン薄膜308aのチャネル領域322の上に配置され、ポリシリコン薄膜308a上に例えばゲート絶縁層314が配置される。

誘電層324はゲート絶縁層314上に配置され、ゲート316を被覆する。また、誘電層324上にソース/ドレイン導電層336が配置され、ソース/ドレイン導電層336は、誘電層324とゲート絶縁層314との間に配置されるソース/ドレインコンタクトホール332を介してソース/ドレイン領域318と電気的に接続する。

注意すべきは、本実施形態において、チャネル領域322内のポリシリコン薄膜308a中にあるシリコン結晶粒340は、例えばソース/ドレイン領域318内のポリシリコン薄膜308a中にあるシリコン結晶粒350より大きく、好ましい大きさは、チャネル領域322の長さLの半分より大きい程度である。従って、低温ポリシリコンTFT330は、より高い駆動電流を有することができる。且つ、チャネル領域322内の結晶粒340の大きさがより大きいため、チャネル領域322内の結晶粒界360の数が、ソース/ドレイン領域318内の結晶粒界360の数より少ない。且つ、結晶粒の粒子配向が、電子の低温ポリシリコンTFT330内での伝送方向と平行であるので、低温ポリシリコンTFT330が作動状態であるとき、電子キャリアが容易にチャネル領域322を透過でき、チャネル領域322内の結晶粒界360が多すぎるため乱射され、電子移動度が低下することがない。

特に、本発明は低温ポリシリコンTFT330のゲート316の幅を縮小して、結晶粒340のサイズよりも小さくすることが可能であり(図4Aに示す)、よって薄膜トランジスタのチャネル領域が結晶粒界をまたぐのを防いで、薄膜トランジスタがより良い機能を持つことができる。この分野の通常の知識を有する者であれば分かるように、ここでいう結晶粒サイズとは、通常ゲートの幅と平行な方向上の結晶粒の長さを指す。

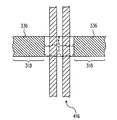

ゲートの幅を縮小する以外、本発明は、更に低温ポリシリコンTFT上に、本発明の別の実施形態に係る低温ポリシリコンTFTの平面図である図4Bに示すようなダブルゲート構造416を配置することができる。このようなダブルゲート構造416も、電子が直接チャネル中央の唯一の結晶粒界の影響を受けるのを減少して、トランジスタの機能を明らかに向上させることができる。

本発明は、特殊な製造プロセスにより、上記チャネル領域が好ましい特性を有する低温ポリシリコンTFTを製造する。以下で実施形態を挙げて上記低温ポリシリコンTFTのチャネル層の製造方法について説明する。

図5Aから図5Eは、本発明の第2実施形態に係る低温ポリシリコンTFTのチャネル層の製造フロー断面図である。また、図6Aから図6Cはそれぞれ図5Aから図5Cに対応する平面図であり、図6Dは図5Eに対応する平面図である。

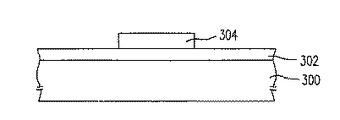

図5Aに示すように、まず基板300上に緩衝層302及び犠牲層304を順に、例えばCVD法若しくはスパッタ法により形成する。また、犠牲層304の材質は例えば金属材料である。更に注意すべきは、緩衝層302は選択性の層であって、その機能は前記の実施形態のとおりであるので、ここでは特に述べない。また、この分野の通常の知識を有する者が実際の製造プロセスの必要に応じて緩衝層302を設けても設けなくてもよく、本発明はこれを限定しない。また、犠牲層304は、例えば図6Aに示すような、緩衝層302上に配置された長方形パターンの膜層である。

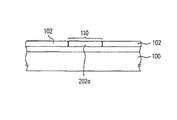

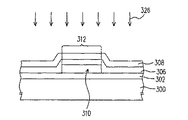

図5B及び図6Bに示すように、緩衝層302上にキャップ層306及びアモルファスシリコン薄膜308を順に形成して、犠牲層304を被覆する。このうち、後続の製造プロセスにおいて犠牲層304上方の領域312内に低温ポリシリコンTFTのチャネル層を形成し、領域312の両側にソース/ドレイン領域を形成する。従って、犠牲層304の幅が該低温ポリシリコンTFTのチャネル層の長さを決定する。つまり、犠牲層304の幅を制御することにより、低温ポリシリコンTFTにおけるチャネル領域の長さを有効に制御できる。

図5C及び図6Cに示すように、次に犠牲層304を除去して、キャップ層306と緩衝層302との間に、例えば空気が充填している隙間領域310を形成する。このステップは、ウェットエッチングにより犠牲層304を除去し、例えば図5Bに示すような構造をエッチング液に浸す(図示せず)。また、このエッチング液の犠牲層304に対するエッチング速度が他の膜層のエッチング速度よりはるかに大きいので、このステップにより他の膜層が完全に保持されたまま犠牲層304を除去することができる。

図5D及び図5Eに示すように、隙間領域310を形成した後、続いてレーザアニール工程によりアモルファスシリコン薄膜308を溶融して再結晶させてポリシリコン薄膜308aを形成し、隙間領域310の上方にあるキャップ層306上にポリシリコンチャネル層522(つまり、領域312内に位置するポリシリコン薄膜308a)を形成する。本実施形態が使用するレーザアニール工程は、例えばエキシマレーザアニール工程であり、図5Dに示すように、エキシマレーザビーム326でアモルファスシリコン薄膜308を照射して溶融させ、液態シリコンとする(図示せず)。一定時間経過すると、液態シリコンが次第に冷えて再結晶し、ポリシリコン薄膜となる。この際、領域312が隙間領域310の上方に位置し、隙間領域310内には、例えば空気が存在しており、空気の熱伝導係数は0.025W/cm2Kであり、キャップ層306及び緩衝層302の熱伝導係数よりはるかに小さい。従って、領域312内の液態シリコンの結晶速度が両側の液態シリコンの結晶速度より遅くなる。つまり、結晶化の過程において、シリコン原子が両側から領域312の中央に向かって横方向に結晶粒を成長させてポリシリコン薄膜308aを形成する。図5E及び図6Dに示すように、この領域312内のポリシリコン薄膜308aがトランジスタのポリシリコンチャネル層522である。

特に、領域312中にある結晶粒の成長速度が遅いため、形成された結晶粒のサイズも、両側領域内で形成された結晶粒より大きく、つまり、ポリシリコンチャネル層522中にある結晶粒のサイズがより大きく、例えばポリシリコンチャネル層522の長さLの半分よりやや大きい。

この他、ポリシリコンチャネル層522内の結晶粒界の数は、両側領域中にある結晶粒界の数より少ないので、電子がポリシリコンチャネル層522内においてより好ましい移動度を有し、トランジスタの電気特性を向上させる。

以上、本発明の実施例を図面を参照して詳述してきたが、具体的な構成は、この実施例に限られるものではなく、本発明の要旨を逸脱しない範囲の設計変更等があっても、本発明に含まれる。

100、300 基板

102、308 アモルファスシリコン薄膜

102a、202a、308a ポリシリコン薄膜

104 マスク

106、326 エキシマレーザビーム

108 ホール

110、312 領域

302 緩衝層

304 犠牲層

306 キャップ層

310 隙間領域

314 ゲート絶縁層

316 ゲート

318 ソース/ドレイン領域

322 チャネル領域

324 誘電層

330 低温ポリシリコンTFT

332 ソース/ドレインコンタクトホール

336 ソース/ドレイン導電層

340、350 シリコン結晶粒

416 ダブルゲート構造

522 ポリシリコンチャネル層

102、308 アモルファスシリコン薄膜

102a、202a、308a ポリシリコン薄膜

104 マスク

106、326 エキシマレーザビーム

108 ホール

110、312 領域

302 緩衝層

304 犠牲層

306 キャップ層

310 隙間領域

314 ゲート絶縁層

316 ゲート

318 ソース/ドレイン領域

322 チャネル領域

324 誘電層

330 低温ポリシリコンTFT

332 ソース/ドレインコンタクトホール

336 ソース/ドレイン導電層

340、350 シリコン結晶粒

416 ダブルゲート構造

522 ポリシリコンチャネル層

Claims (13)

- 基板上に配置するのに適した低温ポリシリコンTFT構造であって、

基板上方に配置され、基板との間に隙間領域があるキャップ層と、

前記キャップ層上に配置され、チャネル領域及び前記チャネル領域の両側に位置するソース/ドレイン領域を備え、前記チャネル領域が前記隙間領域の上にあるポリシリコン薄膜と、

前記ポリシリコン薄膜の前記チャネル領域上方に配置されたゲートと、

を備えることを特徴とする低温ポリシリコンTFT構造。 - 前記基板と前記キャップ層との間に配置された緩衝層を更に備え、前記隙間領域が前記キャップ層と前記緩衝層との間に位置することを特徴とする請求項1に記載の低温ポリシリコンTFT構造。

- 前記隙間領域の熱伝導係数が前記緩衝層の熱伝導係数より小さいことを特徴とする請求項2に記載の低温ポリシリコンTFT構造。

- 前記隙間領域の熱伝導係数が前記基板の熱伝導係数より小さいことを特徴とする請求項1に記載の低温ポリシリコンTFT構造。

- 前記ポリシリコン薄膜上に配置されたゲート絶縁層を更に備えることを特徴とする請求項1に記載の低温ポリシリコンTFT構造。

- 前記ポリシリコン薄膜の前記チャネル領域中にある結晶粒の大きさが前記ポリシリコン薄膜の前記ソース/ドレイン領域中にある結晶粒の大きさより大きいことを特徴とする請求項1に記載の低温ポリシリコンTFT構造。

- 前記ゲートの幅が前記チャネル領域の結晶粒の大きさより小さいことを特徴とする請求項1に記載の低温ポリシリコンTFT構造。

- 前記ゲートがダブルゲート構造であることを特徴とする請求項1に記載の低温ポリシリコンTFT構造。

- 前記ポリシリコン薄膜及び前記ゲート上に配置され、複数のコンタクトホールを有し、前記ポリシリコン薄膜の前記ソース/ドレイン領域を露出させる誘電層と、

前記誘電層上に配置され、前記誘電層における前記コンタクトホールと前記ポリシリコン薄膜の前記ソース/ドレイン領域により電気的接続をするソース/ドレイン導電層と、

を更に備えることを特徴とする請求項1に記載の低温ポリシリコンTFT構造。 - 基板上に犠牲層を形成するステップと、

前記基板上にキャップ層を形成して前記犠牲層を被覆するステップと、

前記キャップ層上にアモルファスシリコン薄膜を形成するステップと、

前記犠牲層を除去して、前記基板と前記キャップ層との間に隙間領域を形成するステップと、

前記アモルファスシリコン薄膜を溶融させた後再結晶させて、前記隙間領域上方の前記キャップ層上にポリシリコンチャネル層を形成するステップと、

を含む低温ポリシリコンTFTのチャネル層の製造方法。 - 前記基板上方に前記犠牲層を形成する前に、緩衝層を前記基板上に形成するステップを更に含むことを特徴とする請求項10に記載の低温ポリシリコンTFTのチャネル層の製造方法。

- 前記犠牲層を除去する方法がウェットエッチングを含み、前記犠牲層のエッチング速度が前記キャップ層のエッチング速度より速いことを特徴とする請求項10に記載の低温ポリシリコンTFTのチャネル層の製造方法。

- 前記アモルファスシリコン薄膜を溶融させる方法がエキシマレーザアニ−ルを含むことを特徴とする請求項10に記載の低温ポリシリコンTFTのチャネル層の製造方法。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| TW093109339A TWI228832B (en) | 2004-04-05 | 2004-04-05 | Structure of LTPS-TFT and fabricating method of channel layer thereof |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005294851A true JP2005294851A (ja) | 2005-10-20 |

Family

ID=35059713

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005108557A Pending JP2005294851A (ja) | 2004-04-05 | 2005-04-05 | 低温ポリシリコンtft構造及びそのチャネル層の製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US20050224876A1 (ja) |

| JP (1) | JP2005294851A (ja) |

| TW (1) | TWI228832B (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2016100537A (ja) * | 2014-11-25 | 2016-05-30 | 株式会社ブイ・テクノロジー | 薄膜トランジスタ、薄膜トランジスタの製造方法及びレーザアニール装置 |

| KR20170124523A (ko) * | 2016-04-01 | 2017-11-10 | 보에 테크놀로지 그룹 컴퍼니 리미티드 | Tft 어레이 기판, 그 제조 방법, 및 디스플레이 디바이스 |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7381586B2 (en) | 2005-06-16 | 2008-06-03 | Industrial Technology Research Institute | Methods for manufacturing thin film transistors that include selectively forming an active channel layer from a solution |

| TWI295855B (en) * | 2006-03-03 | 2008-04-11 | Ind Tech Res Inst | Double gate thin-film transistor and method for forming the same |

| US7972943B2 (en) * | 2007-03-02 | 2011-07-05 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of semiconductor device |

| KR102368593B1 (ko) * | 2015-04-03 | 2022-03-03 | 삼성디스플레이 주식회사 | 박막 트랜지스터 기판 및 이를 구비하는 표시 패널 |

| CN105161498B (zh) * | 2015-08-03 | 2017-09-19 | 京东方科技集团股份有限公司 | 薄膜晶体管及其制作方法、阵列基板以及显示装置 |

| CN105957805B (zh) * | 2016-06-29 | 2018-12-18 | 京东方科技集团股份有限公司 | 低温多晶硅薄膜制作方法、薄膜晶体管、阵列基板和显示装置 |

| US10355034B2 (en) * | 2017-08-21 | 2019-07-16 | Wuhan China Star Optoelectronics Technology Co., Ltd. | Low-temperature polycrystalline silicon array substrate and manufacturing method, display panel |

| JP7261567B2 (ja) * | 2018-11-26 | 2023-04-20 | 株式会社Screenホールディングス | 基板処理方法および基板処理装置 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| AU2001286432A1 (en) * | 2000-08-14 | 2002-02-25 | Matrix Semiconductor, Inc. | Dense arrays and charge storage devices, and methods for making same |

| US20030155572A1 (en) * | 2002-02-19 | 2003-08-21 | Min-Koo Han | Thin film transistor and method for manufacturing thereof |

| TWI231996B (en) * | 2003-03-28 | 2005-05-01 | Au Optronics Corp | Dual gate layout for thin film transistor |

| TW578310B (en) * | 2003-04-02 | 2004-03-01 | Au Optronics Corp | Low temperature poly silicon thin film transistor and method of forming poly silicon layer of the same |

-

2004

- 2004-04-05 TW TW093109339A patent/TWI228832B/zh not_active IP Right Cessation

- 2004-07-30 US US10/710,729 patent/US20050224876A1/en not_active Abandoned

-

2005

- 2005-04-05 JP JP2005108557A patent/JP2005294851A/ja active Pending

- 2005-09-15 US US11/162,569 patent/US20060008953A1/en not_active Abandoned

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2016100537A (ja) * | 2014-11-25 | 2016-05-30 | 株式会社ブイ・テクノロジー | 薄膜トランジスタ、薄膜トランジスタの製造方法及びレーザアニール装置 |

| WO2016084702A1 (ja) * | 2014-11-25 | 2016-06-02 | 株式会社ブイ・テクノロジー | 薄膜トランジスタ、薄膜トランジスタの製造方法及びレーザアニール装置 |

| US10211343B2 (en) | 2014-11-25 | 2019-02-19 | V Technology Co., Ltd. | Thin film transistor, manufacturing process for thin film transistor, and laser annealing apparatus |

| US10535778B2 (en) | 2014-11-25 | 2020-01-14 | V Technology Co., Ltd. | Thin film transistor, manufacturing process for thin film transistor, and laser annealing apparatus |

| US10622484B2 (en) | 2014-11-25 | 2020-04-14 | V Technology Co., Ltd. | Thin film transistor, manufacturing process for thin film transistor, and laser annealing apparatus |

| KR20170124523A (ko) * | 2016-04-01 | 2017-11-10 | 보에 테크놀로지 그룹 컴퍼니 리미티드 | Tft 어레이 기판, 그 제조 방법, 및 디스플레이 디바이스 |

| US10325938B2 (en) | 2016-04-01 | 2019-06-18 | Boe Technology Group Co., Ltd. | TFT array substrate, method for manufacturing the same, and display device |

| KR102055247B1 (ko) * | 2016-04-01 | 2019-12-11 | 보에 테크놀로지 그룹 컴퍼니 리미티드 | Tft 어레이 기판, 그 제조 방법, 및 디스플레이 디바이스 |

Also Published As

| Publication number | Publication date |

|---|---|

| TW200534484A (en) | 2005-10-16 |

| US20050224876A1 (en) | 2005-10-13 |

| US20060008953A1 (en) | 2006-01-12 |

| TWI228832B (en) | 2005-03-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6410373B1 (en) | Method of forming polysilicon thin film transistor structure | |

| KR100785020B1 (ko) | 하부 게이트 박막 트랜지스터 및 그 제조방법 | |

| JP2005303299A (ja) | 電子素子及びその製造方法 | |

| KR20030069779A (ko) | 박막트랜지스터 및 그 제조방법 | |

| JP2005294851A (ja) | 低温ポリシリコンtft構造及びそのチャネル層の製造方法 | |

| TWI520219B (zh) | 形成多晶矽層的方法和製造薄膜電晶體的方法 | |

| JP6081689B2 (ja) | 多結晶シリコン層、薄膜トランジスタ、及び有機電界発光表示装置の製造方法 | |

| JPH02275641A (ja) | 半導体装置の製造方法 | |

| JP4549842B2 (ja) | 薄膜トランジスタの製造方法 | |

| US6387779B1 (en) | Method of crystallizing a silicon film and thin film transistor and fabricating method thereof using the same | |

| US7435667B2 (en) | Method of controlling polysilicon crystallization | |

| KR100915073B1 (ko) | 반도체막의 결정화 방법 및 이 방법에 의해 결정화된반도체막 | |

| JPH1084114A (ja) | 薄膜半導体装置及びその製造方法 | |

| KR19980083097A (ko) | 비정질 실리콘층의 결정화 방법 및 이를 사용한 박막트랜지스터의 제조방법 | |

| JP2007184562A (ja) | 多結晶シリコンフィルムの製造方法及びそれを適用した薄膜トランジスタの製造方法 | |

| CN100391009C (zh) | 低温多晶硅薄膜晶体管及其沟道层的制造方法 | |

| JP2004063478A (ja) | 薄膜トランジスタ及びその製造方法 | |

| US7115449B2 (en) | Method for fabrication of polycrystalline silicon thin film transistors | |

| CN100570836C (zh) | 多晶硅薄膜晶体管及其制造方法 | |

| WO2006007757A1 (fr) | Transistor a film en couches minces en polysilicium a faible temperature | |

| JP2008198643A (ja) | 結晶質半導体膜の製造方法およびアクティブマトリクス基板の製造方法 | |

| CN114242735B (zh) | 一种阵列基板及制作方法、移动终端 | |

| CN100413040C (zh) | 多晶硅薄膜晶体管的形成方法 | |

| CN2717022Y (zh) | 低温多晶硅薄膜晶体管 | |

| US20060172469A1 (en) | Method of fabricating a polycrystalline silicon thin film transistor |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070724 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070801 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20071226 |