JP2005294740A - マルチフィンガーnmosトランジスタ構造 - Google Patents

マルチフィンガーnmosトランジスタ構造 Download PDFInfo

- Publication number

- JP2005294740A JP2005294740A JP2004111172A JP2004111172A JP2005294740A JP 2005294740 A JP2005294740 A JP 2005294740A JP 2004111172 A JP2004111172 A JP 2004111172A JP 2004111172 A JP2004111172 A JP 2004111172A JP 2005294740 A JP2005294740 A JP 2005294740A

- Authority

- JP

- Japan

- Prior art keywords

- nmos transistor

- finger

- resistance

- drain

- transistor structure

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Landscapes

- Semiconductor Integrated Circuits (AREA)

Abstract

【課題】プロセス変動に影響されにくく、且つ、マルチフィンガーNMOSトランジスタの寄生NPNトランジスタを、ほぼ同時にONさせるような静電気保護素子としてのマルチフィンガーNMOSトランジスタの構造を提供すること。

【解決手段】P型半導体基板上に構成される半導体集積回路の静電破壊保護素子であって、複数のゲート電極を有するマルチフィンガータイプのNMOSにおいて、

前記半導体基板と反対導電型の拡散層をNMOSトランジスタを囲繞するように構成し、且つ、囲繞されたP型半導体領域を配線手段によっては、如何なる電位へも接続されないことを特徴とするマルチフィンガーNMOSトランジスタ構造。

【選択図】図1

【解決手段】P型半導体基板上に構成される半導体集積回路の静電破壊保護素子であって、複数のゲート電極を有するマルチフィンガータイプのNMOSにおいて、

前記半導体基板と反対導電型の拡散層をNMOSトランジスタを囲繞するように構成し、且つ、囲繞されたP型半導体領域を配線手段によっては、如何なる電位へも接続されないことを特徴とするマルチフィンガーNMOSトランジスタ構造。

【選択図】図1

Description

本発明は、半導体集積回路における静電気破壊保護回路、特に、複数のゲート電極を有するマルチフィンガー型のNMOSトランジスタの構造に関する。

半導体集積回路の静電気保護素子としては、従来からPN接合ダイオードが用いられてきたが、近年の微細化の進展に伴い、MOSトランジスタのゲート酸化膜厚が、例えば、0.35μmのプロセスでは60〜70Å、0.25μmのプロセスでは40〜60Å、というように薄膜化してきている。

このようにゲート酸化膜の薄膜化が進むと、低電圧化による動作が可能になる反面、静電気耐性が劣化してしまうという問題がある。従来のPNダイオードを用いた保護素子・回路では、PNダイオード自身のブレークダウン電圧がゲート酸化膜の耐圧より大きいこと、又、ブレークダウンする速さが静電気パルスに追従できないこと等から、ゲート酸化膜に損傷が生じてしまうため、近年ではマルチフィンガーNMOSトランジスタの寄生バイポーラトランジスタによるスナップバック特性を利用し、より積極的に静電気電荷を能動素子により消費する方法が用いられている(非特許文献1参照)。

図7(a)〜(c)、図8及び図9を用いて従来例を説明する。

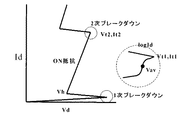

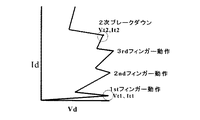

図7(a)は通常用いられるマルチフィンガーNMOSトランジスタの平面図、図7(b)は断面図、図7(c)は寄生のNPNトランジスタまで含めた等価回路図である。図8はNMOSトランジスタのスナップバック特性を示す図、図9はフィンガー数が3の場合のマルチフィンガーNMOSトランジスタのスナップバック特性を示す図である。

微細化されたMOSトランジスタでは、ソース・ドレイン抵抗が増加し性能が劣化するが、これを防ぐためにソース・ドレイン領域にシリサイドが形成され、ソース・ドレイン抵抗を低減させる手法が採られる。

しかしながら、保護素子用のNMOSトランジスタにシリサイド構造を適用すると静電気耐性が劣化することが報告されており(非特許文献2参照)、静電気耐性劣化を防ぐために、通常シリサイド・ブロック技術により保護NMOSトランジスタのゲート電極(図7(a)の11)と静電気放電パルスが印加されるドレイン電極(図7(a)の13)との間にシリサイドを設けない領域(図7(a)の15)を設定する。マルチフィンガーNMOSトランジスタにシリサイド・ブロック技術を適用すると、シリサイド・

ブロックされた領域はバラスト抵抗として動作し、各フィンガーの動作均一性を促す。図7(c)及び図8は静電気放電パルスがドレイン領域に印加されたときのマルチフィンガーNMOSトランジスタの動作、所謂スナップバック特性を示す。

ブロックされた領域はバラスト抵抗として動作し、各フィンガーの動作均一性を促す。図7(c)及び図8は静電気放電パルスがドレイン領域に印加されたときのマルチフィンガーNMOSトランジスタの動作、所謂スナップバック特性を示す。

図9を用いてマルチフィンガーNMOSトランジスタの動作を説明する。

尚、図9はフィンガー数が3本の場合の例である。

尚、図9はフィンガー数が3本の場合の例である。

先ず、パッドに静電気放電パルスが印加されると、N型半導体であるドレイン部とP型半導体であるバックゲート部でアバランシェ・ブレークダウンが起こり、インパクト・イオン化により大量の電子−正孔対が発生し、電子はドレイン電界により引かれ、正孔はバックゲ−ト電位を上昇させるか、最低電位のソース電界に引かれる。バックゲート電位が、ソースをエミッタ、バックゲートをベース、ドレインをコレクタとする寄生NPNトランジスタのエミッタ−ベース間の順方向電圧より大きくなると、寄生NPNトランジスタが動作する。図9のVt1、It1はこの動作点である。寄生NPNトランジスタがONすると、ドレイン部の電流−電圧特性は寄生NMOSトランジスタのON抵抗に従ったものとなる。このとき注意すべき点は、以下の通りである。

マルチフィンガーNMOSトランジスタでは、各ゲート毎に複数のNMOSトランジスタが並列に接続されてなるが、レイアウト的に全てのNMOSトランジスタに同じ構造を用いても、様々な不均一性(多くはプロセス的な)のために全てのNMOSトランジスタの寄生NPNトランジスタが同時にONすることはなく、必ず、或る1つのNMOSトランジスタの寄生NPNトランジスタがONすることから動作が始まる。このとき、各NMOSトランジスタのドレイン部は共通に接続されているので、各ドレイン電圧は一番最初に寄生NPNトランジスタがONしたNMOSトランジスタのドレイン電圧に追従した動作をすることになる(図9の1stフィンガー)。

ドレイン電圧は動作している寄生NPNトランジスタのON抵抗に沿って上昇する。ON抵抗は、ソ−ス・ドレインの抵抗成分で、コンタクト抵抗、バラスト抵抗の値を含めたものとなる。ON抵抗での電圧上昇がVt1を超えると、2つ目のフィンガーで再びアバランシェ・ブレークダウンが起こり、バックゲート電位が上昇し、2つ目の寄生NPNトランジスタがONする。この結果、ON抵抗は2つの寄生NPNトランジスタのON抵抗の合成値となり、この抵抗に沿って3つ目の寄生NPNトランジスタがONするまで電位上昇が起こる。このようにして、全ての寄生NPNトランジスタを順次ONしていくことにより静電気放電パルスのエネルギーをON抵抗で消費される熱エネルギーに変換することで、MOSトランジスタのゲートを保護する。全ての寄生トランジスタがONすると、その合成ON抵抗に沿って電圧は上昇するが、熱暴走に至るまでに温度が上昇すると接合が損傷を受け(図9のVt2、It2)、接合でのリーク電流が増大する。

従って、熱暴走に至るまでに静電気放電エネルギーを全て消費することが必要である。

Layout DesignOn Multi-Finger MOS FET For On-Chip ESD Protection Circuits in a 0.18umSalicided CMOS Process, 2001 IEEE, Multi-Finger Turn-on Circuits and DesignTechniques For Enhanced ESD Performance and Width-Scaling, 2001 EOS/ESDSymposium, etc.

MarkusP.J.Merg ens,et al.,ESD/EOSSymposium 2001、ThomasL.Polgreen et al.,1992 IEEE

しかしながら、このような構成によるとソース・ドレイン抵抗の最適化が困難であるという問題がある。即ち、寄生NPNトランジスタを順次ONさせるためには、ドレイン部のバラスト抵抗は大きい方が、ドレイン電圧がより早くVt1に到達するため望ましいが、大き過ぎるバラスト抵抗値はジュール熱による温度上昇による接合損傷を生じさせる。従って、バラスト抵抗での温度上昇の面からは抵抗値が低い方が良いが、抵抗値を下げることでドレイン電圧がVt1に達するのに時間が掛かり、その期間の電流集中による損傷の問題も発生する。特に、シリサイド部分は粒子状であり、電流が局所的に集中し易いため、容易に熱的損傷を受ける。

これらのことから、ドレイン部の抵抗に最適な値が存在することは明らかであるが、ドレイン抵抗を構成するコンタクト抵抗、シリサイド部抵抗、シリサイド・ブロック領域(ドレイン・インプラント部)、更には、通常シリサイド・ブロック領域はマスクを用いるため、マスクずれの問題等、プロセスに非常に敏感であり、このため、静電気耐性にロットごとに差が生じるという問題もある。

本発明は、以上のような点に鑑みてなされたもので、プロセス変動に影響されにくく、且つ、マルチフィンガーNMOSトランジスタの寄生NPNトランジスタを、ほぼ同時にONさせるような静電気保護素子としてのマルチフィンガーNMOSトランジスタの構造を提供することを目的とする。

本発明は、以上のような点に鑑みてなされたもので、プロセス変動に影響されにくく、且つ、マルチフィンガーNMOSトランジスタの寄生NPNトランジスタを、ほぼ同時にONさせるような静電気保護素子としてのマルチフィンガーNMOSトランジスタの構造を提供することを目的とする。

前述のような問題は、ドレイン部における電圧を、いわばドレイン抵抗が監視し、ドレイン電圧がVt1を超えた時点でアバランシェ・ブレークダウンを起すことを繰返していく過程で生じていることに着目すると、静電気放電パルスが印加された直後のアバランシェ・ブレークダウンに伴うインパクトイオン化によるバックゲート電位上昇を大きくし、寄生のNPNトランジスタがほぼ同時にトリガーされる状況が望ましく、このためにはバックゲート電位を、如何に上昇させるかが重要である。

インパクトイオン化に伴うバックゲート電位上昇を効率的にするためには、バックゲートのインピーダンスを大きくすることが有効であり、最もインピーダンスを高くするにはフローティング状態が望ましいが、完全なフローティング状態はラッチアップを誘発し易いため、望ましくない。

又、P基板においては、フローティング状態を造ることは不可能である。このため、インピーダンスを高めるためには、基板方向ではなく保護素子の側面を基板と切り離すような構造が必要となる。

このために、CMOSプロセスにおいてPMOSトランジスタを製造する際に必須なN型のウェルによってNMOSトランジスタを取り囲むように構成し、

且つ、取り囲まれたP領域は底面のみで基板へ接続され、 金属配線では特定電位(殆どの場合最低電位)へ接続されないような構造とする。

且つ、取り囲まれたP領域は底面のみで基板へ接続され、 金属配線では特定電位(殆どの場合最低電位)へ接続されないような構造とする。

本発明によれば、マルチフィンガータイプの保護NMOSトランジスタをN型の拡散層で囲み、且つ、囲まれたバックゲート領域を金属配線で最低電位へ接続することなく基板との間に抵抗成分を持たせることで各フィンガー部の寄生NPNトランジスタのトリガー均一性を得ることができ、従来例のような1つの寄生NPNトランジスタへの電流集中を防ぎ、電流集中によるドレイン抵抗部の温度上昇を抑え、ジュール熱による接合破壊を防止することが可能になる。

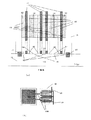

図1に本発明の実施の形態を示す。

図1はフィンガー数が4本の場合を示しているが、フィンガー数は多いほど2次ブレークダウン耐性が向上するので、通常は10本程度の場合が多い。

図1はフィンガー数が4本の場合を示しているが、フィンガー数は多いほど2次ブレークダウン耐性が向上するので、通常は10本程度の場合が多い。

図1(a)本発明の実施の形態の断面図、図1(b)は平面図である。

図1(a),(b)において、11はフィンガーとなるゲート、12はソース、13はドレイン、14はソース、ドレイン部の抵抗を下げるためのサリサイド、15はバラスト抵抗に相当するサリサイドブロック、16は保護NMOSトランジスタを囲繞するN型の拡散層Nウェル、17はフィールド酸化膜、18は1のフィンガーを電気的に接続する金属配線、19はフィンガーごとに構成されるソース12を電気的に接続し、且つ、最低電位接続するための金属配線、110はフィンガーごとに構成されれる3のドレインを電気的に接続し、且つ、パッド111へ接続する金属配線、112は金属配線によってはどの電位へも接続されていない保護NMOSトランジスタのバックゲートである。

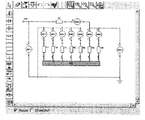

図2はシミュレーションで用いた回路図である。

図1(a),(b)において、11はフィンガーとなるゲート、12はソース、13はドレイン、14はソース、ドレイン部の抵抗を下げるためのサリサイド、15はバラスト抵抗に相当するサリサイドブロック、16は保護NMOSトランジスタを囲繞するN型の拡散層Nウェル、17はフィールド酸化膜、18は1のフィンガーを電気的に接続する金属配線、19はフィンガーごとに構成されるソース12を電気的に接続し、且つ、最低電位接続するための金属配線、110はフィンガーごとに構成されれる3のドレインを電気的に接続し、且つ、パッド111へ接続する金属配線、112は金属配線によってはどの電位へも接続されていない保護NMOSトランジスタのバックゲートである。

図2はシミュレーションで用いた回路図である。

図2において、NOはフィンガー数4のNMOSトランジスタを示しており、1はバックゲートで図1(a)のバックゲート112に相当する部分、2はゲートで図1(a)のゲート11へ、3,4,5はソースで図1(a)のソース12へ、6,7はドレインで図1(a)のドレイス13にそれぞれ相当する。R7はバックゲートと最低電位間のインピーダンス、R6はゲート抵抗、R1,R2,R4はソース直列抵抗、R3,R5はサリサイドブロック部のバラスト抵抗を含んだドレイン部の直列抵抗、VINは静電気放電パルスが印加される端子で、R0は人体帯電モデルの際の1.5kΩ抵抗を示す。

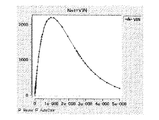

図3はシミュレーションで用いた人体帯電モデルの電圧波形図、図4(a),(b)はシミュレーションで用いたマルチフィンガーNMOSトランジスタの全体図及び1つのフィンガー部の拡大図である。

このような構造において、先ずパッド111へ静電気放電パルスが印加されると、配線10、サリサイド4を経由してドレイン部3の電位は急激に上昇する。人体帯電モデルでは、およそ200v/nsec、2000vmaxの波形が1.5kΩの抵抗を通してパッド111へ印加される。

急激に上昇したドレイン部の電圧は、バックゲートとの間でアバランシェ・ブレークダウンを起し、大量の電子−正孔対を生成し、生成された正孔がバックゲート電位を上昇させる。この電位がソース12をエミッタ、ドレイン13をコレクタ、バックゲート112をベースとする寄生NPNトランジスタのベース・エミッタ間順方向の閾値電圧を超えると寄生NPNトランジスタが動作し、図9に示すスナップバック特性を示すようになる。課題としているのは、フィンガー毎に存在する寄生のNPNトランジスタがほぼ同時にトリガーされ動作することであるが、図5及び図6にバックゲートへ接続される抵抗R7を0.1Ω、1kΩとした場合の各ドレイン電流波形を示している。

図5はR7=0.1Ωの場合であるが、具体的にはバックゲートが金属配線により最低電位へ接続された状態を表している。

ドレイン電流の一方は電流値がゼロであり、寄生NPNトランジスタが動作していないことが分かる。このことは、静電気放電パルスエネルギーを1つの寄生NPNトランジスタで消費しなくてはならず、この結果電流集中により、ドレイン抵抗に熱的損傷を引き起こすことを示している。

図6はR7=1kΩの場合であり、バックゲートはNウェルで囲まれ、基板方向のみで抵抗成分によって最低電位へ接続されている状態を示している。1〜2nsecの遅れ時間はあるが、2つのドレインにほぼ等しい電流が流れている、即ち、寄生NPNトランジスタがどちらも動作していることが分かり、この結果静電気放電パルスのエネルギーは両方の寄生NPNトランジスタでほぼ均等に消費されることを意味する。

図6はR7=1kΩの場合であり、バックゲートはNウェルで囲まれ、基板方向のみで抵抗成分によって最低電位へ接続されている状態を示している。1〜2nsecの遅れ時間はあるが、2つのドレインにほぼ等しい電流が流れている、即ち、寄生NPNトランジスタがどちらも動作していることが分かり、この結果静電気放電パルスのエネルギーは両方の寄生NPNトランジスタでほぼ均等に消費されることを意味する。

11 フィンガー(ゲート)

12 ドレイン

13 ソース

14 サリサイド

15 サリサイドブロック領域

16 N型拡散層

17 シリコン酸化膜

18 フィンガー配線

19 ソース配線

110 パッドからのドレイン配線

111 パッド

112 バックゲート

113 P型拡散層

12 ドレイン

13 ソース

14 サリサイド

15 サリサイドブロック領域

16 N型拡散層

17 シリコン酸化膜

18 フィンガー配線

19 ソース配線

110 パッドからのドレイン配線

111 パッド

112 バックゲート

113 P型拡散層

Claims (3)

- P型半導体基板上に構成される半導体集積回路の静電破壊保護素子であって、複数のゲート電極を有するマルチフィンガータイプのNMOSにおいて、

前記半導体基板と反対導電型の拡散層をNMOSトランジスタを囲繞するように構成し、且つ、囲繞されたP型半導体領域を配線手段によっては、如何なる電位へも接続されないことを特徴とするマルチフィンガーNMOSトランジスタ構造。 - 反対導電型の拡散層は、PMOSトランジスタがその内部に構成されるN型拡散層と同一の拡散層であることを特徴とする請求項1記載のマルチフィンガーNMOSトランジスタ構造。

- 複数のゲート電極は互いに電気的に接続され、且つ、囲繞されたP型半導体領域に金属配線で接続され、複数のドレイン電極は互いに電気的に接続され、且つ、外部引出し端子であるパッドへ金属配線で接続され、複数のソース電極は互いに電気的に接続され、且つ、最低電位配線へ接続されることを特徴とする請求項1記載のマルチフィンガーNMOSトランジスタ構造。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004111172A JP2005294740A (ja) | 2004-04-05 | 2004-04-05 | マルチフィンガーnmosトランジスタ構造 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004111172A JP2005294740A (ja) | 2004-04-05 | 2004-04-05 | マルチフィンガーnmosトランジスタ構造 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005294740A true JP2005294740A (ja) | 2005-10-20 |

Family

ID=35327296

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004111172A Withdrawn JP2005294740A (ja) | 2004-04-05 | 2004-04-05 | マルチフィンガーnmosトランジスタ構造 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005294740A (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2014112294A1 (ja) | 2013-01-18 | 2014-07-24 | セイコーインスツル株式会社 | 半導体装置 |

| TWI449157B (zh) * | 2009-02-25 | 2014-08-11 | Univ Chien Hsin Sci & Tech | 靜電防護結構 |

| JPWO2021140563A1 (ja) * | 2020-01-07 | 2021-07-15 |

-

2004

- 2004-04-05 JP JP2004111172A patent/JP2005294740A/ja not_active Withdrawn

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI449157B (zh) * | 2009-02-25 | 2014-08-11 | Univ Chien Hsin Sci & Tech | 靜電防護結構 |

| WO2014112294A1 (ja) | 2013-01-18 | 2014-07-24 | セイコーインスツル株式会社 | 半導体装置 |

| KR20150109359A (ko) | 2013-01-18 | 2015-10-01 | 세이코 인스트루 가부시키가이샤 | 반도체 장치 |

| JPWO2021140563A1 (ja) * | 2020-01-07 | 2021-07-15 | ||

| WO2021140563A1 (ja) * | 2020-01-07 | 2021-07-15 | 三菱電機株式会社 | 高周波半導体装置 |

| JP7239023B2 (ja) | 2020-01-07 | 2023-03-14 | 三菱電機株式会社 | 高周波半導体装置 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN102456687B (zh) | 半导体esd器件和方法 | |

| JP4290468B2 (ja) | 静電気放電保護素子 | |

| CN111009524B (zh) | 经过栅极提升的nmos esd保护装置 | |

| US7986011B2 (en) | Electrostatic discharge protection device | |

| JP2007235151A (ja) | 集積回路用の保護構造 | |

| JP2006319330A (ja) | 静電気放電保護装置 | |

| CN114783994A (zh) | 集成电路元件及在静电放电事件中的保护方法 | |

| JP2005045016A (ja) | 半導体集積回路 | |

| CN100444378C (zh) | 静电防护电路 | |

| KR101043238B1 (ko) | 고전압용 정전기 방전 보호 소자 | |

| US7145204B2 (en) | Guardwall structures for ESD protection | |

| US6949806B2 (en) | Electrostatic discharge protection structure for deep sub-micron gate oxide | |

| TWI278095B (en) | High voltage operating electrostatic discharge protection device | |

| JP2005294740A (ja) | マルチフィンガーnmosトランジスタ構造 | |

| CN103811482B (zh) | 静电放电保护电路 | |

| JP2006313880A (ja) | 静電気放電回路及びこれを有する集積回路 | |

| JP3123489B2 (ja) | 半導体集積回路における静電保護回路及びその製造方法 | |

| JP2008172216A (ja) | ウェル電位トリガによるesd保護 | |

| JP2007059543A (ja) | Esd保護回路及びesd保護回路製造方法 | |

| JP2005294691A (ja) | 半導体集積回路における静電気保護装置 | |

| KR100612948B1 (ko) | 낮은 항복전압을 갖는 정전기 보호회로의 트랜지스터 | |

| JP2009038189A (ja) | 半導体装置、電圧供給システムおよび半導体装置の製造方法 | |

| JP2007242965A (ja) | 半導体装置 | |

| JP4694123B2 (ja) | 静電気放電保護素子 | |

| KR20070058165A (ko) | 반도체 장치의 정전 방전 보호 소자 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20060201 |

|

| A300 | Withdrawal of application because of no request for examination |

Free format text: JAPANESE INTERMEDIATE CODE: A300 Effective date: 20070605 |