JP2005294548A - ネットワーク電子部品およびその製造方法 - Google Patents

ネットワーク電子部品およびその製造方法 Download PDFInfo

- Publication number

- JP2005294548A JP2005294548A JP2004107800A JP2004107800A JP2005294548A JP 2005294548 A JP2005294548 A JP 2005294548A JP 2004107800 A JP2004107800 A JP 2004107800A JP 2004107800 A JP2004107800 A JP 2004107800A JP 2005294548 A JP2005294548 A JP 2005294548A

- Authority

- JP

- Japan

- Prior art keywords

- thin film

- electronic component

- network electronic

- passive element

- film passive

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H10W72/012—

Landscapes

- Semiconductor Integrated Circuits (AREA)

Abstract

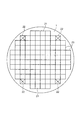

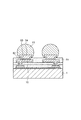

【解決手段】 ウエハ状態のシリコン基板1上の複数のネットワーク電子部品形成領域に対して、薄膜抵抗体3、接続パッド4、下地金属層9を含む配線10、柱状電極11および半田ボール13の形成を一括して行ない、その後にダイシングストリート23に沿って分断して複数個のネットワーク電子部品を得る。

【選択図】 図11

Description

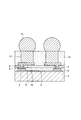

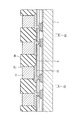

図1はこの発明の第1実施形態としてのネットワーク電子部品の等価回路的平面図を示す。このネットワーク電子部品では、平面正方形状のシリコン基板(半導体基板)1上に2つの薄膜抵抗素子(薄膜受動素子)2が相互に分離されて設けられている。この場合、薄膜抵抗素子2の両端部は、後述する柱状電極11からなる外部接続用電極に接続されている。

図13はこの発明の第2実施形態としてのネットワーク電子部品の等価回路的平面図を示す。このネットワーク電子部品では、平面正方形状のシリコン基板1上に1つの薄膜抵抗素子2と1つの薄膜容量素子(薄膜受動素子)31とからなるRC素子(ローパスフィルタ)が設けられている。この場合、薄膜抵抗素子2の両端部は、柱状電極からなる入力側および出力側の外部接続用電極32、33に接続されている。薄膜容量素子31の一端部は薄膜抵抗素子2の出力側に接続され、他端部は、柱状電極からなる入力側および出力側の外部接続用電極34、35に接続されている。

図16はこの発明の第3実施形態としてのネットワーク電子部品の等価回路的平面図を示す。このネットワーク電子部品では、シリコン基板1上に1つの薄膜抵抗素子2と2つの薄膜容量素子31が設けられている。この場合、薄膜抵抗素子2の両端部は、上側の2つの柱状電極11からなる外部接続用電極に接続されている。一方の薄膜容量素子31の両端部は、左側の2つの柱状電極11からなる外部接続用電極に接続されている。他方の薄膜容量素子31の両端部は、右側の2つの柱状電極11からなる外部接続用電極に接続されている。

例えば、上記第1実施形態では、図4に示すダイシングストリート23の全てに沿って切断し、図1に示すように、平面正方形状で2つの薄膜抵抗素子2を有するネットワーク電子部品を複数個得ているが、これに限定されるものではない。例えば、図4において、縦線からなるダイシングストリート23の全てに沿って切断し、且つ、横線からなるダイシングストリート23の1本おきに沿って切断すると、図17に示すこの発明の第4実施形態のように、平面長方形状で4つの薄膜抵抗素子2を有するネットワーク電子部品が複数個得られる。

また、図4において、縦線からなるダイシングストリート23の1本おきに沿って切断し、且つ、横線からなるダイシングストリート23の1本おきに沿って切断すると、図18に示すこの発明の第5実施形態のように、平面正方形状で8つの薄膜抵抗素子2を有するネットワーク電子部品が複数個得られる。

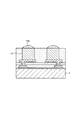

図19はこの発明の第6実施形態としてのネットワーク電子部品の断面図を示す。このネットワーク電子部品において、図3に示すネットワーク電子部品と異なる点は、半田ボール13の代わりに、柱状電極11の上面に半田層13aを設けた点である。

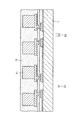

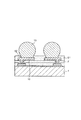

図20はこの発明の第7実施形態としてのネットワーク電子部品の断面図を示す。このネットワーク電子部品において、図3に示すネットワーク電子部品と異なる点は、柱状電極11および封止膜11を有せず、配線10を含む保護膜7の上面にソルダーレジスト等からなるオーバーコート膜51を設け、配線10の接続パッド部に対応する部分におけるオーバーコート膜51に開口部52を設け、開口部52を介して露出された配線10の接続パッド部(外部接続用電極)上に半田ボールを設けた点である。

図21はこの発明の第8実施形態としてのネットワーク電子部品の断面図を示す。このネットワーク電子部品において、図20に示すネットワーク電子部品と異なる点は、オーバーコート膜51の開口部52内およびその近傍のオーバーコート膜51の上面に銅等からなる下地金属層53および銅からなる上層接続パッド(外部接続用電極)54を配線10の接続パッド部に接続させて設け、下地金属層53を含む上層接続パッド54上に半田ボール13を設けた点である。

2 薄膜抵抗素子

3 薄膜抵抗体

4 接続パッド

5 絶縁膜

7 保護膜

10 配線

11 柱状電極

12 封止膜

13 半田ボール

Claims (21)

- 基板と、前記基板上に設けられた薄膜受動素子と、前記薄膜受動素子を含む前記基板上に前記薄膜受動素子に接続されて設けられた複数の外部接続用電極とを有することを特徴とするネットワーク電子部品。

- 請求項1に記載の発明において、前記基板は半導体基板であることを特徴とするネットワーク電子部品。

- 請求項1に記載の発明において、前記薄膜受動素子は抵抗素子であることを特徴とするネットワーク電子部品。

- 請求項1に記載の発明において、前記薄膜受動素子は容量素子であることを特徴とするネットワーク電子部品。

- 請求項1に記載の発明において、前記薄膜受動素子はRC素子であることを特徴とするネットワーク電子部品。

- 請求項1に記載の発明において、前記薄膜受動素子は複数であることを特徴とするネットワーク電子部品。

- 請求項1に記載の発明において、前記外部接続用電極は、前記薄膜受動素子を含む前記基板上に前記薄膜受動素子に接続されて設けられた配線の接続パッド部上に設けられた柱状電極であることを特徴とするネットワーク電子部品。

- 請求項1に記載の発明において、前記外部接続用電極は、前記薄膜受動素子を含む前記基板上に前記薄膜受動素子に接続されて設けられた配線の接続パッド部であることを特徴とするネットワーク電子部品。

- 請求項1に記載の発明において、前記外部接続用電極は、前記薄膜受動素子を含む前記基板上に前記薄膜受動素子に接続されて設けられた配線の接続パッド部上に設けられた上層接続パッドであることを特徴とするネットワーク電子部品。

- 請求項1に記載の発明において、前記外部接続用電極上に半田ボールが設けられていることを特徴とするネットワーク電子部品。

- 請求項1に記載の発明において、前記外部接続用電極上に半田層が設けられていることを特徴とするネットワーク電子部品。

- ウエハ状態の半導体基板上の複数のネットワーク電子部品形成領域にそれぞれ薄膜受動素子を形成する工程と、前記薄膜受動素子を含む前記ウエハ状態の半導体基板上の前記各ネットワーク電子部品形成領域にそれぞれ外部接続用電極を対応する前記薄膜受動素子に接続されて形成する工程と、前記ウエハ状態の半導体基板を切断して少なくとも1つのネットワーク電子部品形成領域を有するネットワーク電子部品を複数個得る工程とを有することを特徴とするネットワーク電子部品の製造方法。

- 請求項12に記載の発明において、前記薄膜受動素子は抵抗素子であることを特徴とするネットワーク電子部品の製造方法。

- 請求項12に記載の発明において、前記薄膜受動素子は容量素子であることを特徴とするネットワーク電子部品の製造方法。

- 請求項12に記載の発明において、前記薄膜受動素子はRC素子であることを特徴とするネットワーク電子部品の製造方法。

- 請求項12に記載の発明において、前記切断は、前記ネットワーク電子部品形成領域が偶数含まれるように切断することを特徴とするネットワーク電子部品の製造方法。

- 請求項12に記載の発明において、前記外部接続用電極は、前記薄膜受動素子を含む前記基板上に前記薄膜受動素子に接続されて設けられた配線の接続パッド部上に設けられた柱状電極であることを特徴とするネットワーク電子部品の製造方法。

- 請求項12に記載の発明において、前記外部接続用電極は、前記薄膜受動素子を含む前記基板上に前記薄膜受動素子に接続されて設けられた配線の接続パッド部であることを特徴とするネットワーク電子部品の製造方法。

- 請求項12に記載の発明において、前記外部接続用電極は、前記薄膜受動素子を含む前記基板上に前記薄膜受動素子に接続されて設けられた配線の接続パッド部上に設けられた上層接続パッドであることを特徴とするネットワーク電子部品の製造方法。

- 請求項12に記載の発明において、前記外部接続用電極上に半田ボールを形成する工程を有することを特徴とするネットワーク電子部品の製造方法。

- 請求項12に記載の発明において、前記外部接続用電極上に半田層を形成する工程を有することを特徴とするネットワーク電子部品の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004107800A JP2005294548A (ja) | 2004-03-31 | 2004-03-31 | ネットワーク電子部品およびその製造方法 |

| US11/093,571 US7808073B2 (en) | 2004-03-31 | 2005-03-30 | Network electronic component, semiconductor device incorporating network electronic component, and methods of manufacturing both |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004107800A JP2005294548A (ja) | 2004-03-31 | 2004-03-31 | ネットワーク電子部品およびその製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005294548A true JP2005294548A (ja) | 2005-10-20 |

Family

ID=35327138

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004107800A Pending JP2005294548A (ja) | 2004-03-31 | 2004-03-31 | ネットワーク電子部品およびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005294548A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008108935A (ja) * | 2006-10-26 | 2008-05-08 | Casio Comput Co Ltd | 半導体装置の製造方法 |

-

2004

- 2004-03-31 JP JP2004107800A patent/JP2005294548A/ja active Pending

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008108935A (ja) * | 2006-10-26 | 2008-05-08 | Casio Comput Co Ltd | 半導体装置の製造方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7022609B2 (en) | Manufacturing method of a semiconductor substrate provided with a through hole electrode | |

| US7782173B2 (en) | Chip resistor | |

| US7999189B2 (en) | Circuit board structure and method for fabricating the same | |

| CN106898448B (zh) | 片式电阻器及其制造方法 | |

| JP6606331B2 (ja) | 電子装置 | |

| CN104247584B (zh) | 印刷电路板及其制造方法 | |

| JP4716099B2 (ja) | チップ型ヒューズの製造方法 | |

| CN106449576B (zh) | 半导体装置封装及制造其的方法 | |

| JP3945380B2 (ja) | 半導体装置およびその製造方法 | |

| CN104160459A (zh) | 基板内置用芯片电阻器及其制造方法 | |

| CN111403602A (zh) | 垂直电容器结构、电容器组件,以及制造所述垂直电容器结构的方法 | |

| JP4632358B2 (ja) | チップ型ヒューズ | |

| CN106298710B (zh) | 基板结构及其制法暨导电结构 | |

| JP4752280B2 (ja) | チップ型電子部品およびその製造方法 | |

| JP2005294548A (ja) | ネットワーク電子部品およびその製造方法 | |

| CN108242296B (zh) | 贴片电阻器 | |

| TW201117334A (en) | Semiconductor device and manufacturing method thereof | |

| CN101506971B (zh) | 具有凸出电极的半导体元件和半导体组合装置 | |

| JP2006310277A (ja) | チップ型ヒューズ | |

| JP5137320B2 (ja) | 半導体装置およびその製造方法 | |

| JP2003151425A (ja) | チップ型電流ヒューズ及びその製造方法 | |

| JP2017175014A (ja) | 基板内層用チップ抵抗器、基板内層用チップ抵抗器の製造方法および部品内蔵型回路基板 | |

| JP4473087B2 (ja) | 半導体装置およびその製造方法 | |

| JP2006196811A (ja) | コンデンサおよびそれを用いた複合部品 | |

| JP2949072B2 (ja) | ボールグリッドアレイタイプ部品の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20060209 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20060314 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20071019 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20071030 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071226 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20080129 |