JP2005294360A - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP2005294360A JP2005294360A JP2004104041A JP2004104041A JP2005294360A JP 2005294360 A JP2005294360 A JP 2005294360A JP 2004104041 A JP2004104041 A JP 2004104041A JP 2004104041 A JP2004104041 A JP 2004104041A JP 2005294360 A JP2005294360 A JP 2005294360A

- Authority

- JP

- Japan

- Prior art keywords

- mos transistor

- film

- nisi

- semiconductor device

- manufacturing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/791—Arrangements for exerting mechanical stress on the crystal lattice of the channel regions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/285—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation

- H01L21/28506—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers

- H01L21/28512—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table

- H01L21/28518—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table the conductive layers comprising silicides

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/0212—Manufacture or treatment of FETs having insulated gates [IGFET] using self-aligned silicidation

-

- H10D64/0112—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0165—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including complementary IGFETs, e.g. CMOS devices

- H10D84/0172—Manufacturing their gate conductors

- H10D84/0174—Manufacturing their gate conductors the gate conductors being silicided

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/02—Manufacture or treatment characterised by using material-based technologies

- H10D84/03—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology

- H10D84/038—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology using silicon technology, e.g. SiGe

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/601—Insulated-gate field-effect transistors [IGFET] having lightly-doped drain or source extensions, e.g. LDD IGFETs or DDD IGFETs

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Electrodes Of Semiconductors (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Abstract

【課題】 NiSi膜のダイシリサイド化を抑制することのできる半導体装置の製造方法を提供する。

【解決手段】 P−MOSトランジスタ10およびN−MOSトランジスタ20双方のゲート電極12,22およびソース・ドレイン領域14,24上にNiSi膜42を形成する(シリサイド膜形成工程)。次に、NiSi膜42を含めた表面全体にダイレクト窒化膜44を形成する(窒化膜形成工程)。続いて、NiSi膜42の耐熱温度を高める元素をNiSi膜42に注入する(元素注入工程)。これにより、NiSi膜42の耐熱性が向上し、後工程における熱処理によりNiSi膜42がダイシリサイド化するのを抑制することができる。

【選択図】 図5

【解決手段】 P−MOSトランジスタ10およびN−MOSトランジスタ20双方のゲート電極12,22およびソース・ドレイン領域14,24上にNiSi膜42を形成する(シリサイド膜形成工程)。次に、NiSi膜42を含めた表面全体にダイレクト窒化膜44を形成する(窒化膜形成工程)。続いて、NiSi膜42の耐熱温度を高める元素をNiSi膜42に注入する(元素注入工程)。これにより、NiSi膜42の耐熱性が向上し、後工程における熱処理によりNiSi膜42がダイシリサイド化するのを抑制することができる。

【選択図】 図5

Description

本発明は、半導体装置の製造方法に関するものである。

従来の半導体装置の製造方法としては、例えば特許文献1に開示されたものがある。同文献に記載の製造方法は、素子の寄生抵抗を低減するために、MOSトランジスタのゲート電極上およびソース・ドレイン電極上にNiSiからなるモノシリサイド膜を形成する工程を含んでいる。

特開平5−90293号公報

しかしながら、上記製造方法においては、後工程における熱処理によりNiSi膜がダイシリサイド化するおそれがある。NiSi膜がダイシリサイド化した場合、MOSトランジスタの寄生抵抗の増大等につながってしまう。

本発明は、上記課題に鑑みてなされたものであり、半導体装置に用いられるNiSi膜の耐熱性を高め、ダイシリサイド化を抑制し、これにより半導体装置の性能を向上させることを目的とする。

上記課題を解決する本発明によれば、MOSトランジスタを備える半導体装置を製造する方法であって、前記MOSトランジスタのゲート電極およびソース・ドレイン領域の少なくとも一方の上にNiSi膜を形成するシリサイド膜形成工程と、前記NiSi膜のダイシリサイド化を抑制する反応抑制元素を前記NiSi膜に注入する元素注入工程と、を含むことを特徴とする半導体装置の製造方法が提供される。

この製造方法においては、元素注入工程において、NiSi膜のダイシリサイド化を抑制する反応抑制元素がNiSi膜中に導入される。これにより、NiSi膜の耐熱性が向上し、後工程における熱処理によりNiSi膜がダイシリサイド化するのを抑制することができる。

NiSi膜上にダイレクト窒化膜を形成する窒化膜形成工程を含み、元素注入工程においては、元素がNiSi膜に到達するように、ダイレクト窒化膜上から上記元素を注入してもよい。この場合、ダイシリサイド化の抑制とともに、ダイレクト窒化膜の応力を緩和することが可能となる。

本発明において、半導体装置は、P−MOSトランジスタおよびN−MOSトランジスタを備え、ダイレクト窒化膜はテンサイル応力を持つものであり、元素注入工程においては、P−MOSトランジスタおよびN−MOSトランジスタのうちP−MOSトランジスタに形成されたNiSi膜にのみ上記元素を注入してもよい。ダイレクト窒化膜がテンサイル応力を持つ場合、N−MOSトランジスタのオン電流が向上する一方で、P−MOSトランジスタのオン電流は低下してしまう。したがって、元素注入工程においてP−MOSトランジスタ側にのみ元素注入を行うことにより、テンサイル応力が緩和され、P−MOSトランジスタのオン電流の低下が抑制される。

本発明において、半導体装置は、P−MOSトランジスタおよびN−MOSトランジスタを備え、ダイレクト窒化膜はコンプレッシブ応力を持つものであり、元素注入工程においては、P−MOSトランジスタおよびN−MOSトランジスタのうちN−MOSトランジスタに形成されたNiSi膜にのみ上記元素を注入してもよい。ダイレクト窒化膜がコンプレッシブ応力を持つ場合、P−MOSトランジスタのオン電流が向上する一方で、N−MOSトランジスタのオン電流は低下してしまう。したがって、元素注入工程においてN−MOSトランジスタ側にのみ元素注入を行うことにより、コンプレッシブ応力が緩和され、N−MOSトランジスタのオン電流の低下が抑制される。

NiSi膜は、NiSiであってもよい。NiSiは抵抗が低いため、シリサイド膜として好適に機能することができる。

上記元素は、Ge、N、F、OおよびCからなる群より選ばれる1または2以上の元素であってもよい。これらの元素は、NiSi膜の耐熱温度の向上によるダイシリサイド化の抑制およびダイレクト窒化膜の応力緩和に資するものである。

本発明によれば、NiSi膜のダイシリサイド化を抑制することのできる半導体装置の製造方法が実現される。

以下、図面を参照しつつ、本発明による半導体装置の製造方法の好適な実施形態について詳細に説明する。なお、図面の説明においては、同一要素には同一符号を付し、重複する説明を省略する。

図1〜図6を用いて、本発明による半導体装置の製造方法の一実施形態を説明する。本実施形態において製造される半導体装置は、P−MOSトランジスタおよびN−MOSトランジスタを備えるCMOSトランジスタ装置である。

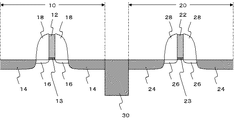

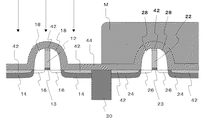

まず、図1に示すように、P−MOSトランジスタ10およびN−MOSトランジスタ20を形成する。P−MOSトランジスタ10は、ゲート電極12、ゲート酸化膜13、ソース・ドレイン領域14、LDD(Lightly Doped Drain)領域16およびスペーサ18を有している。同様に、N−MOSトランジスタ20は、ゲート電極22、ゲート酸化膜23、ソース・ドレイン領域24、LDD領域26およびスペーサ28を有している。P−MOSトランジスタ10とN−MOSトランジスタ20とは、素子分離領域であるSTI(シャロートレンチアイソレーション)領域30によって互いに分離されている。

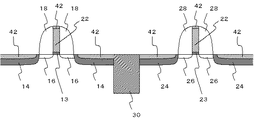

次に、図2に示すように、P−MOSトランジスタ10およびN−MOSトランジスタ20双方のゲート電極12,22およびソース・ドレイン領域14,24上にモノシリサイド膜としてNiSi膜42を形成する(シリサイド膜形成工程)。ただし、NiSi膜42は、ゲート電極12,22およびソース・ドレイン領域のうち何れか一方にのみ形成してもよい。

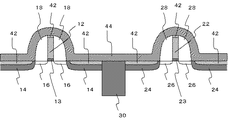

次に、図3に示すように、NiSi膜42を含めた表面全体にダイレクト窒化膜44(層間窒化膜)を形成する(窒化膜形成工程)。このダイレクト窒化膜44は、後述する層間酸化膜46と共に層間絶縁膜を構成するものである。また、本実施形態においてダイレクト窒化膜44は、テンサイル応力を持っている。ダイレクト窒化膜44としては、例えばSiNを用いることができる。

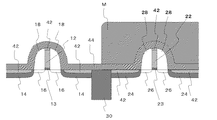

次に、図4に示すように、フォトレジストを用いてN−MOSトランジスタ20全体にマスクMを形成する。

続いて、図5に示すように、NiSi膜42の耐熱温度を高める元素(以下、反応抑制元素という)をNiSi膜42に注入する(元素注入工程)。このとき、N−MOSトランジスタ20側はマスクMにより覆われているため、P−MOSトランジスタ10側にのみ反応抑制元素が注入される。注入条件は、反応抑制元素がNiSi膜42まで到達するように設定される。反応抑制元素としては、例えばGe、N、F、OおよびCが挙げられる。これらの元素は、NiSi膜42の耐熱温度を高め、ダイシリサイド化反応を抑制する働きを有する上、ダイレクト窒化膜44の応力を緩和することもできる。なお、反応抑制元素のうち何れか1つを注入してもよく、複数組み合わせて注入してもよい。

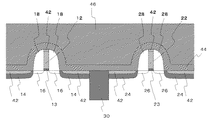

最後に、図6に示すように、ダイレクト窒化膜44上に層間酸化膜46を形成する。層間酸化膜46としては、例えばSiO2を用いることができる。

本実施形態に係る製造方法の効果を説明する。

上記製造方法においては、元素注入工程において反応抑制元素をNiSi膜42に注入している。これにより、NiSi膜42の耐熱性が向上し、後工程における熱処理によりNiSi膜42がダイシリサイド化するのを抑制することができる。NiSi2はNiSiに比してシート抵抗値が高いため、NiSiのダイシリサイド化を防ぐことは、素子の寄生抵抗を低減する上で非常に重要である。また、NiSiのダイシリサイド化はリーク電流の増大にもつながるが、上記製造方法によれば、このようなリーク電流の増大をも抑制することができる。

また、NiSi膜42への反応抑制元素の導入を、NiSi膜42の形成後に注入を行うことにより実行している。このため、P−MOSトランジスタ10への注入量とN−MOSトランジスタ20への注入量とを別々に制御することが容易となる。例えば、本実施形態においては、マスクMを用いることにより、P−MOSトランジスタ10およびN−MOSトランジスタ20のうちP−MOSトランジスタ10に形成されたNiSi膜42にのみ注入を行うことを容易に実現している。

ところで、NiSi膜に反応抑制元素を導入する方法としては、Ni膜成膜時のスパッタガスに反応抑制元素を混入させることも考えられる。しかし、その方法は、P−MOSトランジスタ10側のNiSi膜42とN−MOSトランジスタ20側のNiSi膜42とでNiSi膜42に反応抑制元素の導入量を別々に制御することができないため、好ましくない。しかも、例えばN−MOSトランジスタ20側に不純物元素としてAsが導入されている場合、AsもまたNiSiの耐熱温度を高める働きを持つ元素であるため、スパッタによりP−MOSトランジスタ10側とN−MOSトランジスタ20側とに同量の反応抑制元素を導入してしまうと、結果として、NiSiの耐熱温度を高める元素がP−MOSトランジスタ10側に比してN−MOSトランジスタ20側により多く導入されることになる。すると、NiSi膜を形成する際に、P−MOSトランジスタ10およびN−MOSトランジスタ20間で反応温度のバランスが取りにくくなってしまうという問題がある。

これに対して、NiSi膜42の形成後に反応抑制元素の注入を行う本実施形態によれば、NiSi膜42の形成時には反応抑制元素が未だ導入されていないため、かかる問題を防ぐことができる。

さらに、元素注入工程においては、反応抑制元素がNiSi膜42まで到達するような注入条件に設定される。ここで、基板への導入ダメージやゲート酸化膜への影響を考慮すると、基板やゲート酸化膜には反応抑制元素が注入されないことが望ましい。この点、注入は金属中では止まり易いため、反応抑制元素がNiSi膜42中で止まるように注入条件を設定することは容易である。

特に、本実施形態においては、ダイレクト窒化膜44上から反応抑制元素を注入している。これにより、NiSi膜42のダイシリサイド化の抑制とともに、ダイレクト窒化膜44の応力を緩和することができる。

また、P−MOSトランジスタ10に形成されたNiSi膜42にのみ反応抑制元素を注入している。ダイレクト窒化膜44は、テンサイル応力を持っているため、N−MOSトランジスタのオン電流を向上させる一方で、P−MOSトランジスタのオン電流を低下させる。したがって、P−MOSトランジスタ10側にのみ元素注入を行うことにより、P−MOSのオン電流の低下を抑制することができる。

なお、上記実施形態においてはテンサイル応力を持つダイレクト窒化膜を用い、P−MOSトランジスタ10側にのみ反応抑制元素を注入する例を示したが、コンプレッシブ応力を持つダイレクト窒化膜を用い、N−MOSトランジスタ20側にのみ反応抑制元素を注入することとしてもよい。

また、本実施形態においては、ダイレクト窒化膜44と層間酸化膜46とを積層させた構造の層間絶縁膜を形成している。これにより、コンタクト形成等のため層間絶縁膜をエッチングする際に、ダイレクト窒化膜44をエッチングストッパとして機能させることができる。ただし、ダイレクト窒化膜44を設けることは必須ではない。ダイレクト窒化膜44を設けない場合すなわち窒化膜形成工程を省略する場合には、シリサイド膜形成工程の直後に元素注入工程を実行すればよい。このとき、P−MOSトランジスタ10側およびN−MOSトランジスタ20側の双方に反応抑制元素を注入してもよく、何れか一方にのみ注入してもよい。

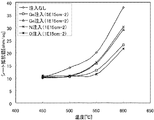

図7は、NiSi膜に反応抑制元素を注入した場合および注入しない場合それぞれについて、NiSi膜の耐熱温度を測定したグラフである。反応抑制元素の注入は、ダイレクト窒化膜上から行った。ここでいう耐熱温度とは、NiSi膜が、ダイシリサイド化すなわちNiSi2膜に変化するときの温度である。グラフの縦軸はシート抵抗値(Ω/□)を表し、横軸は温度(℃)を表す。ニッケルがダイシリサイド化するとシート抵抗値が増大することから、注入なしの場合の耐熱温度が約450℃であるのに対し、反応抑制元素を注入した場合の耐熱温度は500℃以上であることが判る。したがって、反応抑制元素を注入することにより、NiSi膜の耐熱性を向上させることができ、それによりNiSi膜のダイシリサイド化を抑制することができる。

10 P−MOSトランジスタ

12 ゲート電極

13 ゲート酸化膜

14 ソース・ドレイン領域

16 LDD領域

18 スペーサ

20 N−MOSトランジスタ

22 ゲート電極

23 ゲート酸化膜

24 ソース・ドレイン領域

26 LDD領域

28 スペーサ

30 STI領域

42 SiNi膜

44 ダイレクト窒化膜

46 層間酸化膜

12 ゲート電極

13 ゲート酸化膜

14 ソース・ドレイン領域

16 LDD領域

18 スペーサ

20 N−MOSトランジスタ

22 ゲート電極

23 ゲート酸化膜

24 ソース・ドレイン領域

26 LDD領域

28 スペーサ

30 STI領域

42 SiNi膜

44 ダイレクト窒化膜

46 層間酸化膜

Claims (5)

- MOSトランジスタを備える半導体装置を製造する方法であって、

前記MOSトランジスタのゲート電極およびソース・ドレイン領域の少なくとも一方の上にNiSi膜を形成するシリサイド膜形成工程と、

前記NiSi膜のダイシリサイド化を抑制する反応抑制元素を前記NiSi膜に注入する元素注入工程と、

を含むことを特徴とする半導体装置の製造方法。 - 請求項1に記載の半導体装置の製造方法であって、

前記NiSi膜上に層間窒化膜を形成する窒化膜形成工程を含み、

前記元素注入工程においては、前記元素が前記NiSi膜に到達するように、前記層間窒化膜上から前記元素を注入することを特徴とする半導体装置の製造方法。 - 請求項2に記載の半導体装置の製造方法であって、

前記半導体装置は、P−MOSトランジスタおよびN−MOSトランジスタを備え、

前記層間窒化膜はテンサイル応力を持つものであり、

前記元素注入工程においては、前記P−MOSトランジスタおよび前記N−MOSトランジスタのうち前記P−MOSトランジスタに形成された前記NiSi膜にのみ前記元素を注入することを特徴とする半導体装置の製造方法。 - 請求項2に記載の半導体装置の製造方法であって、

前記半導体装置は、P−MOSトランジスタおよびN−MOSトランジスタを備え、

前記層間窒化膜はコンプレッシブ応力を持つものであり、

前記元素注入工程においては、前記P−MOSトランジスタおよび前記N−MOSトランジスタのうち前記N−MOSトランジスタに形成された前記NiSi膜にのみ前記元素を注入することを特徴とする半導体装置の製造方法。 - 請求項1〜4の何れか一項に記載の半導体装置の製造方法であって、

前記反応抑制元素は、Ge、N、F、OおよびCからなる群より選ばれる1または2以上の元素であることを特徴とする半導体装置の製造方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004104041A JP2005294360A (ja) | 2004-03-31 | 2004-03-31 | 半導体装置の製造方法 |

| CNB2005100625263A CN100377322C (zh) | 2004-03-31 | 2005-03-29 | 制造半导体器件的方法 |

| US11/094,393 US7348273B2 (en) | 2004-03-31 | 2005-03-31 | Method of manufacturing a semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004104041A JP2005294360A (ja) | 2004-03-31 | 2004-03-31 | 半導体装置の製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005294360A true JP2005294360A (ja) | 2005-10-20 |

Family

ID=35050044

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004104041A Pending JP2005294360A (ja) | 2004-03-31 | 2004-03-31 | 半導体装置の製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7348273B2 (ja) |

| JP (1) | JP2005294360A (ja) |

| CN (1) | CN100377322C (ja) |

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2007055095A1 (ja) * | 2005-11-14 | 2007-05-18 | Nec Corporation | 半導体装置およびその製造方法 |

| WO2007074775A1 (ja) * | 2005-12-26 | 2007-07-05 | Nec Corporation | Nmosfet及びその製造方法並びにcmosfet及びその製造方法 |

| WO2007077814A1 (ja) * | 2006-01-06 | 2007-07-12 | Nec Corporation | 半導体装置及びその製造方法 |

| WO2007122667A1 (ja) * | 2006-03-29 | 2007-11-01 | Fujitsu Limited | 半導体装置及びその製造方法 |

| JP2007294496A (ja) * | 2006-04-21 | 2007-11-08 | Renesas Technology Corp | 半導体装置及びその製造方法 |

| WO2008035490A1 (en) * | 2006-09-20 | 2008-03-27 | Nec Corporation | Semiconductor device and method for manufacturing same |

| JP2009522796A (ja) * | 2006-01-09 | 2009-06-11 | インターナショナル・ビジネス・マシーンズ・コーポレーション | 同じ基板上に同じ導電型の低性能及び高性能デバイスを有する半導体デバイス構造体 |

| WO2009157042A1 (ja) * | 2008-06-26 | 2009-12-30 | 富士通マイクロエレクトロニクス株式会社 | 半導体装置とその製造方法 |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7297584B2 (en) * | 2005-10-07 | 2007-11-20 | Samsung Electronics Co., Ltd. | Methods of fabricating semiconductor devices having a dual stress liner |

| JP4755894B2 (ja) * | 2005-12-16 | 2011-08-24 | 株式会社東芝 | 半導体装置およびその製造方法 |

| US7473623B2 (en) * | 2006-06-30 | 2009-01-06 | Advanced Micro Devices, Inc. | Providing stress uniformity in a semiconductor device |

| US8470700B2 (en) * | 2010-07-22 | 2013-06-25 | Globalfoundries Singapore Pte. Ltd. | Semiconductor device with reduced contact resistance and method of manufacturing thereof |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001250791A (ja) * | 2000-03-03 | 2001-09-14 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| JP2001352058A (ja) * | 2000-06-09 | 2001-12-21 | Toshiba Corp | 半導体装置の製造方法 |

| WO2002043151A1 (fr) * | 2000-11-22 | 2002-05-30 | Hitachi, Ltd | Dispositif a semi-conducteur et procede de fabrication correspondant |

| JP2002184717A (ja) * | 2000-10-02 | 2002-06-28 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0590293A (ja) | 1991-07-19 | 1993-04-09 | Toshiba Corp | 半導体装置およびその製造方法 |

| US5937315A (en) * | 1997-11-07 | 1999-08-10 | Advanced Micro Devices, Inc. | Self-aligned silicide gate technology for advanced submicron MOS devices |

| US6180469B1 (en) * | 1998-11-06 | 2001-01-30 | Advanced Micro Devices, Inc. | Low resistance salicide technology with reduced silicon consumption |

| US6274511B1 (en) * | 1999-02-24 | 2001-08-14 | Advanced Micro Devices, Inc. | Method of forming junction-leakage free metal silicide in a semiconductor wafer by amorphization of refractory metal layer |

| US6255214B1 (en) * | 1999-02-24 | 2001-07-03 | Advanced Micro Devices, Inc. | Method of forming junction-leakage free metal silicide in a semiconductor wafer by amorphization of source and drain regions |

| US6586333B1 (en) * | 2000-10-05 | 2003-07-01 | Advanced Micro Devices, Inc. | Integrated plasma treatment and nickel deposition and tool for performing same |

| US6890854B2 (en) * | 2000-11-29 | 2005-05-10 | Chartered Semiconductor Manufacturing, Inc. | Method and apparatus for performing nickel salicidation |

| US6605513B2 (en) * | 2000-12-06 | 2003-08-12 | Advanced Micro Devices, Inc. | Method of forming nickel silicide using a one-step rapid thermal anneal process and backend processing |

| US6444578B1 (en) * | 2001-02-21 | 2002-09-03 | International Business Machines Corporation | Self-aligned silicide process for reduction of Si consumption in shallow junction and thin SOI electronic devices |

| US6689688B2 (en) * | 2002-06-25 | 2004-02-10 | Advanced Micro Devices, Inc. | Method and device using silicide contacts for semiconductor processing |

| JP4585510B2 (ja) * | 2003-03-07 | 2010-11-24 | 台湾積體電路製造股▲ふん▼有限公司 | シャロートレンチアイソレーションプロセス |

| US20050090067A1 (en) * | 2003-10-27 | 2005-04-28 | Dharmesh Jawarani | Silicide formation for a semiconductor device |

| US6977194B2 (en) * | 2003-10-30 | 2005-12-20 | International Business Machines Corporation | Structure and method to improve channel mobility by gate electrode stress modification |

| US7262105B2 (en) * | 2003-11-21 | 2007-08-28 | Freescale Semiconductor, Inc. | Semiconductor device with silicided source/drains |

| US7105429B2 (en) * | 2004-03-10 | 2006-09-12 | Freescale Semiconductor, Inc. | Method of inhibiting metal silicide encroachment in a transistor |

| US7078285B1 (en) * | 2005-01-21 | 2006-07-18 | Sony Corporation | SiGe nickel barrier structure employed in a CMOS device to prevent excess diffusion of nickel used in the silicide material |

-

2004

- 2004-03-31 JP JP2004104041A patent/JP2005294360A/ja active Pending

-

2005

- 2005-03-29 CN CNB2005100625263A patent/CN100377322C/zh not_active Expired - Fee Related

- 2005-03-31 US US11/094,393 patent/US7348273B2/en not_active Expired - Fee Related

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001250791A (ja) * | 2000-03-03 | 2001-09-14 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| JP2001352058A (ja) * | 2000-06-09 | 2001-12-21 | Toshiba Corp | 半導体装置の製造方法 |

| JP2002184717A (ja) * | 2000-10-02 | 2002-06-28 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| WO2002043151A1 (fr) * | 2000-11-22 | 2002-05-30 | Hitachi, Ltd | Dispositif a semi-conducteur et procede de fabrication correspondant |

Cited By (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7786537B2 (en) | 2005-11-14 | 2010-08-31 | Nec Corporation | Semiconductor device and method for manufacturing same |

| WO2007055095A1 (ja) * | 2005-11-14 | 2007-05-18 | Nec Corporation | 半導体装置およびその製造方法 |

| JP5056418B2 (ja) * | 2005-11-14 | 2012-10-24 | 日本電気株式会社 | 半導体装置およびその製造方法 |

| WO2007074775A1 (ja) * | 2005-12-26 | 2007-07-05 | Nec Corporation | Nmosfet及びその製造方法並びにcmosfet及びその製造方法 |

| WO2007077814A1 (ja) * | 2006-01-06 | 2007-07-12 | Nec Corporation | 半導体装置及びその製造方法 |

| JPWO2007077814A1 (ja) * | 2006-01-06 | 2009-06-11 | 日本電気株式会社 | 半導体装置及びその製造方法 |

| US7968947B2 (en) | 2006-01-06 | 2011-06-28 | Nec Corporation | Semiconductor device and manufacturing process therefor |

| JP2009522796A (ja) * | 2006-01-09 | 2009-06-11 | インターナショナル・ビジネス・マシーンズ・コーポレーション | 同じ基板上に同じ導電型の低性能及び高性能デバイスを有する半導体デバイス構造体 |

| WO2007122667A1 (ja) * | 2006-03-29 | 2007-11-01 | Fujitsu Limited | 半導体装置及びその製造方法 |

| JP2007294496A (ja) * | 2006-04-21 | 2007-11-08 | Renesas Technology Corp | 半導体装置及びその製造方法 |

| JPWO2008035490A1 (ja) * | 2006-09-20 | 2010-01-28 | 日本電気株式会社 | 半導体装置およびその製造方法 |

| US7875935B2 (en) | 2006-09-20 | 2011-01-25 | Nec Corporation | Semiconductor device and method for manufacturing the same |

| WO2008035490A1 (en) * | 2006-09-20 | 2008-03-27 | Nec Corporation | Semiconductor device and method for manufacturing same |

| WO2009157042A1 (ja) * | 2008-06-26 | 2009-12-30 | 富士通マイクロエレクトロニクス株式会社 | 半導体装置とその製造方法 |

| US8399345B2 (en) | 2008-06-26 | 2013-03-19 | Fujitsu Semiconductor Limited | Semiconductor device having nickel silicide layer |

| JP5310722B2 (ja) * | 2008-06-26 | 2013-10-09 | 富士通セミコンダクター株式会社 | 半導体装置の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20050250326A1 (en) | 2005-11-10 |

| CN100377322C (zh) | 2008-03-26 |

| US7348273B2 (en) | 2008-03-25 |

| CN1677627A (zh) | 2005-10-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4937253B2 (ja) | コンタクト絶縁層および異なる特性を有するシリサイド領域を形成するための技法 | |

| CN101809713B (zh) | 阻止晶体管栅极电极的预非晶化 | |

| JP3523151B2 (ja) | Mosトランジスタの製造方法 | |

| US20100001317A1 (en) | Cmos transistor and the method for manufacturing the same | |

| US7902082B2 (en) | Method of forming field effect transistors using diluted hydrofluoric acid to remove sacrificial nitride spacers | |

| US7795644B2 (en) | Integrated circuits with stress memory effect and fabrication methods thereof | |

| US8084826B2 (en) | Semiconductor device and manufacturing method thereof | |

| US20090101979A1 (en) | Methods of Forming Field Effect Transistors Having Stress-Inducing Sidewall Insulating Spacers Thereon and Devices Formed Thereby | |

| JP2005294360A (ja) | 半導体装置の製造方法 | |

| CN102569394B (zh) | 晶体管及其制作方法 | |

| JP6996858B2 (ja) | 半導体装置及びその製造方法 | |

| US20080237734A1 (en) | Complementary metal-oxide-semiconductor transistor and method of fabricating the same | |

| JP2007103642A (ja) | 半導体装置およびその製造方法 | |

| KR100773352B1 (ko) | 스트레스 인가 모스 트랜지스터를 갖는 반도체소자의제조방법 및 그에 의해 제조된 반도체소자 | |

| US20060263992A1 (en) | Method of forming the N-MOS and P-MOS gates of a CMOS semiconductor device | |

| CN106558491A (zh) | 一种半导体器件及其制造方法、电子装置 | |

| US20050282324A1 (en) | Semiconductor device containing distorted silicon layer formed on silicon germanium layer | |

| CN101140954A (zh) | 半导体器件 | |

| US6342440B1 (en) | Method for forming low-leakage impurity regions by sequence of high-and low-temperature treatments | |

| US8574993B2 (en) | Semiconductor device and method of manufacturing the same | |

| JP2007214208A (ja) | 半導体装置及びその製造方法 | |

| JP4152265B2 (ja) | 半導体装置の製造方法 | |

| JP2008103644A (ja) | 半導体装置およびその製造方法 | |

| JPH0964349A (ja) | 高融点シリサイドを持つ半導体装置とその製造方法 | |

| CN100424841C (zh) | 制造半导体器件的方法及移除间隙壁的方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070208 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080827 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110104 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110426 |