JP2005293751A - 半導体メモリ - Google Patents

半導体メモリ Download PDFInfo

- Publication number

- JP2005293751A JP2005293751A JP2004109059A JP2004109059A JP2005293751A JP 2005293751 A JP2005293751 A JP 2005293751A JP 2004109059 A JP2004109059 A JP 2004109059A JP 2004109059 A JP2004109059 A JP 2004109059A JP 2005293751 A JP2005293751 A JP 2005293751A

- Authority

- JP

- Japan

- Prior art keywords

- pair

- power supply

- semiconductor memory

- pseudo

- memory cell

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Static Random-Access Memory (AREA)

Abstract

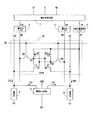

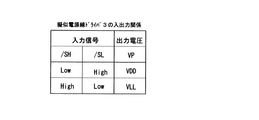

【解決手段】 メモリセル10と、擬似電源線VPと、一対の擬似GND線VG,/VGと、一対のビット線BL,/BLに接続された一対の書込みバッファ2と、電流センス回路5とを有する半導体メモリにおいて、VDDとVLL(VDD>VLL)の電源をもち、書込みバッファ2のHigh出力レベルを読み出し時はVDDに、書込み時はVLLに切り替え、擬似電源線VPのレベルを読み出し時はVDDに、書込み時はVLLに切り替える。

【選択図】 図1

Description

図10の従来例において、メモリセル10に記憶されたデータ“1”を出力端子DOに読み出す動作は以下の通りである。読出し動作を通じて、書込要求信号WEは非書込み状態(GNDレベル)である。

IR1+IS1=IR2+IS2

上述の例では、「IR2>0かつIR1=0」であるので、電流センス回路5の入力信号には「IS1>IS2>0」の関係がある。これを電流センス回路5は検出して、データ“1”に相当するVDDレベルの信号を出力端子DOから出力する。

データ“1”が記憶された図10のメモリセル10に、入力端子DIから入力された逆データ“0”を書き込む動作について以下に述べる。書込み動作を通じて、活性化信号SAEは非活性状態(GNDレベル)である。

図1の実施例1において、スタンバイ状態すなわちメモリセルアレイに対してデータの読出しも書込みも行わない状態における各部の電位関係について、以下に説明する。書込要求信号WEは非書込み状態(GNDレベル)、活性化信号SAEは非活性状態(GNDレベル)、凝似電源線VPはVLLレベルである。ワード線WLは非選択状態(GNDレベル)、ビット線BL,/BLはVLLレベル、擬似GND線VG,/VGはGNDレベルである。メモリセル10内のMOSFETに関しては、Q1,Q4は導通状態、Q2,Q3,Q5,Q6は非導通状態である。

図1の実施例1において、メモリセル10に記憶されたデータ“1”を出力端子DOに読み出す動作は以下の通りである。読出し動作を通じて、書込要求信号WEは非書込み状態(GNDレベル)である。

データ“1”が記憶された図1のメモリセル10に、入力端子DIから入力された逆データ“0”を書き込む動作について以下に述べる。書込み動作を通じて、活性化信号SAEは非活性状態(GNDレベル)、擬似電源線VPはVLLレベルである。

(VDD−Vthn)/VDD

に低減できる。ここで、VthnはnMOSFETの閾値電圧である。

(VLL−Vthn)/VLL

に低減できる。

VLL>max(Vthn,|Vthp|)

で与えられる。このような低動作電圧条件では、書込みバッファ2の駆動力が低下する為に、ビット線BL,/BLをLowレベルに制御してもメモリセル10内のフリップフロップ回路を反転できないという現象が発生する。実施例2は、上記の問題に対処するものである。

2,2’:書込みバッファ

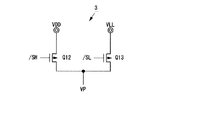

3:擬似電源線ドライバ

3’:固定電源

4:高抵抗

5:電流センス回路

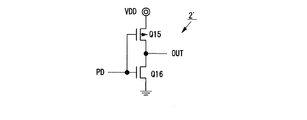

6:低電圧プルアップ回路

7:リセット回路

8:電流制限抵抗

10:メモリセル

WL:ワード線

BL,/BL:ビット線ペア

VG,/VG:擬似GND線ペア

VP:擬似電源線

Q1,Q2,Q7,Q10,Q11,Q12,Q13,Q14,Q15:pMOSFET

Q3,Q4,Q5,Q6,Q7’,Q8,Q9,Q9’,Q10’,Q11’,Q11”,Q11”’,Q16:nMOSFET

INV1,INV2,INV3:インバータ

OR1:オアゲート

Y:コラム選択信号、入力端子、

SAE:活性化信号、入力端子

WE:書込要求信号、入力端子

DI:データの入力端子

DO:出力データ、出力端子

/PUH:ビット線のHighレベルプルアップ信号

/PUL:ビット線のLowレベルプルアップ信号

PD:ビット線のプルダウン信号

/RST:リセット信号

/SH:擬似電源線のHighレベル制御信号

/SL:擬似電源線のLowレベル制御信号

SF:擬似電源線の開放(フローティング)制御信号

N1,N2,G1,G2,T1,T2,T3,T4:回路節点

Claims (7)

- 一対の負荷用MOSFETおよび一対の駆動用MOSFETからなるフリップフロップ回路並びに該フリップフロップ回路の一方と他方の入出力側にそれぞれ接続した一対のセル選択用MOSFETからなるメモリセルと、前記一対のセル選択用MOSFETの前記フリップフロップ回路に接続される側と反対のドレイン又はソースにそれぞれ接続した一対のビット線と、前記一対の負荷用MOSFETのソースに共通接続した擬似電源線と、前記一対の駆動用MOSFETのソースにそれぞれ接続した一対の擬似GND線と、前記一対のビット線にそれぞれ接続した一対の書込みバッファと、前記一対の擬似GND線に共通接続した電流センス回路とを有する半導体メモリにおいて、

出力電圧が異なる第1および第2の電源と、前記各書込みバッファのHigh出力レベルを前記第1又は第2の電源の電圧に対応する電圧に個々に切り替える手段と、前記擬似電源線のレベルを前記第1又は第2電源の電圧に対応する電圧に切り替える手段を設けたことを特徴とする半導体メモリ。 - 請求項1に記載の半導体メモリにおいて、

前記擬似電源線を開放状態にする手段を設けたことを特徴とする半導体メモリ。 - 請求項1又は2に記載の半導体メモリにおいて、

スタンバイ状態時に、前記擬似電源線と前記一対のビット線を、前記第1および第2の電源のうちの低い電圧の電源に対応する第1のHighレベルに制御する手段を設けたことを特徴とする半導体メモリ。 - 請求項1又は2に記載の半導体メモリにおいて、

メモリセルからのデータの読み出しの際に、当該メモリセルの擬似電源線と一対のビット線を、前記第1および第2の電源のうちの高い電圧の電源に対応する第2のHighレベルに制御し、非選択状態のメモリセルの擬似電源線と一対のビット線を、前記第1および第2の電源のうちの低い電圧の電源に対応する第1のHighレベルに制御する手段を設けたことを特徴とする半導体メモリ。 - 請求項1に記載の半導体メモリにおいて、

メモリセルへのデータの書き込みの際に、当該メモリセルの擬似電源線と一対のビット線のうちのHigh側ビット線を、前記第1および第2の電源のうちの低い電圧の電源に対応する第1のHighレベルに制御する手段を設けたことを特徴とする半導体メモリ。 - 請求項1に記載の半導体メモリにおいて、

前記擬似電源線を開放状態にする手段を設け、

メモリセルへのデータの書込みの際に、当該メモリセルの擬似電源線を開放状態に制御し、かつ当該メモリセルの一対のビット線のうちのHigh側ビット線を、前記第1および第2の電源のうちの低い電圧の電源に対応する第1のHighレベルに制御する手段を設けたことを特徴とする半導体メモリ。 - 請求項3乃至6のいずれか1つに記載の半導体メモリにおいて、

前記第1のHighレベルに制御する手段に前記第1の電源を使用し、前記第2のHighレベルに制御する手段に前記第2の電源を使用することを特徴とする半導体メモリ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004109059A JP2005293751A (ja) | 2004-04-01 | 2004-04-01 | 半導体メモリ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004109059A JP2005293751A (ja) | 2004-04-01 | 2004-04-01 | 半導体メモリ |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005293751A true JP2005293751A (ja) | 2005-10-20 |

Family

ID=35326512

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004109059A Pending JP2005293751A (ja) | 2004-04-01 | 2004-04-01 | 半導体メモリ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005293751A (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7826298B2 (en) | 2007-05-24 | 2010-11-02 | Renesas Electronics Corporation | Semiconductor memory device with low standby current |

| JP2013254531A (ja) * | 2012-06-05 | 2013-12-19 | Fujitsu Semiconductor Ltd | 半導体メモリおよびシステム |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS58122693A (ja) * | 1982-01-14 | 1983-07-21 | Nippon Telegr & Teleph Corp <Ntt> | メモリ回路 |

| JPH07141883A (ja) * | 1993-11-18 | 1995-06-02 | Fujitsu Ltd | スタティックram |

| JPH1031888A (ja) * | 1996-07-15 | 1998-02-03 | Ricoh Co Ltd | 半導体メモリ回路 |

| JPH11260055A (ja) * | 1998-12-25 | 1999-09-24 | Hitachi Ltd | 半導体装置 |

| JP2000057778A (ja) * | 1998-08-18 | 2000-02-25 | Nippon Telegr & Teleph Corp <Ntt> | 半導体メモリ |

| JP2003016786A (ja) * | 2001-06-28 | 2003-01-17 | Mitsubishi Electric Corp | 半導体記憶装置 |

| JP2003123479A (ja) * | 2001-10-12 | 2003-04-25 | Matsushita Electric Ind Co Ltd | 半導体記憶装置 |

-

2004

- 2004-04-01 JP JP2004109059A patent/JP2005293751A/ja active Pending

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS58122693A (ja) * | 1982-01-14 | 1983-07-21 | Nippon Telegr & Teleph Corp <Ntt> | メモリ回路 |

| JPH07141883A (ja) * | 1993-11-18 | 1995-06-02 | Fujitsu Ltd | スタティックram |

| JPH1031888A (ja) * | 1996-07-15 | 1998-02-03 | Ricoh Co Ltd | 半導体メモリ回路 |

| JP2000057778A (ja) * | 1998-08-18 | 2000-02-25 | Nippon Telegr & Teleph Corp <Ntt> | 半導体メモリ |

| JPH11260055A (ja) * | 1998-12-25 | 1999-09-24 | Hitachi Ltd | 半導体装置 |

| JP2003016786A (ja) * | 2001-06-28 | 2003-01-17 | Mitsubishi Electric Corp | 半導体記憶装置 |

| JP2003123479A (ja) * | 2001-10-12 | 2003-04-25 | Matsushita Electric Ind Co Ltd | 半導体記憶装置 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7826298B2 (en) | 2007-05-24 | 2010-11-02 | Renesas Electronics Corporation | Semiconductor memory device with low standby current |

| JP2013254531A (ja) * | 2012-06-05 | 2013-12-19 | Fujitsu Semiconductor Ltd | 半導体メモリおよびシステム |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10325650B2 (en) | Semiconductor storage device | |

| KR100718429B1 (ko) | 반도체 기억장치, 반도체 집적회로장치 및 휴대기기 | |

| JP6830681B2 (ja) | 電子回路 | |

| JP5122449B2 (ja) | 論理回路電源電圧と異なるメモリ用の別の電源電圧を有する集積回路 | |

| US7986571B2 (en) | Low power, single-ended sensing in a multi-port SRAM using pre-discharged bit lines | |

| US8164971B2 (en) | Dual power rail word line driver and dual power rail word line driver array | |

| US6373745B2 (en) | Semiconductor memory cell and semiconductor memory device | |

| US5187686A (en) | Control circuit having outputs with differing rise and fall times | |

| US20040243758A1 (en) | Data storage circuit | |

| JP2003258624A (ja) | 入力バッファ回路及び半導体記憶装置 | |

| JPH09231767A (ja) | スタティック型半導体記憶装置 | |

| JP4562515B2 (ja) | 論理回路及びワードドライバ回路 | |

| JP6578413B2 (ja) | 半導体装置 | |

| JP2005293751A (ja) | 半導体メモリ | |

| Nautiyal et al. | Charge recycled low power SRAM with integrated write and read assist, for wearable electronics, designed in 7nm FinFET | |

| JP2014164777A (ja) | Sram | |

| JP4342467B2 (ja) | 半導体メモリ | |

| JPH0330234B2 (ja) | ||

| KR100278981B1 (ko) | 반도체 메모리의 구동전압 가변형 데이타 기록장치 | |

| JPH1139865A (ja) | ワード線駆動回路 | |

| JP2003257182A (ja) | スタティックram | |

| JPH0524594B2 (ja) | ||

| JP2014123932A (ja) | 半導体装置 | |

| JP2009043302A (ja) | データ書き込み回路及びそれを用いた半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060912 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090525 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090603 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090730 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100316 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20100713 |