JP2005183943A - 半導体素子 - Google Patents

半導体素子 Download PDFInfo

- Publication number

- JP2005183943A JP2005183943A JP2004339608A JP2004339608A JP2005183943A JP 2005183943 A JP2005183943 A JP 2005183943A JP 2004339608 A JP2004339608 A JP 2004339608A JP 2004339608 A JP2004339608 A JP 2004339608A JP 2005183943 A JP2005183943 A JP 2005183943A

- Authority

- JP

- Japan

- Prior art keywords

- silicon carbide

- carbide layer

- semiconductor element

- region

- electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 119

- 229910010271 silicon carbide Inorganic materials 0.000 claims abstract description 183

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 claims abstract description 163

- 239000000758 substrate Substances 0.000 claims abstract description 80

- 229910021478 group 5 element Inorganic materials 0.000 claims abstract description 25

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 claims description 50

- 229910052757 nitrogen Inorganic materials 0.000 claims description 26

- 238000010438 heat treatment Methods 0.000 claims description 24

- 239000013078 crystal Substances 0.000 claims description 21

- MWUXSHHQAYIFBG-UHFFFAOYSA-N Nitric oxide Chemical group O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 claims description 17

- 239000012535 impurity Substances 0.000 claims description 17

- 150000001875 compounds Chemical class 0.000 claims description 11

- 230000001590 oxidative effect Effects 0.000 claims description 9

- 238000007669 thermal treatment Methods 0.000 abstract 1

- 239000010410 layer Substances 0.000 description 169

- 108091006146 Channels Proteins 0.000 description 66

- 239000013598 vector Substances 0.000 description 41

- 238000000034 method Methods 0.000 description 18

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 16

- 239000000969 carrier Substances 0.000 description 11

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 8

- 229910052782 aluminium Inorganic materials 0.000 description 8

- 229910052759 nickel Inorganic materials 0.000 description 8

- 238000003860 storage Methods 0.000 description 8

- 238000010586 diagram Methods 0.000 description 7

- 230000000694 effects Effects 0.000 description 7

- 239000007789 gas Substances 0.000 description 7

- 238000000137 annealing Methods 0.000 description 5

- 230000008878 coupling Effects 0.000 description 5

- 238000010168 coupling process Methods 0.000 description 5

- 238000005859 coupling reaction Methods 0.000 description 5

- 238000004519 manufacturing process Methods 0.000 description 5

- 229910004298 SiO 2 Inorganic materials 0.000 description 3

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 3

- 238000009413 insulation Methods 0.000 description 3

- 239000011229 interlayer Substances 0.000 description 3

- 229910052760 oxygen Inorganic materials 0.000 description 3

- 239000001301 oxygen Substances 0.000 description 3

- ODUCDPQEXGNKDN-UHFFFAOYSA-N Nitrogen oxide(NO) Natural products O=N ODUCDPQEXGNKDN-UHFFFAOYSA-N 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 239000004020 conductor Substances 0.000 description 2

- 239000007772 electrode material Substances 0.000 description 2

- 230000012447 hatching Effects 0.000 description 2

- 238000002513 implantation Methods 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 1

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- 102000004129 N-Type Calcium Channels Human genes 0.000 description 1

- 108090000699 N-Type Calcium Channels Proteins 0.000 description 1

- 238000009825 accumulation Methods 0.000 description 1

- 230000004913 activation Effects 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 230000006837 decompression Effects 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 230000007613 environmental effect Effects 0.000 description 1

- 238000009499 grossing Methods 0.000 description 1

- 230000005524 hole trap Effects 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 229910003465 moissanite Inorganic materials 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 230000003746 surface roughness Effects 0.000 description 1

- 230000002195 synergetic effect Effects 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Chemical compound O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

- H01L29/41725—Source or drain electrodes for field effect devices

- H01L29/41766—Source or drain electrodes for field effect devices with at least part of the source or drain electrode having contact below the semiconductor surface, e.g. the source or drain electrode formed at least partially in a groove or with inclusions of conductor inside the semiconductor

Abstract

【解決手段】 本発明の半導体素子では、炭化珪素基板11の上に設けられたn型の炭化珪素層12は、(0001)面から<11−20>方向にオフカットされた上面を有している。そして、チャネル領域14において、オフカット方向に沿って流れる電流が支配的となるようにゲート電極17やソース電極18が配置されている。

本発明では、ゲート絶縁膜17を形成した後に、V族元素を含む雰囲気下で熱処理を行う。これにより、炭化珪素層12とゲート絶縁膜の界面において界面準位密度が低下するため、オフカット方向Aに垂直な方向よりもオフカット方向Aのほうが電子移動度が高くなる。

【選択図】 図1

Description

素を含む化合物を用いて熱処理を行う工程を経て形成されるので、炭化珪素層の上面にステップバンチングが形成されていても、チャネル層が形成されるゲート絶縁膜と炭化珪素層の界面において、界面準位密度が低減され、オフカット方向に沿った方向の電子移動度が向上する。これにより、オフカット方向に沿った方向の電子移動度が、オフカット方向に垂直な方向の電子移動度よりも高くなりやすい。

を含む雰囲気で熱処理することにより形成された場合には、上記界面準位密度を低下させることができ、その結果、オフカット方向における電子移動度が高くなる。

る場合には、高い効果を得ることができる。

囲気で熱酸化することにより形成された場合であっても、ゲート絶縁膜と炭化珪素層の界面は良好なものが得られ、特に上記の酸化窒素を含む雰囲気で熱酸化して形成されたゲート絶縁膜も本発明に対して有効に働く。

経て形成されるので、炭化珪素層の上面にステップバンチングが形成されていても、チャネル層が形成されるゲート絶縁膜と炭化珪素層の界面において、界面準位密度が低減され、オフカット方向に沿った方向の電子移動度が向上する。これにより、オフカット方向に沿った方向の電子移動度が、オフカット方向に垂直な方向の電子移動度よりも高くなりやすい。

を含む雰囲気で熱処理することにより形成された場合には、上記界面準位密度を低下させることができ、その結果、オフカット方向における電子移動度が高くなる。

る場合には、高い効果を得ることができる。

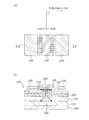

図1(a), (b)は、第1の実施形態において、炭化珪素層を用いた一般的な縦型蓄積型MOSFETの2つのユニットセルの結合部を示す断面図である。ここで、図1(a)は、MOSFETの電極の一部を上方から見た平面図であり、図1(b)は、図1(a)のI−I線における断面図である。

従来の半導体素子は、オフカット方向に平行な方向よりも垂直な方向の方が電子移動度が大きいという異方性を有していた。それに対し、本実施形態の半導体装置ではこの異方性が逆転している。これは、本実施形態では、窒素と酸素とを含むガスを用いた熱処理を行うことにより、炭化珪素層とゲート絶縁膜の界面における界面準位密度が低下し、オフカット方向に沿った方向の電子移動度が向上する。以下に、炭化珪素基板の電子移動度が、オフカット方向において大きいという理由について考察する。

図1に示す2つのユニットセルの結合部では、オフカット方向Aに平行な方向にのみ電流を流す例を示した。しかし実際には、縦型の半導体素子では複数の方向に電流を流す場合が多い。この場合には、複数の方向の中で最も電流量の多い方向がオフカット方向と平行になるように素子を配置する。以下に、その構造について説明する。

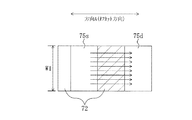

縦型のMOSFETにおいては、ソース電極18およびゲート電極17がストライプ状(または櫛形)に配置されている場合がある。そのような場合について、図7(a), (b)を参照しながら説明する。

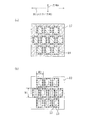

縦型のMOSFETは、多角形のユニットセルごとに配置され、各ユニットセルでは、ソース電極の側方がゲート電極によって囲まれている場合がある。そのような場合について、図8(a), (b)を参照しながら説明する。

図11(a), (b)は、第2の実施形態において、炭化珪素層を用いた一般的な横型蓄積型MOSFETを示す断面図である。ここで、図11(a)は、MOSFETの電極の一部を上方から見た平面図であり、図11(b)は、図11(a)のVII−VII線における断面図である。

なお、上述の実施形態においては、半導体基板として4H−SiCから約8度オフカットされた表面を有する基板を用いた。しかしながら、本発明では、指定された結晶面Sから所定の方向Aに10度以下の角度だけ傾いた表面を具備した基板であれば、他の基板を用いてもよい。

1B 上部配線電極

7C ベース電極

10 縦型蓄積型MOSFET

11 半導体基板

12 n型炭化珪素層

13 p型ウェル領域

14 チャネル層

15 n型ソース領域

16 ゲート絶縁膜

17 ゲート電極

18 ソース電極

19 ドレイン電極

20 SiC基板

21 酸化物層

30 チャンバ

31 真空ポンプ

60 縦型反転型MOSFET

70 横型蓄積型MOSFET

71 半導体基板

72 p型炭化珪素層

74 チャネル層

75d ドレイン領域

75s ソース領域

76 ゲート絶縁膜

77 ゲート電極

78 ソース電極

79 ドレイン電極

90 横型反転型MOSFET

101 半導体基板

102 n型炭化珪素層

103 p型ウェル領域

104 チャネル層

105 ソース領域

106 ゲート絶縁膜

107 ゲート電極

108 ソース電極

109 ドレイン電極

Claims (31)

- 半導体基板と、

上記半導体基板の上に設けられ、結晶面から10度以下の角度だけオフカット方向に傾いた上面を有する炭化珪素層と、

上記炭化珪素層の上に設けられたゲート絶縁膜と、上記ゲート絶縁膜の上に設けられたゲート電極と、

上記炭化珪素層の上のうち上記ゲート電極の側方に設けられたソース電極と、

上記半導体基板の下方に設けられたドレイン電極と、

上記炭化珪素層のうち少なくとも上記ソース電極の下に位置する領域に設けられたソース領域とを備え、

平面視して、上記ソース領域のうち最も長い辺は、上記オフカット方向に垂直な方向に沿っている、半導体素子。 - 請求項1に記載の半導体素子であって、

上記炭化珪素層のうち上記ソース領域の側方および下方に設けられた第2導電型のウェル領域と、

上記ウェル領域と電気的に接続されるベース電極とをさらに備える、半導体素子。 - 請求項1または2に記載の半導体素子であって、

上記オフカット方向に垂直な方向に沿った方向とは、上記オフカット方向に垂直な方向からの傾きが5度以内の方向である、半導体素子。 - 請求項1〜3のうちいずれか1項に記載の半導体素子であって、

上記炭化珪素層のうち上記ゲート絶縁膜の下に位置する領域にチャネル層が設けられている、半導体素子。 - 請求項4に記載の半導体素子であって、

上記チャネル領域には、少なくとも1層の第1炭化珪素層と、第1炭化珪素層よりも第1導電型の不純物濃度が高くかつ第1炭化珪素層の膜厚よりも薄い、少なくとも1層の第2炭化珪素層とを有する積層構造が設けられている、半導体素子。 - 請求項1〜5のうちいずれか1項に記載の半導体素子であって、

上記炭化珪素層では、結晶面の面内方向における電子移動度よりも、上記結晶面に対する垂直方向における電子移動度の方が大きい、半導体素子。 - 請求項1〜6のうちいずれか1項に記載の半導体素子であって、

上記炭化珪素層は、4H−SiCである、半導体素子。 - 請求項1〜7のうちいずれか1項に記載の半導体素子であって、

上記炭化珪素層の上面は、(0001)面から<11−20>方向に傾いた面である、半導体素子。 - 請求項1〜7のうちいずれか1項に記載の半導体素子であって、

上記炭化珪素層の上面は、(0001)面から<1−100>方向に傾いた面である、半導体素子。 - 請求項1〜9のうちいずれか1項に記載の半導体素子であって、

上記ゲート絶縁膜は、上記炭化珪素層の上部を熱酸化した後に、V族元素を含む化合物

を含む雰囲気で熱処理することにより形成された、半導体素子。 - 請求項10に記載の半導体素子であって

上記V族元素を含む化合物は、酸化窒素である、半導体素子。 - 請求項10または11に記載の半導体素子であって、

上記炭化珪素層と上記ゲート絶縁膜との界面において、窒素濃度の最大値が1×1020cm-3以上で1×1022cm-3以下である、半導体素子。 - 請求項1〜12のうちいずれか1項に記載の半導体素子であって、

上記ソース電極は、上記ベース電極と同一の膜で設けられている、半導体素子。 - 請求項1〜13のうちいずれか1項に記載の半導体素子であって、

上記ゲート電極は、平面視して多角形がくり抜かれた形状で設けられ、

上記多角形におけるくり抜かれた部分の辺のうち最も長い辺は、上記オフカット方向に垂直な方向に沿っている、半導体素子。 - 請求項14に記載の半導体素子であって、

平面視して、上記ソース電極は多角形の形状で配置し、上記ゲート電極は上記ソース電極と離間して、かつ上記ソース電極の側方を囲む形状で配置している、半導体素子。 - 請求項1〜13のうちいずれか1項に記載の半導体素子であって、

上記ゲート電極は、平面視して多角形の形状で設けられ、

上記多角形の辺のうち最も長い辺は、上記オフカット方向に垂直な方向に沿っている、半導体素子。 - 請求項16に記載の半導体素子であって、

平面視して、上記ソース電極は、ストライプ状に並ぶ複数の第1矩形部と、上記複数の第1矩形部の端部を接続する第1接続部とを有する櫛形に配置し、上記ゲート電極は、上記複数の第1矩形部のそれぞれと交互に配置するストライプ状の複数の第2矩形部と、上記第2矩形部の端部を接続する第2接続部とを有する櫛形に配置している、半導体素子。 - 半導体基板と、

上記半導体基板の上に設けられ、結晶面から10度以下の角度だけオフカット方向に傾いた上面を有する炭化珪素層と、

上記炭化珪素層の上に設けられたゲート絶縁膜と、上記ゲート絶縁膜の上に設けられたゲート電極と、

上記炭化珪素層の上のうち上記ゲート電極の側方に設けられたソース電極と、

上記炭化珪素層の上のうち上記ゲート電極の側方に設けられたドレイン電極と、

上記炭化珪素層のうち少なくとも上記ソース電極および上記ドレイン電極の下に位置する領域に互いに離間して設けられたソース・ドレイン領域とを備え、

平面視して、上記ソース・ドレイン領域の辺のうち互いに対向する辺は、上記オフカット方向に垂直な方向に沿っている、半導体素子。 - 請求項18に記載の半導体素子であって、

上記炭化珪素層内に設けられ、第1導電型の不純物を含むベース領域と、

上記ベース領域と電気的に接続されるベース電極とをさらに備える、半導体素子。 - 請求項18または19に記載の半導体素子であって、

上記ゲート電極は多角形の形状で設けられ、

上記多角形の辺のうち最も長い辺は、上記オフカット方向に垂直な方向に沿っている、半導体素子。 - 請求項18〜20のうちいずれか1項に記載の半導体素子であって、

上記オフカット方向に垂直な方向に沿った方向とは、上記オフカット方向に垂直な方向からの傾きが5度以内の方向である、半導体素子。 - 請求項18〜21のうちいずれか1項に記載の半導体素子であって、

上記炭化珪素層のうち上記ゲート絶縁膜の下に位置する領域にチャネル層が設けられている、半導体素子。 - 請求項22に記載の半導体素子であって、

上記チャネル領域には、少なくとも1層の第1炭化珪素層と、第1炭化珪素層よりも第1導電型の不純物濃度が高くかつ第1炭化珪素層の膜厚よりも薄い、少なくとも1層の第2炭化珪素層とを有する積層構造が設けられている、半導体素子。 - 請求項18〜23のうちいずれか1項に記載の半導体素子であって、

上記炭化珪素層では、結晶面の面内方向における電子移動度よりも、上記結晶面に対する垂直方向における電子移動度の方が大きい、半導体素子。 - 請求項18〜24のうちいずれか1項に記載の半導体素子であって、

上記炭化珪素層は、4H−SiCである、半導体素子。 - 請求項18〜25のうちいずれか1項に記載の半導体素子であって、

上記炭化珪素層の上面は、(0001)面から<11−20>方向に傾いた面である、半導体素子。 - 請求項18〜25のうちいずれか1項に記載の半導体素子であって、

上記炭化珪素層の上面は、(0001)面から<1−100>方向に傾いた面である、半導体素子。 - 請求項18〜27のうちいずれか1項に記載の半導体素子であって、

上記ゲート絶縁膜は、上記炭化珪素層の上部を熱酸化した後に、V族元素を含む化合物

を含む雰囲気で熱処理することにより形成された、半導体素子。 - 請求項28に記載の半導体素子であって、

上記V族元素を含む化合物は、酸化窒素である、半導体素子。 - 請求項28または29のうちいずれか1項に記載の半導体素子であって、

上記炭化珪素層と上記ゲート絶縁膜との界面において、窒素濃度の最大値が1×1020cm-3以上で1×1022cm-3以下である、半導体素子。 - 請求項18〜30のうちいずれか1項に記載の半導体素子であって、

上記ソース電極は、上記ベース電極と同一の膜で設けられている、半導体素子。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004339608A JP2005183943A (ja) | 2003-11-25 | 2004-11-24 | 半導体素子 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003393320 | 2003-11-25 | ||

| JP2004339608A JP2005183943A (ja) | 2003-11-25 | 2004-11-24 | 半導体素子 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005183943A true JP2005183943A (ja) | 2005-07-07 |

| JP2005183943A5 JP2005183943A5 (ja) | 2005-11-04 |

Family

ID=34797149

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004339608A Pending JP2005183943A (ja) | 2003-11-25 | 2004-11-24 | 半導体素子 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005183943A (ja) |

Cited By (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010080786A (ja) * | 2008-09-26 | 2010-04-08 | Toshiba Corp | 半導体装置 |

| US7745828B2 (en) | 2007-01-11 | 2010-06-29 | Samsung Electronics Co., Ltd. | Organic light emitting device and manufacturing method thereof |

| WO2010110252A1 (ja) * | 2009-03-27 | 2010-09-30 | 住友電気工業株式会社 | Mosfetおよびmosfetの製造方法 |

| WO2010110253A1 (ja) * | 2009-03-27 | 2010-09-30 | 住友電気工業株式会社 | Mosfetおよびmosfetの製造方法 |

| WO2010116887A1 (ja) * | 2009-04-10 | 2010-10-14 | 住友電気工業株式会社 | 絶縁ゲート型電界効果トランジスタ |

| WO2010116886A1 (ja) * | 2009-04-10 | 2010-10-14 | 住友電気工業株式会社 | 絶縁ゲート型バイポーラトランジスタ |

| JP2012234908A (ja) * | 2011-04-28 | 2012-11-29 | Denso Corp | 炭化珪素半導体装置 |

| US9012923B2 (en) | 2013-08-01 | 2015-04-21 | Kabushiki Kaisha Toshiba | Semiconductor device |

| JP2015099845A (ja) * | 2013-11-19 | 2015-05-28 | 住友電気工業株式会社 | 半導体装置 |

| JPWO2013145023A1 (ja) * | 2012-03-30 | 2015-08-03 | 株式会社日立製作所 | 電界効果型炭化珪素トランジスタ |

| JP2016063122A (ja) * | 2014-09-19 | 2016-04-25 | 株式会社東芝 | 半導体装置 |

| JP2016149566A (ja) * | 2014-08-29 | 2016-08-18 | 住友電気工業株式会社 | 炭化珪素半導体装置およびその製造方法 |

| JP2019176194A (ja) * | 2019-07-22 | 2019-10-10 | ローム株式会社 | 半導体装置 |

| US10612160B2 (en) | 2014-08-01 | 2020-04-07 | Sumitomo Electric Industries, Ltd. | Epitaxial wafer and method for manufacturing same |

| JP2021108380A (ja) * | 2013-09-20 | 2021-07-29 | モノリス セミコンダクター インコーポレイテッド | 高電圧mosfetデバイスおよび該デバイスを製造する方法 |

-

2004

- 2004-11-24 JP JP2004339608A patent/JP2005183943A/ja active Pending

Cited By (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7745828B2 (en) | 2007-01-11 | 2010-06-29 | Samsung Electronics Co., Ltd. | Organic light emitting device and manufacturing method thereof |

| US8796694B2 (en) | 2008-09-26 | 2014-08-05 | Kabushiki Kaisha Toshiba | Semiconductor device |

| JP2010080786A (ja) * | 2008-09-26 | 2010-04-08 | Toshiba Corp | 半導体装置 |

| US8513673B2 (en) | 2009-03-27 | 2013-08-20 | Sumitomo Electric Industries, Ltd. | MOSFET and method for manufacturing MOSFET |

| WO2010110252A1 (ja) * | 2009-03-27 | 2010-09-30 | 住友電気工業株式会社 | Mosfetおよびmosfetの製造方法 |

| WO2010110253A1 (ja) * | 2009-03-27 | 2010-09-30 | 住友電気工業株式会社 | Mosfetおよびmosfetの製造方法 |

| US8536583B2 (en) | 2009-03-27 | 2013-09-17 | Sumitomo Electric Industries, Ltd. | MOSFET and method for manufacturing MOSFET |

| JPWO2010110253A1 (ja) * | 2009-03-27 | 2012-09-27 | 住友電気工業株式会社 | Mosfetおよびmosfetの製造方法 |

| JPWO2010110252A1 (ja) * | 2009-03-27 | 2012-09-27 | 住友電気工業株式会社 | Mosfetおよびmosfetの製造方法 |

| EP2418680A1 (en) * | 2009-04-10 | 2012-02-15 | Sumitomo Electric Industries, Ltd. | Insulated gate bipolar transistor |

| US8502236B2 (en) | 2009-04-10 | 2013-08-06 | Sumitomo Electric Industries, Ltd. | Insulated gate field effect transistor |

| US8525187B2 (en) | 2009-04-10 | 2013-09-03 | Sumitomo Electric Industries, Ltd. | Insulated gate bipolar transistor |

| WO2010116886A1 (ja) * | 2009-04-10 | 2010-10-14 | 住友電気工業株式会社 | 絶縁ゲート型バイポーラトランジスタ |

| WO2010116887A1 (ja) * | 2009-04-10 | 2010-10-14 | 住友電気工業株式会社 | 絶縁ゲート型電界効果トランジスタ |

| EP2418680A4 (en) * | 2009-04-10 | 2012-12-12 | Sumitomo Electric Industries | ISOLATED GRID BIPOLAR TRANSISTOR |

| JP2012234908A (ja) * | 2011-04-28 | 2012-11-29 | Denso Corp | 炭化珪素半導体装置 |

| JPWO2013145023A1 (ja) * | 2012-03-30 | 2015-08-03 | 株式会社日立製作所 | 電界効果型炭化珪素トランジスタ |

| US9012923B2 (en) | 2013-08-01 | 2015-04-21 | Kabushiki Kaisha Toshiba | Semiconductor device |

| JP2021108380A (ja) * | 2013-09-20 | 2021-07-29 | モノリス セミコンダクター インコーポレイテッド | 高電圧mosfetデバイスおよび該デバイスを製造する方法 |

| JP7179893B2 (ja) | 2013-09-20 | 2022-11-29 | モノリス セミコンダクター インコーポレイテッド | 高電圧mosfetデバイスおよび該デバイスを製造する方法 |

| WO2015076020A1 (ja) * | 2013-11-19 | 2015-05-28 | 住友電気工業株式会社 | 半導体装置 |

| US9698220B2 (en) | 2013-11-19 | 2017-07-04 | Sumitomo Electric Industries, Ltd. | Semiconductor device |

| JP2015099845A (ja) * | 2013-11-19 | 2015-05-28 | 住友電気工業株式会社 | 半導体装置 |

| US10612160B2 (en) | 2014-08-01 | 2020-04-07 | Sumitomo Electric Industries, Ltd. | Epitaxial wafer and method for manufacturing same |

| JP2016149566A (ja) * | 2014-08-29 | 2016-08-18 | 住友電気工業株式会社 | 炭化珪素半導体装置およびその製造方法 |

| JP2016063122A (ja) * | 2014-09-19 | 2016-04-25 | 株式会社東芝 | 半導体装置 |

| JP2019176194A (ja) * | 2019-07-22 | 2019-10-10 | ローム株式会社 | 半導体装置 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7381993B2 (en) | High-breakdown-voltage insulated gate semiconductor device | |

| US10217858B2 (en) | Semiconductor device and method of manufacturing semiconductor device | |

| US9722017B2 (en) | Silicon carbide semiconductor device | |

| US8748901B1 (en) | Silicon carbide semiconductor element | |

| US9018699B2 (en) | Silicon carbide semiconductor element and method for fabricating the same | |

| US8421151B2 (en) | Semiconductor device and process for production thereof | |

| JP6572423B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| KR100199997B1 (ko) | 탄화규소 반도체장치 | |

| US8564060B2 (en) | Semiconductor device with large blocking voltage and manufacturing method thereof | |

| JP6801323B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| JP6848316B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| WO2013001677A1 (ja) | 半導体装置とその製造方法 | |

| JP4487655B2 (ja) | 半導体装置の製造方法 | |

| JP7006280B2 (ja) | 半導体装置 | |

| JP2005183943A (ja) | 半導体素子 | |

| JP2019003967A (ja) | 半導体装置および半導体装置の製造方法 | |

| JP2023001343A (ja) | 半導体装置 | |

| JP5817204B2 (ja) | 炭化珪素半導体装置 | |

| JP5463725B2 (ja) | 炭化珪素半導体装置およびその製造方法 | |

| WO2012105170A1 (ja) | 半導体装置およびその製造方法 | |

| JP7462394B2 (ja) | 炭化珪素半導体装置および炭化珪素半導体装置の製造方法 | |

| JP7331393B2 (ja) | 炭化珪素半導体装置の製造方法 | |

| KR20060136356A (ko) | 반도체소자 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050804 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050909 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20050909 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20051013 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20051108 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20051227 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20060509 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060710 |

|

| A911 | Transfer of reconsideration by examiner before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20060728 |

|

| A912 | Removal of reconsideration by examiner before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20060922 |