CN1253608C - 处理具有最小边缘隔绝的衬底的方法和设备 - Google Patents

处理具有最小边缘隔绝的衬底的方法和设备 Download PDFInfo

- Publication number

- CN1253608C CN1253608C CNB018044514A CN01804451A CN1253608C CN 1253608 C CN1253608 C CN 1253608C CN B018044514 A CNB018044514 A CN B018044514A CN 01804451 A CN01804451 A CN 01804451A CN 1253608 C CN1253608 C CN 1253608C

- Authority

- CN

- China

- Prior art keywords

- wafer

- contact

- forming board

- anode

- area

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/288—Deposition of conductive or insulating materials for electrodes conducting electric current from a liquid, e.g. electrolytic deposition

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25D—PROCESSES FOR THE ELECTROLYTIC OR ELECTROPHORETIC PRODUCTION OF COATINGS; ELECTROFORMING; APPARATUS THEREFOR

- C25D5/00—Electroplating characterised by the process; Pretreatment or after-treatment of workpieces

- C25D5/02—Electroplating of selected surface areas

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25D—PROCESSES FOR THE ELECTROLYTIC OR ELECTROPHORETIC PRODUCTION OF COATINGS; ELECTROFORMING; APPARATUS THEREFOR

- C25D17/00—Constructional parts, or assemblies thereof, of cells for electrolytic coating

- C25D17/001—Apparatus specially adapted for electrolytic coating of wafers, e.g. semiconductors or solar cells

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/288—Deposition of conductive or insulating materials for electrodes conducting electric current from a liquid, e.g. electrolytic deposition

- H01L21/2885—Deposition of conductive or insulating materials for electrodes conducting electric current from a liquid, e.g. electrolytic deposition using an external electrical current, i.e. electro-deposition

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76877—Filling of holes, grooves or trenches, e.g. vias, with conductive material

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25D—PROCESSES FOR THE ELECTROLYTIC OR ELECTROPHORETIC PRODUCTION OF COATINGS; ELECTROFORMING; APPARATUS THEREFOR

- C25D7/00—Electroplating characterised by the article coated

- C25D7/12—Semiconductors

- C25D7/123—Semiconductors first coated with a seed layer or a conductive layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3205—Deposition of non-insulating-, e.g. conductive- or resistive-, layers on insulating layers; After-treatment of these layers

- H01L21/321—After treatment

- H01L21/32115—Planarisation

- H01L21/3212—Planarisation by chemical mechanical polishing [CMP]

Abstract

在具有一个直径的晶片的表面上处理材料的设备,包括:空腔,由终止于围缘的围壁所限定,具有至少一个小于晶片直径的侧向尺寸和至少一个大于晶片直径的侧向尺寸,被配置为保持接近围缘的处理溶液,使得处理溶液总是与第一晶片表面区域相接触;被配置为在空腔的上方保持晶片的头,使得晶片的表面面对空腔;以及电接触子,位于空腔围壁的外面,被配置为接触第二晶片表面区域,在此,空腔的侧向尺寸小于晶片直径,并且当晶片相对于接触子移动时保持与晶片的电接触。本发明的优点包括对晶片基本上完全的表面处理。

Description

本申请是2001年1月17日提交的US序列号09/760,757的继续申请,它要求2000年11月3日申请的US临时申请60/245,211的优先权,其全部公开内容引用在此,作为参考。

技术领域

本发明主要涉及电沉积工艺技术,并且,更具体地,涉及获得均匀和平面沉积的电沉积工艺。

背景技术

传统的半导体器件一般包括:通常为硅的半导体衬底,以及大量顺序形成的介质层,例如二氧化硅,和由导电材料制成的导电通路或内部连线。内部连线通常通过在介质层中蚀刻出来的沟槽内填充导电材料而形成。在集成电路中,内部连线网络的多层相对于衬底表面侧向延伸。形成于不同层中的内部连线可使用通孔或接头来实现电连接。这样一些部件,即通孔、沟槽、焊点或接头的导电材料填充工艺可以这样完成:在包含上述部件的衬底上沉积导电材料。然后可以通过使用平面化和诸如化学机械抛光(CMP)这样的抛光技术来除去衬底上多余的导电材料。

铜(Cu)和Cu合金作为内部连线材料最近受到了相当的关注,因为它们优良的电迁移和低电阻特性。Cu沉积的优选方法是电沉积。在加工过程中,铜被电镀或电沉积到预先覆盖有隔离层和种子层的衬底上。典型的隔离层材料通常包括钨(W)、钽(Ta)、钛(Ti)、它们的合金及氮化物。典型的长铜种子层的材料通常为一薄层铜,它通过CVD或PVD方法沉积在上述隔离层上。

有许多不同的镀Cu系统的设计。例如,1996年5月4日授予Andricacos等人的美国专利号5,516,412公开了一种垂直桨电镀槽,用

以在平面制品上电沉积薄膜。1999年11月16日授予Koon的美国专利号5,985,123也公开了另一种垂直电镀设备,其主旨在于解决与可变衬底尺寸联系在一起的非均匀沉积问题。

在电沉积Cu的过程中,使用了特别配制的电镀溶液或电解液。这些溶液或电解液包含离子形式的Cu以及用来控制已沉积材料的晶体结构、形态和电镀状态的添加剂。需要使用添加剂来使沉积层光滑且稍有光泽。

有多种Cu电镀溶液的配方,其中一些在商业上是可行的。一种这样的配方包括作为铜来源的硫酸铜(CuSO4)(参见James Kelly etal.,Journal of The Electrochemical Society,Vol.146,pages 2540-2545(1999)),还包括水、硫酸(H2SO4)以及氯化物离子。众所周知,常被作为添加剂提到的其它化学药品也可加入Cu电解溶液中以获得沉积材料的期望特性(例如,参见Robert Mikkola and Linlin Chen,用在改进的内部连线镀金中的第二代铜电镀化学中添加剂组分作用的研究(Investigation of the Roles of the Additive Components for SecondGeneration Copper Electroplating Chemistries used for AdvancedInterconnect Metallization),Proceedings fo the InternationalInterconnect Technology Conference,pages 117-119,June 5-7,2000)。

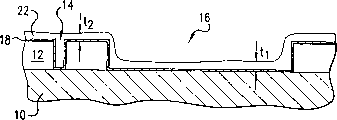

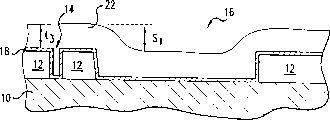

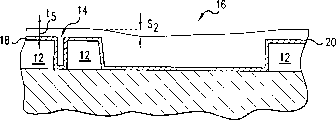

图1至2举例说明了一种传统电沉积方法和设备。图1A显示了一种在其上形成有一绝缘层12的衬底10。使用传统的蚀刻技术,在绝缘层12和衬底10的暴露区域上形成了诸如一排小通孔14和一条宽沟槽16这样的部件。在该实施例中,通孔14又窄又深;换句话说,他们具有很大的长宽比(即,他们的深度比宽度值很大)。通常,通孔14的宽度为亚微米。另一方面,该实施例中所示的沟槽16很宽且具有小的长宽比。沟槽16的宽度可以为其深度的5到50倍或更大。

图1B-1C显示了一种用铜材料填充这些部件的传统方法。图1B显示,隔离层/胶着或粘合层18和种子层20被顺序地沉积在衬底10和绝缘层12上。隔离层18可以是Ta、W、Ti、它们的合金、氮化物或它们的混合物。隔离层18通常使用各种溅射方法中的任何一种、化学气象沉积(CVD)、或无电镀膜法来进行沉积。然后,在隔离层18之上沉积种子层20。如果要镀的导体也是铜的话,那么种子层20通常是铜,并且可通过使用各种溅射方法、CVD或无电沉积或它们的组合来沉积在隔离层18上。

在图1C中,沉积完种子层20之后,从合适的电解槽或电解槽配方中将导电材料层22(即,铜层)部分电沉积到种子层20上。在此步骤中,在铜种子层20和/或隔离层18上做一个电接头,这样可以相对于阳极(未示出)对其施加一个阴极(负极)电压。然后,如上面所讨论的,利用电解溶液在衬底上电沉积铜材料层22。通过调整诸如氯化物离子、抑制剂/阻化剂、促进剂这样的添加剂的总量,有可能在小部件中获得自底而上的铜膜生长。

如图1C中所示,铜材料22完全填满通孔14,而且在大沟槽16中也通常是等角的,因为所用的添加剂在大部件中不起作用。例如,据信在通孔14中自底而上的沉积之所以会发生,是因为抑制剂/阻化剂分子黏附在通孔14的顶部以抑制在那附近的材料生长。这些分子并不能通过狭窄的开口有效地扩散到通孔14的底部表面。通孔14底部表面上促进剂的优先吸附导致在该区域的快速生长,最终导致自底而上的生长以及如图1C中所示的Cu沉积轮廓。这里,沟槽16底部表面的Cu厚度t1与绝缘层12之上的Cu厚度t2大致相同。

正如所能预料的,为用Cu材料完全填满沟槽16,需要进一步电镀。图1D显示了附加的Cu电镀之后最终结构。在此情形中,绝缘层12上的Cu厚度相对较大,并且从绝缘层12上的Cu层顶部到沟槽16中的Cu层22顶部之间有一个台阶S1。对于集成电路(IC)应用,还需要对Cu层22进行CMP或其它材料移除过程以使绝缘层12上的Cu层22和隔离层18都被移除,从而只在部件14和16中留下Cu层。这些移除过程据知花费非常高。

如图1E中显示的获得基本平坦的Cu沉积的方法和设备,就加工效率和花费来说是很昂贵的。该实施例中绝缘层12上的Cu厚度t5小于图1D中所示的传统情形,而且台阶S2的高度也小很多。利用CMP或其它方法移除图1E中较薄的Cu层会更容易,非常重要地节省了花费。

在1998年12月1日提出、由本发明的受让人共同拥有的题为“电化学机械沉积的方法和设备”的共同未决的美国专利申请序列号09/201,929中,提出了一种技术,实现在衬底表面空腔中的导电材料沉积,同时通过在导电材料沉积的同时利用一个焊点抛光场效应区来使场效应区的沉积最小化,从而得到平面铜沉积。

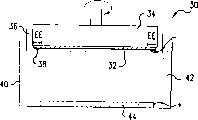

图2A示出了一种现有技术的电沉积系统30的示意性描述。在该系统中,借助于环绕晶片32圆周边的环形夹36,晶片支架34固定了晶片32。电接头38同样制成环形,并与提供阴极电镀的电源的(-)接线柱相连。晶片支架34降入充满电解液42的电解槽40中。与电解槽42接触的阳极44置于晶片表面的对面,并与电源的(+)接线柱相连。阳极44可用要沉积的材料(即铜)制成,或用合适的惰性阳极材料(例如铂、镀铂的钛或石墨)制成。电镀过程开始于能源的提供。在该电镀系统中,电接触38与电解液隔绝,并通过晶片32的圆周传导电镀电流。然而,接头38和晶片30圆周上的夹子36的存在是该系统的一个重大的缺点,并增大了图2A中‘EE’部分所表示的边缘隔绝。边缘隔绝的结果就是,失去了晶片32表面上很有价值的基本区域。

图1A至1E示出了如何在晶片表面上的部件中填充铜。为使该填充过程在整个晶片上都有效且均匀,重要的是在整个晶片表面沉积厚度均匀的铜。厚度均匀性需要非常好,因为非均匀铜的厚度会在CMP过程中导致问题。如图2B中所示,为提高沉积层的均匀性,可在现有技术的电镀系统中加入护罩46,如图2A中所示的那样。在这样的系统中,晶片32和护罩46都是可旋转的。例如,在授予Broadbent的美国专利6,027,631、授予Reid等人的美国专利号6,074,544以及授予Woo等人的美国专利6,103,085中都描述了这样的护罩。

考虑到前面所述的,需要替换的电趁机过程和系统,它们使边缘隔绝问题最小化并沉积均匀的导电薄膜。

发明内容

本发明包括通过电沉积过程在半导体晶片整个表面上沉积导电材料。特别地,本发明提供了在半导体晶片整个表面上形成基本平坦的导电材料层的方法和系统,而不在表面上留下任何地方作为电极,即,没有晶片边缘隔绝。

在本发明的一个方案中,提供了一种在晶片表面沉积材料的工艺,它无需隔绝出任何区域用来在表面做电接触,由此该晶片具有最大侧向尺寸。该工艺包括以下步骤:制作阳极,在阳极和晶片表面之间支撑一块成形板,通过成形板在阳极和晶片表面注入电解液,用一个接触子来接触晶片表面的接触区域,以及在阳极和接触子之间施加电势差。

成形板可以被支撑在阳极和衬底表面之间,以使成形板上表面面向晶片表面。成形板包括大量开孔以使每个开孔让晶片表面和阳极之间有流体交换。成形板侧向尺寸大于晶片的最大侧向尺寸。接触子在成形板“凹”边之外接触晶片表面上的接触区域,从而形成对晶片表面的电接触。当电势差施加到阳极和接触子之间时,当晶片在第一位置时,通过成形板在晶片表面的沉积区域的材料沉积发生。通过将晶片移到第二位置,同时以接触子接触接触区域,在接触区域和沉积区域上的材料沉积都发生。

根据本发明的另一个方案,提供了一种用以在具有最大侧向尺寸的晶片表面沉积材料的系统。该系统包括:阳极、确定凹边的成形板、容纳于阳极和衬底表面之间的液态电解液,以及用以在成形板的凹边之外接触衬底表面的接触区域的电接触子。

成形板可以被支撑在阳极和衬底表面之间,以使成形板上表面面向晶片表面。成形板包括大量开孔。成形板上表面的侧向尺寸大于晶片的最大侧向尺寸。液态电解液通过成形板的开孔并紧靠晶片表面流动,由此电解液总是接触晶片表面的第一区域。电接触子在成形板之外与晶片表面的第二区域建立电接触。当晶片在成形板之上旋转时,第二区域间歇地接触电解液。

根据本发明的又一方案,一种通过其可使导电材料在电解液之外沉积到半导体衬底表面上的系统包括:在材料沉积过程中向衬底表面提供电解液的装置,以及在该沉积过程中被电解液接触的阳极。在该沉积过程中,至少一个接头与此表面在表面的选定范围电互连。材料沉积在选定范围间断地进行,而在表面的其余部分连续进行,因为在阳极和接头之间施加电势差期间,接头和表面中至少一个相对于另一个移动了。

能够提供一种减轻材料在选定范围和表面其余部分之间的沉积不均匀性的设备。该设备可包括一个护罩,其上确定了开孔,安置在阳极和表面之间以改变电场分布。作为选择地,该设备可包括一个多孔板,置于阳极和具有槽孔区域的表面之间,且具有不同的开孔范围程度。

提供电解液的装置可以包括一个具有空腔的杯子,在导电材料沉积过程中电解液从其中流过。阳极可以容纳在空腔中,而接头置于所述空腔之外。该装置进一步包括一个用以向空腔提供电解液的入口。

一个可旋转的,而且最好是可移动的载体在导电材料沉积过程中支持着衬底,用以相对接头移动衬底表面。

在导电材料沉积过程中成形板可置于阳极和表面之间。成形板是多孔的并可让电解液穿过。

如果系统的极性反转了,系统就可以用来通过电蚀刻以均匀的方式从晶片或衬底表面移除材料,而不是沉积材料。在此情形中,电镀电解液可更换为通常所知的电蚀刻或电抛光溶液。而且,在此情形中,阳极可更换为惰性材料制成的惰性电极。

根据本发明的一种在具有最大侧向尺寸的晶片的表面沉积材料的系统,该系统包括:阳极,该阳极置于由终止于围缘的围壁所限定的空腔中,其中晶片被支撑于围缘上方以使晶片表面朝向空腔,并且其中围缘的侧向尺寸大于晶片的最大侧向尺寸;充满空腔直到围缘的电解液,因而电解液总是与晶片表面的第一区域相接触;以及电接触子,用以在邻近于空腔围壁的位置接触晶片表面的第二区域,其中第二区域在晶片旋转时间歇地接触电解液。

根据上述系统,其中第二区域为沿晶片圆周延伸的接触区域,并且其中该接触区域环绕第一区域。

根据上述系统,其中接触子为接触接触区域的导线。

根据上述系统,其中当电解液在晶片表面流动时电解液接触晶片。

根据上述系统,其中晶片由晶片载体从晶片背表面支撑。

根据上述系统,其中晶片载体对晶片背表面施加负压吸引以使晶片保持在晶片载体上。

根据上述系统,其中晶片载体包括卡环来沿晶片圆周夹持晶片。

根据上述系统,其中由围壁的围缘所确定的范围大于晶片表面的范围。

根据本发明的一种用以在具有最大侧向尺寸的晶片的表面沉积材料的系统,该系统包括:阳极;成形板,它限定了一个边缘,该成形板被支撑于阳极和晶片表面之间因而成形板的上表面朝向晶片表面,成形板包括大量开孔,其中成形板上表面具有大于晶片最大侧向尺寸的侧向尺寸;液态电解液,流经成形板的开孔和晶片表面因而该电解液总是接触晶片表面的第一区域;以及电接触子,用以在邻近成形板边缘处与晶片表面的第二区域建立电接触,其中当晶片在成形板上方旋转时第二区域间歇地接触电解液。

根据上述系统,其中成形板具有第一部分和第二部分。

根据上述系统,其中第二部分的开孔数目多于第一部分。

根据上述系统,其中第二区域为沿晶片圆周延伸的接触区域,并且其中接触区域环绕第一区域。

根据上述系统,其中接触子为接触第二区域的导线。

根据上述系统,其中当电解液紧靠晶片表面流动时电解液与晶片表面接触。

根据上述系统,其中晶片由晶片承载装置从晶片背表面支撑。

根据上述系统,其中晶片载体相晶片背表面施加负压吸引以使晶片保持在晶片载体上。

根据上述系统,其中晶片载体包括卡环来沿晶片圆周夹持晶片。

根据本发明的一种在晶片表面沉积材料而不隔绝出任何区域用来做表面上的电接触的工艺,其中晶片具有最大侧向尺寸,该工艺包括下面的步骤:提供阳极;在阳极和晶片表面之间支撑成形板因而成形板上表面朝向晶片表面,成形板包括大量开孔因而每个开孔都使晶片表面和阳极之间可以流体流通,其中成形板上表面具有大于晶片最大侧向尺寸的侧向尺寸;使电解液流经成形板的开孔并在阳极和晶片表面之间流动;用接触子在邻近成形板边缘的位置上接触晶片表面的接触区域以对表面产生电接触;在阳极和接触子之间施加电势差以当晶片位于第一位置时将材料通过成形板沉积到晶片表面的沉积区域;以及在用接触子接触接触区域的同时将晶片移到第二位置,从而在接触区域和沉积区域上都沉积材料。

根据上述工艺,进一步包括用成形板接触晶片表面。

根上述工艺,进一步包括在用成形板接触晶片表面的同时沿第一方向相对成形板移动晶片。

根据上述工艺,其中第一方向平行于成形板边缘。

根据上述工艺,其中沿第一方向移动晶片包括将晶片从成形板第一部分移到成形板第二部分。

根据上述工艺,其中第一部分中的开孔数目少于第二部分中的开孔数目因而第二部分给出更高的沉积速率。

根据本发明的一种在晶片表面上沉积导电材料而不隔绝出任何区域用来做表面上的电接触的工艺,其中晶片具有最大侧向尺寸,该工艺包括下面的步骤:提供阳极,阳极置于由终止于围缘的围壁所限定的空腔中,其中围缘的侧向尺寸大于晶片的最大侧向尺寸;将晶片支撑在围缘上方因而晶片表面朝向空腔;用电解液充满空腔因而电解液接触晶片表面的第一区域;用接触子在邻近于空腔围壁的位置接触晶片表面的接触区域以建立对晶片表面的电接触;在阳极和接触子之间施加电势差以当晶片位于第一位置时通过成形板在晶片表面的第一区域连续地沉积材料;以及在用接触子接触接触区域的同时旋转晶片至第二位置,从而在第一区域和接触区域都沉积材料。

根据本发明的一种用以从具有最大侧向尺寸的晶片的表面蚀刻材料的系统,该系统包括:阴极,该阴极置于由终止于围缘的围壁所限定的空腔中,其中晶片被支撑于围缘上方以使晶片表面朝向空腔,并且其中围缘的侧向尺寸大于晶片的最大侧向尺寸;充满空腔直到围缘的电解液,因而电解液总是与晶片表面的第一区域相接触;以及电接触子,用以在邻近于空腔围壁的位置接触晶片表面的第二区域,其中第二区域在晶片旋转时间歇地接触电解液。

根据本发明的一种用以从具有最大侧向尺寸的晶片的表面蚀刻材料的系统,该系统包括:阴极;成形板,它限定了一个凹边,该成形板被支撑于阴极和晶片表面之间因而成形板的上表面朝向晶片表面,成形板包括大量开孔,其中成形板上表面具有大于晶片最大侧向尺寸的侧向尺寸;液态电解液,流经成形板的开孔和晶片表面因而该电解液总是接触晶片表面的第一区域;以及电接触子,用以在邻近成形板凹边处与晶片表面的第二区域建立电接触,其中当晶片在成形板上方旋转时第二区域间歇地接触电解液。

根据本发明的一种在晶片表面蚀刻材料而不隔绝出任何区域用来做表面上的电接触的工艺,其中晶片具有最大侧向尺寸,该工艺包括下面的步骤:提供阴极;在阴极和晶片表面之间支撑成形板因而成形板上表面朝向晶片表面,成形板包括大量开孔因而每个开孔都使晶片表面和阴极之间可以流体流通,其中成形板上表面具有大于晶片最大侧向尺寸的侧向尺寸;使电解液流经成形板的开孔并在阴极和晶片表面之间流动;用接触子在邻近成形板边缘的位置上接触晶片表面的接触区域以对表面产生电接触;在阴极和接触子之间施加电势差以当晶片位于第一位置时将材料通过成形板从晶片表面的蚀刻区域蚀刻下来;以及在用接触子接触接触区域的同时将晶片移到第二位置,从而从接触区域和蚀刻区域上都移除材料。

根据本发明的一种在晶片表面上沉积导电材料而不隔绝出任何区域用来做表面上的电接触的工艺,其中晶片具有最大侧向尺寸,该工艺包括下面的步骤:提供阳极,阳极置于由终止于围缘的围壁所限定的空腔中,其中围缘的侧向尺寸大于晶片的最大侧向尺寸;将晶片支撑在围缘上方因而晶片表面朝向空腔;用电解液充满空腔因而电解液接触晶片表面的第一区域;用接触子在邻近于空腔围壁的位置接触晶片表面的接触区域以建立对晶片表面的电接触;在阳极和接触子之间施加电势差以当晶片位于第一位置时通过成形板从晶片表面的第一区域连续地蚀刻材料;以及在用接触子接触接触区域的同时旋转晶片至第二位置,从而从第一区域和接触区域都蚀刻材料。

根据本发明的一种可将导电材料从电解液中沉积到半导体衬底表面的系统,包括:在材料沉积过程中向衬底表面提供电解液的装置,在所述的沉积过程中被电解液接触的阳极,以及至少一个在所述的沉积过程中与表面在表面的选定范围电互连的触点,其中,当在阳极和触点之间施加电势差期间触点与表面至少一个相对于对方移动时,所述的沉积过程在所述的选定范围上间断地进行而在表面的其余部分连续地进行。

根据上述系统,进一步包括减轻表面上所述选定范围和其余部分之间材料沉积不均匀性的设备。

根据上述系统,其中该设备包括置于阳极和表面之间来改变电场分布的护罩。

根据上述系统,其中护罩包括在其上确定的开孔。

根据上述系统,其中该设备包括多孔元件,在阳极和表面之间提供具有不同开孔范围度的槽孔区域。

根据上述系统,其中所述的元件为一块板。

根据上述系统,其中所述的装置包括一个杯,它确定了一个在沉积过程中电解液所流经的空腔。

根据上述系统,其中所述的阳极容纳于空腔中。

根据上述系统,其中所述的触点置于空腔之外。

根据上述系统,其中所述的装置进一步包括用以向所述的空腔提供电解液的入口。

根据上述系统,进一步包括在所述的沉积过程中夹持衬底的载体。

根据上述系统,其中所述的载体是可旋转的以相对触点移动表面。

根据上述系统,进一步包括置于所述的阳极和表面之间并在沉积过程中极接近表面的成形元件。

根据上述系统,其中所述的成形元件是多孔的且允许电解液流过。

根据上述系统,其中所述的元件为成形板。

根据本发明的一种能将导电材料从电解液中沉积到半导体衬底表面的工艺,包括:向衬底表面提供电解液并使阳极与电解液相接触,在表面的选定范围使至少一个触点与表面电互连,以及在触点和表面至少一个相对于对方移动的同时,在阳极和触点之间施加电势差以在所述的选定范围上间断地沉积材料而在表面的其它部分连续地沉积材料。

根据上述工艺,进一步包括减轻在所述选定范围和表面其它部分之间材料沉积的不均匀性。

根据本发明的一种能从半导体衬底表面移除导电材料的系统,包括:在材料移除过程中向衬底表面提供电刻蚀溶液的装置,在所述的移除过程中被溶液接触的电极,以及至少一个在所述的移除过程中在表面的选定范围与表面电互连的触点,其中,当在电极和触点之间施加电势差期间接触和表面至少一个相对于对方移动时,所述的移除过程在选定范围间断地进行而在表面的其它部分连续地进行。

根据本发明的一种从半导体衬底表面移除导电材料的工艺,包括:在材料移除过程中向衬底表面提供电蚀刻溶液并且使电极与溶液接触,在表面的选定范围使至少一个触点与表面电互连,以及在触点和表面至少一个相对于对方移动的同时,在电极和触点之间施加电势差以从所述的选定范围间断地移除材料而从表面的其它部分连续地移除材料。

根据本发明的一种在晶片处理过程中用以与具有导电层的该晶片建立电接触的系统,该晶片在其前表面具有边缘部分和内侧部分,该系统包括:至少一个仅与导电层在晶片边缘部分建立电接触的接触子,其中在晶片处理过程中至少一个接触子与晶片之间的相对运动导致至少一个接触子电接触晶片边缘部分的不同部分。

根据上述系统,其中该至少一个接触子是导电刷、针和滚筒之一。

根据上述系统,进一步包括两个接触子,以使每个接触子置于基本相对的边缘部分并且每个接触子电接触晶片边缘部分的不同部分。

根据上述系统,其中晶片由晶片载体从晶片背表面支撑,并且相对运动包括晶片和该至少一个接触子之间的相对旋转运动。

根据上述系统,其中两个接触子中的每一个都是固定在静止位置而晶片载体旋转。

根据上述系统,其中晶片由晶片载体从晶片背表面支撑,并且相对运动包括晶片和该至少一个接触子之间的相对旋转运动。

根据上述系统,其中该至少一个接触子是固定于静止位置而晶片载体旋转。

根据本发明的一种在晶片处理过程中用以与具有导电层的该晶片建立电接触的方法,该晶片在其前表面具有边缘部分和内侧部分,该方法包括:在晶片处理过程中,在至少一个接触子和晶片导电层之间仅在晶片的边缘部分建立相对运动,以导致该至少一个接触子电接触晶片边缘部分的不同部分。

根据上述方法,其中该运动包括旋转运动,该至少一个接触子与晶片之间的每个相对旋转运动导致晶片的每旋转一次都重复了与晶片边缘部分的不同部分的电接触。

根据上述方法,其中旋转运动由至少一个固定的接触子以及随可旋转晶片载体转动的晶片导致。

根据上述方法,其中该至少一个接触子包括两个接触子,因而每个接触子置于基本相对的边缘部分并且每个接触子在建立相对运动的步骤中电接触晶片边缘部分的不同部分。

根据上述方法,其中建立相对运动的步骤进一步包括至少一个电接触子和晶片边缘部分的相对直线运动。

根据本发明的一种使用溶液处理晶片的电化学处理系统,该晶片具有导电层,在其前表面上有边缘部分和内侧部分,该系统包括:用以夹持晶片的晶片载体;电极;以及至少一个接触子,在至少向晶片内侧部分注入溶液并且在电极和晶片之间保持电势差来电化学处理晶片的同时,仅在晶片边缘部分与导电层建立电接触,其中在电化学处理过程中该至少一个接触子和晶片之间的相对运动导致该至少一个接触子电接触晶片边缘部分的不同部分。

根据上述系统,其中保持于电极和晶片之间的电势差导致导体从溶液中向至少是导电层的内侧部分的沉积。

根据上述系统,其中保持于电极和晶片之间的电势差导致导体从至少是导电层的内侧部分上的蚀刻。

根据上述系统,其中该至少一个接触子为导电刷、针和滚筒之一。

根据上述系统,进一步包括两个接触子,使得每个接触子置于晶片的基本相对的边缘部分。

根据上述系统,其中晶片由晶片载体从晶片背表面支撑,并且相对运动包括晶片和该至少一个接触子之间的相对旋转运动。

根据上述系统,其中两个接触子中的每一个都安在一个固定位置上而晶片载体旋转。

根据上述系统,其中晶片由晶片载体从晶片背表面支撑,并且相对运动包括晶片和该至少一个接触子之间的相对旋转运动。

根据上述系统,其中该至少一个接触子安在一个固定位置上而晶片载体旋转。

根据上述系统,进一步包括一个护罩。

根据上述系统,其中安装护罩来电化学处理晶片使得导体以基本均匀的方式沉积到导电层上。

根据上述系统,其中安装护罩来电化学处理晶片使得从导电层上蚀刻下均匀量的导体。

根据本发明的一种使用溶液处理晶片的电化学处理方法,该晶片具有导电层,在其前表面上有边缘部分和内侧部分,该方法包括:在晶片导电层和电极之间保持电势差,此电势差的保持包括:使至少一个接触子和导电层仅在晶片边缘部分产生相对运动,此相对运动导致该至少一个接触子电接触晶片边缘部分的不同部分;以及在保持电势差和相对运动的同时使用溶液在至少是晶片的内侧部分上进行电化学处理。

根据上述方法,其中电极和晶片之间保持的电势差导致导体从溶液中向至少是导电层内侧部分的沉积。

根据上述方法,其中沉积的导体为铜,使用铜沉积溶液。

根据上述方法,其中电极和晶片之间保持的电势差导致导体的从至少是导电层内侧部分的蚀刻。

根据上述方法,其中蚀刻的导体为铜,使用蚀刻溶液。

根据上述方法,其中相对运动包括旋转运动并且该至少一个接触子和晶片之间的每个相对旋转导致晶片每旋转一次都重复了与晶片边缘部分的不同部分的电接触。

根据上述方法,其中旋转运动由至少一个固定的接触子以及随可旋转晶片载体转动的晶片导致。

根据上述方法,其中该至少一个接触子包括两个接触子,因而每个接触子置于基本相对的边缘部分并且每个接触子在建立相对运动的步骤中电接触晶片边缘部分的不同部分。

根据上述方法,其中建立相对运动的步骤进一步包括至少一个电接触子和晶片边缘部分的相对直线运动。

根据本发明的一种使用溶液处理晶片的电化学机械处理系统,该晶片具有导电其,在其前表面上有边缘部分和内侧部分,该系统包括:用以夹持晶片的晶片载体;电极;靠近晶片安置并位于电极和晶片之间的衬垫,用以在有溶液参与的情况下通过物理接触晶片前表面来在晶片前表面上操作;以及至少一个接触子,仅在晶片边缘部分与导电层建立电接触,其中该至少一个接触子和晶片之间的相对运动导致该至少一个接触子电接触晶片边缘部分的不同部分,并且,在保持相对运动的同时,使衬垫通过物理接触晶片前表面来在晶片的前表面上操作。

根据上述系统,其中靠近晶片安置的衬垫不覆盖晶片的一部分,并且其中该衬垫做成具有高电流密度的一块区域和低电流密度的另一块区域。

根据上述系统,进一步包括相对衬垫侧向移动晶片的装置。

根据上述系统,其中晶片由晶片载体从晶片背表面支撑,并且相对运动包括晶片和该至少一个接触子之间的相对旋转运动。

根据上述系统,其中晶片由晶片载体从晶片背表面支撑,载体转动晶片以导致此相对旋转运动,该至少一个接触子安在一个固定位置上。

根据上述系统,其中保持于电极和晶片之间的电势差导致导体从溶液中向至少是导电层的内侧部分的沉积。

根据上述系统,其中保持于电极和晶片之间的电势差导致导体从至少是导电层的内侧部分上的蚀刻。

根据上述系统,进一步包括两个接触子,因而每个接触子置于晶片的基本相对的边缘部分。

根据上述系统,其中晶片由晶片载体从晶片背表面支撑,并且相对运动包括晶片和两个接触子之间的旋转运动。

根据上述系统,其中两个接触子中的每一个都安在一个固定位置上而晶片载体旋转。

根据上述系统,其中晶片由晶片载体从晶片背表面支撑,相对运动包括晶片和该至少一个接触子之间的相对旋转运动。

根据上述系统,其中晶片由晶片载体从晶片背表面支撑,载体转动晶片以导致此相对旋转运动,该至少一个接触子安在一个固定位置上。

根据本发明的一种使用溶液处理晶片的电化学机械处理方法,该晶片具有导电层,其前表面上有边缘部分和内侧部分,该方法包括:在晶片导电层和电极之间保持电势差,此电势差的保持包括:使至少一个接触子和导电层仅在晶片边缘部分产生相对运动,此相对运动导致该至少一个接触子电接触晶片边缘部分的不同部分;以及在保持电势差和相对运动的同时使用溶液在至少是晶片的内侧部分上进行电化学机械处理,电化学机械处理包括在有溶液参与的情况下移动衬垫,该衬垫有摩擦地接触晶片并且位于电极和晶片之间。

根据上述方法,其中在进行电化学机械处理的步骤中衬垫不覆盖晶片的一部分,并且其中该衬垫做成具有高电流密度的一块区域和低电流密度的另一块区域。

根据上述方法,其中进行电化学机械处理的步骤进一步包括相对衬垫侧向移动晶片。

根据上述方法,其中相对运动包括旋转运动并且该至少一个接触子和晶片之间的每个相对旋转导致晶片每旋转一次都重复了与晶片边缘部分的不同部分的电接触。

根据上述方法,其中旋转运动由至少一个固定的接触子以及随可旋转晶片载体转动的晶片导致。

根据上述方法,其中该至少一个接触子包括两个接触子,因而每个接触子置于基本相对的边缘部分并且每个接触子在建立相对运动的步骤中电接触晶片边缘部分的不同部分。

根据上述方法,其中建立相对运动的步骤进一步包括至少一个电接触子和晶片边缘部分的相对直线运动。

根据上述方法,其中电极和晶片之间所保持的电势差导致导体从溶液中向至少是导电层内侧部分的沉积。

根据上述方法,其中沉积的导体为使用铜沉积溶液的铜。

根据上述方法,其中电极和晶片之间所保持的电势差导致导体从至少是导电层内侧部分的蚀刻。

根据上述方法,其中蚀刻的导体为使用蚀刻溶液的铜。

根据上述方法,其中相对运动包括旋转运动并且该至少一个接触子和晶片之间的每个相对旋转导致晶片每旋转一次都重复了与晶片边缘部分的不同部分的电接触。

根据上述方法,其中旋转运动由至少一个固定的接触子以及随可旋转晶片载体转动的晶片导致。

根据上述方法,其中该至少一个接触子包括两个接触子,因而每个接触子置于基本相对的边缘部分并且每个接触子在建立相对运动的步骤中电接触晶片边缘部分的不同部分。

根据上述方法,其中建立相对运动的步骤进一步包括至少一个电接触子和晶片边缘部分的相对直线运动。

根据本发明的一种供电化学机械处理系统用的衬垫,使用溶液在晶片的导电上表面上起作用,包括:用以物理接触至少是晶片的导电上表面的内区的上表面,从而当晶片和该上表面之间的相对旋转运动发生时,留下边区的一部分没有连续地与晶片进行物理接触;用以让溶液从衬垫背面流到衬垫正面的大量开孔,这些大量开孔进一步用以向一个至少与边区宽度相同的范围提供一个高电流密度区域,以及另一个低电流密度区域。

根据上述衬垫,其中具有开孔范围度比另一区域更高的区域,开孔范围允许溶液从背面流到正面。

根据上述衬垫,其中该区域中开孔的平均尺寸大于另一区域中另一些开孔的平均尺寸。

根据上述衬垫,其中该衬垫形状是矩形的并且这些开孔在该矩形形状的一边上,而那些另外的开孔在矩形形状的另一边上。

根据上述衬垫,其中该衬垫形状是矩形的并且该区域在该矩形形状的一边上,而那另外的区域在该矩形形状的另一边上。

根据上述衬垫,其中该衬垫形状是矩形的并且高电流密度区域在矩形形状的一边上,而那另外的低电流密度区域在矩形形状的另一边上。

参考下面的附图、描述和权利要求,将能更好地理解本发明的这些和其它的特点、方案和优点。

附图说明

图1A为在其顶部形成有隔绝结构的半导体衬底的示意图,其中该隔绝结构已被蚀刻以在衬底上形成沟槽和通孔部件;

图1B为图1A中所示的衬底的部分剖面图,其中在那些部件和隔绝或绝缘层上已形成了隔离层和种子层;

图1C为图1B中所示结构的示意图,其中在种子层上部分沉积了传统的等角层;

图1D为图1C中所示结构的示意图,其中此层已完全沉积了;

图1E为图1D中所示结构的示意图,其中形成了更平坦的层;

图2A为一种现有技术的电沉积系统的示意图;

图2B为另一种使用了护罩的现有技术的电沉积系统的示意图;

图3为本发明一个系统的一个实施方案的示意图,该系统用以在晶片的整个表面沉积导电材料,而不隔绝任何边缘区域;

图4为图3中所示系统的示意图,示出了与本发明阳极杯的外侧壁宽度相关的电接头和晶片上接触区域的位置;

图5为图3中所示系统的部分俯视图,示出了晶片上的间歇和连续沉积区域;

图6为图3中所示的本发明的系统的示意图,它包括置于系统阳极和阴极之间的护罩;

图7为用来在晶片整个表面沉积导电材料而不隔绝任何边缘区域的本发明的系统的另一实施方案的示意图;

图8为图7中所示系统的部分示意图,示出了本发明的一个晶片承载装置和一个成形板;

图9A为在其上置有晶片的成形板的俯视图,其中该晶片具有连续和间歇沉积区域;

图9B为该成形板的示意性剖面图,示出了整个成形板上连续的槽孔;

图9C为本发明的成形板的另一实施方案的示意图,其中该成形板有两个具有不同开孔密度的区域;

图10A为本发明的电沉积系统的示意性侧视图,示出了与本发明的成形板宽度相关的接触区域上的晶片电接头的状态;

图10B为本发明的电沉积系统的另一示意性侧视图,示出了沿本发明的成形板长度方向的晶片状态;

图11A为一晶片高度放大的剖面图,该晶片具有在进行本发明的沉积过程之前就已覆盖有种子层的通孔和沟槽部件;

图11B为图11A中所示结构的示意图,其中已使用本发明电沉积了一层沉积层;以及

图11C为图11B中所示结构的示意图,其中沉积层已沉积为平坦的样式。

具体实施方式

本发明包括通过电沉积工艺在半导体衬底或晶片的整个表面或全面沉积半导体材料。正如下面所要描述的,本发明提供了一种方法和一种系统,用以在半导体衬底的整个表面形成基本平坦的导电材料层,即没有晶片边缘隔绝。本发明的全面沉积工艺方便地获得了半导体晶片整个表面上诸如沟槽、通孔、接触孔等大量空腔中的导电材料沉积。在某一实施方案中,本发明使用了成形杯或阳极杯并直接向晶片表面供应电解液以在晶片表面上沉积导电材料。在另一实施方案中,导电材料通过多孔板来沉积。在该实施方案中,多孔板促进了导电材料的均匀沉积。在又一实施方案中,本发明通过多孔板获得导电材料在晶片表面部件中的沉积,同时通过使用本发明的多孔板接触、清扫和抛光该表面来使部件之间的上表面区域上的沉积最小化。

本发明的工艺显示了增强的沉积性能,导致了具有以前难以达到的平坦程度的沉积层以及具有超过使用现有技术工艺和设备制备的现有技术的沉积层材料性能的导电层。

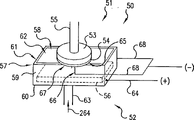

现在要给附图定下参数,其中相同数字始终表示相同部分。如图3中所示,在某一实施方案中,本发明的电沉积系统50可以包括上部51和下部52。在具体实施方案中,系统50可用来在像硅晶片这样的半导体晶片上沉积诸如铜这样的导电材料。然而,需要注意的是,尽管用铜作为例子,本发明还可用来沉积其它常见的导体,例如Ni、Pd、Pt、Au以及它们的合金。该电沉积系统50的上部51可包括具有与承载臂55相连的晶片载体53的承载装置,示于图3中,支撑着一块示范晶片54。

系统50的下部52可包括具有阳极56的阳极装置,阳极最好置于外壳中,例如阳极杯57或成形杯。阳极杯57可包括一个由从下盘60向上伸出的外侧壁59所限定的内腔58或壳体。外侧壁59的上缘框61形成了阳极杯57的上端。在该实施方案中,上缘框61优选地是矩形的,并且当晶片载体53向着边缘框61降下时调整边缘框的水平面使其基本平行于晶片54。如图5中所示,边缘框具有最大侧向尺寸D。镀铜电解液62可通过形成于下盘60中的液体入口63沿箭头264方向泵入阳极杯57中。这样,阳极杯和入口至少形成了向半导体晶片或衬底的前表面提供电解液62的装置的一部分。在电沉积过程中,阳极杯57充满电解液62,直到边缘框61。阳极56通过阳极接线64与电源(未示出)正极电连通。在电沉积过程中,晶片54保持与边缘框61基本平行又极为接近,并可旋转。通过控制电解液的流速,电解液与极接近的晶片前表面65接触。剩下的电解液在外侧壁59上流下,并被收集起来以备循环使用。

在此实施方案中,应该明白电接触子66与晶片54在前表面65的接触区域67接触或换句话说电互连。当晶片54在阳极杯57上方旋转时,接触区域67的位置相对于边缘框61成环形改变。接触子66通过使用接线68与电源(未示出)负极相连。

如图4中所示,晶片载体53从晶片54的背表面支撑晶片并使其紧靠晶片载体53的卡盘面。晶片54可通过使用负压吸引或卡环70(示于图4中)或二者都用上来夹持,从而完全暴露了晶片54的前表面65和接触区域67。依照本发明的原理,晶片54确定了一个最大侧向尺寸d,在此情形中它为晶片直径。作为选择地,卡环70可以是晶片载体53的一个组成部分。在此过程中,可以通过绕着转轴71或晶片载体53的垂直轴沿转动方向72转动承载臂55来使晶片载体53故而晶片54转动。正如下面所要更完整地描述的,旋转运动使接触区域67在电解液62表面移动并将接触区域67暴露在电解液前。晶片54前表面65的完全暴露以及通过在阳极杯57上方移动接触区域67而使它们暴露于电解液62前的能力的混合作用导致了晶片54上的零边缘隔绝。

如图4和5中所示,在该实施方案中,成形杯或阳极杯57的外侧壁59通常可制作成矩形侧壁,它包括第一侧壁73、第二侧壁74、第三侧壁75和第四侧壁76。在该实施方案中,第一和第二侧壁73、74长度上可长于第三和第四侧壁75、76的长度并形成外侧壁59的“凹”边77,即,相对于晶片54圆周外边凹入的边。第三和第四侧壁75、76形成了阳极杯57外侧壁的侧边78。在该实施方案中,阳极杯57的宽度或凹边77之间的距离被调整成小于晶片54的直径,该直径为晶片的最大侧向距离d,而等于边缘框61最大侧向距离D的阳极杯长度或侧边之间的距离被调整成大于晶片直径。

由于最大侧向距离d和上缘框宽度之间的差别,这种结构暴露了晶片54的接触区域67并允许电接触子66对接触区域67的接触。尽管在该实施方案中凹边77是直的,但在本发明的范围内凹边77可形成为凹陷的、V形的或任何可在晶片前表面65形成电接触的可能结构。应当指出,在任一给定时刻,只有当接触区域67旋转到电解液62上方时晶片54的接触区域67才能被镀上铜。在这方面,当晶片54旋转时,图5中虚线圆所示的第一范围79总是位于阳极杯上方并被连续电镀。然而,在表面上位于第一范围79之外并被接触区域所限定的选定的第二范围80中,沉积过程以不连续的方式进行。所以,第一范围79中的沉积速率和第二范围80中的沉积速率不一样从而第二范围80会具有更薄的沉积层。

图6示出了通过使用护罩82是如何使沉积层中的不均匀性得以减轻的。护罩82浸入电解液中并图6中所示的方式置于接近第一范围79处,尽管作为选择地,如果阳极到阴极(晶片)的距离减小了,它们可以搁在阳极56上。护罩82上可有孔洞99或开孔。护罩改变了阳极和晶片上第一范围79(见图5)或接触区域67之间的电场分布,并且改变第一范围79上的沉积速率,从而调整横过晶片前表面电沉积铜的厚度轮廓。在该实施方案中,护罩82可用像聚合物材料这样的非导电材料制成。

回过来看图4和6,使用中,电解液沿箭头264的方向泵入阳极杯57中。一旦在外加压力下电解液充满阳极杯57,电解液沿箭头81的方向到达晶片54的前表面。正如前面提到的,晶片54的前表面极靠近电解液。晶片54的前表面65和电解液液面之间的空隙可通过沿轴71垂直移动承载装置53来调整。在调整前表面65和电解液之间的距离之后,电沉积过程通过在阳极56和接触子66之间施加电势差来启动。因此,在这一步中,选择电势差使接触子比阳极电势更低(-)。进一步,由于接触子碰触到晶片54的前表面65,前表面65也成为阴极。正如前面提到的,晶片54的接触区域只有当接触区域67旋转到电解液上方并暴露在电解液前时才能被镀上铜。箭头82所描述的溢出电解液可被收集起来用作循环。

如图7中所示,在另一实施方案中,本发明的一个电沉积系统100可优选地包括上部102和下部104。在具体实施方案中,系统100可用以在像硅晶片这样的半导体晶片上沉积像铜这样的导电材料。和前面的实施方案一样,尽管用铜作为例子,本发明还可用来沉积其它常见的导体,例如Ni、Pd、Pt、Au以及它们的合金。电沉积系统100的上部102可包括具有与承载臂110相连的晶片载体106的承载装置,示于图7中,支撑着一块示范晶片108。承载臂可旋转或者侧向或垂直移动晶片108。

系统100的下部104可包括阳极装置和成形板114,阳极装置包括一个阳极112,最好是可消耗的铜阳极。阳极可优选地置于一外壳中,例如阳极杯116,并被阳极板118所封闭,成形板114可置于阳极板118上。成形板114和阳极板118都最好是多孔板。成形板114可包括大量开孔120或槽孔。开孔120被调整成与阳极板118上的开孔(见图10A和10B)广泛相配,所以当它们贴在一起时,对应的开孔形成渠道,使电解液在电沉积过程中流经板114和118并浸湿晶片108的前表面。在电沉积过程中,晶片108可保持与成形板114上表面119基本平行,并可旋转。晶片还可侧向移动。镀铜电解液通过液体入口121沿箭头122的方向泵入阳极杯116中。再一次,所以,阳极杯和入口至少形成了向半导体晶片或衬底前表面提供电解液的装置的一部分。阳极112通过阳极接线124与电源(未示出)的正接线柱电连接。应当指出如果成形板由刚性材料制成,阳极板118则可以不要。

正如下面将要详细描述的,在该实施方案中,电接触子126在接触区域128上与晶片108接触或换句话说电互连。当晶片108在成形板114上方旋转或移动时,接触区域128的位置相对成形板114做环形改变。接触子使用接线129与电源(未示出)的负接线柱相连。

如图8中所示,晶片载体106从晶片108的背表面130支撑晶片108。晶片可以图8中所示的方式被支撑在一较低的面131或晶片载体106的卡盘面上。在该实施方案中,晶片通过使用负压吸引或卡环133(示于图8中)或二者都用上来夹持,从而向电解液完全暴露了晶片108的前表面132。作为选择地,卡环133可以是晶片载体106的一个组成部分。在此过程中,可以通过绕着转轴134或晶片载体106的垂直轴沿转动方向135转动承载臂110来使晶片载体106故而晶片108转动。正如下面所要更完整地描述的,旋转运动使接触区域128在电解液62表面方便地移动并将接触区域128暴露在流经成形板(见图7)的电解液前。晶片108前表面132的完全暴露以及通过在成形板114上方移动接触区域128而使它们连续暴露于电解液前的能力的混合作用导致了晶片108上的零边缘隔绝。

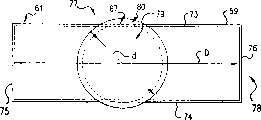

如图9A至9B中所示,在该实施方案中,本发明的成形板114通常制成由第一侧壁136、第二侧壁138、第三侧壁140和第四侧壁142所限定的矩形。在该实施方案中,第一和第二侧壁136、138可长于第三和第四侧壁140、142并形成成形板114的“凹”边,即,相对于晶片108圆周外边凹入的边。第三和第四侧壁140和142形成成形板114的侧边。成形板114的宽度或凹边之间的距离设定成小于晶片108的直径d。与前面的实施方案类似,侧边146之间的距离为成形板最大侧向尺寸D。进一步,晶片的直径为晶片108的最大侧向尺寸d。尽管在具体实施方案中成形板114被制成矩形,成形板可被赋予任何几何形状。

如图9A中所示,侧向距离d和成形板宽度之间的差别暴露了晶片108上的接触区域128并进一步允许电接触子126在接触区域128上的接触(见图7)。尽管在该实施方案中凹边的形状是直的,但在本发明的范围内凹边可形成为凹陷的、V形的或任何可在晶片前表面形成电接触的可能结构。通过选择上面所描述的成形板114的宽度和长度,当晶片108在成形板114上方沿第一方向147移动时,接触区域128可被接触子126接触或换句话说与它电互连。在图9A中,接触子以直条带形式示出,它碰触接触区域128。然而,应当指出,在一个给定时刻,只有当接触区域旋转到成形板114的槽孔上方时,晶片上的接触区域128才能被镀上铜。在这方面,当晶片旋转时,图9A中虚线圆所示的第一范围148总是位于成形板114上方并被连续电镀。然而,在表面上位于第一范围148之外并被接触区域所限定的选定的第二范围149中,沉积过程以不连续的方式进行。所以,第一范围148中的沉积速率和第二范围149中的沉积速率不一样从而第二范围149预期会具有稍薄一些的沉积层。正如下面所要描述的,此厚度上的差别可使用替换的槽孔设计来消除。另外,上面描述并示于图6中的互罩82可用于此实施方案中来提供沿晶片108前表面132的均匀沉积层。

参看图9B,槽孔120由延伸于成形板114上表面119的上开孔152和下表面156的下开孔154之间的内侧壁150所限定。正如前面提到的,在电沉积过程中,电解液溶液经由槽孔120到达晶片的前表面。取决于成形板114的功能性,成形板114可用绝缘材料或导电材料制成。若进行电沉积,成形板可由导电材料制成。然而,如果电沉积和抛光一起进行,则优选绝缘材料,例如聚合材料或陶瓷材料。尽管在此实施方案中槽孔120形状是矩形的,它们可以被制成不同的几何形状,例如椭圆形、方形、圆形或其它。槽孔120的形状和容积和密度决定了沉积膜的均匀性。槽孔120的内侧壁150无需垂直于上、下表面119和156,即,它们可以使倾斜的、弯曲的或其它形式或形状。

图9C示出了成形板114的一种替代的实施方案。在该实施方案中,成形板114包括第一和第二槽孔区157和158。由于它的设计,第二槽孔区158比第一槽孔区157具有更大的开孔范围度,这使它能在晶片上沉积更多的铜。当晶片通过环绕第一区域157中的位置A振动而被电镀时,可获得某种沉积层厚度轮廓并且沿接触区域128的沉积层厚度会稍微薄一些。为了提高沿接触区域128的厚度,晶片可被移至位置B,并且部分位于第二区域158至上,以使接触区域128受到更高的铜沉积速率。这一步可在电沉积过程的一部分期间进行以致可获得沉积铜层的均匀沉积轮廓。下面这些也在本发明的范围之内:这样的高密度区可在成形板114的一个或多个地点形成并且沉积层的厚度轮廓可随意改变或控制。也就是说,横过晶片前表面的厚度轮廓可做成凹面、凸面或平面。利用这种实施方案,边缘隔绝可以为零,即,整个晶片前表面可以均匀电镀一直到其边缘。

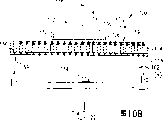

如图10A和10B所示,成形板置于具有大量孔洞159的阳极板118上。阳极板118中的孔洞159和成形板114中的槽孔120形成了连接阳极杯116内腔162和成形板114上表面119的连续电解液渠道160,阳极杯116在电镀过程中充满电解液。电解液沿箭头122的方向进入阳极杯并且沿箭头164的方向流经渠道160。在内腔162中可放置过滤器(未示出)来捕获阳极112在电镀过程中分解产生的微粒。阳极板118可由绝缘材料或导电材料制成。对于不使用可消耗阳极的系统来说,阳极板118可用作阳极或用另一个惰性阴极来代替阳极112。在这样的系统中,阳极板可用像钛这样的金属制成并且可以最好覆盖一层惰性金属,例如铂。因此,正电压连在阳极板上而不是连在可消耗阳极——例如在本发明情形中的铜阳极——上。

图10A还示出了用以接触接触区域128的接触子126的位置。接触子可制成各种外形,例如刷形、针形、滚筒形、平面等。接触子应与阳极充分隔绝,并且最好是固定的而使接触区域在其上滑动。接触子也可随晶片一起运动。接触子优选地由像铂、钌和难熔材料的氮化物等等柔性的抗腐蚀材料制成或被它们覆盖。正如前面所提到并且示于图10A中的,由于不用传统的夹子来建立与晶片108前表面132的电连接,沉积过程中的边缘隔绝很方便地降到了零。接触子对接触区可能产生的刮擦可通过确保接触子施加到接触区域上的力最小来避免或最小化。

回头来看图10A,在具体实施方案的工艺中,电解液沿箭头122的方向泵入电沉积系统100阳极杯116的内腔162中。一旦电解液充满内腔162,电解液沿箭头164方向通过流经阳极板118中的孔洞159然后成形板114中的槽孔120到达晶片108的前表面132。现在参看图10A至10B,晶片108的前表面132可沿轴134支持在第一位置上,最好极接近成形板114,例如距离0.25-5毫米。晶片108前表面132和成形板114之间的空隙可通过沿轴134垂直移动承载装置102来调整。在调整前表面132和成形板114上表面之间的距离后,电沉积过程通过在阳极112和接触子126之间施加电势差来启动。因此,在这一步中,电势差这样选择:接触子的电势比阳极更低。进一步,由于接触子碰触晶片108的前表面132,前表面132也成为阴极。

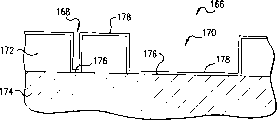

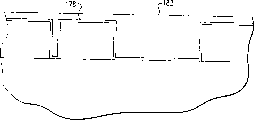

这里,可借助于图11A和11B进一步描述使用了本发明系统100的电沉积过程的细节。图11A举例说明了在电沉积过程之前晶片108前表面132(见图8)的表面部分166。表面部分166可包括通孔部件168或窄孔以及沟槽170或大孔。通孔部件168和沟槽部件170可形成于绝缘层172中,绝缘层形成在衬底上,衬底可以是晶片108的一部分或是形成在晶片上。部件168和170暴露了衬底174上的有源器件位置176。

参看图10B,一旦施加了电势差,当晶片108在成形板114上方如图10B中所示的方式沿旋转方向135旋转并沿第一方向147直线移动的同时,铜被电镀到前表面132上。第一方向147优选地平行于凹边144且垂直于侧边146。尽管在第一方向147的直线运动可优选地从大约5毫米到100毫米,取决于晶片尺寸,更长的直线运动也在本发明范围内且可被利用。在这方面,晶片108的旋转可从大约1rpm到250rpm。尽管优选地在侧向移动晶片,应该明白的是晶片是可旋转的并且阳极装置可侧向移动以获得在晶片和成形板之间的相似运动。如图11B中所示,随着沉积过程的进行,在铜种子层178上均匀形成了沉积层180并填满通孔和沟槽部件168和170。正如前面提到的,铜种子层178可形成于一隔离层顶上。正如前面还提到的,通过旋转晶片108,将使沉积层的非均匀性最小化。只有当接触区域128旋转到成形板114的槽孔120上方因而暴露在电解液前时,晶片上的接触区域128才能被镀上铜。

参看图10B,为沉积平面薄膜,成形板114和晶片108前表面之间的空隙可减小至零,而且通过沿轴134垂直移动承载装置102和晶片108至第二位置,前表面132与成形板114的上表面119相接触。在此情形中,成形板可由抛光垫做成。作为选择地,阳极装置104可沿轴134垂直移动,如果该装置具有此种移动能力的话。在第二位置中,由于晶片108旋转并沿第一方向147移动,当沉积过程继续时,晶片108触碰并摩擦成形板114。如图11C中所示,通过使绝缘层172顶上的沉积层180厚度最小化而在部件168和170中的材料沉积不受阻碍,这又形成了平面层182。

如果系统极性反转了,系统100可用来从晶片表面以均匀的方式移除材料(电蚀刻)而不是以均匀方式沉积材料。在此情形下,电镀电解液可用通常所知的电蚀刻或电抛光溶液。Cu电极可用惰性电极代替,惰性电极由诸如Pt、Ti或覆盖Pt的Ti材料这样的惰性材料制成。

当然应该明白的是,以上涉及的是本发明的优选实施方案,只要不背离权利要求书提出的本发明的精神和范围的修改都是可行的。

Claims (18)

1.在具有一个直径的晶片的表面上处理材料的设备,包括:

空腔,由终止于围缘的围壁所限定,具有至少一个小于晶片直径的侧向尺寸和至少一个大于晶片直径的侧向尺寸,被配置为保持接近围缘的处理溶液,使得处理溶液总是与第一晶片表面区域相接触;

一个头部,被配置为在空腔的上方保持晶片,使得晶片的表面面对空腔;以及

电接触子,位于空腔围壁的外面,被配置为接触第二晶片表面区域,在此,空腔的侧向尺寸小于晶片直径,并且当晶片相对于接触子移动时保持与晶片的电接触。

2.根据权利要求1的设备,其中,第二晶片表面区域为沿晶片圆周延伸的接触区域,并且其中该接触区域环绕第一晶片表面区域。

3.根据权利要求1的设备,其中,由围壁的围缘限定的区域大于晶片表面的区域。

4.根据权利要求1的设备,其中,材料被从晶片的表面移走。

5.根据权利要求1的设备,其中,材料被沉积在晶片的表面。

6.根据权利要求1的设备,还包括适于匹配在空腔和晶片之间的一个成形板,该成形板具有多个槽孔区。

7.根据权利要求6的设备,其中,所述头部被设置成将所述晶片移动到多个槽孔区。

8.根据权利要求6的设备,其中,所述多个槽孔区至少包括具有第一尺寸开口的第一槽孔区和具有第二尺寸开口的第二槽孔区。

9.根据权利要求6的设备,其中,面向晶片的成形板的顶表面包括一个抛光垫。

10.使用电极在晶片表面上处理材料而不排除任何用于表面上电接触的区域的方法,其中晶片的直径包括处理区域和接触区域,该方法包括步骤:

在电极和晶片表面之间支持一个成形板,使得成形板的上表面面对晶片表面,该成形板包括多个开口使得每一开口让晶片表面与电极流体地联通,其中成形板的上表面具有一个大于晶片直径的第一侧向尺寸和一个小于晶片直径的第二侧向尺寸;

使处理溶液流动通过成形板的开口和电极与晶片表面之间;

在相邻于成形板边缘的位置以接触子接触晶片表面的接触区域以便电接触晶片表面;以及

在电极和接触子之间施加电势差以便当晶片在第一位置时处理在处理区域上的材料和接触区域的一部分,和当晶片在另一位置时处理在处理区域上的材料和接触区域的另一部分。

11.根据权利要求10的方法,其中,成形板的上表面包括一个抛光垫,该方法还包括以抛光垫接触晶片表面的步骤。

12.根据权利要求10的方法,还包括沿基本上平行于成形板的上表面的方向移动晶片的步骤。

13.根据权利要求12的方法,其中,移动晶片的步骤包括旋转晶片。

14.根据权利要求13的方法,还包括控制在晶片的表面上被处理的材料的厚度剖面的步骤。

15.根据权利要求13的方法,其中,移动晶片的步骤包括将晶片从成形板的第一区域移动到成形板的第二区域。

16.根据权利要求15的方法,其中,第一区域以与第二区域不同的处理速率来处理材料。

17.根据权利要求10的方法,其中,在电极和接触子之间施加电势差的步骤将材料沉积到晶片的表面上。

18.根据权利要求10的方法,其中,在电极和接触子之间施加电势差的步骤将材料从晶片的表面上移除。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US24521100P | 2000-11-03 | 2000-11-03 | |

| US60/245,211 | 2000-11-03 | ||

| US09/760,757 | 2001-01-17 | ||

| US09/760,757 US6610190B2 (en) | 2000-11-03 | 2001-01-17 | Method and apparatus for electrodeposition of uniform film with minimal edge exclusion on substrate |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1433487A CN1433487A (zh) | 2003-07-30 |

| CN1253608C true CN1253608C (zh) | 2006-04-26 |

Family

ID=26937071

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB018044514A Expired - Fee Related CN1253608C (zh) | 2000-11-03 | 2001-11-02 | 处理具有最小边缘隔绝的衬底的方法和设备 |

Country Status (8)

| Country | Link |

|---|---|

| US (3) | US6610190B2 (zh) |

| EP (1) | EP1332243A2 (zh) |

| JP (1) | JP4034655B2 (zh) |

| KR (1) | KR100801270B1 (zh) |

| CN (1) | CN1253608C (zh) |

| AU (1) | AU2002246910A1 (zh) |

| TW (1) | TW511167B (zh) |

| WO (1) | WO2002057514A2 (zh) |

Families Citing this family (56)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7686935B2 (en) * | 1998-10-26 | 2010-03-30 | Novellus Systems, Inc. | Pad-assisted electropolishing |

| US7097755B2 (en) | 1998-12-01 | 2006-08-29 | Asm Nutool, Inc. | Electrochemical mechanical processing with advancible sweeper |

| US6534116B2 (en) * | 2000-08-10 | 2003-03-18 | Nutool, Inc. | Plating method and apparatus that creates a differential between additive disposed on a top surface and a cavity surface of a workpiece using an external influence |

| US6610190B2 (en) * | 2000-11-03 | 2003-08-26 | Nutool, Inc. | Method and apparatus for electrodeposition of uniform film with minimal edge exclusion on substrate |

| US6497800B1 (en) | 2000-03-17 | 2002-12-24 | Nutool Inc. | Device providing electrical contact to the surface of a semiconductor workpiece during metal plating |

| US6902659B2 (en) * | 1998-12-01 | 2005-06-07 | Asm Nutool, Inc. | Method and apparatus for electro-chemical mechanical deposition |

| US6251235B1 (en) | 1999-03-30 | 2001-06-26 | Nutool, Inc. | Apparatus for forming an electrical contact with a semiconductor substrate |

| US7204917B2 (en) * | 1998-12-01 | 2007-04-17 | Novellus Systems, Inc. | Workpiece surface influencing device designs for electrochemical mechanical processing and method of using the same |

| US6413388B1 (en) * | 2000-02-23 | 2002-07-02 | Nutool Inc. | Pad designs and structures for a versatile materials processing apparatus |

| US6355153B1 (en) * | 1999-09-17 | 2002-03-12 | Nutool, Inc. | Chip interconnect and packaging deposition methods and structures |

| US6852208B2 (en) | 2000-03-17 | 2005-02-08 | Nutool, Inc. | Method and apparatus for full surface electrotreating of a wafer |

| US7754061B2 (en) * | 2000-08-10 | 2010-07-13 | Novellus Systems, Inc. | Method for controlling conductor deposition on predetermined portions of a wafer |

| US6921551B2 (en) | 2000-08-10 | 2005-07-26 | Asm Nutool, Inc. | Plating method and apparatus for controlling deposition on predetermined portions of a workpiece |

| US20040170753A1 (en) * | 2000-12-18 | 2004-09-02 | Basol Bulent M. | Electrochemical mechanical processing using low temperature process environment |

| US7172497B2 (en) * | 2001-01-05 | 2007-02-06 | Asm Nutool, Inc. | Fabrication of semiconductor interconnect structures |

| US7211174B2 (en) * | 2001-01-17 | 2007-05-01 | Novellus Systems, Inc. | Method and system to provide electrical contacts for electrotreating processes |

| US7211186B2 (en) * | 2001-01-17 | 2007-05-01 | Novellus Systems, Inc. | Method and system to provide electrical contacts for electrotreating processes |

| US7244347B2 (en) * | 2001-01-17 | 2007-07-17 | Novellus Systems, Inc. | Method and system to provide electrical contacts for electrotreating processes |

| JP2005507170A (ja) * | 2001-10-26 | 2005-03-10 | ナトゥール・インコーポレイテッド | 電気的処理プロセスのための電気接点を形成する方法及びシステム |

| US6815354B2 (en) * | 2001-10-27 | 2004-11-09 | Nutool, Inc. | Method and structure for thru-mask contact electrodeposition |

| AU2002363479A1 (en) * | 2001-11-02 | 2003-05-19 | Nutool, Inc. | Electrochemical mechanical processing with advancible sweeper |

| US6776693B2 (en) * | 2001-12-19 | 2004-08-17 | Applied Materials Inc. | Method and apparatus for face-up substrate polishing |

| US20060137994A1 (en) * | 2001-12-21 | 2006-06-29 | Basol Bulent M | Method of wafer processing with edge seed layer removal |

| US7029567B2 (en) * | 2001-12-21 | 2006-04-18 | Asm Nutool, Inc. | Electrochemical edge and bevel cleaning process and system |

| US6833063B2 (en) * | 2001-12-21 | 2004-12-21 | Nutool, Inc. | Electrochemical edge and bevel cleaning process and system |

| AU2003226367A1 (en) * | 2002-04-12 | 2003-10-27 | Acm Research, Inc. | Electropolishing and electroplating methods |

| US7128823B2 (en) | 2002-07-24 | 2006-10-31 | Applied Materials, Inc. | Anolyte for copper plating |

| US7090750B2 (en) * | 2002-08-26 | 2006-08-15 | Micron Technology, Inc. | Plating |

| US20040226654A1 (en) * | 2002-12-17 | 2004-11-18 | Akihisa Hongo | Substrate processing apparatus and substrate processing method |

| US7201828B2 (en) * | 2003-02-25 | 2007-04-10 | Novellus Systems, Inc. | Planar plating apparatus |

| US20050173260A1 (en) * | 2003-03-18 | 2005-08-11 | Basol Bulent M. | System for electrochemical mechanical polishing |

| ATE418621T1 (de) * | 2003-04-24 | 2009-01-15 | Afshin Ahmadian | Verfahren zur detektion allelspezifischer mutationen |

| US7335288B2 (en) * | 2003-09-18 | 2008-02-26 | Novellus Systems, Inc. | Methods for depositing copper on a noble metal layer of a work piece |

| US20050170080A1 (en) * | 2003-10-29 | 2005-08-04 | Basol Bulent M. | System and method for electroless surface conditioning |

| US7064057B2 (en) * | 2003-11-21 | 2006-06-20 | Asm Nutool, Inc. | Method and apparatus for localized material removal by electrochemical polishing |

| US7648622B2 (en) * | 2004-02-27 | 2010-01-19 | Novellus Systems, Inc. | System and method for electrochemical mechanical polishing |

| US20060183321A1 (en) * | 2004-09-27 | 2006-08-17 | Basol Bulent M | Method for reduction of gap fill defects |

| US7550070B2 (en) * | 2006-02-03 | 2009-06-23 | Novellus Systems, Inc. | Electrode and pad assembly for processing conductive layers |

| EP1839695A1 (en) * | 2006-03-31 | 2007-10-03 | Debiotech S.A. | Medical liquid injection device |

| US8500985B2 (en) | 2006-07-21 | 2013-08-06 | Novellus Systems, Inc. | Photoresist-free metal deposition |

| US7732329B2 (en) * | 2006-08-30 | 2010-06-08 | Ipgrip, Llc | Method and apparatus for workpiece surface modification for selective material deposition |

| US20080237048A1 (en) * | 2007-03-30 | 2008-10-02 | Ismail Emesh | Method and apparatus for selective electrofilling of through-wafer vias |

| DE102007026633B4 (de) * | 2007-06-06 | 2009-04-02 | Atotech Deutschland Gmbh | Vorrichtung und Verfahren zum elektrolytischen Behandeln von plattenförmiger Ware |

| US20090065365A1 (en) * | 2007-09-11 | 2009-03-12 | Asm Nutool, Inc. | Method and apparatus for copper electroplating |

| TWI410531B (zh) * | 2010-05-07 | 2013-10-01 | Taiwan Semiconductor Mfg | 直立式電鍍設備及其電鍍方法 |

| US9988734B2 (en) | 2011-08-15 | 2018-06-05 | Lam Research Corporation | Lipseals and contact elements for semiconductor electroplating apparatuses |

| TWI609100B (zh) * | 2012-03-30 | 2017-12-21 | 諾發系統有限公司 | 使用反向電流除鍍以清洗電鍍基板夾持具 |

| WO2014098774A1 (en) * | 2012-12-21 | 2014-06-26 | Agency For Science, Technology And Research | Porous metallic membrane |

| BR112016009844B1 (pt) * | 2013-11-14 | 2022-02-22 | Toyota Jidosha Kabushiki Kaisha | Aparelho de formação de filme de filme metálico e método de formação de filme de filmemetálico |

| JP5826952B2 (ja) * | 2014-01-17 | 2015-12-02 | 株式会社荏原製作所 | めっき方法およびめっき装置 |

| JP6745103B2 (ja) * | 2014-11-26 | 2020-08-26 | ノベラス・システムズ・インコーポレーテッドNovellus Systems Incorporated | 半導体電気メッキ装置用のリップシールおよび接触要素 |

| US10053793B2 (en) | 2015-07-09 | 2018-08-21 | Lam Research Corporation | Integrated elastomeric lipseal and cup bottom for reducing wafer sticking |

| US20170145577A1 (en) * | 2015-11-19 | 2017-05-25 | Rohm And Haas Electronic Materials Llc | Method of electroplating low internal stress copper deposits on thin film substrates to inhibit warping |

| US20190096866A1 (en) * | 2017-09-26 | 2019-03-28 | Powertech Technology Inc. | Semiconductor package and manufacturing method thereof |

| JP2023504033A (ja) * | 2019-11-27 | 2023-02-01 | ラム リサーチ コーポレーション | レジストによるめっきのためのエッジ除去 |

| US11230778B2 (en) | 2019-12-13 | 2022-01-25 | Macdermid Enthone Inc. | Cobalt chemistry for smooth topology |

Family Cites Families (62)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3328273A (en) | 1966-08-15 | 1967-06-27 | Udylite Corp | Electro-deposition of copper from acidic baths |

| FR2510145B1 (fr) | 1981-07-24 | 1986-02-07 | Rhone Poulenc Spec Chim | Additif pour bain de cuivrage electrolytique acide, son procede de preparation et son application au cuivrage des circuits imprimes |

| US4948474A (en) | 1987-09-18 | 1990-08-14 | Pennsylvania Research Corporation | Copper electroplating solutions and methods |

| DE3836521C2 (de) | 1988-10-24 | 1995-04-13 | Atotech Deutschland Gmbh | Wäßriges saures Bad zur galvanischen Abscheidung von glänzenden und rißfreien Kupferüberzügen und Verwendung des Bades |

| US4954142A (en) | 1989-03-07 | 1990-09-04 | International Business Machines Corporation | Method of chemical-mechanical polishing an electronic component substrate and polishing slurry therefor |

| US5084071A (en) | 1989-03-07 | 1992-01-28 | International Business Machines Corporation | Method of chemical-mechanical polishing an electronic component substrate and polishing slurry therefor |

| US5256565A (en) | 1989-05-08 | 1993-10-26 | The United States Of America As Represented By The United States Department Of Energy | Electrochemical planarization |

| US5225034A (en) | 1992-06-04 | 1993-07-06 | Micron Technology, Inc. | Method of chemical mechanical polishing predominantly copper containing metal layers in semiconductor processing |

| JP3397501B2 (ja) | 1994-07-12 | 2003-04-14 | 株式会社東芝 | 研磨剤および研磨方法 |

| US5567300A (en) * | 1994-09-02 | 1996-10-22 | Ibm Corporation | Electrochemical metal removal technique for planarization of surfaces |

| US5516412A (en) | 1995-05-16 | 1996-05-14 | International Business Machines Corporation | Vertical paddle plating cell |

| US5795215A (en) | 1995-06-09 | 1998-08-18 | Applied Materials, Inc. | Method and apparatus for using a retaining ring to control the edge effect |

| US5681215A (en) | 1995-10-27 | 1997-10-28 | Applied Materials, Inc. | Carrier head design for a chemical mechanical polishing apparatus |

| DE69637333T2 (de) | 1995-06-27 | 2008-10-02 | International Business Machines Corp. | Kupferlegierungen für Chipverbindungen und Herstellungsverfahren |

| US5755859A (en) | 1995-08-24 | 1998-05-26 | International Business Machines Corporation | Cobalt-tin alloys and their applications for devices, chip interconnections and packaging |

| US5762544A (en) | 1995-10-27 | 1998-06-09 | Applied Materials, Inc. | Carrier head design for a chemical mechanical polishing apparatus |

| US5840629A (en) | 1995-12-14 | 1998-11-24 | Sematech, Inc. | Copper chemical mechanical polishing slurry utilizing a chromate oxidant |

| US5858813A (en) | 1996-05-10 | 1999-01-12 | Cabot Corporation | Chemical mechanical polishing slurry for metal layers and films |

| US5862605A (en) * | 1996-05-24 | 1999-01-26 | Ebara Corporation | Vaporizer apparatus |

| US5793272A (en) | 1996-08-23 | 1998-08-11 | International Business Machines Corporation | Integrated circuit toroidal inductor |

| US5773364A (en) | 1996-10-21 | 1998-06-30 | Motorola, Inc. | Method for using ammonium salt slurries for chemical mechanical polishing (CMP) |

| US5954997A (en) | 1996-12-09 | 1999-09-21 | Cabot Corporation | Chemical mechanical polishing slurry useful for copper substrates |

| WO1998027585A1 (en) | 1996-12-16 | 1998-06-25 | International Business Machines Corporation | Electroplated interconnection structures on integrated circuit chips |

| US5933753A (en) | 1996-12-16 | 1999-08-03 | International Business Machines Corporation | Open-bottomed via liner structure and method for fabricating same |

| US5911619A (en) | 1997-03-26 | 1999-06-15 | International Business Machines Corporation | Apparatus for electrochemical mechanical planarization |

| US5807165A (en) | 1997-03-26 | 1998-09-15 | International Business Machines Corporation | Method of electrochemical mechanical planarization |

| US5930669A (en) | 1997-04-03 | 1999-07-27 | International Business Machines Corporation | Continuous highly conductive metal wiring structures and method for fabricating the same |

| US5922091A (en) | 1997-05-16 | 1999-07-13 | National Science Council Of Republic Of China | Chemical mechanical polishing slurry for metallic thin film |

| US6001235A (en) | 1997-06-23 | 1999-12-14 | International Business Machines Corporation | Rotary plater with radially distributed plating solution |

| US5985123A (en) | 1997-07-09 | 1999-11-16 | Koon; Kam Kwan | Continuous vertical plating system and method of plating |

| AU5907798A (en) * | 1997-09-30 | 1999-04-23 | Semitool, Inc. | Electroplating system having auxiliary electrode exterior to main reactor chamber for contact cleaning operations |

| US5897375A (en) | 1997-10-20 | 1999-04-27 | Motorola, Inc. | Chemical mechanical polishing (CMP) slurry for copper and method of use in integrated circuit manufacture |

| US6027631A (en) | 1997-11-13 | 2000-02-22 | Novellus Systems, Inc. | Electroplating system with shields for varying thickness profile of deposited layer |

| US6156167A (en) | 1997-11-13 | 2000-12-05 | Novellus Systems, Inc. | Clamshell apparatus for electrochemically treating semiconductor wafers |

| US6159354A (en) | 1997-11-13 | 2000-12-12 | Novellus Systems, Inc. | Electric potential shaping method for electroplating |

| US6004880A (en) | 1998-02-20 | 1999-12-21 | Lsi Logic Corporation | Method of single step damascene process for deposition and global planarization |

| US5976331A (en) | 1998-04-30 | 1999-11-02 | Lucent Technologies Inc. | Electrodeposition apparatus for coating wafers |

| US6071388A (en) | 1998-05-29 | 2000-06-06 | International Business Machines Corporation | Electroplating workpiece fixture having liquid gap spacer |

| US6074544A (en) | 1998-07-22 | 2000-06-13 | Novellus Systems, Inc. | Method of electroplating semiconductor wafer using variable currents and mass transfer to obtain uniform plated layer |

| US6132587A (en) | 1998-10-19 | 2000-10-17 | Jorne; Jacob | Uniform electroplating of wafers |

| US6176992B1 (en) | 1998-11-03 | 2001-01-23 | Nutool, Inc. | Method and apparatus for electro-chemical mechanical deposition |

| US6534116B2 (en) * | 2000-08-10 | 2003-03-18 | Nutool, Inc. | Plating method and apparatus that creates a differential between additive disposed on a top surface and a cavity surface of a workpiece using an external influence |

| US6497800B1 (en) * | 2000-03-17 | 2002-12-24 | Nutool Inc. | Device providing electrical contact to the surface of a semiconductor workpiece during metal plating |

| US6902659B2 (en) * | 1998-12-01 | 2005-06-07 | Asm Nutool, Inc. | Method and apparatus for electro-chemical mechanical deposition |

| US6610190B2 (en) * | 2000-11-03 | 2003-08-26 | Nutool, Inc. | Method and apparatus for electrodeposition of uniform film with minimal edge exclusion on substrate |

| US7578923B2 (en) * | 1998-12-01 | 2009-08-25 | Novellus Systems, Inc. | Electropolishing system and process |

| US6589105B2 (en) * | 1998-12-01 | 2003-07-08 | Nutool, Inc. | Pad tensioning method and system in a bi-directional linear polisher |

| US6251235B1 (en) * | 1999-03-30 | 2001-06-26 | Nutool, Inc. | Apparatus for forming an electrical contact with a semiconductor substrate |

| US6103085A (en) | 1998-12-04 | 2000-08-15 | Advanced Micro Devices, Inc. | Electroplating uniformity by diffuser design |

| US6261426B1 (en) * | 1999-01-22 | 2001-07-17 | International Business Machines Corporation | Method and apparatus for enhancing the uniformity of electrodeposition or electroetching |

| US6066030A (en) | 1999-03-04 | 2000-05-23 | International Business Machines Corporation | Electroetch and chemical mechanical polishing equipment |

| US6136163A (en) * | 1999-03-05 | 2000-10-24 | Applied Materials, Inc. | Apparatus for electro-chemical deposition with thermal anneal chamber |

| JP3422731B2 (ja) * | 1999-07-23 | 2003-06-30 | 理化学研究所 | Elidセンタレス研削装置 |

| US6653226B1 (en) * | 2001-01-09 | 2003-11-25 | Novellus Systems, Inc. | Method for electrochemical planarization of metal surfaces |

| US6848970B2 (en) * | 2002-09-16 | 2005-02-01 | Applied Materials, Inc. | Process control in electrochemically assisted planarization |

| US6482307B2 (en) * | 2000-05-12 | 2002-11-19 | Nutool, Inc. | Method of and apparatus for making electrical contact to wafer surface for full-face electroplating or electropolishing |

| US6346479B1 (en) * | 2000-06-14 | 2002-02-12 | Advanced Micro Devices, Inc. | Method of manufacturing a semiconductor device having copper interconnects |

| US7220166B2 (en) * | 2000-08-30 | 2007-05-22 | Micron Technology, Inc. | Methods and apparatus for electromechanically and/or electrochemically-mechanically removing conductive material from a microelectronic substrate |

| US6696358B2 (en) * | 2001-01-23 | 2004-02-24 | Honeywell International Inc. | Viscous protective overlayers for planarization of integrated circuits |

| US7201829B2 (en) * | 2001-03-01 | 2007-04-10 | Novellus Systems, Inc. | Mask plate design |

| US6482656B1 (en) * | 2001-06-04 | 2002-11-19 | Advanced Micro Devices, Inc. | Method of electrochemical formation of high Tc superconducting damascene interconnect for integrated circuit |

| TW584899B (en) * | 2001-07-20 | 2004-04-21 | Nutool Inc | Planar metal electroprocessing |

-

2001

- 2001-01-17 US US09/760,757 patent/US6610190B2/en not_active Expired - Lifetime

- 2001-05-28 TW TW090112769A patent/TW511167B/zh not_active IP Right Cessation

- 2001-11-02 AU AU2002246910A patent/AU2002246910A1/en not_active Abandoned

- 2001-11-02 WO PCT/US2001/051158 patent/WO2002057514A2/en not_active Application Discontinuation

- 2001-11-02 CN CNB018044514A patent/CN1253608C/zh not_active Expired - Fee Related

- 2001-11-02 JP JP2002558562A patent/JP4034655B2/ja not_active Expired - Fee Related

- 2001-11-02 EP EP01994521A patent/EP1332243A2/en not_active Withdrawn

- 2001-11-02 KR KR1020027008660A patent/KR100801270B1/ko not_active IP Right Cessation

-

2003

- 2003-06-11 US US10/460,032 patent/US6942780B2/en not_active Expired - Lifetime

-

2005

- 2005-09-13 US US11/225,913 patent/US20060006060A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005501963A (ja) | 2005-01-20 |

| US6610190B2 (en) | 2003-08-26 |

| WO2002057514A3 (en) | 2003-02-06 |

| US20030209429A1 (en) | 2003-11-13 |

| TW511167B (en) | 2002-11-21 |

| KR20020095179A (ko) | 2002-12-20 |

| US20020053516A1 (en) | 2002-05-09 |

| WO2002057514A2 (en) | 2002-07-25 |

| AU2002246910A1 (en) | 2002-07-30 |

| US20060006060A1 (en) | 2006-01-12 |

| JP4034655B2 (ja) | 2008-01-16 |

| CN1433487A (zh) | 2003-07-30 |

| EP1332243A2 (en) | 2003-08-06 |

| KR100801270B1 (ko) | 2008-02-04 |

| US6942780B2 (en) | 2005-09-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1253608C (zh) | 处理具有最小边缘隔绝的衬底的方法和设备 | |

| CN1276483C (zh) | 以电化学机械研磨法进行衬底平坦化 | |

| CN1531028A (zh) | 电镀方法 | |

| CN1180133C (zh) | 应用调制电场在小深孔中的金属电淀积法 | |

| CN1220798C (zh) | 用于通用材料加工设备的衬垫设计和结构 | |

| CN1265425C (zh) | 基片处理装置 | |

| US9476139B2 (en) | Cleaning electroplating substrate holders using reverse current deplating | |

| CN1551931A (zh) | 用于控制电镀层厚度均匀性的方法和装置 | |

| CN1458671A (zh) | 用于电化学机械抛光的导电抛光用品 | |

| CN1639840A (zh) | 无电淀积设备和方法 | |

| CN100346009C (zh) | 电解加工装置和方法 | |

| CN1454266A (zh) | 用于电镀和平面化导电层的阳极装置 | |

| JP2005501963A5 (zh) | ||

| CN1137511C (zh) | 生产集成电路时由高纯铜电镀形成导体结构的方法 | |

| CN1551295A (zh) | 电子器件的制造方法 | |

| CN1842618A (zh) | 用于沉积半导体晶片薄膜和使其平面化的装置和方法 | |

| CN1572911A (zh) | 用于镀敷基片的装置和方法 | |

| CN1585835A (zh) | 电解抛光组件以及对导电层执行电解抛光的方法 | |

| CN1646264A (zh) | 用于微电子工件的电化学-机械加工的方法和设备 | |

| CN100346008C (zh) | 用于再生离子交换剂的方法与设备以及电解处理装置 | |

| CN1302155C (zh) | 用于电解处理相互分开的板材块和箔材块的可导电表面的方法和装置以及该方法的应用 | |

| TWI275667B (en) | Tilted electrochemical plating cell with constant wafer immersion angle | |

| CN1829587A (zh) | 用于电化学机械抛光的导电抛光物件 | |

| US20060124468A1 (en) | Contact plating apparatus | |

| CN1751382A (zh) | 镀覆装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20060426 Termination date: 20141102 |

|

| EXPY | Termination of patent right or utility model |