JP4034655B2 - 均一な薄膜を最小限のエッジ除外で基板上へ電着する方法および装置 - Google Patents

均一な薄膜を最小限のエッジ除外で基板上へ電着する方法および装置 Download PDFInfo

- Publication number

- JP4034655B2 JP4034655B2 JP2002558562A JP2002558562A JP4034655B2 JP 4034655 B2 JP4034655 B2 JP 4034655B2 JP 2002558562 A JP2002558562 A JP 2002558562A JP 2002558562 A JP2002558562 A JP 2002558562A JP 4034655 B2 JP4034655 B2 JP 4034655B2

- Authority

- JP

- Japan

- Prior art keywords

- wafer

- contact

- contact member

- pad

- region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/288—Deposition of conductive or insulating materials for electrodes conducting electric current from a liquid, e.g. electrolytic deposition

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25D—PROCESSES FOR THE ELECTROLYTIC OR ELECTROPHORETIC PRODUCTION OF COATINGS; ELECTROFORMING; APPARATUS THEREFOR

- C25D5/00—Electroplating characterised by the process; Pretreatment or after-treatment of workpieces

- C25D5/02—Electroplating of selected surface areas

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25D—PROCESSES FOR THE ELECTROLYTIC OR ELECTROPHORETIC PRODUCTION OF COATINGS; ELECTROFORMING; APPARATUS THEREFOR

- C25D17/00—Constructional parts, or assemblies thereof, of cells for electrolytic coating

- C25D17/001—Apparatus specially adapted for electrolytic coating of wafers, e.g. semiconductors or solar cells

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/288—Deposition of conductive or insulating materials for electrodes conducting electric current from a liquid, e.g. electrolytic deposition

- H01L21/2885—Deposition of conductive or insulating materials for electrodes conducting electric current from a liquid, e.g. electrolytic deposition using an external electrical current, i.e. electro-deposition

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76877—Filling of holes, grooves or trenches, e.g. vias, with conductive material

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25D—PROCESSES FOR THE ELECTROLYTIC OR ELECTROPHORETIC PRODUCTION OF COATINGS; ELECTROFORMING; APPARATUS THEREFOR

- C25D7/00—Electroplating characterised by the article coated

- C25D7/12—Semiconductors

- C25D7/123—Semiconductors first coated with a seed layer or a conductive layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3205—Deposition of non-insulating-, e.g. conductive- or resistive-, layers on insulating layers; After-treatment of these layers

- H01L21/321—After treatment

- H01L21/32115—Planarisation

- H01L21/3212—Planarisation by chemical mechanical polishing [CMP]

Description

【発明の属する技術分野】

本発明は一般に、電着プロセス技術、およびより詳細には、均一で平坦な堆積物を形成する電着プロセスに関する。

【0002】

【従来の技術】

従来の半導体デバイスは一般に、半導体基板(通常、シリコン基板)と、順次形成された複数の誘電体中間層(二酸化珪素など)と、導電材料から作られた導電性経路またはインターコネクトとを備える。インターコネクトは通常、導電材料を、誘電体中間層内部にエッチングされたトレンチに充填して、形成される。集積回路においては、複数のレベルのインターコネクトネットワークが、基板表面に対して横方向に延びている。異なる層内に形成されたインターコネクトは、ビアまたはコンタクトを用いて電気的に接続することができる。このようなフィーチャー(features)、すなわちビア開口部、トレンチ、パッドまたはコンタクトへの導電材料充填プロセスは、導電材料を、このようなフィーチャーを含む基板上へ堆積させることによって行なうことができる。次に、基板上の過剰な導電材料を、平坦化または研磨技術たとえば化学的機械研磨(CMP)を用いて、除去することができる。

【0003】

最近、銅(Cu)および銅合金が、インターコネクト材料として著しい注目を受けている。その理由は、エレクロトマイグレーションが優れており、低抵抗率の特性であるからである。Cu堆積の好ましい方法は、電着である。製造の際、銅を、予めバリアまたはシード層がコートされた基板上に、電気メッキまたは電着する。典型的なバリア材料には一般に、タングステン(W)、タンタル(Ta)、チタン(Ti)、これらの合金およびこれらの窒化物が含まれる。銅用の典型的なシード材料は通常、銅の薄層であり、この層を前述のバリア層上にCVDまたはPVDによって堆積する。

【0004】

Cuメッキシステムには、多くの様々なデザインがある。例えば、米国特許第5,516,412号(1996年5月14日にAndricacosらに付与)には、薄膜を平坦な物品上に電着するように構成された垂直パドルメッキ槽が開示されている。米国特許第5,985,123号(Koonに1999年11月16日に付与)には、さらに他の垂直型電着装置(基板サイズの変化に関連する不均一堆積の問題を打開すると称する)が開示されている。

【0005】

Cu電着プロセスの際、特別に配合されたメッキ溶液または電解液が用いられる。これらの溶液または電解液には、堆積された材料のテクスチャー、モホロジー、およびメッキ挙動を制御するために、Cuのイオン種と添加剤とが含まれている。添加剤は、堆積層を平坦にし幾らか光沢を出すために必要である。

【0006】

Cuメッキ溶液の組成物には多くのタイプがあり、一部は市販されている。このような組成物の一つには、銅源としての硫酸Cu(CuSO4)(James Kellyら、Journal of The Electrochemical Society、Vol.146、ページ2540-2545、(1999)を参照)が含まれ、また水、硫酸(H2SO4)、および小量の塩化物イオンが含まれる。

【0007】

良く知られているように、所望の特性の堆積材料を得るために、その他の化学薬品(添加剤と呼ばれることが多い)をCuメッキ溶液に加えることができる(例えば、Robert MikkolaおよびLinlin Chen、「Investigation of the Roles of the Additive Components for Second Generation Copper Electroplating Chemistries used for Advanced Interconnect Metallization」、Proceedings of the International Interconnect Technology Conference、ページ117-119、6月5-7、2000を参照)。

【0008】

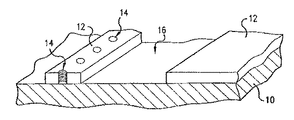

図1A〜2Bに、従来の電着方法および装置を例示する。図1Aには、基板10と、その上に形成された絶縁層12とが示されている。従来のエッチング技術を用いて、小さいビア14の列および幅広いトレンチ16などのフィーチャーが、絶縁層12上、および基板10の露出領域上に形成される。この例では、ビア14が狭く深い。言い換えれば、ビア14はアスペクト比が高い(すなわち、その深さと幅との比が大きい)。典型的に、ビア14の幅はサブミクロンである。一方、この例に示されるトレンチ16は、幅が広く、アスペクト比が小さい。トレンチ16の幅は、その深さよりも5〜50倍またはそれ以上大きい場合がある。

【0009】

図1B〜1Cに、フィーチャーに銅材料を充填するための従来の方法を示す。図1Bには、バリア/グルーまたは付着層18とシード層20とが、基板10および絶縁物12上に、連続して堆積されているのが示されている。バリア層18は、Ta、W、Ti、これらの合金、これらの窒化物、またはこれらの組み合わせであり得る。バリア層18は一般に、種々のスパッタリング方法の何れかを用いて、化学気相成長(CVD)によって、または無電解メッキ法によって堆積させる。その後、シード層20を、バリア層18上に堆積させる。シード層20は、メッキすべき導体が銅である場合に、典型的に銅である。またシード層20は、バリア層18上に、種々のスパッタリング方法、CVD、もしくは無電解メッキまたはこれらの組み合わせを用いて、堆積させることができる。

【0010】

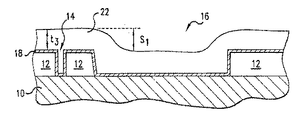

図1Cにおいて、シード層20を堆積させた後に、導電材料層22(たとえば銅層)を、シード層20上に、好適なメッキ浴または浴組成物から部分的に電着させる。この工程の際、電気コンタクト部材を銅シード層20および/またはバリア層18に形成することで、アノード(図示せず)に対するカソード(負)電圧を、その層に印加することができる。その後、前述したように、銅材料層22を基板表面上にメッキ溶液を用いて電着する。添加剤(塩化物イオンなど)、抑制剤(suppressor)/抑止剤(inhibitor)、および促進剤の量を調整することによって、小さいフィーチャー内においてボトムアップ銅薄膜成長を得ることができる。

【0011】

図1Cに示すように、銅材料22はビア14には完全に充填されるとともに、通常大きなトレンチ16内ではコンフォーマル(conformal)である。これは使用した添加剤が大きなフィーチャー内では効力がないからである。例えば、ビア14内へのボトムアップ堆積が起こるのは、抑制剤/抑止剤の分子がそれ自身をビア14の頂部に付着させて、その付近の材料成長を抑制するからだと考えられている。これらの分子は、狭い開口部を通ってビア14の底面へ効果的に拡散することはできない。ビア14の底面へ促進剤を優先的に吸着させることによって、その領域での成長を速めることができる。その結果、ボトムアップ成長および図1Cに示すようなCu堆積プロファイルが得られる。ここで、トレンチ16の底面でのCu厚みt1は、絶縁層12上のCu厚みt2とほぼ同じである。

【0012】

予想され得るように、トレンチ16をCu材料で完全に充填するためには、さらにメッキすることが必要である。図1Dに、追加のCuメッキ後に結果として得られる構造を示す。この場合、絶縁層12上のCu厚みt3は比較的大きく、絶縁層12上のCu層の頂部からトレンチ16内の銅層22の頂部までの段差S1が存在する。集積回路(IC)用途の場合には、Cu層22に、CMPまたは他の何らかの材料除去プロセスを施して、絶縁層12上のCu層22とともにバリア層18を除去することによって、銅層をフィーチャー14および16内にのみ残す必要がある。これらの除去プロセスは、非常にコストがかかることが知られている。

【0013】

図1Eに示したような概ね平坦なCu堆積物を得るための方法および装置は、プロセス効率およびコストの点で非常に有益である。この例における絶縁層12上のCu厚みt5は、図1Dに示したような従来の場合よりも小さく、段差S2の高さも非常に小さい。図1Eのより薄いCu層をCMPまたは他の方法で除去することはより簡単であり、顕著なコスト削減が得られる。

【0014】

同時継続中の米国特許出願第09/201,929号、発明の名称「METHOD AND APPARATUS FOR ELECTROCHEMICAL MECHANICAL DEPOSITION」(1998年12月1日出願)(本発明の譲受人にも共通に所有されている)には、基板表面上のキャビティ内への導電材料の堆積を実現しながら、フィールド領域上への堆積を最小限にする技術が開示されている。これは、導電材料を堆積させるときに、フィールド領域をパッドを用いて研磨することによって行なう。その結果、平坦な銅堆積物がもたらされる。

【0015】

図2Aに、従来技術の電着システム30の概略図を示す。このシステムでは、ウェハー32を、ウェハー32の周縁エッジを覆うリングクランプ36を用いて、ウェハーホルダー34によって保持する。電気コンタクト38もリング状に作られ、陰極メッキ用電源の(−)端子に接続されている。ウェハーホルダー34は、メッキ浴40(メッキ電解液42で満たされている)中に降ろされる。アノード44(電解液42とコンタクトを形成する)が、ウェハー表面の真向かいに配置され、電源の(+)端子と接続されている。アノード44は、堆積すべき材料(すなわち銅)で形成しても良いし、または適切な不活性アノード材料(プラチナ、プラチナコートされたチタンまたはグラファイトなど)で形成しても良い。メッキプロセスは、パワーが印加されるとすぐに開始する。このメッキシステムでは、電気コンタクト38は電解液からシールされて、メッキ電流をウェハー32の周縁を通して流す。しかしウェハー30の周縁にコンタクト38およびクランプ36が存在することが、このシステムの重大な欠点であり、これらの存在によって図2Aの「EE」で示されるエッジ除外が増加する。エッジ除外の結果、ウェハー32の表面上の非常に有益な主要領域32が失われる。

【0016】

図1A〜1Eに、ウェハー表面上のフィーチャーが銅によって充填される模様を示す。この充填プロセスは効果的でウェハーの至る所で均一であるため、均一な厚みの銅がウェハー表面全体に渡って堆積することが重要である。厚み均一性は非常に良好である必要がある。その理由は、不均一な銅厚みでは、CMPプロセスの間に問題を引き起こすからである。図2Bに示したように、堆積層の均一性を改善するために、従来技術の電着システム(図2Aに示したシステムなど)では、シールド46を備える場合がある。このようなシステムでは、ウェハー32またはシールド46の何れかが回転し得る。このようなシールドは、例えば、米国特許第6,027,631号(Broadbent)、米国特許第6,074,544号(Reidら)、および米国特許第6,103,085号(Wooら)に記載されている。

【0017】

【発明が解決しようとする課題】

前述したことを考慮すると、エッジ除外問題を最小限にして均一な導電薄膜を堆積させる代替的な電着プロセスおよびシステムが必要とされる。

【0018】

【課題を解決するための手段】

本発明には、導電材料を半導体ウェハーの全表面へ、電着プロセスによって堆積させることが含まれる。具体的には、本発明によって、実質的に平坦な導電材料層を半導体ウェハーの全表面へ、電気コンタクト用表面上のスペースを何ら失うことなく、すなわちウェハーエッジ除外なしで、形成する方法およびシステムが提供される。

【0019】

本発明の一態様においては、材料を、最大横方向寸法を有するウェハー表面へ、表面上の電気コンタクト用領域を何ら除外することなく堆積させるプロセスが提供される。本プロセスは、アノードを用意する工程と、成形プレートを、アノードとウェハー表面との間で支持する工程と、電解液を、成形プレートを通して、アノードとウェハー表面との間に流す工程と、ウェハー表面のコンタクト領域をコンタクト部材と接触させる工程と、電位差をアノードとコンタクト部材との間に印加する工程とを含む。

【0020】

成形プレートは、アノードと基板表面との間に成形プレート上面がウェハー表面に面するように支持することができる。成形プレートは複数の開口部を備え、各開口部はウェハー表面をアノードと流体連絡させる。成形プレートは、ウェハーの最大横方向寸法よりも大きい横方向寸法を有する。コンタクト部材は、成形プレートの「後退(recessed)」エッジの外側のウェハー表面上のコンタクト領域と接触することによって、ウェハー表面との電気コンタクトを形成する。電位差をアノードとコンタクト部材との間に印加すると、ウェハーが第1位置にあるときに、成形プレートを通したウェハー表面の堆積領域への材料堆積が起こる。コンタクト領域をコンタクト部材と接触させながら、ウェハーを第2位置に移動させることによって、コンタクト領域と堆積領域との両方への材料堆積が起こる。

【0021】

本発明の他の態様によれば、材料を、最大横方向寸法を有するウェハー表面へ堆積させる装置が提供される。本装置は、アノードと、後退エッジを規定する成形プレートと、アノードと基板表面との間に収容される電解液と、成形プレートの後退エッジの外側の基板表面のコンタクト領域と接触する電気コンタクト部材とを備える。

【0022】

成形プレートは、アノードとウェハー表面との間に成形プレート上面がウェハー表面に面するように支持することができる。成形プレートは複数の開口部を備える。成形プレート上面は、ウェハーの最大横方向寸法よりも大きい横方向寸法を有する。電解液は、ウェハー表面の第1領域と常に接触するように、成形プレートの開口部を通ってウェハー表面に接して流れる。電気コンタクト部材は、成形プレートの後退エッジの外側のウェハー表面の第2領域と、電気コンタクトを形成する。第2領域は、ウェハーが成形プレート上方で回転するときに電解液と断続的に接触する。

【0023】

本発明のさらに他の態様によれば、導電材料を電解液から半導体基板の表面上へ堆積させることが可能な装置であって、材料の堆積中に、電解液を基板表面へ供給するアセンブリと、この堆積中に、電解液によって接触されるアノードとを備える装置が提供される。堆積中に、少なくとも1つのコンタクトが、表面と、表面の選択領域で電気的にインターコネクトされる。電位差をアノードとコンタクトとの間へ印加中に、コンタクトおよび表面の少なくとも一方が他方に対して移動するときに、材料の堆積が、選択領域上では断続的に、表面の残り部分上では連続的に進行する。

【0024】

選択領域上への材料の堆積と、表面の残り部分上への材料の堆積との間の不均一性を緩和する装置を設けることができる。装置は、電界分布を変えるために、アノードと表面との間に配置されるシールド(内部に規定される開口部を有する)備えることができる。その代わりに、装置は、開口度(a degree of open area)が異なる複数のアスペリティ領域を有する、アノードと表面との間に設けられた孔の開いたプレートを備えることができる。

【0025】

電解液を供給するアセンブリは、導電材料の堆積中に電解液が流れるキャビティを規定するカップを備えていても良い。アノードはキャビティ内に収容することができ、コンタクトは前記キャビティの外側に配置することができる。アセンブリは、電解液をキャビティへ供給するための入口をさらに備える。

【0026】

導電材料の堆積中に、回転可能で好ましくは移動可能なキャリアによって、基板を保持して、基板表面をコンタクトに対して移動させる。

【0027】

導電材料の堆積中に、成形プレートを、アノードと表面との間に配置することができる。成形プレートは多孔性であり、電解液の貫通流れを可能にする。

【0028】

システムの極性を反対にすると、材料を堆積させる代わりに、材料をウェハーまたは基板表面から、電解エッチング(electroetching)によって、均一に除去するために、システム100を用いることができる。この場合、メッキ電解液の代わりに、一般的に知られる電解エッチングまたは電解研磨溶液を用いても良い。またこの場合、アノードの代わりに、不活性材料から形成される不活性電極を用いても良い。

【0029】

適用の対象に応じて、本発明に基づく装置または方法は、以下に示す特徴の内の一つまたは二つ以上を備える。

【0030】

−本発明の一つの態様によれば、本発明の堆積装置は、

材料を、最大横方向寸法を有するウェハー表面へ堆積させる装置であって、

周囲のエッジで終わる周囲壁によって規定されるキャビティ内に配置されるアノード(ウェハーは周囲エッジ上方に、ウェハー表面がキャビティに面するように支持され、周囲エッジの横方向寸法は、ウェハーの最大横方向寸法よりも大きい)と、

キャビティに周囲エッジまで充填されて、ウェハー表面の第1領域に常に接触する電解液と、

ウェハーが回転するときに電解液に断続的に接触するウェハー表面の第2領域に、キャビティの周囲壁付近の位置で接触する電気コンタクト部材と、

を備えることを特徴とする。

【0031】

−このような堆積装置において、第2領域は、ウェハー周縁に沿って延び、第1領域を囲むコンタクト領域である;

−更に、このようなコンタクト部材は、例えば、コンタクト領域と接触する導電ワイヤである;

−前記堆積装置において、電解液がウェハー表面に接して流れるときに、電解液はウェハーと接触する;

−前記堆積装置において、ウェハーは、ウェハーキャリアによってウェハー背面から支持される;

−更に、このようなウェハーキャリアによって真空吸引がウェハー背面に印加されることで、ウェハーがウェハーキャリア上に保持される;

−更に、このようなウェハーキャリアは、ウェハーをウェハー周縁に沿って支持するための保持リングを備える;

−前記堆積装置において、周囲壁の周囲エッジによって規定される面積は、ウェハーの表面積よりも大きい。

【0032】

−本発明の他の態様によれば、本発明の堆積装置は、

材料を、最大横方向寸法を有するウェハー表面へ堆積させる装置であって、

アノードと、

エッジを規定する成形プレートであって、アノードとウェハー表面との間に成形プレート上面がウェハー表面に面するように支持され、複数の開口部を備え、成形プレート上面はウェハーの最大横方向寸法よりも大きい横方向寸法を有する成形プレートと、

ウェハー表面の第1領域と常に接触するように、成形プレートの開口部を通ってウェハー表面に接して流れる電解液と、

ウェハーが成形プレート上方で回転するときに電解液に断続的に接触するウェハー表面の第2領域に、成形プレートのエッジ付近で電気コンタクトを形成する電気コンタクト部材と、

を備えることを特徴とする。

【0033】

−このような堆積装置において、成形プレートは、第1部分と第2部分とを有する;

−更に、このような第2部分は第1部分よりも、開口部の数が多い;

−前記第2領域は、ウェハー周縁に沿って延び、第1領域を囲むコンタクト領域である;

−前記堆積装置において、コンタクト部材は、第2領域と接触する導電ワイヤである;

−前記堆積装置において、電解液は、ウェハー表面に接して流れるときにウェハーと接触する;

−前記堆積装置において、ウェハーは、ウェハーキャリアアセンブリによってウェハー背面から支持される;

−更に、このようなウェハーキャリアによって真空吸引がウェハー背面に印加されることで、ウェハーがウェハーキャリア上に保持される;

−更に、このようなウェハーキャリアは、ウェハーをウェハー周縁に沿って支持するための保持リングを備える。

【0034】

−本発明の他の態様によれば、本発明の堆積方法は、

材料を、最大横方向寸法を有するウェハー表面へ、表面上の電気コンタクト用 領域を何ら除外することなく堆積させる方法であって、

アノードを用意する工程と、

成形プレートを、アノードとウェハー表面との間に、成形プレート上面がウェハー表面に面するように支持し、成形プレートは複数の開口部を備え、各開口部はウェハー表面をアノードと流体連絡させ、成形プレート上面はウェハーの最大横方向寸法よりも大きい横方向寸法を有する工程と、

電解液を、成形プレートの開口部を通して、アノードとウェハー表面との間に流す工程と、

ウェハー表面のコンタクト領域をコンタクト部材と、成形プレートのエッジ付近の位置で接触させて、表面との電気コンタクトを形成する工程と、

電位差をアノードとコンタクト部材との間に印加して、ウェハーが第1位置にあるときに、材料をウェハー表面の堆積領域に成形プレートを通して堆積させる工程と、

コンタクト領域をコンタクト部材と接触させながら、ウェハーを第2位置に移動させて、材料をコンタクト領域と堆積領域との両方に堆積させる工程と、

を含むことを特徴とする。

【0035】

−このような堆積方法は、ウェハー表面を成形プレートに接触させることを更に含む;

−更に、このような堆積方法は、ウェハー表面を成形プレートに接触させながら、ウェハーを、成形プレートに対して第1の方向に移動させることを含む;

−更に、このような堆積方法において、第1の方向は、成形プレートのエッジに平行である;

−更に、このような堆積方法において、ウェハーを第1の方向に移動させることには、ウェハーを成形プレートの第1部分から成形プレートの第2部分へ移動させることが含まれる;

−更に、このような堆積方法において、第1部分の開口部の数は第2部分の開口部の数よりも少なく、第2部分はより高い堆積速度をもたらす。

【0036】

−本発明の他の態様によれば、本発明の堆積方法は、

導電材料を、最大横方向寸法を有するウェハー表面へ、表面上の電気コンタクト用領域を何ら除外することなく堆積させる方法であって、

アノードを用意し、このアノードを、周囲のエッジで終わる周囲壁によって規定されるキャビティ内に配置し、周囲エッジの横方向寸法はウェハーの最大横方向寸法よりも大きい工程と、

ウェハーを周囲エッジの上方に、ウェハー表面がキャビティと面するように支持する工程と、

キャビティに電解液を、電解液がウェハー表面の第1領域と接触するように充填する工程と、

ウェハー表面のコンタクト領域をコンタクト部材と、キャビティの周囲壁付近の位置で接触させて、ウェハー表面との電気コンタクトを形成する工程と、

電位差をアノードとコンタクト部材との間に印加して、ウェハーが第1位置にあるときに、材料をウェハー表面の第1領域に成形プレートを通して堆積させる工程と、

コンタクト領域をコンタクト部材と接触させながら、ウェハーを第2位置まで回転させて、材料を第1領域とコンタクト領域との両方に堆積させる工程と、

を含むことを特徴とする。

【0037】

−本発明の他の態様によれば、本発明のエッチング装置は、

材料を、最大横方向寸法を有するウェハーの表面からエッチング除去するための装置であって、

周囲のエッジで終わる周囲壁によって規定されるキャビティ内に配置されるカソード(ウェハーは周囲エッジ上方に、ウェハー表面がキャビティに面するように支持され、周囲エッジの横方向寸法は、ウェハーの最大横方向寸法よりも大きい)と、

キャビティに、キャビティの周囲エッジまで充填されて、ウェハー表面の第1領域に常に接触する電解液と、

ウェハーが回転するときに電解液に断続的に接触するウェハー表面の第2領域に、キャビティの周囲壁付近の位置で接触する電気コンタクト部材と、

を備えることを特徴とする。

【0038】

−本発明の他の態様によれば、本発明のエッチング装置は、

材料を、最大横方向寸法を有するウェハーの表面からエッチング除去するための装置であって、

カソードと、

後退エッジを規定する成形プレートであって、アノードとウェハー表面との間に、成形プレート上面がウェハー表面に面するように支持され、複数の開口部を備え、成形プレート上面はウェハーの最大横方向寸法よりも大きい横方向寸法を有する成形プレートと、

ウェハー表面の第1領域と常に接触するように、成形プレートの開口部を通ってウェハー表面に接して流れる電解液と、

ウェハーが成形プレート上方で回転するときに電解液に断続的に接触するウェハー表面の第2領域に、成形プレートの後退エッジ付近で電気コンタクトを形成する電気コンタクト部材と、

を備えることを特徴とする。

【0039】

−本発明の他の態様によれば、本発明のエッチング方法は、

材料を、最大横方向寸法を有するウェハーの表面から、表面上の電気コンタクト用領域を何ら除外することなくエッチング除去するための方法であって、

カソードを用意する工程と、

成形プレートを、アノードとウェハー表面との間に、成形プレート上面がウェハー表面に面するように支持し、成形プレートは複数の開口部を備え、各開口部はウェハー表面をアノードと流体連絡させ、成形プレート上面はウェハーの最大横方向寸法よりも大きい横方向寸法を有する工程と、

電解液を、成形プレートの開口部を通して、アノードとウェハー表面との間に流す工程と、

ウェハー表面のコンタクト領域をコンタクト部材と、成形プレートのエッジ付近の位置で接触させて、表面との電気コンタクトを形成する工程と、

電位差をカソードとコンタクト部材との間に印加して、ウェハーが第1位置にあるときに、材料をウェハー表面のエッチ領域から成形プレートを通してエッチングする工程と、

コンタクト領域をコンタクト部材と接触させながら、ウェハーを第2位置に移動させて、材料をコンタクト領域とエッチ領域との両方から除去する工程と、

を含むことを特徴とする。

【0040】

−本発明の他の態様によれば、本発明の堆積方法は、

導電材料を、最大横方向寸法を有するウェハー表面へ、表面上の電気コンタクト用領域を何ら除外することなく堆積させる方法であって、

アノードを用意し、このアノードを、周囲のエッジで終わる周囲壁によって規定されるキャビティ内に配置し、周囲エッジの横方向寸法はウェハーの最大横方向寸法よりも大きい工程と、

ウェハーを周囲エッジの上方に、ウェハー表面がキャビティと面するように支持する工程と、

キャビティに電解液を、電解液がウェハー表面の第1領域と接触するように充填する工程と、

ウェハー表面のコンタクト領域をコンタクト部材と、キャビティの周囲壁付近の位置で接触させて、ウェハー表面との電気コンタクトを形成する工程と、

電位差をアノードとコンタクト部材との間に印加して、ウェハーが第1位置にあるときに、材料をウェハー表面の第1領域から成形プレートを通して連続的にエッチングする工程と、

コンタクト領域をコンタクト部材と接触させながら、ウェハーを第2位置まで回転させて、材料を第1領域とコンタクト領域との両方からエッチングする工程と、

を含むことを特徴とする。

【0041】

−本発明の他の態様によれば、本発明の堆積装置は、

導電材料を電解液から半導体基板の表面上へ堆積させることが可能な装置であって、

材料の堆積中に、電解液を基板表面へ供給するアセンブリと、

前記堆積中に、電解液によって接触されるアノードと、

前記堆積中に、表面と、表面の選択領域で電気的にインターコネクトされる少なくとも1つのコンタクトと、を備え、

電位差をアノードとコンタクトとの間へ印加中に、コンタクトおよび表面の少なくとも一方が他方に対して 移動するときに、前記堆積が、前記選択領域上では断続的に、表面の残り部分上では連続的に進行すること、

を特徴とする。

【0042】

−このような堆積装置は、前記選択領域上への前記材料の堆積と、表面の残り部分上への前記材料の堆積との間の不均一性を緩和する装置を、更に備える;

−更に、このような堆積装置は、電界分布を変えるために、アノードと表面との間に配置されるシールドを備える;

−更に、このようなシールドは、内部に規定される開口部を備える;

−前記堆積装置は、開口度が異なる複数のアスペリティ領域を有する、アノードと表面との間に設けられた孔の開いた要素を備える;

−この要素はプレートである。

【0043】

−前記堆積装置において、前記アセンブリは、前記堆積中に電解液が流れるキャビティを規定するカップを備える;

−更に、このような堆積装置において、前記アノードは前記キャビティ内に収容される;

−更に、このような堆積装置において、前記コンタクトは前記キャビティの外側に配置される;

−更に、このような堆積装置において、前記アセンブリは、電解液を前記 キャビティへ供給するための入口を更に備える。

【0044】

−前記堆積装置は、前記基板を前記堆積中に保持するキャリアを更に備える;

−更に、このような堆積装置において、前記キャリアは、表面をコンタクトに対して移動させるように回転可能である。

【0045】

−前記堆積装置は、前記アノードと前記表面との間に配置され、前記堆積中に前記表面の近傍に配置される成形要素を更に備える;

−この成形要素は、多孔性であり、前記電解液の貫通流れを可能にする;

−この成形要素は、成形プレートである。

【0046】

−本発明の他の態様によれば、本発明の堆積方法は、

導電材料を電解液から半導体基板の表面上へ堆積させることが可能な方法であって、

電解液を基板表面へ供給して、アノードを電解液と接触させ、

少なくとも1つのコンタクトを、表面と、表面の選択領域で電気的にインターコネクトさせ、

電位差をアノードとコンタクトとの間へ印加しながら、コンタクトおよび表面の少なくとも一方を他方に対して移動させて、前記材料を、前記選択領域上では断続的に、表面の残り部分上では連続的に堆積させること、

を特徴とする。

【0047】

−このような堆積方法は、前記選択領域上への前記材料の堆積と、表面の残り部分上への前記材料の堆積との間の不均一性を緩和することを更に含む。

【0048】

−本発明の他の態様によれば、本発明のエッチング装置は、

導電材料を、半導体基板の表面から除去することが可能な装置であって、

材料の除去中に、電解エッチング溶液を基板表面へ供給するアセンブリと、

前記除去中に、溶液によって接触される電極と、

前記除去中に、表面と、表面の選択領域で電気的にインターコネクトされる少なくとも1つのコンタクトとを備え、

電位差を電極とコンタクトとの間へ印加中に、コンタクトおよび表面の少なくとも一方が他方に対して移動するときに、前記除去が、前記選択領域上では断続的に、表面の残り部分上では連続的に進行すること、

を特徴とする。

【0049】

−本発明の他の態様によれば、本発明のエッチング方法は、

導電材料を、半導体基板の表面から除去することが可能な方法であって、

材料の除去中に、電解エッチングを基板表面へ供給して、電極を溶液と接触させ、

少なくとも1つのコンタクトを、表面と、表面の選択領域で電気的にインターコネクトさせ、

電位差を電極とコンタクトとの間へ印加しながら、コンタクトおよび表面の少なくとも一方を他方に対して移動させて、前記材料を、前記選択領域からは断続的に、表面の残り部分からは連続的に除去すること、

を特徴とする。

【0050】

−本発明の他の態様によれば、本発明のシステムは、

ウェハーに処理を行っている間、ウェハーとの間で電気的コンタクトを取るためのシステムであって、

前記ウェハーは、その前面側の表面に、エッジ部分及び内側部分を備えた導電性レイヤを有しており、

当該システムは、前記ウェハーの前記エッジ部分のみで、前記導電性レイヤとの間で電気的コンタクトを形成する少なくとも一つのコンタクト部材を有し、

ウェハーに処理を行っている間、前記少なくとも一つのコンタクト部材と前記ウェハーの間の相対的な運動によって、前記少なくとも一つのコンタクト部材を前記ウェハーのエッジ部分の異なる部分に電気的にコンタクトさせること、

を特徴とする。

【0051】

−このようなシステムにおいて、前記少なくとも一つのコンタクト部材は、導電性のブラシ、ピンまたはローラの内の一つである;

−前記システムは、二つのコンタクト部材を備え、各コンタクト部材は実質的に反対側のエッジ部分に配置され、各コンタクト部材は前記ウェハーのエッジ部分の異なる部分に電気的にコンタクトする;

−更に、このようなシステムにおいて、前記ウェハーは、その背面側からウェハーキャリアによって支持され、

前記相対的運動は、前記ウェハーと前記少なくとも一つのコンタクト部材との間の相対的な回転運動を含む;

−更に、このようなシステムにおいて、前記二つのコンタクト部材のそれぞれが静止位置に固定され、前記ウェハーキャリアが回転する。

【0052】

−前記システムにおいて、前記ウェハーは、その背面側からウェハーキャリアによって支持され、

前記相対的運動は、前記ウェハーと前記少なくとも一つのコンタクト部材との間の相対的な回転運動を含む;

−更に、このようなシステムにおいて、前記少なくとも一つのコンタクト部材が静止位置に固定され、前記ウェハーキャリアが回転する。

【0054】

−更に、このようなシステムにおいて、前記ウェハーは、その背面側から回転可能なウェハーキャリアによって支持され、このウェハーキャリアはウェハーを回転させて前記相対的な回転運動を発生させ、各列の中の前記複数のコンタクト部材のそれぞれは、静止位置に固定される。

【0055】

−本発明の他の態様によれば、本発明の方法は、

ウェハーに処理を行っている間、ウェハーとの間で電気的コンタクトを取るための方法であって、

前記ウェハーは、その前面側の表面に、エッジ部分及び内側部分を備えた導電性レイヤを有しており、

当該方法は、ウェハーに処理を行っている間、前記ウェハーの前記エッジ部分のみで、少なくとも一つのコンタクト部材と前記ウェハーの前記導電性レイヤとの間で相対的な運動を発生させ、それによって、前記少なくとも一つのコンタクト部材を、前記ウェハーのエッジ部分の異なる部分に電気的にコンタクトさせること、

を特徴とする。

【0056】

−このような方法において、前記相対的な運動は回転運動を含み、前記少なくとも一つのコンタクト部材と前記ウェハーの間のそれぞれの相対的な運動は、前記ウェハーの回転の度に繰り返されるところの、前記ウェハーのエッジ部分の異なる部分との電気的コンタクトを発生させる;

−更に、このような方法において、前記回転運動は、静止状態の少なくとも一つのコンタクト部材と、回転可能なウェハーキャリアによって回転される前記ウェハーとによって生ずる;

−更に、このような方法において、前記少なくとも一つのコンタクト部材は、二つのコンタクト部材を備え、

各コンタクト部材は、実質的に反対側のエッジ部分に配置され、

各コンタクト部材は、前記相対的な運動を発生させるステップの間、前記ウェハーのエッジ部分の異なる部分に電気的にコンタクトする。

【0057】

−あるいは、前記相対的な運動を発生させるステップは、前記少なくとも一つの電気的コンタクト部材と前記ウェハーのエッジ部分との間の相対的な直線運動を、更に含む。

【0058】

−本発明の他の態様によれば、本発明のシステムは、

溶液を用いてウェハーの処理をするための電気化学的処理システム( electrochemical processing system )であって、

前記ウェハーは、その前面側の表面に、エッジ部分及び内側部分を備えた導電性レイヤを有しており、

当該システムは、

前記ウェハーを保持するためのウェハーキャリアと、

電極と、

前記溶液が前記ウェハーの少なくとも前記内側部分に供給されている間、前記ウェハーの前記エッジ部分のみで、前記導電性レイヤとの間で電気的コンタクト を取る少なくとも一つのコンタクト部材を有し、

前記電極と前記ウェハーの間で電位差を維持することによって、前記ウェハーを電気化学的に処理し、

前記電気化学的な処理の間の、前記少なくとも一つのコンタクト部材とウェハーの間の相対的な運動は、前記少なくとも一つのコンタクト部材を、前記ウェハーのエッジ部分の異なる部分に電気的にコンタクトさせること、

を特徴とする。

【0059】

−このような電気化学的処理システムにおいて、前記電極と前記ウェハーの間で維持される前記電位差によって、前記溶液から、少なくとも前記導電性レイヤの前記内側部分の上に、導電材( conductor )の堆積が行われる;

−あるいは、このような電気化学的処理システムにおいて、前記電極と前記ウェハーの間で維持される電位差によって、前記導電性レイヤの少なくとも前記内側部分で導電材のエッチングが行われる。

【0060】

−前記電気化学的処理システムにおいて、前記少なくとも一つのコンタクト部材は、導電性のブラシ、ピンまたはローラの内の一つである;

−前記電気化学的処理システムは、二つのコンタクト部材を備え、各コンタクト部材は実質的に反対側のエッジ部分に配置されている;

−更に、このような電気化学的処理システムにおいて、前記ウェハーは、ウェハーの背面側からウェハーキャリアによって支持され、

前記相対的運動は、前記ウェハーと前記少なくとも一つのコンタクト部材との間の相対的な回転運動を含む;

−更に、このような電気化学的処理システムにおいて、前記二つのコンタクト部材のそれぞれが静止位置に固定され、前記ウェハーキャリアが回転する。

【0061】

−前記電気化学的処理システムにおいて、前記ウェハーは、ウェハーの背面側からウェハーキャリアによって支持され、

前記相対的運動は、前記ウェハーと前記少なくとも一つのコンタクト部材との 間の相対的な回転運動を含む;

−更に、このような電気化学的処理システムにおいて、前記少なくとも一つのコンタクト部材のそれぞれが静止位置に固定され、前記ウェハーキャリアが回転する。

【0063】

−更に、このような電気化学的処理システムにおいて、前記ウェハーは、ウェハーの背面側から回転可能なウェハーキャリアによって支持され、このウェハーキャリアはウェハーを回転させて、前記相対的な回転運動を発生させ、各列の中の前記複数のコンタクト部材のそれぞれは、静止位置に固定される。

【0064】

−前記電気化学的処理システムは、更に、シールドを備える;

−更に、このような電気化学的処理システムにおいて、前記シールドは、前記ウェハーを電気化学的に処理して、導電材が前記導電性レイヤの上に実質的に一様な状態で堆積されるように構成される;

−あるいは、このような電気化学的処理システムにおいて、前記シールドは、前記ウェハーを電気化学的に処理して、前記導電性レイヤから一様な量の導電材がエッチングされるように構成される。

【0065】

−本発明の他の態様によれば、本発明の方法は、溶液を用いてウェハーを処理するための電気化学的処理方法( electrochemical processing method )であって、

前記ウェハーは、その前面側の表面に、エッジ部分及び内側部分を備えた導電性レイヤを有しており、

当該方法は、

前記ウェハーの前記導電性レイヤと電極の間の電位差を維持すること、

前記ウェハーの前記エッジ部分のみで、少なくとも一つのコンタクト部材と前記ウェハーの前記導電性レイヤとの間で相対的な運動を発生させ、それによって、前記少なくとも一つのコンタクト部材を、前記ウェハーのエッジ部分の異なる部分に電気的にコンタクトさせること、及び、

前記電位差及び前記相対的運動が維持されている間に、前記溶液を用いて、少なくとも前記ウェハーの内側部分に対して、電気化学的処理を行うこと、

を特徴とする。

【0066】

−このような電気化学的処理方法において、前記電極と前記ウェハーの間で維持される前記電位差によって、前記溶液から、少なくとも前記導電性レイヤの前記内側部分の上に、導電材の堆積が行われる;

−更に、このような電気化学的処理方法において、銅堆積用溶液が使用され、前記導電材は銅である;

−あるいは、このような電気化学的処理方法において、前記電極と前記ウェハーの間で維持される前記電位差によって、少なくとも前記導電性レイヤの前記内側部分で、導電材のエッチングが行われる;

−更に、このような電気化学的処理方法において、銅エッチング用溶液が使用され、前記導電材は銅である。

【0067】

−このような電気化学的処理方法において、前記相対的な運動は回転運動を含み、前記少なくとも一つのコンタクト部材と前記ウェハーの間のそれぞれの相対的な運動は、前記ウェハーの回転の度に繰り返されるところの、前記ウェハーのエッジ部分の異なる部分との電気的コンタクトを発生させる;

−更に、このような電気化学的処理方法において、前記回転運動は、静止状態の少なくとも一つのコンタクト部材と、回転可能なウェハーキャリアによって回転される前記ウェハーとによって生ずる。

【0068】

−あるいは、このような電気化学的処理方法において、前記少なくとも一つのコンタクト部材は、二つのコンタクト部材を備え、

各コンタクト部材は、実質的に反対側のエッジ部分に配置され、

各コンタクト部材は、前記相対的な運動を発生させるステップの間、前記ウェハーのエッジ部分の異なる部分に電気的にコンタクトする。

【0069】

−あるいは、このような電気化学的処理方法において、前記相対的な運動を発生させるステップは、前記少なくとも一つのコンタクト部材と前記ウェハーのエッジ部分との間の相対的な直線運動を更に含む。

【0070】

−本発明の他の態様によれば、本発明のシステムは、溶液を用いてウェハーを処理するための電気化学的加工システム( electrochemical mechanical process system )であって、

前記ウェハーは、その前面側の表面に、エッジ部分及び内側部分を備えた導電 性レイヤを有しており、

当該システムは、

前記ウェハーを保持するためのウェハーキャリアと、

電極と、

前記ウェハーの近傍に配置され、前記電極とウェハーの間に位置し、前記溶液の存在下で前記ウェハーの前面側の表面に物理的に接触することによって、前記ウェハーの前面側の表面の処理をするためのパッドと、

前記ウェハーの前記エッジ部分のみで、前記導電性レイヤとの間で電気的コンタクトを形成する少なくとも一つのコンタクト部材と、

を備え、

前記少なくとも一つのコンタクト部材とウェハーの間の相対的な運動は、前記少なくとも一つのコンタクト部材を、前記ウェハーのエッジ部分の異なる部分に電気的にコンタクトさせること、及び、

前記相対的運動が維持されている間、前記ウェハーの前面側の表面に物理的に接触することによって、前記パッドで前記ウェハーの前面側の表面の処理をすること、

を特徴とする。

【0071】

−このような電気化学的処理システムにおいて、前記ウェハーの近傍に配置された前記パッドは、前記ウェハーの一部をカバーせず、且つ、前記パッドは、電流密度が高い領域と電流密度が低い他の領域を有するように構成される;

−更に、このような電気化学的処理システムは、前記パッドに対して前記ウェハーを横方向に移動させるための手段を、更に備える;

−更に、このような電気化学的処理システムにおいて、前記ウェハーは、その背面側からウェハーキャリアによって支持され、

前記相対的運動は、前記ウェハーと前記少なくとも一つのコンタクト部材との間の相対的な回転運動を含む。

【0072】

−更に、このような電気化学的処理システムにおいて、前記ウェハーは、その背面側からウェハーキャリアによって支持され、このウェハーキャリアはウェハーを回転させて前記相対的な回転運動を発生させ、前記少なくとも一つのコンタクト部材は、静止位置に固定される。

【0073】

−前記電気化学的処理システムにおいて、前記電極と前記ウェハーの間で維持される前記電位差によって、前記溶液から、少なくとも前記導電性レイヤの前記内側部分の上に、導電材の堆積が行われる;

−あるいは、前記電気化学的処理システムにおいて、前記電極と前記ウェハーの間で維持される電位差によって、少なくとも前記導電性レイヤの前記内側部分で導電材のエッチングが行われる。

【0074】

−前記電気化学的処理システムは、二つのコンタクト部材を備え、各コンタクト部材は実質的に反対側のエッジ部分に配置される;

−更に、このような電気化学的処理システムにおいて、前記ウェハーは、その背面側からウェハーキャリアによって支持され、

前記相対的運動は、前記ウェハーと前記二つのコンタクト部材との間の回転運動を含む;

−更に、このような電気化学的処理システムにおいて、前記二つのコンタクト部材のそれぞれが静止位置に固定され、前記ウェハーキャリアが回転する。

【0075】

−前記電気化学的処理システムにおいて、前記ウェハーは、その背面側からウェハーキャリアによって支持され、

前記相対的運動は、前記ウェハーと前記少なくとも一つのコンタクト部材との間の相対的な回転運動を含む;

−更に、このような電気化学的処理システムにおいて、前記ウェハーは、その背面側からウェハーキャリアによって支持され、このウェハーキャリアはウェハーを回転させて前記相対的な回転運動を発生させ、前記少なくとも一つのコンタクト部材は、静止位置に固定される。

【0077】

−更に、このような電気化学的処理システムにおいて、前記ウェハーは、その背面側から回転可能なウェハーキャリアによって支持され、このウェハーキャリアはウェハーを回転させ、前記各列の中の前記複数のコンタクト部材のそれぞれは、静止位置に固定される。

【0078】

−本発明の他の態様によれば、本発明の方法は、溶液を用いてウェハーを処理するための電気化学的加工方法( electrochemical mechanical processing method )であって、

前記ウェハーは、その前面側の表面に、エッジ部分及び内側部分を備えた導電 性レイヤを有しており、

当該方法は、

前記ウェハーの前記導電性レイヤと電極の間の電位差を維持すること、

前記ウェハーの前記エッジ部分のみで、少なくとも一つのコンタクト部材と前記導電性レイヤとの間で相対的な運動を発生させ、それによって、前記少なくとも一つのコンタクト部材を、前記ウェハーのエッジ部分の異なる部分に電気的にコンタクトさせること、

前記電位差及び前記相対的運動が維持されている間に、前記溶液を用いて、少なくとも前記ウェハーの内側部分に対して、電気化学的加工( electrochemical mechanical processing )を行うこと、及び、

前記電気化学的加工は、前記ウェハーに対して摺動可能な状態で接触し、前記電極と前記ウェハーの間に配置されたパッドを、前記溶液の存在下で動かすことを含むこと、

を特徴とする。

【0079】

−このような電気化学的加工方法において、前記電気化学的加工を行うステップの間、前記パッドは、前記ウェハーの一部をカバーせず、且つ、前記パッドは、電流密度が高い領域と電流密度が低い他の領域を有するように構成される;

−更に、このような電気化学的加工方法において、前記電気化学的加工を行うステップの間、前記領域は、前記パッドをカバーしていない前記ウェハーの部分と同調し、それによって、加工の間、ウェハー上で平坦な導電材表面が得られる。

【0080】

−あるいは、このような電気化学的加工方法において、前記電気化学的加工を行うステップは、前記パッドに対して前記ウェハーを横方向に移動させることを、更に含む;

−更に、このような電気化学的加工方法において、前記相対的な運動は回転運動を含み、前記少なくとも一つのコンタクト部材と前記ウェハーの間のそれ ぞれの相対的な運動は、前記ウェハーの回転の度に繰り返されるところの、前記ウェハーのエッジ部分の異なる部分との電気的コンタクトを発生させる;

−更に、このような電気化学的加工方法において、前記回転運動は、静止状態の少なくとも一つのコンタクト部材と、回転可能なウェハーキャリアによって回転される前記ウェハーとによって生ずる;

−更に、このような電気化学的加工方法において、前記少なくとも一つのコンタクト部材は、二つのコンタクト部材を備え、

各コンタクト部材は、実質的に反対側のエッジ部分に配置され、

各コンタクト部材は、前記相対的な運動を発生させるステップの間、前記ウェハーのエッジ部分の異なる部分に電気的にコンタクトする;

−あるいは、このような電気化学的加工方法において、前記相対的な運動を発生させるステップは、前記少なくとも一つの電気的コンタクト部材と前記ウェハーのエッジ部分との間の相対的な直線運動を、更に含む。

【0081】

−前記電気化学的加工方法において、前記電極と前記ウェハーの間で維持される前記電位差によって、前記溶液から、少なくとも前記導電性レイヤの前記内側部分の上に、導電材の堆積が行われる;

−更に、このような電気化学的加工方法において、銅堆積用溶液が使用され、前記導電材は銅である;

−あるいは、前記電気化学的加工方法において、前記電極と前記ウェハーの間で維持される前記電位差によって、少なくとも前記導電性レイヤの前記内側部分で、導電材のエッチングが行われる;

−更に、このような電気化学的加工方法において、銅エッチング用溶液が使用され、前記導電材は銅である。

【0082】

−前記電気化学的加工方法において、前記相対的な運動は回転運動を含み、前記少なくとも一つのコンタクト部材と前記ウェハーの間のそれぞれの相対的な運動は、前記ウェハーの回転の度に繰り返されるところの、前記ウェハーのエッジ部分の異なる部分との電気的コンタクトを発生させる;

−更に、このような電気化学的加工方法において、前記回転運動は、静止状態の少なくとも一つのコンタクト部材と、回転可能なウェハーキャリアにより回転される前記ウェハーとによって生ずる;

−更に、このような電気化学的加工方法において、前記少なくとも一つのコンタクト部材は二つのコンタクト部材を備え、

各コンタクト部材は、実質的に反対側のエッジ部分に配置され、

各コンタクト部材は、前記相対的な運動を発生させるステップの間、前記ウェハーのエッジ部分の異なる部分に電気的にコンタクトする。

【0083】

−あるいは、このような電気化学的加工方法において、前記相対的な運動を発生させるステップは、前記少なくとも一つの電気的コンタクト部材と前記ウェハーのエッジ部分との間の相対的な直線運動を、更に含む。

【0084】

−本発明の他の態様によれば、本発明のシステムは、溶液を用いてウェハーの導電性の前面側表面に対して処理を行う電気化学的加工システム( electrochemical mechanical processing system )において使用するためのパッドであって、

前面側表面と複数の開口部を備え、

前記パッドの前面側表面は、前記ウェハーの導電性の前面側表面の少なくとも内部領域に物理的に接触するように形成され、それによって、前記ウェハーと当該パッドの前面側表面の間で相対的な回転運動が発生したとき、前記ウェハーと連続的には物理的に接触しないエッジエリアの部分を残すこと、

前記複数の開口部は、前記溶液が前記パッドの背面側から前記パッドの前面側 に流れるように形成されていること、及び、

前記複数の開口部は、少なくとも前記エッジ領域と同様に広い面積に対して電流密度が高い領域を作るとともに、電流密度が低い他の領域を作るように形成されていること、

を特徴とする。

【0085】

−このようなパッドにおいて、前記領域内では、前記他の領域に比べて、前記溶液を前記パッドの背面側から前記パッドの前面側に流す開口面積の割合が大きい;

−更に、このようなパッドにおいて、前記領域内での開口部の平均サイズは、前記他の領域の中の他の開口部の平均サイズと比べて、大きい;

−更に、このようなパッドにおいて、前記パッドの形状は矩形であって、前記開口部はこの矩形の一方の側にあり、前記他の開口部はこの矩形のもう一方の側にある;

−あるいは、前記パッドにおいて、前記パッドの形状は矩形であって、前記開口部はこの矩形の一方の側にあり、前記他の開口部はこの矩形のもう一方の側にある;

−あるいは、前記パッドにおいて、前記パッドの形状は矩形であって、電流密度が高い前記領域はこの矩形の一方の側にあり、電流密度が低い前記他の領域はこの矩形のもう一方の側にある。

【0086】

【発明の実施の形態】

本発明のこれらおよび他の特徴、態様、および利点は、以下の図面、説明、および特許請求の範囲を参照して、より良く理解される。

【0087】

本発明には、導電材料を、半導体基板またはウェハーの全表面または全面に、電着プロセスによって堆積させることが含まれる。後述するように、本発明によって、実質的に平坦な導電材料層を半導体基板の全表面に、電気コンタクト用表面上のスペースを何ら失うことなく、すなわちウェハーエッジ除外なしで、形成する方法およびシステムが提供される。本発明の全面堆積プロセスは、有利なことに、半導体ウェハーの全表面上の複数のキャビティ(トレンチ、ビア、コンタクトホールなど)への導電材料の堆積を実現する。一実施形態においては、本発明は、成形カップ(shaping cup)またはアノードカップを用いて、電解液をウェハー表面上へ直接送ることで、導電材料をウェハー表面上へ堆積させる。他の実施形態においては、孔の開いたプレートを通して、導電材料を堆積させる。この実施形態では、孔の開いたプレートによって、導電材料の均一な堆積が促進される。さらに他の実施形態では、本発明は、孔の開いたプレートを通して、ウェハー表面のフィーチャー内への導電材料の堆積を実現する一方で、本発明の孔の開いたプレートに対して、ウェハー表面を接触させ、掃引し、研磨することによって、フィーチャー間の最上表面領域への堆積を最小限にする。

【0088】

本発明のプロセスによって向上された堆積特性が示され、以前は達成不可能な平坦さを有する層、従来技術のプロセスおよび装置を用いて作製された従来技術の層よりも材料特性が勝る導電層が得られる。

【0089】

図面を参照するが、全体を通して、同様の部材は同様の数字によって参照する。図3に示すように、一実施形態においては、本発明の電着システム50は好ましくは、上部51と下部52とを備えていても良い。好ましい実施形態においては、システム50を、導電材料(銅など)を半導体ウェハー(シリコンウェハーなど)上に堆積させるために用いても良い。しかし例として銅を用いるが、本発明は、他の一般的な導電体(Ni、Pd、Pt、Auおよびそれらの合金など)を堆積させるために用いても良いことに注意されたい。電着システム50の上部51を、ウェハーキャリア53を有するキャリアアセンブリから構成しても良い(図3に示す)。ウェハーキャリア53は、典型的なウェハー54を保持し、キャリアアーム55に取り付けられる。

【0090】

システム50の下部52は、アノード56を備えるアノードアセンブリから構成しても良い。アノード56は好ましくは、エンクロージャー(アノードカップ57または成形カップなど)の中に配置される。アノードカップ57は、内部キャビティ58またはハウジング(底部壁60上に立つ周囲の側壁59によって規定される)を備えていても良い。周囲側壁59の上部リムフレーム(rim frame)61によって、アノードカップ57の上端が形成される。この実施形態においては、上部リムフレーム61は好ましくは矩形状であり、リムフレームの面は、ウェハーキャリア53をリムフレーム61に向かって下げたときに、ウェハー54と実質的に平行になるように適合されている。図5に示すように、リムフレームは最大横方向寸法Dを有する。銅メッキ電解液62を、ポンプによって、アノードカップ57内へ底部壁60に形成された液体入口63を通して、矢印264の方向に入れても良い。こうしてアノードカップおよび入口によって、電解液62を半導体ウェハーまたは基板の前面へ供給することができるアセンブリの少なくとも一部が構成される。電着プロセスの間、アノードカップ57は、電解液62によってリムフレーム61まで完全に充填されている。アノード56は、電圧源(図示せず)の正端子に、アノードコネクター64を通して電気的に接続されている。電着プロセスの間、ウェハー54は、リムフレーム61と実質的に平行であるとともにこれに近接するように保たれ、そして回転する。電解液62の流量を制御することによって、電解液は、近接するウェハーの前面65とコンタクトを形成する。過剰な電解液は、周囲側壁59を越えて流れ落ちた後、回収されて再循環される。

【0091】

この実施形態においては、電気コンタクト部材66がウェハー54と、前面65のコンタクト領域67上で接触するか、そうでなければ電気的にインターコネクトすることが理解される。コンタクト領域67の位置は、ウェハー54がアノードカップ57の上方で回転するときに、リムフレーム61に対して環状に変化する。コンタクト部材66は、負電圧源(図示せず)に、コネクター68を用いて接続される。

【0092】

図4に示すように、ウェハーキャリア53はウェハー54を、ウェハー54の背面69から、ウェハーキャリア53のチャック面に接触させて保持する。ウェハー54を、真空吸引もしくは保持リング70(図4に示す)または両方を用いて保持することで、ウェハー54の前面65およびコンタクト領域67を完全にさらす。本発明の原理によれば、ウェハー54によって最大横方向寸法dが規定される。この寸法は、この場合、ウェハーの直径である。代替的に、保持リング70は、ウェハーキャリア53の一体部分であっても良い。プロセスの間、ウェハーキャリア53、したがってウェハー54を、キャリアアーム55を回転軸71またはウェハーキャリア53の垂直軸の周りに回転方向72に回転させることによって、回転させても良い。後でより十分に説明するように、回転運動によって、コンタクト領域67が電解液62上で移動することで、コンタクト領域67が電解液にさらされる。ウェハー54の前面65が完全にさらされていること、およびコンタクト領域67をアノードカップ57上で移動させることによって、コンタクト領域67を電解液62へさらすことができることの両方の効果が組み合わさる結果、ウェハー54上のエッジ除外がゼロになる。

【0093】

図4および5に示すように、この実施形態においては、成形カップまたはアノードカップ57の周囲側壁59は通常、矩形の側壁(第1の側壁73、第2の側壁74、第3の側壁75、および第4の側壁76を備えていても良い)として形作っても良い。この実施形態では、第1および第2の側壁73、74は、その長さが第3および第4の側壁75、76の長さより長くても良く、周囲側壁59の「後退」エッジ77(すなわちウェハー54の周縁の外部エッジと比べて後退しているエッジ)を形成していても良い。第3および第4の側壁75、76は、アノードカップ57の周囲側壁の側面エッジ78を形成する。この実施形態においては、アノードカップ57の幅、または後退エッジ77間の距離は、ウェハー54の直径(ウェハーの最大横方向距離d)よりも小さくなるように適合されている。一方で、アノードカップの長さ、または側面エッジ間の距離(リムフレーム61の最大横方向距離D)は、ウェハー直径よりも長くなるように適合されている。

【0094】

最大横方向距離dと上部リムフレームの幅とが違うために、この構成によって、ウェハー54上のコンタクト領域67が露出し、電気コンタクト部材66をコンタクト領域67上へ配置することができる。この実施形態では後退エッジ77は直線であるが、本発明の範囲としては、電気コンタクトをウェハーの前面65上へ配置できるならば、後退エッジ77は、窪んでいても、V形状であっても、または他の可能などんな構成で形成されていても良いことが含まれる。いつであっても、ウェハー54上のコンタクト領域67が銅メッキされ得るのは、コンタクト領域67が電解液62上方で回転しているときのみであることに注意されたい。この点について言えば、ウェハー54が回転するときに、第1の領域79(図5において点線の円で示される)は、常にアノードカップ上に留まるため、連続してメッキされる。しかし選択された第2の表面領域80(第1の領域79の外側にあり、コンタクト領域によって範囲が規定される)においては、堆積プロセスが不連続に進行する。したがって第1の領域79での堆積速度と、第2の領域80での堆積速度とは異なっており、その結果、第2の領域80はより薄い堆積層を有する可能性がある。

【0095】

図6に、堆積層のこの不均一性が、シールド82を用いることによって緩和される様子を示す。シールド82を、図6に示したように、電解液中に浸漬させて、第1の領域79の付近に配置する。しかしアノードからカソード(ウェハー)までの距離が短いならば、その代わりに、シールド82をアノード56上に配置しても良い。シールド82は、孔99または開口部を有していても良い。シールドによって、アノードとウェハー54上の第1の領域79(図5を参照)またはコンタクト領域67との間の電解分布が変化して、第1の領域79での堆積速度が変化する。そのため、電着された銅のウェハー前面65上での厚みプロファイルが修正される。この実施形態では、シールド82は、非導電材料(ポリマー材料など)で形成されていても良い。

【0096】

図4および6に戻って、使用中は、電解液をポンプによって、アノードカップ57内に矢印264の方向に入れる。いったん電解液によってアノードカップ57が満たされれば、印加される圧力によって、電解液はウェハー54の前面65に、矢印81の方向に到達する。前述したように、ウェハー54の前面65は、電解液に近接して保持されている。ウェハー54の前面65と電解液表面との間のギャップは、キャリアアセンブリ53を軸71に沿って垂直に動かすことによって調整できる。前面65と電解液との間の距離を調整した後に、アノード56とコンタクト部材66との間に電位差を印加することによって、電着プロセスを開始する。その結果、この段階では、電位差は、コンタクト部材がアノードよりも陰極性(−)になるように選択されている。またコンタクト部材はウェハー54の前面65に接触しているため、前面65も陰極性となる。堆積プロセスが進行するにつれて、銅が均一に前面65上に堆積する。前述したように、ウェハー54上のコンタクト領域が銅メッキされ得るのは、コンタクト領域67が電解液62上を回転しているときのみ、したがって電解液にさらされているときのみである。あふれ出る電解液(矢印82で示す)は、回収して再循環しても良い。

【0097】

図7に示すように、他の実施形態においては、本発明の電着システム100は好ましくは、上部102と下部104とを備えていても良い。好ましい実施形態においては、システム100を、導電材料(銅など)を半導体ウェハー(シリコンウェハーなど)上に堆積させるために用いても良い。前述した実施形態と同様に、例として銅を用いるが、本発明は、他の一般的な導電体(Ni、Pd、Pt、Auおよびそれらの合金など)を堆積させるために用いても良い。電着システム100の上部102を、ウェハーキャリア106を有するキャリアアセンブリから構成しても良い(図7に示す)。ウェハーキャリア106は、典型的なウェハー108を保持し、キャリアアーム110に取り付けられる。キャリアアームは、回転するか、またはウェハー108を横方向もしくは縦方向に動かしても良い。

【0098】

システム100の下部104は、アノードアセンブリ(アノード112、好ましくは消耗品である銅アノード、および成形プレート114を備える)から構成しても良い。アノードを好ましくは、エンクロージャー(アノードカップ116など)内に配置して、アノードプレート118で囲んでも良い。アノードプレート118上には、成形プレート114を配置しても良い。成形プレート114とアノードプレート118とは両方とも、好ましくは孔の開いたプレートである。成形プレート114は、複数の開口部120またはアスペリティ(asperities)を備えていても良い。開口部120は、アノードプレート118の開口部(図10Aおよび10Bを参照)と概ね一致するように適合されている。そのため両者を一緒に取り付けたときに、対応する開口部は、電着プロセスの間に電解液をプレート114および118を通して流して、ウェハー108の前面を濡らすことができる経路を形成する。電着プロセスの間、ウェハー108を成形プレート114の上面119と実質的に平行に保持して、回転させても良い。またウェハーは、横方向に移動しても良い。銅メッキ電解液を、ポンプによって、アノードカップ116内へ液体入口121を通して、矢印122の方向に入れても良い。この場合もやはり、したがってアノードカップと入口とによって、電解液を半導体ウェハーまたは基板の前面へ供給することができるアセンブリの少なくとも一部が構成される。アノード112は、電圧源(図示せず)の正端子に、アノードコネクター124を通して電気的に接続されている。成形プレート114が堅い材料からなるときには、アノードプレート118は必要でない場合がある。

【0099】

後でより十分に説明するように、この実施形態においては、電気コンタクト部材126をウェハー108と、コンタクト領域128上で接触させるか、そうでなければ電気的にインターコネクトさせる。コンタクト領域128の位置は、ウェハー108が成形プレート114の上方で回転または移動するときに、成形プレート114に対して環状に変化する。コンタクト部材は、電圧源(図示せず)の負端子に、コネクター129を用いて接続される。

【0100】

図8に示すように、ウェハーキャリア106はウェハー108を、ウェハー108の背面130から保持する。ウェハー108は、図8で示すように、ウェハーキャリア106の下面131またはチャック面上に保持しても良い。この実施形態においては、ウェハーを、真空吸引もしくは保持リング133(図8に示す)または両方を用いて保持することで、ウェハー108の前面132を電解液に完全にさらす。その代わりに、保持リング133はウェハーキャリア106の一体部品であっても良い。プロセスの間、ウェハーキャリア106、したがってウェハー108を、キャリアアーム110を回転軸134またはウェハーキャリア106の垂直軸の周りに回転方向135に回転させることによって、回転させても良い。後でより十分に説明するように、回転運動によって、有利なことに、コンタクト領域128が成形プレート114上で移動することで、コンタクト領域128が、成形プレートを通って流れる電解液にさらされる(図7を参照)。ウェハー108の前面132が完全にさらされていること、およびコンタクト領域128を成形プレート114上で移動させることによって、コンタクト領域128を電解液へ連続してさらすことができることの両方の効果が組み合わさる結果、ウェハー108上のエッジ除外がゼロになる。

【0101】

図9Aおよび9Aに示すように、この実施形態においては、本発明の成形プレート114は通常、矩形状(第1の側壁136、第2の側壁138、第3の側壁140、および第4の側壁142によって規定される)に形作っても良い。この実施形態では、第1および第2の側壁136、138は、その長さが第3および第4の側壁140、142の長さより長くても良く、成形プレート114の「後退」エッジ144(すなわちウェハー108の周縁の外部エッジと比べて後退しているエッジ)を形成していても良い。第3および第4の側壁140および142は、成形プレート114の側面エッジ146を形成する。成形プレート114の幅、または後退エッジ間の距離は、ウェハー108の直径よりも小さくなるように構成されている。前述した実施形態と同様に、側面エッジ146間の距離は、成形プレート114の最大横方向寸法Dである。またウェハーの直径は、ウェハー108の最大横方向寸法dである。好ましい実施形態においては成形プレート114を矩形状に形作っているが、成形プレートにはどんな幾何学的形状を与えても良い。

【0102】

図9Aに示すように、横方向距離dと成形プレートの幅とが違うために、ウェハー108上のコンタクト領域128が露出し、また電気コンタクト部材126をコンタクト領域128上へ配置することができる(図7を参照)。この実施形態では後退エッジは直線状であるが、本発明の範囲としては、電気コンタクトをウェハーの前面上へ配置できるならば、後退エッジは、窪んでいても、V形状であっても、または他の可能などんな構成で形成されていても良いことが含まれる。前述したように、成形プレート114の幅および長さを選択することによって、ウェハー108を成形プレート114上方で第1の方向147へ移動させるときに、コンタクト領域128を電気コンタクト部材126と接触させるか、そうでなければ電気的にインターコネクトさせることができる。図9Aにおいて、コンタクト部材を、コンタクト領域128と接触する直線状のストリップとして示す。しかし、いつであっても、ウェハー上のコンタクト領域128が銅メッキされ得るのは、コンタクト領域が成形プレート114のアスペリティの上方で回転しているときのみであることに注意されたい。この点について言えば、ウェハーが回転するときに、第1の領域148(図9Aにおいて点線の円で示される)は、常に成形プレート114上方に留まるため、連続してメッキされる。しかし第2の選択された領域149(第1の領域148の外側にあり、コンタクト領域によって範囲が規定される)においては、堆積プロセスが不連続に進行する。したがって第1の領域148での堆積速度と、第2の領域149での堆積速度とは異なっており、その結果、第2の領域149はわずかに薄い堆積層を有することが予想される。後述するように、この厚みの差は、代替的なアスペリティデザインを用いることによって無くすことができる。さらに、前述したシールド82(図6に示す)を、この実施形態とともに用いることで、ウェハー108の前面132上に均一な堆積層を得ることができる。

【0103】

図9Bを参照して、アスペリティ120は内部側壁150によって規定される。内部側壁150は、上部開口部152(成形プレート114の上面119内)と下部開口部154(成形プレート114の底面156内)との間を延びる。前述したように、電着プロセスの間、電解溶液はウェハー前面にアスペリティ120を通して到達する。成形プレート114の機能性(functionality)に依存して、成形プレート114は絶縁材料または導電材料から形成されていても良い。電着のみを行なうのであれば、成形プレートは導電材料から形成されていても良い。しかし電着および研磨を共に行なうのであれば、絶縁材料(ポリマーまたはセラミック材料など)が好ましい。この実施形態ではアスペリティ120は長方形状であるが、種々の幾何学形状(楕円、四角形、円、またはその他など)で形成しても良い。アスペリティ120の形状、容積スペース、密度によって、堆積薄膜の均一性が規定される。アスペリティ120の内部側壁150は、上部および底部表面119および156に対して垂直である必要はない。すなわち内部側壁150は、傾斜しているか、湾曲しているか、またはその他の形態もしくは形状であり得る。

【0104】

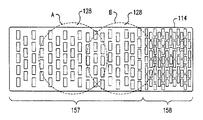

図9Cに、成形プレート114の代替的な実施形態を示す。この実施形態では、成形プレート114は、第1および第2のアスペリティ領域(157および158)をそれぞれ備える。このデザインの結果、第2のアスペリティ領域158は、開口度が第1のアスペリティ領域157よりも高く、ウェハー上の銅堆積が多い。ウェハーを、第1の領域157内の位置Aの周りで振動させることによってメッキすると、ある程度の堆積層厚みプロファイルが得られ、堆積層の厚みがコンタクト領域128に沿ってわずかに薄い場合がある。コンタクト領域128に沿った厚みを増加させるために、ウェハーを位置Bに移動させて一部を第2の領域158上に動かし、コンタクト領域128をより高い銅堆積速度にさらす。この工程を電着プロセスの一部の間に行なって、均一な堆積プロファイルの銅層堆積を実現しても良い。またこのような高密度領域を成形プレート114上の1または複数の場所に形成して、層堆積の厚みプロファイルを任意に変更または制御できることも本発明の範囲内である。すなわち、ウェハー前面での厚みプロファイルを、凹形、凸形、または完全に平坦にすることができる。この実施形態では、エッジ除外をゼロにすることができる。すなわちウェハー前面の全体を、そのエッジまでずっと均一にメッキすることができる。

【0105】

図10Aおよび10Bに示すように、成形プレート114を、複数の孔159を有するアノードプレート118上に配置する。アノードプレート118の孔159と成形プレート114のアスペリティ120とは、連続的した電解液経路160を形成する。電解液経路160は、アノードカップ116の内部キャビティ162(プロセスの間、電解液によって満たされる)を、成形プレート114の上面119と接続する。電解液は、アノードカップに矢印122の方向に入り、経路160を矢印164の方向に通過して流れる。フィルター(図示せず)を内部キャビティ162内に配置して、電着の間にアノード112の溶解によって発生したパーティクルを捕えても良い。アノードプレート118は、絶縁材料または導電材料から形成されていても良い。消耗アノードを用いないシステムの場合、アノードプレート118をアノードとして用いても良いし、または別の不活性カソードをアノード112の代わりに用いることができる。このようなシステムでは、アノードプレートを金属(チタンなど)で形成することができ、好ましくは不活性金属(プラチナなど)でコートすることができる。その結果、正電圧は、消耗アノード(本発明の場合には銅アノードなど)ではなくアノードプレートに接続される。

【0106】

また図10Aには、コンタクト領域128に接触するコンタクト部材126の位置が示されている。コンタクト部材は、種々の構成(ブラシ、ピン、ローラー、平坦面など)で製造しても良い。コンタクト部材は、アノードから完全に絶縁されていなければならず、好ましくは静止していてコンタクト領域がその上を滑る。コンタクト部材がウェハーとともに移動しても良い。コンタクト部材は好ましくは、柔軟で耐食性の導電材料(プラチナ、ルテニウム、ロジウム、および耐熱性材料の窒化物など)で形成されるか、またはこれらの材料でコートされている。前述したように(図10Aに示す)、従来のクランプを、ウェハー108の前面132との電気コンタクトを取るためには全く用いていないため、電着中のエッジ除外が有利なことに低減されて、ゼロになっている。コンタクト部材がコンタクト領域を引っ掻く可能性があるが、これは、コンタクト部材がコンタクト領域に加える力が最小であることを保証することで、回避または最小限にできる。

【0107】

図10Aに戻って、好ましい実施形態のプロセスでは、電解液をポンプによって、電着システム100のアノードカップ116の内部キャビティ162内へ、矢印122の方向に入れる。いったん電解液が内部キャビティ162を満たせば、電解液は、アノードプレート118の孔159、それから成形プレート114のアスペリティ120を通って流れることによって、ウェハー108の前面132に矢印164の方向に到達する。図10A〜10Bを参照して、ウェハー108の前面132は、軸134に沿う第1の位置、好ましくは成形プレート114に近接する位置(たとえば0.25〜5mmの距離)に、保持しても良い。ウェハー108の前面132と成形プレート114との間のギャップは、キャリアアセンブリ102を軸134に沿って垂直に動かすことによって調整できる。前面132と成形プレート114の上面との間の距離を調整した後に、アノード112とコンタクト部材126との間に電位差を印加することによって、電着プロセスを開始する。その結果、この段階では、電位差は、コンタクト部材がアノードよりも陰極性(−)になるように選択されている。またコンタクト部材はウェハー108の前面132に接触しているため、前面132も陰極性となる。

【0108】

ここで、本発明のシステム100を用いる電着プロセスの詳細を、図11Aおよび11Bを用いてさらに説明することができる。図11Aに、電着プロセス前のウェハー108の前面132(図8を参照)の表面部分166を例示する。表面部分166は、ビアフィーチャー168または狭いホールおよびトレンチ170またはより大きなホールを備えていても良い。ビアフィーチャー168およびトレンチフィーチャー170は、ウェハー108の一部であり得る基板174上に形成される絶縁層172内に形成されていても良いし、ウェハー108上に形成されていても良い。フィーチャー168および170は、基板174上の活性デバイス位置176を露出する。

【0109】

図10Bを参照して、電位差が印加されるとすぐに銅が前面132上にメッキされ、同時に図10Bに示したように、ウェハー108を回転方向135に回転させて、成形プレート114上を第1の方向147に直線的に移動させる。第1の方向147は好ましくは、後退エッジ144に平行で、側面エッジ146に垂直である。第1の方向147への直線運動は好ましくは、ウェハーサイズに依存して約5mm〜100mmであっても良いが、それ以上に長い直線運動も本発明の範囲内であり、用いることができる。この点で、ウェハー108の回転は約1rpm〜250rpmであっても良い。ウェハーを横方向に動かすことが好ましいが、ウェハーを回転させてアノードアセンブリを横方向に動かすことで、同様の動きをウェハーと成形プレートとの間に実現しても良いことを理解されたい。図11Bに示すように、電着プロセスが進行するにつれて、堆積層180が銅シード層178上に均一に形成されて、ビアおよびトレンチフィーチャー168および170を充填する。前述したように、銅シード層178は、バリア層の上に形成しても良い。また前述したように、ウェハー108を回転させることで、堆積層の不均一性は最小限になる。ウェハー上のコンタクト領域128が銅メッキされ得るのは、コンタクト領域128が、成形プレート114のアスペリティ120の上方で回転しているとき、したがって電解液にさらされているときのみである。

【0110】

図10Bを参照して、平坦な薄膜を堆積させるために、成形プレート114とウェハー108前面との間のギャップをゼロまで減らして、前面132を成形プレート114の上面119と接触させても良い。これは、キャリアアセンブリ102とウェハー108とを、軸134に沿って垂直に動かして第2の位置へ持っていくことによって行なわれる。この場合、成形プレートは研磨パッドで形成されていても良い。代替的に、アノードアセンブリ104を軸134に沿って垂直に動かしても良い(ただし、アセンブリがこのような動きのために装備されている場合)。この第2の位置において、ウェハー108は回転して第1の方向147に沿って移動するため、堆積プロセスが続く間、ウェハー108は成形プレート114と接触して擦れる。図11Cに示したように、この結果、平坦化された層182が形成される。これは、絶縁層172上の堆積層180の厚みを最小限にしながら、フィーチャー168および170内への材料の堆積を妨げないからである。

【0111】

システムの極性を反対にすると、材料を均一に堆積させる代わりに、ウェハー表面から材料を均一に除去(電解エッチング)するために、システム100を用いることができる。この場合、メッキ電解液の代わりに、一般的に知られる電解エッチングまたは電解研磨溶液を用いても良い。Cuアノードの代わりに、不活性電極(不活性材料たとえばPt、Ti、またはPtコートされたTi材料から形成される)を用いても良い。

【0112】

言うまでもないが、前述したことは本発明の好ましい実施形態に関しており、特許請求の範囲に記載される本発明の趣旨および範囲を逸脱することなく変更を行なっても良いことを理解されたい。

【図面の簡単な説明】

【図1A】 基板上に形成されたアイソレーション構造を有する半導体基板の概略図であり、アイソレーション構造はエッチされてトレンチおよびビアフィーチャーが基板上に形成されている。

【図1B】 バリア層およびシード層が、フィーチャーおよびアイソレーションまたは絶縁層上に形成されている図1Aに示した基板の部分断面図。

【図1C】 従来のコンフォーマル層が、シード層上に部分的に堆積されている図1Bに示した構造の概略図。

【図1D】 層が完全に堆積されている図1Cに示した構造の概略図。

【図1E】 より平坦な層が形成されている図1Dに示した構造の概略図。

【図2A】 従来技術の電着システムの概略図。

【図2B】 シールドを用いた他の従来技術の電着システムの概略図。

【図3】 エッジ領域を何ら除外しないでウェハー全面へ導電材料を堆積するための本発明のシステムの一実施形態を示す概略図。

【図4】 本発明のアノードカップの周囲側壁の幅と比較した、ウェハー上の電気コンタクトおよびコンタクト領域の位置を示す図3に示したシステムの概略図。

【図5】 ウェハー上の断続的および連続的堆積領域を示す図3に示したシステムの部分平面図。

【図6】 システムのアノードおよびカソードの間に配置されたシールドを備える図3に示した本発明のシステムの概略図。

【図7】 エッジ領域を何ら除外しないでウェハー全面へ導電材料を堆積するための本発明のシステムの他の実施形態を示す概略図。

【図8】 本発明のウェハーキャリアアセンブリおよび成形プレートを示す図7のシステムの部分概略図。

【図9A】 ウェハーは連続的および断続的堆積領域を有している、成形プレートとその上に配置されたウェハーとを示す平面図。

【図9B】 成形プレートを通る連続したアスペリティを示す成形プレートの概略断面図。

【図9C】 成形プレートは開口部密度が異なる2つの領域を有する本発明の成形プレートの他の実施形態を示す概略図。

【図10A】 本発明の成形プレートの幅と比較した、コンタクト領域上のウェハー電気コンタクトの位置を示す本発明の電着システムの概略側面図。

【図10B】 本発明の成形プレートの長さに沿うウェハーの位置を示す本発明の電着システムの他の概略側面図。

【図11A】 本発明の堆積プロセス前の、シード層で覆われたビアおよびトレンチフィーチャーを有するウェハーを大きく拡大した断面図。

【図11B】 本発明を用いて堆積層が電着されている図11Aに示した構造の概略図。

【図11C】 堆積層が平坦に堆積されている図11Bに示した構造の概略図。

【符号の説明】

10…基板

12…絶縁層

14…ビア

16…トレンチ

18…バリア層

20…シード層

22…導電材料層

30…電着システム

32…ウェハー

34…ウェハーホルダー

36…リングクランプ

38…電気コンタクト

40…メッキ浴

44…アノード

46…シールド

50…電着システム

53…ウェハーキャリア

54…ウェハー

55…キャリアアーム

56…アノード

57…アノードカップ

58…内部キャビティ

61…リムフレーム

62…電解液

63…液体入口

64…アノードコネクター

65…ウェハー前面

66…電気コンタクト部材

67…コンタクト領域

68…コネクター

70…保持リング

73、74…第2の側壁

75、76…第4の側壁

82…シールド

100…電着システム

102…キャリアアセンブリ

104…アノードアセンブリ

106…ウェハーキャリア

108…ウェハー

110…キャリアアーム

112…アノード

114…成形プレート

116…アノードカップ

118…アノードプレート

120…開口部

121…液体入口

124…アノードコネクター

126…電気コンタクト部材

128…コンタクト領域

129…コネクター

133…保持リング

136、138…第2の側壁

140、142…第4の側壁

140…第4の側壁

157…第1のアスペリティ領域

158…第2のアスペリティ領域

160…電解液経路

162…内部キャビティ

168…ビアフィーチャー

170…トレンチフィーチャー

172…絶縁層

174…基板

176…活性デバイス位置

178…銅シード層

180…堆積層

S1…段差

S2…段差

D…最大横方向寸法

d…最大横方向距離

Claims (11)

- ウェハーとの間で電気的なコンタクトを取るための装置であって、

前記ウェハーは、その前面側の表面に、エッジ部分及び内側部分を備えた導電性レイヤを有しており、

前記ウェハーの前記エッジ部分のみで、前記導電性レイヤとの間で電気的なコンタクトを取る、少なくとも一つのコンタクト部材を有し、前記少なくとも一つのコンタクト部材と前記ウェハーの間の相対的な運動により、前記少なくとも一つのコンタクト部材を前記ウェハーのエッジ部分の異なる部分に電気的にコンタクトさせるように構成された装置において、

前記ウェハーを保持するためのウェハーキャリアと、

電極と、

前記ウェハーの近傍に配置され、前記電極とウェハーの間に位置し、前記溶液の存在下で前記ウェハーの前面側の表面に物理的に接触することによって、前記ウェハーの前面側の表面の処理をするためのパッドと、

を備え、

前記少なくとも一つのコンタクト部材は、前記電極と前記ウェハーの間で電位差を維持することによって、前記ウェハーを電気化学的に加工するように構成され、且つ、前記ウェハーの前面側の表面に物理的に接触することによって、前記パッドで前記ウェハーの前面側の表面の処理をするように構成されていることを特徴とする装置。 - 前記ウェハーの近傍に配置された前記パッドは、前記ウェハーの一部をカバーしていないこと、及び、

前記パッドは、電流密度が高い領域と電流密度が低い他の領域を有するように構成されていること、

を特徴とする請求項1に記載の電気化学的加工装置。 - 前記ウェハーを前記パッドに対して、前記パッドの表面に平行な方向に、移動させるための手段を、更に備え、それによって、前記ウェハーの前記一部が、前記パッドの前記電流密度が高い領域の上に来るように構成されていることを特徴とする請求項2に記載の電気化学的加工装置。

- 前記ウェハーを前記パッドに対して、前記パッドの表面に平行な方向に、移動させるための手段を、更に備えたことを特徴とする請求項2に記載の電気化学的加工装置。

- 二つのコンタクト部材を備え、各コンタクト部材は、前記ウェハーの実質的に反対側のエッジ部分に配置されることを特徴とする請求項1に記載の電気化学的加工装置。

- ウェハーとの間で電気的なコンタクトを取るための方法であって、

前記ウェハーは、その前面側の表面に、エッジ部分及び内側部分を備えた導電性レイヤを有しており、

前記ウェハーの前記エッジ部分で、少なくとも一つのコンタクト部材と前記ウェハーの前記導電性レイヤとの間で相対的な運動を発生させ、それによって、前記少なくとも一つのコンタクト部材を、前記ウェハーの連続するエッジ部分の異なる部分に電気的にコンタクトさせる方法において、

前記相対的な運動を発生させるステップで、相対的な回転及び直線運動を発生させること、及び、

前記ウェハーの前記導電性レイヤと電極の間の電位差を維持し、この電位差が維持されている間に、溶液を用いて、少なくとも前記ウェハーの内側部分に対して、電気化学的な処理を行うこと、

を特徴とする方法。 - ウェハーとの間で電気的なコンタクトを取るための方法であって、

前記ウェハーは、その前面側の表面に、エッジ部分及び内側部分を備えた導電性レイヤを有しており、

前記ウェハーの前記エッジ部分で、少なくとも一つのコンタクト部材と前記ウェハーの前記導電性レイヤとの間で相対的な運動を発生させ、それによって、前記少なくとも一つのコンタクト部材を、前記ウェハーの連続するエッジ部分の異なる部分に電気的にコンタクトさせる方法において、

前記ウェハーの前記導電性レイヤと電極の間の電位差を維持し、この電位差が維持されている間に、溶液を用いて、少なくとも前記ウェハーの内側部分に対して、電気化学的加工を行うこと、及び、

前記電気化学的加工のプロセスは、前記ウェハーに対して摺動可能な状態で接触し且つ前記電極とウェハーの間に配置されたパッドを、前記溶液の存在の下で動かすことを含むこと、

を特徴とする方法。 - 前記電気化学的加工を行うステップの間、前記パッドは前記ウェハーの一部をカバーしていないこと、及び、

前記パッドは、電流密度が高い領域及び電流密度が低い他の領域を有するように構成されていること、

を特徴とする請求項7に記載の方法。 - 前記電気化学的加工を行うステップは、前記ウェハーを前記パッドに対して、前記パッドの表面に平行な方向に、移動させるステップを含むことを特徴とする請求項8に記載の方法。

- 前記動きは回転運動を含み、前記少なくとも一つのコンタクト部材及び前記ウェハーのそれぞれの相対的な回転は、前記ウェハーの回転の度に繰り返されるところの、前記ウェハーの連続するエッジ部分の異なる部分との電気的なコンタクトを発生させることを特徴とする請求項7に記載の方法。

- 前記少なくとも一つのコンタクト部材は、二つのコンタクト部材を備え、

各コンタクト部材は、実質的に反対側のエッジ部分に配置され、

各コンタクト部材は、相対的な運動を発生させる前記ステップの間、前記ウェハーのエッジ部分の異なる部分に電気的にコンタクトすること、

を特徴とする請求項7に記載の方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US24521100P | 2000-11-03 | 2000-11-03 | |

| US09/760,757 US6610190B2 (en) | 2000-11-03 | 2001-01-17 | Method and apparatus for electrodeposition of uniform film with minimal edge exclusion on substrate |

| PCT/US2001/051158 WO2002057514A2 (en) | 2000-11-03 | 2001-11-02 | Method and apparatus for electrodeposition or etching of uniform film with minimal edge exclusion on substrate |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005501963A JP2005501963A (ja) | 2005-01-20 |

| JP2005501963A5 JP2005501963A5 (ja) | 2005-04-07 |

| JP4034655B2 true JP4034655B2 (ja) | 2008-01-16 |

Family

ID=26937071

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002558562A Expired - Fee Related JP4034655B2 (ja) | 2000-11-03 | 2001-11-02 | 均一な薄膜を最小限のエッジ除外で基板上へ電着する方法および装置 |

Country Status (8)

| Country | Link |

|---|---|

| US (3) | US6610190B2 (ja) |

| EP (1) | EP1332243A2 (ja) |

| JP (1) | JP4034655B2 (ja) |

| KR (1) | KR100801270B1 (ja) |

| CN (1) | CN1253608C (ja) |

| AU (1) | AU2002246910A1 (ja) |

| TW (1) | TW511167B (ja) |

| WO (1) | WO2002057514A2 (ja) |

Families Citing this family (56)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7686935B2 (en) * | 1998-10-26 | 2010-03-30 | Novellus Systems, Inc. | Pad-assisted electropolishing |

| US6251235B1 (en) | 1999-03-30 | 2001-06-26 | Nutool, Inc. | Apparatus for forming an electrical contact with a semiconductor substrate |

| US6610190B2 (en) * | 2000-11-03 | 2003-08-26 | Nutool, Inc. | Method and apparatus for electrodeposition of uniform film with minimal edge exclusion on substrate |

| US6413388B1 (en) * | 2000-02-23 | 2002-07-02 | Nutool Inc. | Pad designs and structures for a versatile materials processing apparatus |

| US7097755B2 (en) | 1998-12-01 | 2006-08-29 | Asm Nutool, Inc. | Electrochemical mechanical processing with advancible sweeper |

| US6497800B1 (en) * | 2000-03-17 | 2002-12-24 | Nutool Inc. | Device providing electrical contact to the surface of a semiconductor workpiece during metal plating |

| US7204917B2 (en) | 1998-12-01 | 2007-04-17 | Novellus Systems, Inc. | Workpiece surface influencing device designs for electrochemical mechanical processing and method of using the same |

| US6902659B2 (en) * | 1998-12-01 | 2005-06-07 | Asm Nutool, Inc. | Method and apparatus for electro-chemical mechanical deposition |

| US6534116B2 (en) * | 2000-08-10 | 2003-03-18 | Nutool, Inc. | Plating method and apparatus that creates a differential between additive disposed on a top surface and a cavity surface of a workpiece using an external influence |

| US6355153B1 (en) * | 1999-09-17 | 2002-03-12 | Nutool, Inc. | Chip interconnect and packaging deposition methods and structures |

| US6852208B2 (en) | 2000-03-17 | 2005-02-08 | Nutool, Inc. | Method and apparatus for full surface electrotreating of a wafer |

| US7754061B2 (en) * | 2000-08-10 | 2010-07-13 | Novellus Systems, Inc. | Method for controlling conductor deposition on predetermined portions of a wafer |

| US6921551B2 (en) | 2000-08-10 | 2005-07-26 | Asm Nutool, Inc. | Plating method and apparatus for controlling deposition on predetermined portions of a workpiece |

| US20040170753A1 (en) * | 2000-12-18 | 2004-09-02 | Basol Bulent M. | Electrochemical mechanical processing using low temperature process environment |

| US7172497B2 (en) * | 2001-01-05 | 2007-02-06 | Asm Nutool, Inc. | Fabrication of semiconductor interconnect structures |

| US7211186B2 (en) * | 2001-01-17 | 2007-05-01 | Novellus Systems, Inc. | Method and system to provide electrical contacts for electrotreating processes |

| US7211174B2 (en) * | 2001-01-17 | 2007-05-01 | Novellus Systems, Inc. | Method and system to provide electrical contacts for electrotreating processes |

| US7244347B2 (en) * | 2001-01-17 | 2007-07-17 | Novellus Systems, Inc. | Method and system to provide electrical contacts for electrotreating processes |

| KR20040070342A (ko) * | 2001-10-26 | 2004-08-07 | 누툴 인코포레이티드 | 전기처리 공정용 전기 콘택을 제공하는 방법 및 시스템 |

| US6815354B2 (en) * | 2001-10-27 | 2004-11-09 | Nutool, Inc. | Method and structure for thru-mask contact electrodeposition |

| EP1439935A2 (en) * | 2001-11-02 | 2004-07-28 | Nutool, Inc. | Electrochemical mechanical processing with advancible sweeper |

| US6776693B2 (en) * | 2001-12-19 | 2004-08-17 | Applied Materials Inc. | Method and apparatus for face-up substrate polishing |

| US20060137994A1 (en) * | 2001-12-21 | 2006-06-29 | Basol Bulent M | Method of wafer processing with edge seed layer removal |

| US6833063B2 (en) * | 2001-12-21 | 2004-12-21 | Nutool, Inc. | Electrochemical edge and bevel cleaning process and system |

| US7029567B2 (en) * | 2001-12-21 | 2006-04-18 | Asm Nutool, Inc. | Electrochemical edge and bevel cleaning process and system |

| EP1495161A4 (en) * | 2002-04-12 | 2006-06-28 | Acm Res Inc | ELECTROPOLISHING AND ELECTRODEPOSITION PROCESSES |

| US7128823B2 (en) | 2002-07-24 | 2006-10-31 | Applied Materials, Inc. | Anolyte for copper plating |

| US7090750B2 (en) * | 2002-08-26 | 2006-08-15 | Micron Technology, Inc. | Plating |

| US20040226654A1 (en) * | 2002-12-17 | 2004-11-18 | Akihisa Hongo | Substrate processing apparatus and substrate processing method |

| US7201828B2 (en) * | 2003-02-25 | 2007-04-10 | Novellus Systems, Inc. | Planar plating apparatus |

| US20050173260A1 (en) * | 2003-03-18 | 2005-08-11 | Basol Bulent M. | System for electrochemical mechanical polishing |

| DK1620568T3 (da) * | 2003-04-24 | 2009-03-30 | Afshin Ahmadian | Analyse til allelspecifik mutationspåvisning |

| US7335288B2 (en) * | 2003-09-18 | 2008-02-26 | Novellus Systems, Inc. | Methods for depositing copper on a noble metal layer of a work piece |

| WO2005045906A1 (en) * | 2003-10-29 | 2005-05-19 | Asm Nutool, Inc. | System and method for electroless surface conditioning |

| US7064057B2 (en) * | 2003-11-21 | 2006-06-20 | Asm Nutool, Inc. | Method and apparatus for localized material removal by electrochemical polishing |

| US7648622B2 (en) * | 2004-02-27 | 2010-01-19 | Novellus Systems, Inc. | System and method for electrochemical mechanical polishing |

| US20060183321A1 (en) * | 2004-09-27 | 2006-08-17 | Basol Bulent M | Method for reduction of gap fill defects |

| US7550070B2 (en) * | 2006-02-03 | 2009-06-23 | Novellus Systems, Inc. | Electrode and pad assembly for processing conductive layers |

| EP1839695A1 (en) * | 2006-03-31 | 2007-10-03 | Debiotech S.A. | Medical liquid injection device |

| US8500985B2 (en) | 2006-07-21 | 2013-08-06 | Novellus Systems, Inc. | Photoresist-free metal deposition |

| US7732329B2 (en) * | 2006-08-30 | 2010-06-08 | Ipgrip, Llc | Method and apparatus for workpiece surface modification for selective material deposition |

| US20080237048A1 (en) * | 2007-03-30 | 2008-10-02 | Ismail Emesh | Method and apparatus for selective electrofilling of through-wafer vias |

| DE102007026633B4 (de) * | 2007-06-06 | 2009-04-02 | Atotech Deutschland Gmbh | Vorrichtung und Verfahren zum elektrolytischen Behandeln von plattenförmiger Ware |

| US20090065365A1 (en) * | 2007-09-11 | 2009-03-12 | Asm Nutool, Inc. | Method and apparatus for copper electroplating |

| TWI410531B (zh) * | 2010-05-07 | 2013-10-01 | Taiwan Semiconductor Mfg | 直立式電鍍設備及其電鍍方法 |

| US9988734B2 (en) | 2011-08-15 | 2018-06-05 | Lam Research Corporation | Lipseals and contact elements for semiconductor electroplating apparatuses |

| KR102092416B1 (ko) * | 2012-03-30 | 2020-03-24 | 노벨러스 시스템즈, 인코포레이티드 | 역전류 디플레이팅을 이용한 전기도금 기판 홀더의 클리닝 |

| WO2014098774A1 (en) * | 2012-12-21 | 2014-06-26 | Agency For Science, Technology And Research | Porous metallic membrane |

| CN105637125B (zh) * | 2013-11-14 | 2017-10-13 | 丰田自动车株式会社 | 金属被膜的成膜装置及其成膜方法 |

| JP5826952B2 (ja) | 2014-01-17 | 2015-12-02 | 株式会社荏原製作所 | めっき方法およびめっき装置 |

| JP6745103B2 (ja) * | 2014-11-26 | 2020-08-26 | ノベラス・システムズ・インコーポレーテッドNovellus Systems Incorporated | 半導体電気メッキ装置用のリップシールおよび接触要素 |

| US10053793B2 (en) | 2015-07-09 | 2018-08-21 | Lam Research Corporation | Integrated elastomeric lipseal and cup bottom for reducing wafer sticking |

| US20170145577A1 (en) * | 2015-11-19 | 2017-05-25 | Rohm And Haas Electronic Materials Llc | Method of electroplating low internal stress copper deposits on thin film substrates to inhibit warping |

| US20190096866A1 (en) * | 2017-09-26 | 2019-03-28 | Powertech Technology Inc. | Semiconductor package and manufacturing method thereof |

| US20230012414A1 (en) * | 2019-11-27 | 2023-01-12 | Lam Research Corporation | Edge removal for through-resist plating |

| US11230778B2 (en) * | 2019-12-13 | 2022-01-25 | Macdermid Enthone Inc. | Cobalt chemistry for smooth topology |

Family Cites Families (62)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3328273A (en) | 1966-08-15 | 1967-06-27 | Udylite Corp | Electro-deposition of copper from acidic baths |

| FR2510145B1 (fr) | 1981-07-24 | 1986-02-07 | Rhone Poulenc Spec Chim | Additif pour bain de cuivrage electrolytique acide, son procede de preparation et son application au cuivrage des circuits imprimes |

| US4948474A (en) | 1987-09-18 | 1990-08-14 | Pennsylvania Research Corporation | Copper electroplating solutions and methods |

| DE3836521C2 (de) | 1988-10-24 | 1995-04-13 | Atotech Deutschland Gmbh | Wäßriges saures Bad zur galvanischen Abscheidung von glänzenden und rißfreien Kupferüberzügen und Verwendung des Bades |

| US5084071A (en) | 1989-03-07 | 1992-01-28 | International Business Machines Corporation | Method of chemical-mechanical polishing an electronic component substrate and polishing slurry therefor |

| US4954142A (en) | 1989-03-07 | 1990-09-04 | International Business Machines Corporation | Method of chemical-mechanical polishing an electronic component substrate and polishing slurry therefor |

| US5256565A (en) | 1989-05-08 | 1993-10-26 | The United States Of America As Represented By The United States Department Of Energy | Electrochemical planarization |

| US5225034A (en) | 1992-06-04 | 1993-07-06 | Micron Technology, Inc. | Method of chemical mechanical polishing predominantly copper containing metal layers in semiconductor processing |

| JP3397501B2 (ja) | 1994-07-12 | 2003-04-14 | 株式会社東芝 | 研磨剤および研磨方法 |

| US5567300A (en) * | 1994-09-02 | 1996-10-22 | Ibm Corporation | Electrochemical metal removal technique for planarization of surfaces |

| US5516412A (en) | 1995-05-16 | 1996-05-14 | International Business Machines Corporation | Vertical paddle plating cell |

| US5795215A (en) | 1995-06-09 | 1998-08-18 | Applied Materials, Inc. | Method and apparatus for using a retaining ring to control the edge effect |

| US5681215A (en) | 1995-10-27 | 1997-10-28 | Applied Materials, Inc. | Carrier head design for a chemical mechanical polishing apparatus |

| KR100232506B1 (ko) | 1995-06-27 | 1999-12-01 | 포만 제프리 엘. | 전기적 접속을 제공하는 배선 구조 및 도체와 그 도체형성방법 |

| US5755859A (en) | 1995-08-24 | 1998-05-26 | International Business Machines Corporation | Cobalt-tin alloys and their applications for devices, chip interconnections and packaging |

| US5762544A (en) | 1995-10-27 | 1998-06-09 | Applied Materials, Inc. | Carrier head design for a chemical mechanical polishing apparatus |

| US5840629A (en) | 1995-12-14 | 1998-11-24 | Sematech, Inc. | Copper chemical mechanical polishing slurry utilizing a chromate oxidant |

| US5858813A (en) | 1996-05-10 | 1999-01-12 | Cabot Corporation | Chemical mechanical polishing slurry for metal layers and films |

| US5862605A (en) * | 1996-05-24 | 1999-01-26 | Ebara Corporation | Vaporizer apparatus |

| US5793272A (en) | 1996-08-23 | 1998-08-11 | International Business Machines Corporation | Integrated circuit toroidal inductor |

| US5773364A (en) | 1996-10-21 | 1998-06-30 | Motorola, Inc. | Method for using ammonium salt slurries for chemical mechanical polishing (CMP) |

| US5954997A (en) | 1996-12-09 | 1999-09-21 | Cabot Corporation | Chemical mechanical polishing slurry useful for copper substrates |

| EP0932913A1 (en) | 1996-12-16 | 1999-08-04 | International Business Machines Corporation | Electroplated interconnection structures on integrated circuit chips |

| US5933753A (en) | 1996-12-16 | 1999-08-03 | International Business Machines Corporation | Open-bottomed via liner structure and method for fabricating same |

| US5807165A (en) | 1997-03-26 | 1998-09-15 | International Business Machines Corporation | Method of electrochemical mechanical planarization |

| US5911619A (en) | 1997-03-26 | 1999-06-15 | International Business Machines Corporation | Apparatus for electrochemical mechanical planarization |

| US5930669A (en) | 1997-04-03 | 1999-07-27 | International Business Machines Corporation | Continuous highly conductive metal wiring structures and method for fabricating the same |

| US5922091A (en) | 1997-05-16 | 1999-07-13 | National Science Council Of Republic Of China | Chemical mechanical polishing slurry for metallic thin film |

| US6001235A (en) | 1997-06-23 | 1999-12-14 | International Business Machines Corporation | Rotary plater with radially distributed plating solution |

| US5985123A (en) | 1997-07-09 | 1999-11-16 | Koon; Kam Kwan | Continuous vertical plating system and method of plating |

| WO1999016936A1 (en) * | 1997-09-30 | 1999-04-08 | Semitool, Inc. | Electroplating system having auxiliary electrode exterior to main reactor chamber for contact cleaning operations |

| US5897375A (en) | 1997-10-20 | 1999-04-27 | Motorola, Inc. | Chemical mechanical polishing (CMP) slurry for copper and method of use in integrated circuit manufacture |

| US6156167A (en) | 1997-11-13 | 2000-12-05 | Novellus Systems, Inc. | Clamshell apparatus for electrochemically treating semiconductor wafers |

| US6027631A (en) | 1997-11-13 | 2000-02-22 | Novellus Systems, Inc. | Electroplating system with shields for varying thickness profile of deposited layer |

| US6159354A (en) | 1997-11-13 | 2000-12-12 | Novellus Systems, Inc. | Electric potential shaping method for electroplating |

| US6004880A (en) | 1998-02-20 | 1999-12-21 | Lsi Logic Corporation | Method of single step damascene process for deposition and global planarization |

| US5976331A (en) | 1998-04-30 | 1999-11-02 | Lucent Technologies Inc. | Electrodeposition apparatus for coating wafers |

| US6071388A (en) | 1998-05-29 | 2000-06-06 | International Business Machines Corporation | Electroplating workpiece fixture having liquid gap spacer |

| US6074544A (en) | 1998-07-22 | 2000-06-13 | Novellus Systems, Inc. | Method of electroplating semiconductor wafer using variable currents and mass transfer to obtain uniform plated layer |

| US6132587A (en) | 1998-10-19 | 2000-10-17 | Jorne; Jacob | Uniform electroplating of wafers |

| US6176992B1 (en) | 1998-11-03 | 2001-01-23 | Nutool, Inc. | Method and apparatus for electro-chemical mechanical deposition |

| US6497800B1 (en) * | 2000-03-17 | 2002-12-24 | Nutool Inc. | Device providing electrical contact to the surface of a semiconductor workpiece during metal plating |

| US6534116B2 (en) * | 2000-08-10 | 2003-03-18 | Nutool, Inc. | Plating method and apparatus that creates a differential between additive disposed on a top surface and a cavity surface of a workpiece using an external influence |

| US7578923B2 (en) * | 1998-12-01 | 2009-08-25 | Novellus Systems, Inc. | Electropolishing system and process |

| US6610190B2 (en) * | 2000-11-03 | 2003-08-26 | Nutool, Inc. | Method and apparatus for electrodeposition of uniform film with minimal edge exclusion on substrate |

| US6589105B2 (en) * | 1998-12-01 | 2003-07-08 | Nutool, Inc. | Pad tensioning method and system in a bi-directional linear polisher |

| US6902659B2 (en) * | 1998-12-01 | 2005-06-07 | Asm Nutool, Inc. | Method and apparatus for electro-chemical mechanical deposition |

| US6251235B1 (en) * | 1999-03-30 | 2001-06-26 | Nutool, Inc. | Apparatus for forming an electrical contact with a semiconductor substrate |

| US6103085A (en) | 1998-12-04 | 2000-08-15 | Advanced Micro Devices, Inc. | Electroplating uniformity by diffuser design |

| US6261426B1 (en) * | 1999-01-22 | 2001-07-17 | International Business Machines Corporation | Method and apparatus for enhancing the uniformity of electrodeposition or electroetching |

| US6066030A (en) | 1999-03-04 | 2000-05-23 | International Business Machines Corporation | Electroetch and chemical mechanical polishing equipment |

| US6136163A (en) * | 1999-03-05 | 2000-10-24 | Applied Materials, Inc. | Apparatus for electro-chemical deposition with thermal anneal chamber |

| JP3422731B2 (ja) * | 1999-07-23 | 2003-06-30 | 理化学研究所 | Elidセンタレス研削装置 |

| US6653226B1 (en) * | 2001-01-09 | 2003-11-25 | Novellus Systems, Inc. | Method for electrochemical planarization of metal surfaces |

| US6848970B2 (en) * | 2002-09-16 | 2005-02-01 | Applied Materials, Inc. | Process control in electrochemically assisted planarization |

| US6482307B2 (en) * | 2000-05-12 | 2002-11-19 | Nutool, Inc. | Method of and apparatus for making electrical contact to wafer surface for full-face electroplating or electropolishing |

| US6346479B1 (en) * | 2000-06-14 | 2002-02-12 | Advanced Micro Devices, Inc. | Method of manufacturing a semiconductor device having copper interconnects |

| US7220166B2 (en) * | 2000-08-30 | 2007-05-22 | Micron Technology, Inc. | Methods and apparatus for electromechanically and/or electrochemically-mechanically removing conductive material from a microelectronic substrate |

| US6696358B2 (en) * | 2001-01-23 | 2004-02-24 | Honeywell International Inc. | Viscous protective overlayers for planarization of integrated circuits |

| US7201829B2 (en) * | 2001-03-01 | 2007-04-10 | Novellus Systems, Inc. | Mask plate design |

| US6482656B1 (en) * | 2001-06-04 | 2002-11-19 | Advanced Micro Devices, Inc. | Method of electrochemical formation of high Tc superconducting damascene interconnect for integrated circuit |

| TW584899B (en) * | 2001-07-20 | 2004-04-21 | Nutool Inc | Planar metal electroprocessing |

-

2001

- 2001-01-17 US US09/760,757 patent/US6610190B2/en not_active Expired - Lifetime

- 2001-05-28 TW TW090112769A patent/TW511167B/zh not_active IP Right Cessation

- 2001-11-02 KR KR1020027008660A patent/KR100801270B1/ko not_active IP Right Cessation

- 2001-11-02 AU AU2002246910A patent/AU2002246910A1/en not_active Abandoned

- 2001-11-02 WO PCT/US2001/051158 patent/WO2002057514A2/en not_active Application Discontinuation

- 2001-11-02 EP EP01994521A patent/EP1332243A2/en not_active Withdrawn

- 2001-11-02 JP JP2002558562A patent/JP4034655B2/ja not_active Expired - Fee Related

- 2001-11-02 CN CNB018044514A patent/CN1253608C/zh not_active Expired - Fee Related

-

2003

- 2003-06-11 US US10/460,032 patent/US6942780B2/en not_active Expired - Lifetime

-

2005

- 2005-09-13 US US11/225,913 patent/US20060006060A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| CN1433487A (zh) | 2003-07-30 |

| WO2002057514A3 (en) | 2003-02-06 |

| CN1253608C (zh) | 2006-04-26 |

| JP2005501963A (ja) | 2005-01-20 |

| TW511167B (en) | 2002-11-21 |

| AU2002246910A1 (en) | 2002-07-30 |

| US6942780B2 (en) | 2005-09-13 |

| US6610190B2 (en) | 2003-08-26 |

| US20060006060A1 (en) | 2006-01-12 |

| KR100801270B1 (ko) | 2008-02-04 |

| WO2002057514A2 (en) | 2002-07-25 |

| KR20020095179A (ko) | 2002-12-20 |

| EP1332243A2 (en) | 2003-08-06 |

| US20030209429A1 (en) | 2003-11-13 |

| US20020053516A1 (en) | 2002-05-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4034655B2 (ja) | 均一な薄膜を最小限のエッジ除外で基板上へ電着する方法および装置 | |

| JP2005501963A5 (ja) | ||

| US6802946B2 (en) | Apparatus for controlling thickness uniformity of electroplated and electroetched layers | |

| US6946066B2 (en) | Multi step electrodeposition process for reducing defects and minimizing film thickness | |

| US6852630B2 (en) | Electroetching process and system | |

| KR100616198B1 (ko) | 기판상에 전기도금하는 전기화학적 증착 시스템 및 방법 | |

| US9593431B2 (en) | Electroplating systems | |

| JP2006505697A (ja) | 電解研磨のためのシステムと方法 | |

| JP2001185553A (ja) | 電気めっき充填を改善する方法 | |

| US8099861B2 (en) | Current-leveling electroplating/electropolishing electrode | |

| US20070141818A1 (en) | Method of depositing materials on full face of a wafer | |

| JP2005520043A (ja) | 電着における粒子の蓄積を避けるための方法および装置 | |

| US7201829B2 (en) | Mask plate design | |

| US6652726B1 (en) | Method for reducing wafer edge defects in an electrodeposition process | |

| US6797144B2 (en) | Method for reducing surface defects in an electrodeposition process | |

| US20090020437A1 (en) | Method and system for controlled material removal by electrochemical polishing | |

| JP2010037637A (ja) | 電解処理装置及び電解処理方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20041029 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070702 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070731 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070824 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20070925 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20071025 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101102 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111102 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121102 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121102 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131102 Year of fee payment: 6 |

|

| LAPS | Cancellation because of no payment of annual fees |