CN1183677C - 带开关-电容电阻的pll环路滤波器 - Google Patents

带开关-电容电阻的pll环路滤波器 Download PDFInfo

- Publication number

- CN1183677C CN1183677C CN00813738.2A CN00813738A CN1183677C CN 1183677 C CN1183677 C CN 1183677C CN 00813738 A CN00813738 A CN 00813738A CN 1183677 C CN1183677 C CN 1183677C

- Authority

- CN

- China

- Prior art keywords

- phase

- circuit

- locked loop

- voltage

- loop filter

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000003990 capacitor Substances 0.000 title claims abstract description 52

- 230000010355 oscillation Effects 0.000 claims description 16

- 238000000034 method Methods 0.000 claims description 8

- 230000010354 integration Effects 0.000 claims 1

- 238000013016 damping Methods 0.000 description 3

- 238000001228 spectrum Methods 0.000 description 3

- 238000012937 correction Methods 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 230000035945 sensitivity Effects 0.000 description 2

- 230000001960 triggered effect Effects 0.000 description 2

- 102100031456 Centriolin Human genes 0.000 description 1

- 101000941711 Homo sapiens Centriolin Proteins 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 230000009514 concussion Effects 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000001914 filtration Methods 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 230000001105 regulatory effect Effects 0.000 description 1

- 230000003595 spectral effect Effects 0.000 description 1

- 238000003786 synthesis reaction Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/093—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal using special filtering or amplification characteristics in the loop

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/089—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal the phase or frequency detector generating up-down pulses

- H03L7/0891—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal the phase or frequency detector generating up-down pulses the up-down pulses controlling source and sink current generators, e.g. a charge pump

Landscapes

- Stabilization Of Oscillater, Synchronisation, Frequency Synthesizers (AREA)

- Networks Using Active Elements (AREA)

Abstract

一种具有改善的噪声特性的锁相环电路,包括一种响应压控输入产生振荡输出信号的压控振荡器(12)。一个基准源提供基准频率信号。一个相位检测器(30)工作上连接到所述压控振荡器和基准源,产生与所述振荡输出信号和基准信号的相位差成比例的输出。一个环路滤波器(46)把所述相位检测器输出连接到所述压控输入。该环路滤波器包括一个开关-电容等效电阻(Q1,Q2,CR)。

Description

技术领域

本发明涉及锁相环滤波器电路,更具体地说,涉及带开关-电容电阻的环路滤波器。

背景技术

锁相环电路广泛用于要求产生高频周期信号的电路中,其中,所述信号的频率是某个非常稳定的低噪声基准频率信号频率的精确倍数。锁相环电路还应用于输出信号的相位必须跟踪基准信号的相位的场合,这也是其名称“锁相环”的由来。

锁相环电路用于在无线电发射器和接收器中产生局部振荡器信号。该局部振荡器信号用于通道选择,因此是稳定、低噪声且常常带温度补偿的基准信号发生器的倍数。锁相环电路还用于数字通讯系统中的时钟校正应用、磁盘驱动器读出通道等。锁相环电路还用于频率调制器以及把频率调制后的信号解调。在“单片电路锁相环和时钟校正电路,理论与设计”Behzad Razavi,IEEE出版物,1996中,讨论了典型应用的概述。

典型的锁相环电路包括把一个相位检测器连接到压控振荡器的环路滤波器。该环路滤波器限定锁相反馈环的动态特性,以满足某一稳定性标准,且使得所述环不会发生振荡。在二阶和更高阶的锁相环电路中,常通过在环路滤波器中插入一个电阻来实现该稳定性。该电阻产生大到影响锁相环输出信号的相位噪声频谱的热噪声。在环路带宽的邻近区域,环路滤波器电阻噪声可能在全部的相位噪声中占优。

本发明的目的是用一种新颖而且简单的方式克服上述问题中的一个或多个。

发明内容

根据本发明提供一种包括带有开关-电容电阻的环路滤波器的锁相环电路。

概括而言,在此公开一种具有改善的相位噪声特征的锁相环电路,包括响应压控输入而产生振荡输出信号的压控振荡器。一个基准源提供基准频率信号。一个相位检测器工作上连接到该压控振荡器和基准源,产生与振荡输出信号和基准频率信号的差值成比例的输出。一个环路滤波器将该相位检测器的输出连接到压控输入。该环路滤波器包括一个电容器和一个开关电路。该开关电路交替地把所述电容器连接到所述相位检测器输出和地。

本发明的特征之一是所述环路滤波器还包括连接在所述开关电路和所述相位检测器输出之间的第二电容器和连接在所述相位检测器输出和地之间的一个附加电容器。

本发明的另一特征是所述开关电路包括一个把所述电容器连接到所述相位检测器输出的第一晶体管和将所述电容器连接到地的第二晶体管。所述开关电路还包括一个非重叠时钟发生器电路,控制所述第一和第二晶体管。该时钟发生器电路工作在所述锁相环电路的环路带宽之上的频率。

本发明的一个附加特征是所述相位检测器包括一个相位频率检测器。该相位检测器还包括一个电荷泵(charge pump)电路,且所述环路滤波器将该电荷泵电路发出的电流脉冲在所述压控输入端转换为电压。该相位检测器包括一对带复位的边沿触发器,所述振荡输出信号和基准频率信号是这些触发器的时钟信号,这些触发器驱动上述电荷泵电路。

本发明还有一个特征,即提供将上述振荡输出信号和基准频率信号连接到所述相位检测器的分频器。

根据本发明的另一方面,公开了一种锁相环电路,包括响应压控输入而产生振荡输出信号的压控振荡器。一个基准源提供基准频率信号。一个相位检测器从工作上连接到该压控振荡器和基准源,产生具有正的或负的电流脉冲,且其脉冲宽度与振荡输出信号和基准频率信号的差值成比例的输出。一个环路滤波器将该相位检测器的输出连接到压控输入。该环路滤波器包括一个积分器,在压控输入端将电流脉冲转换为电压,还包括一个电容器和开关电路。该开关电路交替地把所述电容器连接到所述相位检测器输出和地上。

本发明提供了一种锁相环电路,包括:

响应压控输入产生振荡输出信号的压控振荡器;

提供基准频率信号的基准源;

工作上连接到所述压控振荡器和所述基准源的相位检测器,产生正比于振荡输出信号和基准频率信号的相位差的输出;

把所述相位检测器输出连接到所述压控输入的环路滤波器,该环路滤波器包括:

连接到所述相位检测器的输出的第一旁路电容器;和

开关电容器;和

开关电路,用来交替地把所述开关电容器串连连接到第一旁路电容器和地,以便开关电容器在所述环路滤波器中起电阻性元件的作用。

另外,本发明还提供了一种减小锁相环中热噪声的方法,所述锁相环包括产生输出信号的压控振荡器和为所述压控振荡器产生压控输入的相位检测器,所述方法包括:

在相位检测器的输入和压控振荡器之间连接第一旁路电容;

交替地把开关电容器串连连接到第一旁路电容和地,以便开关电容器起电阻性元件的作用。

从下面的说明和附图中,将会了解本发明的其它特征和优点。

附图说明

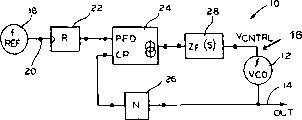

图1是锁相环电路的方块图;

图2是图1所示电路中的相位频率检测器和电荷泵电路的方块图;

图3是表示图1所示锁相环电路的一部分的方块图,包括现有技术环路滤波器电路的示意图;

图4是表示图1所示锁相环电路的一部分的方块图,包括根据本发明的环路滤波器电路的示意图;以及

图5是表示开关-电容电阻的频谱噪声电压密度的曲线。

具体实施方式

首先参考图1,锁相环电路10的典型实现可以用来在无线电接收器或发射器,如蜂窝电话中产生局部振荡器信号。该电路10包括压控振荡器(VCO)12,响应线16上的压控输入(VCNTRL)在线14上产生振荡输出信号。基准源18在线20上提供基准频率信号。线20上的基准频率信号通过第一分频器22耦合到相位检测器24的一个输入端。线14上的振荡输出信号通过第二分频器26连接到相位检测器24的第二输入。特别地,基准频率信号被基准分频比(division ratio)R所除。类似地,振荡输出信号被主分频比N所除。

相位检测器24提供一个输出信号,与其两个输入信号的相位差成比例。环路滤波器28把相位检测器的输出信号滤波,以便在线16上产生压控信号。

根据电路的实现,相位检测器24可以包括相位-频率检测器。在图解的本发明实施方案中,相位检测器24包括相位频率检测器30和电荷泵电路32的一种组合,如图2所示。

相位频率检测器32实现为一种数字电路,包括两个边沿触发的可复位的D型触发器34和36,其输入D连接逻辑“1”。从分频器22输出的标识为“REF”的基准信号作为第一触发器34的时钟信号。从分频器26输出的标识为“VCO”的振荡信号作为第二触发器36的时钟信号。第一触发器34的输出包括一个“UP”输出。第二触发器36的输出包括一个下或“DN”输出。触发器34和36的输出还被连接到与门38的输入端。与门38的输出连接到触发器34和36的复位输入端。

该脉冲-频率检测器30的运行如下:如果REF边沿先于VCO边沿到达,则REF将输出UP设为逻辑“1”,随后到达的VCO边沿将把输出UP复位回逻辑“0”。如果VCO边沿先于REF边沿到达,则输出DN被设为逻辑“1”,然后被随后到达的REF边沿复位到“0”。输出端UP和DN的逻辑“1”使能如下面将要叙述的电荷泵电路32,使得在电荷泵输出端产生正的或负的电流脉冲,用CPOUT标识。这些脉冲的宽度与REF和VCO信号的相位差成比例。

电荷泵电路32包括串连在电源和地之间的第一和第二电流基准源(lcp)40和42。第一电流源40由输出UP运行,第二电流源由输出DN运行。电流源40和42之间的连接传送电荷泵输出电流CPOUT。

图1所示锁相环电路10的目的是设置压控振荡器12的输出频率,实现用源18输出的基准信号锁相。在实现图1所示相位检测器24时,电荷泵输出端的电流脉冲需要被积分并转换为可作用于振荡器12的压控输入端的电压。该转换由环路滤波器28完成。除了起积分器的作用,环路滤波器28还决定反馈环路的稳定性。

参照图3,用现有技术环路滤波器电路44说明了图1所示锁相环电路10的一部分。环路滤波器44是网络,包括连接在电荷泵输出端和地之间,且与第二电容C2并联的串连电容C1和电阻R1。如所周知,如果第二电容C2的值为0,则环路滤波器44是二阶的,否则是三阶滤波器。

虽然电阻R1和环路滤波器44对稳定的环路动态特性是必要的,但它们也会引起各种不便。环路滤波器电阻R1在振荡器的压控输入端产生热噪声电压,从而以随机的方式调节VCO12的相位。对于小的频率,该环路滤波器的电阻噪声被大大削弱。随着频率增加,该电阻的相位噪声的影响也增加。对于小环路带宽中的大谐振灵敏度,环路滤波器R1对总体输出相位噪声的影响是显著的。特别地,在环路带宽的邻近区域,环路滤波器电阻R1在整个相位噪声中占优。

现有技术环路滤波器44还有一个缺陷,为锁相环电路10和压控振荡器12供电的电源电压随着时间的过去而减小。为了用可得到的VCO控制电压的较小的漂移保持相同的输出信号频率谐振范围,要求增加VCO12的谐振灵敏度。这样会降低可能达到的相位噪声。因此,要满足频率合成模块的较低电源电压实现的相位噪声要求会更加困难。

根据本发明,实现了环路滤波器中电阻的功能,而不会增加电阻增加的噪声量。这样就允许在降低相位噪声的同时,实现锁相环电路相同的动态特性。特别地,可以期望把该噪声影响降低到一个点,在该点处,环路中的其它噪声占优,且最终限制其性能。

参照图4,用根据本发明的环路滤波器46说明了图1所示锁相环电路1O的一部分。环路滤波器46如图3采用两个电容器C1(第一旁路电容)和C2(第二旁路电容),但电阻R1用开关-电容器等效电阻电路48代替。电路48包括一个电容器CR(开关电容)和一个开关电路50。

锁相环电路10的优选的应用是结合一种专用集成电路(ASIC)的应用一起使用。不过锁相环电路10也可以与其它应用一起使用。

对于大体上等效的开关-电容,可以假设电容C连接到源m×T的时间。根据Q=C×V,流入电容的电荷将会在电容上产生电压V。然后,电容器从源上断开,并且放电(1-m)×T的时间。因此,在时间T,从源传出电荷Q=C×V。因此,其平均电流为I=Q/T=V/(T/C),该装置实现了一个等效电阻值

R=T/C

为了使上述平均准确,采样频率fs=1/T必须显著高于由源发出的信号的频率。并且电容器在时间(1-m)×T的时间内必须能充分放电,否则,等效电阻将不等于R=T/C。等效电阻值不依赖于开关工作循环m。

上述的电阻实现只有在电路产生的噪声量低于如图3所示的常规电阻的噪声水平时才有用。在时间(1-m)×T期间,该电容器被短路,且其上的rms-噪声电压可以表示为v2 RMS=kT/C。在开关被触发将电容器连接到源的时刻,电容器端子上的瞬时噪声电压被采样,且在下一次循环开始之前不会改变。由于电容器在时间(1-m)×T期间必须充分放电,相对于电容器端子之间噪声频谱的带宽,采样频率fs不满足奈奎斯特(Nyquist)准则,并且会产生严重失真。因此,全部噪声功率就被折叠在频率范围-fs/2≤f≤fs/2之内,其频谱密度为kT/(fsC)。于是,被采样并保持(一段m×T时间)的噪声电压的频谱为(应用R=1/(fsC)):

图5表示等效10kΩ电阻的频谱噪声电压密度,fs=1MHz,m=0.5。

把电容CR连接到环路滤波器46的其余部分(rest)或地的开关电路50通过MOS晶体管形式的开关Q1和Q2实现。开关Q1和Q2由非重叠时钟发生器52控制,该时钟发生器52由一个信号源以频率fs和工作循环m驱动。开关控制的方式是第一晶体管Q1在时间m/fs内导通,第二晶体管Q2在时间(1-m)/fs内导通。如果选择开关频率fs远远高于锁相环电路10的环路带宽,且CR=1/(R1fs),则环路滤波器46等效于图3所示的环路滤波器44。

电容器C1连接在相位检测器输出端和晶体管Q1的集电极之间。第一晶体管Q1的发射极连接到第二晶体管Q2的集电极。第二晶体管Q2的发射极连接到地。电容器CR连接到晶体管Q1和Q2的接点和到地。晶体管Q1和Q2的基极连接到非重叠时钟发生器52。

与图3所示的环路滤波器44相比,公开的环路滤波器电路46产生远远低于总的相位噪声水平的等效电阻相位噪声影响。结果,其它噪声源在环路的噪声特性中占优。

虽然公开的是环路滤波器46利用相位频率检测器30和电荷泵32与数字锁相环电路连接,但是,如所明示,环路滤波器46还可以用于关于其它类型的相位检测器实施和锁相环电路。

这样,根据本发明提供了一种锁相环滤波器,带有开关-电容电阻,以改善由锁相环电路产生的输出信号的相位噪声特性。

Claims (15)

1.一种锁相环电路,包括:

响应压控输入产生振荡输出信号的压控振荡器;

提供基准频率信号的基准源;

工作上连接到所述压控振荡器和所述基准源的相位检测器,产生正比于振荡输出信号和基准频率信号的相位差的输出;

把所述相位检测器输出连接到所述压控输入的环路滤波器,该环路滤波器包括:

连接到所述相位检测器的输出的第一旁路电容器;和

开关电容器;和

开关电路,用来交替地把所述开关电容器串连连接到第一旁路电容器和地,以便开关电容器在所述环路滤波器中起电阻性元件的作用。

2.权利要求1的锁相环电路,其中所述环路滤波器还包括连接在相位检测器输出和地之间的第二旁路电容器。

3.权利要求1的锁相环电路,其中所述开关电路包括将所述开关电容器连接到所述第一旁路电容器的第一晶体管和将所述开关电容器连接到地的第二晶体管。

4.权利要求3的锁相环电路,其中所述开关电路还包括一个非重叠时钟发生器电路,用来控制第一和第二晶体管;

5.权利要求4的锁相环电路,其中所述非重叠时钟发生器电路工作在所述锁相环电路的一个环路带宽之上的频率上。

6.权利要求1的锁相环电路,其中所述相位检测器包括一相位频率检测器。

7.权利要求1的锁相环电路,其中所述相位检测器包括一个电荷泵电路,且所述环路滤波器将该电荷泵电路发出的电流脉冲转换为压控输入端的电压。

8.权利要求7的锁相环电路,其中所述相位检测器包括一对边沿触发的可复位的触发器,且振荡输出信号和基准频率信号是所述触发器的时钟信号,且所述触发器驱动所述电荷泵电路。

9.权利要求1的锁相环电路,还包括把所述振荡输出信号和基准频率信号连接到所述相位检测器的分频器。

10.权利要求1的锁相环电路,其中相位检测器的输出包括一系列脉冲,且其中环路滤波器起积分器的作用,将所述相位检测器的脉冲输出转换为压控输入。

11.一种减少锁相环中热噪声的方法,所述锁相环包括产生输出信号的压控振荡器和为所述压控振荡器产生压控输入的相位检测器,所述方法包括:

在相位检测器的输入和压控振荡器之间连接第一旁路电容;

交替地把开关电容器串连连接到第一旁路电容和地,以便开关电容器起电阻性元件的作用。

12.权利要求11的方法,其中交替地把开关电容器串连连接到第一旁路电容和地包括:

在第一切换阶段闭合第一开关,把所述开关电容器串连连接到旁路电容器;和

在第二切换阶段闭合第二开关,把所述开关电容器连接到地。

13.权利要求12的方法,其中所述第一和第二切换阶段不重叠。

14.权利要求13的方法,其中所述第一和第二开关的切换频率比锁相环的环路带宽大。

15.权利要求11的方法,其中相位检测器的输出包括一系列脉冲,还包括把相位检测器的输出积分的步骤。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/410,308 US6420917B1 (en) | 1999-10-01 | 1999-10-01 | PLL loop filter with switched-capacitor resistor |

| US09/410308 | 1999-10-01 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1377521A CN1377521A (zh) | 2002-10-30 |

| CN1183677C true CN1183677C (zh) | 2005-01-05 |

Family

ID=23624165

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN00813738.2A Expired - Fee Related CN1183677C (zh) | 1999-10-01 | 2000-09-21 | 带开关-电容电阻的pll环路滤波器 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US6420917B1 (zh) |

| EP (1) | EP1216508B1 (zh) |

| JP (1) | JP2003517755A (zh) |

| CN (1) | CN1183677C (zh) |

| AT (1) | ATE284092T1 (zh) |

| AU (1) | AU4027301A (zh) |

| DE (1) | DE60016432T2 (zh) |

| WO (1) | WO2001026230A1 (zh) |

Families Citing this family (45)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FI108688B (fi) * | 2000-06-30 | 2002-02-28 | Nokia Corp | Menetelmä ja järjestely taajuuden asettamiseksi |

| US7043206B2 (en) * | 2001-10-26 | 2006-05-09 | International Business Machines Corporation | Fully integrated offset compensation feedback circuit |

| GB2384123A (en) * | 2002-01-11 | 2003-07-16 | Zarlink Semiconductor Inc | Resampling filter for analog PLL |

| GB0228611D0 (en) * | 2002-12-07 | 2003-01-15 | Ibm | Semiconductor type two phase locked loop filter |

| JP4220843B2 (ja) * | 2003-06-27 | 2009-02-04 | パナソニック株式会社 | 低域ろ波回路およびフィードバックシステム |

| US6980060B2 (en) * | 2003-10-23 | 2005-12-27 | International Business Machines Corporation | Adaptive method and apparatus to control loop bandwidth of a phase lock loop |

| US7277518B2 (en) * | 2003-11-20 | 2007-10-02 | Avago Technologies General Ip (Singapore) Pte. Ltd. | Low-jitter charge-pump phase-locked loop |

| US7459964B2 (en) * | 2004-03-26 | 2008-12-02 | Panasonic Corporation | Switched capacitor filter and feedback system |

| US7002418B2 (en) * | 2004-05-07 | 2006-02-21 | Lattice Semiconductor Corporation | Control signal generation for a low jitter switched-capacitor frequency synthesizer |

| EP2259664B1 (en) | 2004-07-21 | 2017-10-18 | Mevion Medical Systems, Inc. | A programmable radio frequency waveform generator for a synchrocyclotron |

| US7145400B2 (en) * | 2004-12-02 | 2006-12-05 | Ceva Services Limited | Phase locked loop with a switch capacitor resistor in the loop filter |

| JP2006295343A (ja) * | 2005-04-06 | 2006-10-26 | Matsushita Electric Ind Co Ltd | スイッチトキャパシタフィルタ及びフィードバックシステム |

| EP2389981A3 (en) | 2005-11-18 | 2012-03-07 | Still River Systems, Inc. | Charged particle radiation therapy |

| US7598816B2 (en) * | 2005-12-20 | 2009-10-06 | Stmicroelectronics Pvt. Ltd. | Phase lock loop circuit with delaying phase frequency comparson output signals |

| DE102006034581A1 (de) * | 2006-07-26 | 2008-01-31 | Infineon Technologies Ag | Filtervorrichtung |

| US7541850B1 (en) * | 2007-05-16 | 2009-06-02 | Pico Semiconductor, Inc. | PLL with low spurs |

| US7928785B2 (en) * | 2007-11-07 | 2011-04-19 | Samsung Electronics Co., Ltd. | Loop filter, phase-locked loop, and method of operating the loop filter |

| US8933650B2 (en) | 2007-11-30 | 2015-01-13 | Mevion Medical Systems, Inc. | Matching a resonant frequency of a resonant cavity to a frequency of an input voltage |

| CN103259536B (zh) * | 2012-02-20 | 2018-12-18 | 德克萨斯仪器股份有限公司 | 消除电荷泵锁相环路中环路滤波电阻器噪声的装置 |

| US8593188B2 (en) | 2012-02-20 | 2013-11-26 | Texas Instruments Incorporated | Apparatus to remove the loop filter resistor noise in charge-pump PLL |

| CN102611430B (zh) * | 2012-03-29 | 2013-12-18 | 广州市广晟微电子有限公司 | 一种电压控制的等效电阻电路和一种滤波电路 |

| CN102751964B (zh) * | 2012-07-30 | 2015-02-11 | 无锡中科微电子工业技术研究院有限责任公司 | 一种可变阶数全集成环路滤波器 |

| US9681531B2 (en) | 2012-09-28 | 2017-06-13 | Mevion Medical Systems, Inc. | Control system for a particle accelerator |

| US10254739B2 (en) | 2012-09-28 | 2019-04-09 | Mevion Medical Systems, Inc. | Coil positioning system |

| CN104812444B (zh) | 2012-09-28 | 2017-11-21 | 梅维昂医疗系统股份有限公司 | 粒子束的能量调节 |

| TW201438787A (zh) | 2012-09-28 | 2014-10-16 | Mevion Medical Systems Inc | 控制粒子治療 |

| CN104813749B (zh) | 2012-09-28 | 2019-07-02 | 梅维昂医疗系统股份有限公司 | 控制粒子束的强度 |

| JP6254600B2 (ja) | 2012-09-28 | 2017-12-27 | メビオン・メディカル・システムズ・インコーポレーテッド | 粒子加速器 |

| TW201422279A (zh) | 2012-09-28 | 2014-06-16 | Mevion Medical Systems Inc | 聚焦粒子束 |

| TW201433331A (zh) | 2012-09-28 | 2014-09-01 | Mevion Medical Systems Inc | 線圈位置調整 |

| US9622335B2 (en) | 2012-09-28 | 2017-04-11 | Mevion Medical Systems, Inc. | Magnetic field regenerator |

| US9024684B2 (en) | 2013-03-15 | 2015-05-05 | Qualcomm Incorporated | Area-efficient PLL with a low-noise low-power loop filter |

| US8791656B1 (en) | 2013-05-31 | 2014-07-29 | Mevion Medical Systems, Inc. | Active return system |

| US9730308B2 (en) | 2013-06-12 | 2017-08-08 | Mevion Medical Systems, Inc. | Particle accelerator that produces charged particles having variable energies |

| CN110237447B (zh) | 2013-09-27 | 2021-11-02 | 梅维昂医疗系统股份有限公司 | 粒子治疗系统 |

| US10675487B2 (en) | 2013-12-20 | 2020-06-09 | Mevion Medical Systems, Inc. | Energy degrader enabling high-speed energy switching |

| US9962560B2 (en) | 2013-12-20 | 2018-05-08 | Mevion Medical Systems, Inc. | Collimator and energy degrader |

| US9661736B2 (en) | 2014-02-20 | 2017-05-23 | Mevion Medical Systems, Inc. | Scanning system for a particle therapy system |

| US9950194B2 (en) | 2014-09-09 | 2018-04-24 | Mevion Medical Systems, Inc. | Patient positioning system |

| US10786689B2 (en) | 2015-11-10 | 2020-09-29 | Mevion Medical Systems, Inc. | Adaptive aperture |

| US10925147B2 (en) | 2016-07-08 | 2021-02-16 | Mevion Medical Systems, Inc. | Treatment planning |

| US11103730B2 (en) | 2017-02-23 | 2021-08-31 | Mevion Medical Systems, Inc. | Automated treatment in particle therapy |

| EP3645111A1 (en) | 2017-06-30 | 2020-05-06 | Mevion Medical Systems, Inc. | Configurable collimator controlled using linear motors |

| KR102622304B1 (ko) * | 2019-01-03 | 2024-01-09 | 에스케이하이닉스 주식회사 | 클록 발생기 및 이를 포함하는 이미지 센서 |

| WO2020185544A1 (en) | 2019-03-08 | 2020-09-17 | Mevion Medical Systems, Inc. | Delivery of radiation by column and generating a treatment plan therefor |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5883423A (ja) * | 1981-02-21 | 1983-05-19 | Shinsaku Mori | スイツチド・キヤパシタ回路 |

| JPS59127426A (ja) * | 1983-01-12 | 1984-07-23 | Nec Corp | 位相同期ル−プ回路 |

| JPS63227120A (ja) * | 1987-03-16 | 1988-09-21 | Matsushita Electric Ind Co Ltd | クロツク抽出回路 |

| JPH03163912A (ja) * | 1989-11-21 | 1991-07-15 | Mitsubishi Electric Corp | Pll周波数シンセサイザ回路 |

| US5055803A (en) * | 1990-12-14 | 1991-10-08 | Motorola, Inc. | Parameter tolerant PLL synthesizer |

| JPH06291644A (ja) * | 1993-04-07 | 1994-10-18 | Fujitsu General Ltd | Pll回路 |

| JPH09252249A (ja) * | 1996-03-15 | 1997-09-22 | Hitachi Ltd | Pll周波数シンセサイザ |

| US5774023A (en) * | 1997-04-30 | 1998-06-30 | Motorola, Inc. | Adaptive phase locked loop system with charge pump having dual current output |

| US5942949A (en) * | 1997-10-14 | 1999-08-24 | Lucent Technologies Inc. | Self-calibrating phase-lock loop with auto-trim operations for selecting an appropriate oscillator operating curve |

-

1999

- 1999-10-01 US US09/410,308 patent/US6420917B1/en not_active Expired - Lifetime

-

2000

- 2000-09-21 EP EP00963695A patent/EP1216508B1/en not_active Expired - Lifetime

- 2000-09-21 DE DE60016432T patent/DE60016432T2/de not_active Expired - Lifetime

- 2000-09-21 AT AT00963695T patent/ATE284092T1/de not_active IP Right Cessation

- 2000-09-21 WO PCT/US2000/025929 patent/WO2001026230A1/en active IP Right Grant

- 2000-09-21 JP JP2001529081A patent/JP2003517755A/ja active Pending

- 2000-09-21 AU AU40273/01A patent/AU4027301A/en not_active Abandoned

- 2000-09-21 CN CN00813738.2A patent/CN1183677C/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2003517755A (ja) | 2003-05-27 |

| WO2001026230A1 (en) | 2001-04-12 |

| EP1216508B1 (en) | 2004-12-01 |

| CN1377521A (zh) | 2002-10-30 |

| AU4027301A (en) | 2001-05-10 |

| ATE284092T1 (de) | 2004-12-15 |

| US6420917B1 (en) | 2002-07-16 |

| DE60016432D1 (de) | 2005-01-05 |

| EP1216508A1 (en) | 2002-06-26 |

| DE60016432T2 (de) | 2005-12-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1183677C (zh) | 带开关-电容电阻的pll环路滤波器 | |

| KR100358118B1 (ko) | 고속 동기를 갖는 위상동기루프 | |

| CN1481076A (zh) | 电荷泵锁相回路电路 | |

| CN101510777A (zh) | 相位同步电路和接收器 | |

| US20040247027A1 (en) | Clock generator circuit using phase modulation technology and method thereof | |

| JPWO2009057289A1 (ja) | スペクトラム拡散クロック発生装置 | |

| CN100407575C (zh) | 带有用于改善线性和最大化频率的传播延迟补偿的张弛振荡器 | |

| CN1883119A (zh) | 具有增强的信号稳定性的锁相环结构 | |

| CN1336728A (zh) | 高频振荡器 | |

| CN1856932A (zh) | 压控数字模拟振荡器和使用该振荡器的频率合成器 | |

| JP2013530641A (ja) | Pllにおけるドリフト補償の方法及び装置 | |

| US7421052B2 (en) | Oscillator frequency selection | |

| CN114785340A (zh) | 一种基于可编程电容阵列的频带锁相环 | |

| JP2842847B2 (ja) | Pllシンセサイザ回路 | |

| JP2858023B2 (ja) | サンプル・ホールド位相検波器及びその制御方法 | |

| CN1310430C (zh) | 锁相环电路 | |

| US10756739B1 (en) | Charge pump and active loop filter with shared unity gain buffer | |

| US6002302A (en) | Frequency generator | |

| JP2005236431A (ja) | 周波数シンセサイザー | |

| JPH06276090A (ja) | Pll回路 | |

| US7315601B2 (en) | Low-noise sigma-delta frequency synthesizer | |

| US20020011901A1 (en) | Fractional synthesizer comprising a phase jitter compensation | |

| CN116488644A (zh) | 一种全数字锁相环电路结构 | |

| CN114614816A (zh) | 一种能够实现快速锁定的锁相环 | |

| CN118041352A (zh) | 一种宽环路带宽的ii型亚采样锁相环电路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20050105 Termination date: 20180921 |