CN115769221A - 半导体装置及电子设备 - Google Patents

半导体装置及电子设备 Download PDFInfo

- Publication number

- CN115769221A CN115769221A CN202180043979.9A CN202180043979A CN115769221A CN 115769221 A CN115769221 A CN 115769221A CN 202180043979 A CN202180043979 A CN 202180043979A CN 115769221 A CN115769221 A CN 115769221A

- Authority

- CN

- China

- Prior art keywords

- circuit

- transistor

- terminal

- wiring

- switch

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 414

- 239000003990 capacitor Substances 0.000 claims abstract description 198

- 239000000758 substrate Substances 0.000 claims description 151

- 230000015572 biosynthetic process Effects 0.000 claims description 77

- 229910044991 metal oxide Inorganic materials 0.000 claims description 75

- 150000004706 metal oxides Chemical class 0.000 claims description 75

- 229910052710 silicon Inorganic materials 0.000 claims description 68

- 239000010703 silicon Substances 0.000 claims description 68

- 238000003860 storage Methods 0.000 abstract description 49

- 239000012212 insulator Substances 0.000 description 562

- 239000004020 conductor Substances 0.000 description 315

- 210000004027 cell Anatomy 0.000 description 257

- 235000006679 Mentha X verticillata Nutrition 0.000 description 183

- 235000002899 Mentha suaveolens Nutrition 0.000 description 183

- 235000001636 Mentha x rotundifolia Nutrition 0.000 description 183

- 230000006870 function Effects 0.000 description 154

- 239000010410 layer Substances 0.000 description 153

- 229910052760 oxygen Inorganic materials 0.000 description 136

- 239000001301 oxygen Substances 0.000 description 135

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 133

- 239000010408 film Substances 0.000 description 122

- 229910052739 hydrogen Inorganic materials 0.000 description 108

- 239000001257 hydrogen Substances 0.000 description 108

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 94

- 210000002569 neuron Anatomy 0.000 description 93

- 230000002829 reductive effect Effects 0.000 description 73

- 239000012535 impurity Substances 0.000 description 70

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 66

- 239000000463 material Substances 0.000 description 65

- 238000010586 diagram Methods 0.000 description 55

- 238000000034 method Methods 0.000 description 54

- 239000013078 crystal Substances 0.000 description 53

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 45

- 238000013528 artificial neural network Methods 0.000 description 40

- 230000004888 barrier function Effects 0.000 description 40

- 238000009792 diffusion process Methods 0.000 description 38

- 238000013473 artificial intelligence Methods 0.000 description 33

- 229910052782 aluminium Inorganic materials 0.000 description 29

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 29

- 229910052735 hafnium Inorganic materials 0.000 description 26

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 26

- 229910001868 water Inorganic materials 0.000 description 26

- 238000004519 manufacturing process Methods 0.000 description 25

- 238000012545 processing Methods 0.000 description 25

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 25

- 239000011701 zinc Substances 0.000 description 25

- 201000007224 Myeloproliferative neoplasm Diseases 0.000 description 24

- 229910052581 Si3N4 Inorganic materials 0.000 description 24

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 24

- 229910052814 silicon oxide Inorganic materials 0.000 description 23

- 229910052721 tungsten Inorganic materials 0.000 description 23

- 239000010937 tungsten Substances 0.000 description 23

- 125000004429 atom Chemical group 0.000 description 22

- 229910052751 metal Inorganic materials 0.000 description 22

- 229910052757 nitrogen Inorganic materials 0.000 description 22

- 239000000047 product Substances 0.000 description 22

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 22

- 230000007547 defect Effects 0.000 description 21

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 21

- 239000002184 metal Substances 0.000 description 18

- 230000008859 change Effects 0.000 description 17

- -1 polyethylene terephthalate Polymers 0.000 description 17

- 101100449952 Arabidopsis thaliana KOR gene Proteins 0.000 description 16

- 238000010438 heat treatment Methods 0.000 description 16

- 239000000203 mixture Substances 0.000 description 16

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 16

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 15

- 230000000694 effects Effects 0.000 description 15

- 229910052738 indium Inorganic materials 0.000 description 15

- 239000002356 single layer Substances 0.000 description 15

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 14

- 230000015556 catabolic process Effects 0.000 description 14

- 238000006243 chemical reaction Methods 0.000 description 14

- 230000004913 activation Effects 0.000 description 13

- 238000004364 calculation method Methods 0.000 description 13

- 239000011521 glass Substances 0.000 description 13

- 150000002431 hydrogen Chemical class 0.000 description 13

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 13

- 230000009467 reduction Effects 0.000 description 13

- 238000002441 X-ray diffraction Methods 0.000 description 12

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 12

- 238000006731 degradation reaction Methods 0.000 description 12

- 239000011159 matrix material Substances 0.000 description 12

- 150000004767 nitrides Chemical class 0.000 description 12

- 238000000231 atomic layer deposition Methods 0.000 description 11

- 239000000969 carrier Substances 0.000 description 11

- 230000014509 gene expression Effects 0.000 description 11

- 229910000449 hafnium oxide Inorganic materials 0.000 description 11

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 11

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 10

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 10

- 150000001875 compounds Chemical class 0.000 description 10

- 229910052733 gallium Inorganic materials 0.000 description 10

- 230000003071 parasitic effect Effects 0.000 description 10

- 230000008569 process Effects 0.000 description 10

- 102100038204 Large neutral amino acids transporter small subunit 1 Human genes 0.000 description 9

- MWUXSHHQAYIFBG-UHFFFAOYSA-N Nitric oxide Chemical compound O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 9

- 108091006232 SLC7A5 Proteins 0.000 description 9

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 9

- 229910052802 copper Inorganic materials 0.000 description 9

- 239000010949 copper Substances 0.000 description 9

- 230000005669 field effect Effects 0.000 description 9

- 238000012544 monitoring process Methods 0.000 description 9

- 229910052719 titanium Inorganic materials 0.000 description 9

- 239000010936 titanium Substances 0.000 description 9

- 229910052725 zinc Inorganic materials 0.000 description 9

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 8

- 102100038235 Large neutral amino acids transporter small subunit 2 Human genes 0.000 description 8

- 108091006238 SLC7A8 Proteins 0.000 description 8

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 8

- 229910052799 carbon Inorganic materials 0.000 description 8

- 238000002003 electron diffraction Methods 0.000 description 8

- 230000003647 oxidation Effects 0.000 description 8

- 238000007254 oxidation reaction Methods 0.000 description 8

- 238000010615 ring circuit Methods 0.000 description 8

- 229910052715 tantalum Inorganic materials 0.000 description 8

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 8

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 8

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 7

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 7

- 239000002041 carbon nanotube Substances 0.000 description 7

- 229910021393 carbon nanotube Inorganic materials 0.000 description 7

- 101150036359 clpB gene Proteins 0.000 description 7

- 239000011229 interlayer Substances 0.000 description 7

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 7

- 229910052750 molybdenum Inorganic materials 0.000 description 7

- 239000011733 molybdenum Substances 0.000 description 7

- 125000004430 oxygen atom Chemical group O* 0.000 description 7

- 229920003023 plastic Polymers 0.000 description 7

- 239000004033 plastic Substances 0.000 description 7

- 238000004544 sputter deposition Methods 0.000 description 7

- 239000000126 substance Substances 0.000 description 7

- 239000010409 thin film Substances 0.000 description 7

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 6

- 101150110971 CIN7 gene Proteins 0.000 description 6

- 101100286980 Daucus carota INV2 gene Proteins 0.000 description 6

- 229910002601 GaN Inorganic materials 0.000 description 6

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 6

- 101150110298 INV1 gene Proteins 0.000 description 6

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 6

- 101100397044 Xenopus laevis invs-a gene Proteins 0.000 description 6

- 101100397045 Xenopus laevis invs-b gene Proteins 0.000 description 6

- 229910052796 boron Inorganic materials 0.000 description 6

- 230000003247 decreasing effect Effects 0.000 description 6

- 230000005684 electric field Effects 0.000 description 6

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 6

- 229910003437 indium oxide Inorganic materials 0.000 description 6

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 6

- 229920006395 saturated elastomer Polymers 0.000 description 6

- 238000001228 spectrum Methods 0.000 description 6

- 229910052718 tin Inorganic materials 0.000 description 6

- 229910052727 yttrium Inorganic materials 0.000 description 6

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 6

- 101150075681 SCL1 gene Proteins 0.000 description 5

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 5

- 229910021417 amorphous silicon Inorganic materials 0.000 description 5

- 238000005229 chemical vapour deposition Methods 0.000 description 5

- 239000000470 constituent Substances 0.000 description 5

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 5

- 238000001514 detection method Methods 0.000 description 5

- 230000006866 deterioration Effects 0.000 description 5

- 230000020169 heat generation Effects 0.000 description 5

- 239000000395 magnesium oxide Substances 0.000 description 5

- 239000007769 metal material Substances 0.000 description 5

- 229910052759 nickel Inorganic materials 0.000 description 5

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 5

- 239000011800 void material Substances 0.000 description 5

- 229910001928 zirconium oxide Inorganic materials 0.000 description 5

- 101100508840 Daucus carota INV3 gene Proteins 0.000 description 4

- 229910052779 Neodymium Inorganic materials 0.000 description 4

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 4

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 4

- 230000009471 action Effects 0.000 description 4

- 229910052783 alkali metal Inorganic materials 0.000 description 4

- 150000001340 alkali metals Chemical class 0.000 description 4

- 150000001342 alkaline earth metals Chemical class 0.000 description 4

- 239000002585 base Substances 0.000 description 4

- 230000005540 biological transmission Effects 0.000 description 4

- 230000000295 complement effect Effects 0.000 description 4

- 238000010276 construction Methods 0.000 description 4

- 238000013527 convolutional neural network Methods 0.000 description 4

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 4

- 238000007599 discharging Methods 0.000 description 4

- 238000010894 electron beam technology Methods 0.000 description 4

- 238000002149 energy-dispersive X-ray emission spectroscopy Methods 0.000 description 4

- 238000000605 extraction Methods 0.000 description 4

- 239000011888 foil Substances 0.000 description 4

- 229910001195 gallium oxide Inorganic materials 0.000 description 4

- 239000007789 gas Substances 0.000 description 4

- 229910052732 germanium Inorganic materials 0.000 description 4

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 4

- 238000003384 imaging method Methods 0.000 description 4

- 230000010354 integration Effects 0.000 description 4

- 229910052742 iron Inorganic materials 0.000 description 4

- 229910052746 lanthanum Inorganic materials 0.000 description 4

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 4

- 229910052451 lead zirconate titanate Inorganic materials 0.000 description 4

- 239000012528 membrane Substances 0.000 description 4

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 4

- 239000002159 nanocrystal Substances 0.000 description 4

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 4

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 4

- 229920000728 polyester Polymers 0.000 description 4

- 229920000139 polyethylene terephthalate Polymers 0.000 description 4

- 239000005020 polyethylene terephthalate Substances 0.000 description 4

- 229920001721 polyimide Polymers 0.000 description 4

- 229920001343 polytetrafluoroethylene Polymers 0.000 description 4

- 239000004810 polytetrafluoroethylene Substances 0.000 description 4

- 229910001925 ruthenium oxide Inorganic materials 0.000 description 4

- WOCIAKWEIIZHES-UHFFFAOYSA-N ruthenium(iv) oxide Chemical compound O=[Ru]=O WOCIAKWEIIZHES-UHFFFAOYSA-N 0.000 description 4

- SBIBMFFZSBJNJF-UHFFFAOYSA-N selenium;zinc Chemical compound [Se]=[Zn] SBIBMFFZSBJNJF-UHFFFAOYSA-N 0.000 description 4

- 238000000926 separation method Methods 0.000 description 4

- 239000010935 stainless steel Substances 0.000 description 4

- 229910001220 stainless steel Inorganic materials 0.000 description 4

- 210000000225 synapse Anatomy 0.000 description 4

- 229910001936 tantalum oxide Inorganic materials 0.000 description 4

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 4

- 229910052726 zirconium Inorganic materials 0.000 description 4

- 229910052684 Cerium Inorganic materials 0.000 description 3

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 3

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 3

- 239000004642 Polyimide Substances 0.000 description 3

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 3

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 3

- 239000000956 alloy Substances 0.000 description 3

- 230000003321 amplification Effects 0.000 description 3

- 238000004458 analytical method Methods 0.000 description 3

- 239000004760 aramid Substances 0.000 description 3

- 229920003235 aromatic polyamide Polymers 0.000 description 3

- 229910052788 barium Inorganic materials 0.000 description 3

- 210000004556 brain Anatomy 0.000 description 3

- ZMIGMASIKSOYAM-UHFFFAOYSA-N cerium Chemical compound [Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce] ZMIGMASIKSOYAM-UHFFFAOYSA-N 0.000 description 3

- 238000013461 design Methods 0.000 description 3

- 229910001873 dinitrogen Inorganic materials 0.000 description 3

- 238000002524 electron diffraction data Methods 0.000 description 3

- 239000000835 fiber Substances 0.000 description 3

- 235000013305 food Nutrition 0.000 description 3

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 3

- 239000011261 inert gas Substances 0.000 description 3

- 239000011810 insulating material Substances 0.000 description 3

- 229910052749 magnesium Inorganic materials 0.000 description 3

- 239000011777 magnesium Substances 0.000 description 3

- AXZKOIWUVFPNLO-UHFFFAOYSA-N magnesium;oxygen(2-) Chemical compound [O-2].[Mg+2] AXZKOIWUVFPNLO-UHFFFAOYSA-N 0.000 description 3

- 238000005259 measurement Methods 0.000 description 3

- 230000004048 modification Effects 0.000 description 3

- 238000012986 modification Methods 0.000 description 3

- 230000001537 neural effect Effects 0.000 description 3

- 125000004433 nitrogen atom Chemical group N* 0.000 description 3

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 3

- 238000003199 nucleic acid amplification method Methods 0.000 description 3

- 230000001151 other effect Effects 0.000 description 3

- 230000001590 oxidative effect Effects 0.000 description 3

- 230000002093 peripheral effect Effects 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- 239000011574 phosphorus Substances 0.000 description 3

- 230000010287 polarization Effects 0.000 description 3

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 3

- 239000011347 resin Substances 0.000 description 3

- 229920005989 resin Polymers 0.000 description 3

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 3

- 238000004611 spectroscopical analysis Methods 0.000 description 3

- 238000012546 transfer Methods 0.000 description 3

- 229910001930 tungsten oxide Inorganic materials 0.000 description 3

- 229910052720 vanadium Inorganic materials 0.000 description 3

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 3

- 239000004925 Acrylic resin Substances 0.000 description 2

- 229920000178 Acrylic resin Polymers 0.000 description 2

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 2

- 101100182248 Caenorhabditis elegans lat-2 gene Proteins 0.000 description 2

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 2

- BPQQTUXANYXVAA-UHFFFAOYSA-N Orthosilicate Chemical compound [O-][Si]([O-])([O-])[O-] BPQQTUXANYXVAA-UHFFFAOYSA-N 0.000 description 2

- 229920012266 Poly(ether sulfone) PES Polymers 0.000 description 2

- 239000004952 Polyamide Substances 0.000 description 2

- 239000004743 Polypropylene Substances 0.000 description 2

- 229910002367 SrTiO Inorganic materials 0.000 description 2

- 238000004833 X-ray photoelectron spectroscopy Methods 0.000 description 2

- 229910007541 Zn O Inorganic materials 0.000 description 2

- 238000009825 accumulation Methods 0.000 description 2

- 230000003213 activating effect Effects 0.000 description 2

- 239000002313 adhesive film Substances 0.000 description 2

- 230000002411 adverse Effects 0.000 description 2

- 239000005407 aluminoborosilicate glass Substances 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 2

- 229910052790 beryllium Inorganic materials 0.000 description 2

- ATBAMAFKBVZNFJ-UHFFFAOYSA-N beryllium atom Chemical compound [Be] ATBAMAFKBVZNFJ-UHFFFAOYSA-N 0.000 description 2

- 229910052795 boron group element Inorganic materials 0.000 description 2

- 239000005388 borosilicate glass Substances 0.000 description 2

- 229910052800 carbon group element Inorganic materials 0.000 description 2

- 239000002131 composite material Substances 0.000 description 2

- 238000007906 compression Methods 0.000 description 2

- 230000006835 compression Effects 0.000 description 2

- 238000001816 cooling Methods 0.000 description 2

- 238000005520 cutting process Methods 0.000 description 2

- 230000001419 dependent effect Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 239000003822 epoxy resin Substances 0.000 description 2

- 239000000284 extract Substances 0.000 description 2

- 239000002657 fibrous material Substances 0.000 description 2

- 239000011737 fluorine Substances 0.000 description 2

- 229910052731 fluorine Inorganic materials 0.000 description 2

- 238000003780 insertion Methods 0.000 description 2

- 230000037431 insertion Effects 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- 238000002955 isolation Methods 0.000 description 2

- HFGPZNIAWCZYJU-UHFFFAOYSA-N lead zirconate titanate Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ti+4].[Zr+4].[Pb+2] HFGPZNIAWCZYJU-UHFFFAOYSA-N 0.000 description 2

- 238000002844 melting Methods 0.000 description 2

- 230000008018 melting Effects 0.000 description 2

- 229910021424 microcrystalline silicon Inorganic materials 0.000 description 2

- 239000012466 permeate Substances 0.000 description 2

- 239000012782 phase change material Substances 0.000 description 2

- 230000000704 physical effect Effects 0.000 description 2

- 229910052696 pnictogen Inorganic materials 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 229920002647 polyamide Polymers 0.000 description 2

- 229920000647 polyepoxide Polymers 0.000 description 2

- 239000011112 polyethylene naphthalate Substances 0.000 description 2

- 229920001155 polypropylene Polymers 0.000 description 2

- 239000004800 polyvinyl chloride Substances 0.000 description 2

- 229920000915 polyvinyl chloride Polymers 0.000 description 2

- 229920002620 polyvinyl fluoride Polymers 0.000 description 2

- 239000002243 precursor Substances 0.000 description 2

- 238000004549 pulsed laser deposition Methods 0.000 description 2

- 239000010453 quartz Substances 0.000 description 2

- 239000000376 reactant Substances 0.000 description 2

- 230000006798 recombination Effects 0.000 description 2

- 229910052707 ruthenium Inorganic materials 0.000 description 2

- 229910052594 sapphire Inorganic materials 0.000 description 2

- 239000010980 sapphire Substances 0.000 description 2

- 239000005361 soda-lime glass Substances 0.000 description 2

- 229910000679 solder Inorganic materials 0.000 description 2

- 230000003068 static effect Effects 0.000 description 2

- VEALVRVVWBQVSL-UHFFFAOYSA-N strontium titanate Chemical compound [Sr+2].[O-][Ti]([O-])=O VEALVRVVWBQVSL-UHFFFAOYSA-N 0.000 description 2

- 238000012916 structural analysis Methods 0.000 description 2

- 239000013589 supplement Substances 0.000 description 2

- 230000000946 synaptic effect Effects 0.000 description 2

- 229920003002 synthetic resin Polymers 0.000 description 2

- 239000000057 synthetic resin Substances 0.000 description 2

- GPPXJZIENCGNKB-UHFFFAOYSA-N vanadium Chemical compound [V]#[V] GPPXJZIENCGNKB-UHFFFAOYSA-N 0.000 description 2

- 239000011787 zinc oxide Substances 0.000 description 2

- 229910019311 (Ba,Sr)TiO Inorganic materials 0.000 description 1

- 244000025254 Cannabis sativa Species 0.000 description 1

- 235000012766 Cannabis sativa ssp. sativa var. sativa Nutrition 0.000 description 1

- 235000012765 Cannabis sativa ssp. sativa var. spontanea Nutrition 0.000 description 1

- 229920000298 Cellophane Polymers 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- 229920000742 Cotton Polymers 0.000 description 1

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 1

- 239000004593 Epoxy Substances 0.000 description 1

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 1

- 102100024032 Linker for activation of T-cells family member 1 Human genes 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- 241001465754 Metazoa Species 0.000 description 1

- 239000004677 Nylon Substances 0.000 description 1

- 229920000297 Rayon Polymers 0.000 description 1

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 1

- 229910020923 Sn-O Inorganic materials 0.000 description 1

- 229910003077 Ti−O Inorganic materials 0.000 description 1

- 241000838698 Togo Species 0.000 description 1

- 229910007604 Zn—Sn—O Inorganic materials 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 229920006221 acetate fiber Polymers 0.000 description 1

- 239000004480 active ingredient Substances 0.000 description 1

- MDPILPRLPQYEEN-UHFFFAOYSA-N aluminium arsenide Chemical compound [As]#[Al] MDPILPRLPQYEEN-UHFFFAOYSA-N 0.000 description 1

- 150000001450 anions Chemical class 0.000 description 1

- GPBUGPUPKAGMDK-UHFFFAOYSA-N azanylidynemolybdenum Chemical compound [Mo]#N GPBUGPUPKAGMDK-UHFFFAOYSA-N 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 229910000416 bismuth oxide Inorganic materials 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 235000009120 camo Nutrition 0.000 description 1

- 150000001768 cations Chemical class 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 235000005607 chanvre indien Nutrition 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 230000019771 cognition Effects 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 238000013144 data compression Methods 0.000 description 1

- 238000013135 deep learning Methods 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000003795 desorption Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- TYIXMATWDRGMPF-UHFFFAOYSA-N dibismuth;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Bi+3].[Bi+3] TYIXMATWDRGMPF-UHFFFAOYSA-N 0.000 description 1

- 239000003989 dielectric material Substances 0.000 description 1

- 229910001882 dioxygen Inorganic materials 0.000 description 1

- 229920001971 elastomer Polymers 0.000 description 1

- 230000005611 electricity Effects 0.000 description 1

- 239000003792 electrolyte Substances 0.000 description 1

- 239000004744 fabric Substances 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 239000000446 fuel Substances 0.000 description 1

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 1

- YBMRDBCBODYGJE-UHFFFAOYSA-N germanium oxide Inorganic materials O=[Ge]=O YBMRDBCBODYGJE-UHFFFAOYSA-N 0.000 description 1

- 238000005247 gettering Methods 0.000 description 1

- 125000005843 halogen group Chemical group 0.000 description 1

- 230000003862 health status Effects 0.000 description 1

- 239000011487 hemp Substances 0.000 description 1

- 238000002173 high-resolution transmission electron microscopy Methods 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 230000006698 induction Effects 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 238000005304 joining Methods 0.000 description 1

- WABPQHHGFIMREM-UHFFFAOYSA-N lead(0) Chemical compound [Pb] WABPQHHGFIMREM-UHFFFAOYSA-N 0.000 description 1

- 239000010985 leather Substances 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 238000013507 mapping Methods 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 238000001451 molecular beam epitaxy Methods 0.000 description 1

- VOVZXURTCKPRDQ-CQSZACIVSA-N n-[4-[chloro(difluoro)methoxy]phenyl]-6-[(3r)-3-hydroxypyrrolidin-1-yl]-5-(1h-pyrazol-5-yl)pyridine-3-carboxamide Chemical compound C1[C@H](O)CCN1C1=NC=C(C(=O)NC=2C=CC(OC(F)(F)Cl)=CC=2)C=C1C1=CC=NN1 VOVZXURTCKPRDQ-CQSZACIVSA-N 0.000 description 1

- 210000005036 nerve Anatomy 0.000 description 1

- 229910000484 niobium oxide Inorganic materials 0.000 description 1

- URLJKFSTXLNXLG-UHFFFAOYSA-N niobium(5+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Nb+5].[Nb+5] URLJKFSTXLNXLG-UHFFFAOYSA-N 0.000 description 1

- 238000005121 nitriding Methods 0.000 description 1

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 description 1

- 229920001778 nylon Polymers 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 210000004205 output neuron Anatomy 0.000 description 1

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 1

- PVADDRMAFCOOPC-UHFFFAOYSA-N oxogermanium Chemical compound [Ge]=O PVADDRMAFCOOPC-UHFFFAOYSA-N 0.000 description 1

- 238000004806 packaging method and process Methods 0.000 description 1

- 230000036961 partial effect Effects 0.000 description 1

- 101150033318 pcm2 gene Proteins 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- 230000035699 permeability Effects 0.000 description 1

- 239000011295 pitch Substances 0.000 description 1

- 229920002635 polyurethane Polymers 0.000 description 1

- 239000004814 polyurethane Substances 0.000 description 1

- 238000007639 printing Methods 0.000 description 1

- 230000001681 protective effect Effects 0.000 description 1

- 108090000623 proteins and genes Proteins 0.000 description 1

- 238000011002 quantification Methods 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 239000002964 rayon Substances 0.000 description 1

- 238000005215 recombination Methods 0.000 description 1

- 238000011084 recovery Methods 0.000 description 1

- 230000000306 recurrent effect Effects 0.000 description 1

- 229910052706 scandium Inorganic materials 0.000 description 1

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 1

- 230000008054 signal transmission Effects 0.000 description 1

- 229910052708 sodium Inorganic materials 0.000 description 1

- 239000011734 sodium Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000005477 sputtering target Methods 0.000 description 1

- 239000004575 stone Substances 0.000 description 1

- 229910052712 strontium Inorganic materials 0.000 description 1

- CIOAGBVUUVVLOB-UHFFFAOYSA-N strontium atom Chemical compound [Sr] CIOAGBVUUVVLOB-UHFFFAOYSA-N 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

- 229910052717 sulfur Inorganic materials 0.000 description 1

- 230000001502 supplementing effect Effects 0.000 description 1

- 238000005211 surface analysis Methods 0.000 description 1

- 229920002994 synthetic fiber Polymers 0.000 description 1

- 239000012209 synthetic fiber Substances 0.000 description 1

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 1

- 229910052723 transition metal Inorganic materials 0.000 description 1

- 150000003624 transition metals Chemical class 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

- 210000003462 vein Anatomy 0.000 description 1

- 238000005406 washing Methods 0.000 description 1

- 239000002023 wood Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5642—Sensing or reading circuits; Data output circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/06—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration

- H01L27/0688—Integrated circuits having a three-dimensional layout

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06G—ANALOGUE COMPUTERS

- G06G7/00—Devices in which the computing operation is performed by varying electric or magnetic quantities

- G06G7/48—Analogue computers for specific processes, systems or devices, e.g. simulators

- G06G7/60—Analogue computers for specific processes, systems or devices, e.g. simulators for living beings, e.g. their nervous systems ; for problems in the medical field

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/04—Architecture, e.g. interconnection topology

- G06N3/0464—Convolutional networks [CNN, ConvNet]

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/04—Architecture, e.g. interconnection topology

- G06N3/048—Activation functions

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/06—Physical realisation, i.e. hardware implementation of neural networks, neurons or parts of neurons

- G06N3/063—Physical realisation, i.e. hardware implementation of neural networks, neurons or parts of neurons using electronic means

- G06N3/065—Analogue means

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/54—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using elements simulating biological cells, e.g. neuron

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0408—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors

- G11C16/0441—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors comprising cells containing multiple floating gate devices, e.g. separate read-and-write FAMOS transistors with connected floating gates

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/06—Sense amplifiers; Associated circuits, e.g. timing or triggering circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8221—Three dimensional integrated circuits stacked in different levels

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/06—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration

- H01L27/0611—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration integrated circuits having a two-dimensional layout of components without a common active region

- H01L27/0617—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration integrated circuits having a two-dimensional layout of components without a common active region comprising components of the field-effect type

- H01L27/0629—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration integrated circuits having a two-dimensional layout of components without a common active region comprising components of the field-effect type in combination with diodes, or resistors, or capacitors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/08—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind

- H01L27/085—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only

- H01L27/088—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate

- H01L27/092—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate complementary MIS field-effect transistors

- H01L27/0922—Combination of complementary transistors having a different structure, e.g. stacked CMOS, high-voltage and low-voltage CMOS

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/403—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells with charge regeneration common to a multiplicity of memory cells, i.e. external refresh

- G11C11/404—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells with charge regeneration common to a multiplicity of memory cells, i.e. external refresh with one charge-transfer gate, e.g. MOS transistor, per cell

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/403—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells with charge regeneration common to a multiplicity of memory cells, i.e. external refresh

- G11C11/405—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells with charge regeneration common to a multiplicity of memory cells, i.e. external refresh with three charge-transfer gates, e.g. MOS transistors, per cell

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/4076—Timing circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/41—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming static cells with positive feedback, i.e. cells not needing refreshing or charge regeneration, e.g. bistable multivibrator or Schmitt trigger

- G11C11/413—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing, timing or power reduction

- G11C11/417—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing, timing or power reduction for memory cells of the field-effect type

- G11C11/419—Read-write [R-W] circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

- H01L27/1225—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer with semiconductor materials not belonging to the group IV of the periodic table, e.g. InGaZnO

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78645—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate

- H01L29/78648—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate arranged on opposing sides of the channel

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78696—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the structure of the channel, e.g. multichannel, transverse or longitudinal shape, length or width, doping structure, or the overlap or alignment between the channel and the gate, the source or the drain, or the contacting structure of the channel

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/08—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using semiconductor devices

- H03K19/0806—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using semiconductor devices using charge transfer devices (DTC, CCD)

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/033—Making the capacitor or connections thereto the capacitor extending over the transistor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/05—Making the transistor

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Theoretical Computer Science (AREA)

- Biomedical Technology (AREA)

- Health & Medical Sciences (AREA)

- General Health & Medical Sciences (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Life Sciences & Earth Sciences (AREA)

- Mathematical Physics (AREA)

- Biophysics (AREA)

- Molecular Biology (AREA)

- Neurology (AREA)

- Artificial Intelligence (AREA)

- Software Systems (AREA)

- General Engineering & Computer Science (AREA)

- Computing Systems (AREA)

- Evolutionary Computation (AREA)

- Data Mining & Analysis (AREA)

- Computational Linguistics (AREA)

- Neurosurgery (AREA)

- Physiology (AREA)

- Ceramic Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Thin Film Transistor (AREA)

Abstract

提供一种恢复劣化数据的半导体装置。该半导体装置包括第一电路、存储部及运算部,第一电路包括电流源及第一开关,存储部包括第一晶体管及第一电容,运算部包括第二晶体管。第一晶体管的第一端子与第一开关的控制端子电连接,第一开关的第一端子与电流源的输出端子电连接,第一开关的第二端子与第二晶体管的第一端子电连接。在恢复保持在运算部中的数据时,使第一晶体管处于开启状态,将保持在存储部中的数据通过第一晶体管供应给第一开关的控制端子。第一开关根据该数据成为开启状态或关闭状态,电流从电流源通过第二晶体管流过运算部,在运算部的保持部中补充电荷。

Description

技术领域

本发明的一个方式涉及一种半导体装置及电子设备。

本发明的一个方式不局限于上述技术领域。本说明书等所公开的发明的技术领域涉及一种物体、驱动方法或制造方法。此外,本发明的一个方式涉及一种工序(process)、机器(machine)、产品(manufacture)或者组合物(composition of matter)。因此,更具体地说,作为本说明书所公开的本发明的一个方式的技术领域的一个例子可以举出半导体装置、显示装置、液晶显示装置、发光装置、蓄电装置、摄像装置、存储装置、信号处理装置、处理器、电子设备、系统、它们的驱动方法、它们的制造方法或它们的检查方法。

背景技术

现在,以人脑结构为模型的集成电路的开发日益火热。该集成电路组装有作为脑子结构的电子电路且包括相当于人脑的“神经元”及“神经突触”的电路。因此,有时将上述集成电路称为“神经形性(neuro-morphic)”、“脑子形性(brain-morphic)”、“脑子激发(brain-inspire)”等。该集成电路具有非诺依曼型体系结构,与随着处理速度的增加功耗也变高的诺依曼型体系结构相比,可以期待以极低功耗进行并列处理。

包括“神经元”及“神经突触”的模仿神经网络的数据处理模型被称为人工神经网络(ANN)。例如,非专利文献1及非专利文献2公开了使用SRAM(Static Random AccessMemory;静态随机存取存储器)构成人工神经网络的运算装置。

[先行技术文献]

[非专利文献]

[非专利文献1]M.Kang et al.,”IEEE Journal Of Solid-State Circuits”,2018,Volume 53,No.2,p.642-655.

[非专利文献2]J.Zhang et al.,“IEEE Journal Of Solid-State Circuits”,2017,Volume 52,No.4,p.915-924.

发明内容

发明所要解决的技术问题

在人工神经网络中,进行将使两个神经元彼此结合的神经突触的结合强度(有时称为权系数)乘以在两个神经元间传送的信号的计算。尤其是,在分层人工神经网络中,需要将第一层的多个第一神经元的每一个与第二层的第二神经元中的一个之间的神经突触的结合强度分别乘以与从第一层的多个第一神经元的每一个向第二层的第二神经元中的一个输入的信号而将它们加在一起,就是说,需要进行结合强度和信号的积和运算。用于积和运算的该结合强度的个数及表示该信号的参数的个数根据人工神经网络的规模决定。此外,第二神经元使用突触的结合强度和第一神经元所输出的信号的积和运算的结果进行激活函数的运算,将该运算结果作为信号输出到第三层的第三神经元。换言之,在人工神经网络中,分层的数量、神经元的数量等越多,相当于“神经元”及“神经突触”的每一个的电路数量越多,从而运算量有时变庞大。由此,有时电路的功耗增大,来自电路的发热量也增大。

构成芯片的电路数量越多功耗越高,而且驱动装置时产生的发热量也越大。尤其是,发热量越大,对包括在芯片的电路元件的特性带来的影响越大,所以构成芯片的电路优选包括不容易受到温度影响的电路元件。此外,在包括在芯片的晶体管或电流源等的特性有偏差时运算结果也有偏差。

此外,在进行上述积和运算时,在进行乘法运算的电路(在本说明书中称为乘法单元)中需要保持权系数作为乘数(有时是被乘数)。因此,在乘法单元中设置保持权系数的电容等的存储元件,有时随着时间推移保持在存储元件中的数据劣化而权系数的值变化。由于保持在存储元件中的电荷减少导致数据劣化。电荷减少的原因例如是从存储元件流过的泄漏电流,作为泄漏电流的种类例如有晶体管等开关元件中关闭状态时流过的泄漏电流、电容元件中经过一对电极间的介电体流过的泄漏电流等。在晶体管等开关元件中关闭状态时流过的泄漏电流中,通过增大电容元件的电容值可以减少泄漏电流的影响。另一方面,在电容元件中经过一对电极间的介电体流过的泄漏电流中,由于即使增大电容元件的电容值一对电极的单位面积的泄漏电流量也不变,所以难以在整体上减少泄漏电流的影响。

因此,包括乘法单元的运算电路为了防止保持在乘法单元中的数据劣化需要增大电容元件的电容值以外的对策。作为该对策的一个例子,可以举出定期进行对乘法单元的存储元件的权系数的重新写入。或者,在包括乘法单元的运算电路中设置伪单元等,监视保持在该伪单元中的数据,该数据劣化时,进行对乘法单元的权系数的重新写入也是优选的。注意,在本说明书等中,数据的重新写入是指将与原来保持在单元中的数据相同的数据重新写入到该单元中的工作。此外,数据的重新写入也是指为了恢复数据对所保持的电荷量的绝对值变小的单元补充与原来保持的电荷相同的量的电荷的工作。

本发明的一个方式的目的之一是提供一种进行积和运算及/或函数运算的半导体装置等。此外,本发明的一个方式的目的之一是进行保持在乘法单元中的数据的重新写入的半导体装置。此外,本发明的一个方式的目的之一是提供一种保持数字值对该数字值进行数字模拟转换而进行模拟值的运算的半导体装置。另外,本发明的一个方式的目的之一是提供一种进行CNN(Convolutional Neural Network:卷积神经网络)等卷积处理的半导体装置等。此外,本发明的一个方式的目的之一是提供一种用于AI(ArtificialIntelligence:人工智能)的半导体装置等。另外,本发明的一个方式的目的之一是提供一种用于DNN(Deep Neural Network:深度神经网络)的半导体装置等。另外,本发明的一个方式的目的之一是提供一种功耗低的半导体装置等。另外,本发明的一个方式的目的之一是提供一种不容易受到环境温度的影响的半导体装置等。另外,本发明的一个方式的目的之一是提供一种不容易受到晶体管的特性不均匀的影响的半导体装置等。另外,本发明的一个方式的目的之一是提供一种不容易受到电流源的特性不均匀的影响的半导体装置等。另外,本发明的一个方式的目的之一是提供一种新颖的半导体装置等。

注意,本发明的一个方式的目的不局限于上述目的。上述目的并不妨碍其他目的的存在。其他目的是指将在下面的记载中描述的上述以外的目的。本领域技术人员可以从说明书或附图等的记载中导出并适当抽出上述以外的目的。本发明的一个方式实现上述目的及其他目的中的至少一个目的。此外,本发明的一个方式不一定需要实现所有的上述目的及其他目的。

解决技术问题的手段

(1)

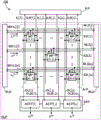

本发明的一个方式是一种半导体装置,包括:第一电路;第二电路;以及第三电路。第一电路包括电流源及第一开关,第二电路包括第一晶体管、第三晶体管、第四晶体管及第一电容,第三电路包括第二晶体管。第一晶体管的第一端子与第一开关的控制端子电连接,第一晶体管的第二端子与第四晶体管的第一端子电连接,第四晶体管的第二端子与第一电容的第一端子电连接,第四晶体管的栅极与第一电容的第二端子及第三晶体管的第一端子电连接,第一开关的第一端子与电流源的输出端子电连接,并且,第一开关的第二端子与第二晶体管的第一端子电连接。

(2)

本发明的一个方式在上述(1)中也可以具有包括锁存电路的第四电路的结构。第一晶体管的第一端子与第一开关的控制端子的电连接通过第四电路的第一端子与第一晶体管的第一端子电连接且第四电路的第二端子与第一开关的控制端子电连接来实现。

(3)

本发明的一个方式是一种半导体装置,包括:第一电路;第二电路;第三电路;以及读出放大器。第一电路包括电流源及第一开关,第二电路包括第一晶体管及第一电容,第三电路包括第二晶体管。第一晶体管的第一端子通过读出放大器与第一开关的控制端子电连接,第一晶体管的第二端子与第一电容的第一端子电连接,第一开关的第一端子与电流源的输出端子电连接,并且,第一开关的第二端子与第二晶体管的第一端子电连接。

(4)

本发明的一个方式在上述(1)至(3)中的任一个中也可以具有第一晶体管的栅极与第二晶体管的栅极电连接的结构。

(5)

本发明的一个方式是一种半导体装置,包括:第一电路;第二电路;以及第三电路。第一电路包括电流源及第一开关,第二电路包括第一晶体管、第三晶体管及第一电容,第三电路包括第二晶体管。第一晶体管的第一端子与第一开关的控制端子电连接,第三晶体管的第一端子与第一电容的第一端子及第一晶体管的栅极电连接,第一开关的第一端子与电流源的输出端子电连接,并且第一开关的第二端子与第二晶体管的第一端子电连接。

(6)

本发明的一个方式也可以具有包括锁存电路的第四电路。第一晶体管的第一端子与第一开关的控制端子的电连接通过第四电路的第一端子与第一晶体管的第一端子电连接且第四电路的第二端子与第一开关的控制端子电连接来实现。

(7)

本发明的一个方式在上述(5)或(6)中也可以具有第一电容的第二端子与第二晶体管的栅极电连接的结构。

(8)

本发明的一个方式在上述(1)至(7)中的任一个中也可以具有包括在第二电路中的晶体管在沟道形成区域中包含金属氧化物的结构。

(9)

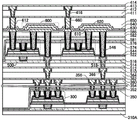

本发明的一个方式是一种半导体装置,包括:第一电路;以及第五电路。第一电路包括第一电流源、第二电流源、第一开关、第五晶体管及第六晶体管,第五电路包括第七晶体管、第八晶体管、第二电容、第二开关、第三开关及电流比较电路。优选的是,第一电流源的输出端子与第一开关的第一端子电连接,第二电流源的输出端子与第五晶体管的栅极、第六晶体管的栅极及第六晶体管的第一端子电连接。优选的是,第七晶体管的第一端子与第八晶体管的第一端子、第二开关的第一端子及第三开关的第一端子电连接,第七晶体管的栅极与第八晶体管的第二端子及第二电容的第一端子电连接。优选的是,第一开关的第二端子与第二开关的第二端子电连接,电流比较电路的第一端子与第三开关的第二端子电连接,并且,电流比较电路的第二端子与第五晶体管的第一端子电连接。

(10)

本发明的一个方式是一种半导体装置,包括:第一电路;以及第五电路,该半导体装置与上述(9)不同。第一电路包括第一电流源、第三电流源、第一开关及第四开关,第五电路包括第七晶体管、第八晶体管、第二电容、第二开关、第三开关、第五开关及电流比较电路。优选的是,第一电流源的输出端子与第一开关的第一端子电连接,第三电流源的输入端子与第四开关的第一端子电连接。优选的是,第七晶体管的第一端子与第八晶体管的第一端子、第二开关的第一端子及第三开关的第一端子电连接,第七晶体管的栅极与第八晶体管的第二端子及第二电容的第一端子电连接。优选的是,第一开关的第二端子与第二开关的第二端子电连接,第四开关的第二端子与第五开关的第一端子电连接。优选的是,电流比较电路的第一端子与第三开关的第二端子电连接,电流比较电路的第二端子与第五开关的第二端子电连接。

(11)

本发明的一个方式在上述(9)或(10)中也可以具有第七晶体管在沟道形成区域中包含硅且第八晶体管在沟道形成区域中包含金属氧化物的结构。

(12)

本发明的一个方式在上述(10)中也可以具有第五电路包括第九晶体管、第十晶体管、第三电容及第六开关的结构。优选的是,第九晶体管的第一端子与第十晶体管的第一端子、第二开关的第一端子及第六开关的第一端子电连接,第九晶体管的栅极与第十晶体管的第二端子及第三电容的第一端子电连接。优选的是,第六开关的第二端子与第五开关的第一端子及第四开关的第二端子电连接。优选的是,第八晶体管的栅极与第十晶体管的栅极不直接连接。

(13)

本发明的一个方式在上述(12)中也可以具有第七晶体管及第九晶体管都在沟道形成区域中包含硅且第八晶体管及第十晶体管都在沟道形成区域中包含金属氧化物的结构。

(14)

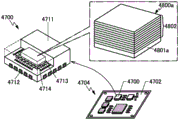

本发明的一个方式是一种包括上述(1)至(13)中的任一个的半导体装置以及外壳的电子设备。

在本说明书等中,半导体装置是指利用半导体特性的装置以及包括半导体元件(晶体管、二极管、光电二极管等)的电路及包括该电路的装置等。此外,半导体装置是指能够利用半导体特性而发挥作用的所有装置。例如,作为半导体装置的例子,有集成电路、具备集成电路的芯片、封装中容纳有芯片的电子构件。此外,有时存储装置、显示装置、发光装置、照明装置以及电子设备等本身是半导体装置,或者包括半导体装置。

此外,在本说明书等中,当记载为“X与Y连接”时,表示在本说明书等中公开了如下情况:X与Y电连接的情况;X与Y在功能上连接的情况;以及X与Y直接连接的情况。因此,不局限于附图或文中所示的连接关系,例如其他的连接关系也在附图或文中所记载的范围内记载。X和Y都是对象物(例如,装置、元件、电路、布线、电极、端子、导电膜、层等)。

作为X和Y电连接的情况的一个例子,可以在X和Y之间连接一个以上的能够电连接X和Y的元件(例如开关、晶体管、电容器、电感器、电阻器、二极管、显示器件、发光器件、负载等)。此外,开关具有控制开启或关闭的功能。换言之,通过使开关处于导通状态(开启状态)或非导通状态(关闭状态)来控制是否使电流流过。

作为X与Y在功能上连接的情况的一个例子,例如可以在X与Y之间连接有一个以上的能够在功能上连接X与Y的电路(例如,逻辑电路(反相器、NAND电路、NOR电路等)、信号转换电路(数字模拟转换电路、模拟数字转换电路、伽马校正电路等)、电位电平转换电路(电源电路(升压电路、降压电路等)、改变信号的电位电平的电平转移电路等)、电压源、电流源、切换电路、放大电路(能够增大信号振幅或电流量等的电路、运算放大器、差分放大电路、源极跟随电路、缓冲电路等)、信号产生电路、存储电路、控制电路等)。注意,例如,即使在X与Y之间夹有其他电路,当从X输出的信号传送到Y时,就可以说X与Y在功能上是连接着的。

此外,当明确地记载为“X与Y电连接”时,包括如下情况:X与Y电连接的情况(换言之,以中间夹有其他元件或其他电路的方式连接X与Y的情况);以及X与Y直接连接的情况(换言之,以中间不夹有其他元件或其他电路的方式连接X与Y的情况)。

例如,可以表现为“X、Y、晶体管的源极(或第一端子等)与晶体管的漏极(或第二端子等)互相电连接,X、晶体管的源极(或第一端子等)、晶体管的漏极(或第二端子等)与Y依次电连接”。或者,可以表现为“晶体管的源极(或第一端子等)与X电连接,晶体管的漏极(或第二端子等)与Y电连接,X、晶体管的源极(或第一端子等)、晶体管的漏极(或第二端子等)与Y依次电连接”。或者,可以表达为“X通过晶体管的源极(或第一端子等)及晶体管的漏极(或第二端子等)与Y电连接,X、晶体管的源极(或第一端子等)、晶体管的漏极(或第二端子等)、Y依次设置”。通过使用与这种例子相同的表达方法规定电路结构中的连接顺序,可以区分晶体管的源极(或第一端子等)与漏极(或第二端子等)而决定技术范围。注意,这种表达方法是一个例子,不局限于上述表达方法。在此,X和Y为对象物(例如,装置、元件、电路、布线、电极、端子、导电膜、层等)。

此外,即使在电路图上独立的构成要素彼此电连接,也有时一个构成要素兼有多个构成要素的功能。例如,在布线的一部分用作电极时,一个导电膜兼有布线和电极的两个构成要素的功能。因此,本说明书中的“电连接”的范畴内还包括这种一个导电膜兼有多个构成要素的功能的情况。

在本说明书等中,“电阻元件”例如包括具有高于0Ω的电阻值的电路元件、高于0Ω的布线等。因此,在本说明书等中,“电阻元件”包括具有电阻值的布线、电流流过源极和漏极之间的晶体管、二极管、线圈等。因此,“电阻元件”也可以称为“电阻”、“负载”、“具有电阻值的区域”等,与此相反,“电阻”、“负载”、“具有电阻值的区域”也可以称为“电阻元件”等。作为电阻值,例如优选为1mΩ以上且10Ω以下,更优选为5mΩ以上且5Ω以下,进一步优选为10mΩ以上且1Ω以下。此外,例如也可以为1Ω以上且1×109Ω以下。

在本说明书等中,“电容元件”例如包括具有高于0F的静电电容值的电路元件、具有高于0F的静电电容值的布线的区域、寄生电容、晶体管的栅极电容等。因此,在本说明书等中,“电容元件”包括具有一对电极及在该电极之间的介电体的电路元件等。此外,“电容元件”、“寄生电容”、“栅极电容”等也可以称为“电容”等,与此相反,“电容”也可以称为“电容元件”、“寄生电容”、“栅极电容”等。此外,“电容”的“一对电极”也可以称为“一对导电体”、“一对导电区域”、“一对区域”等。静电电容值例如可以为0.05fF以上且10pF以下。此外,例如,也可以为1pF以上且10μF以下。

在本说明书等中,晶体管包括栅极、源极以及漏极这三个端子。栅极用作控制晶体管的导通状态的控制端子。用作源极或漏极的两个端子是晶体管的输入输出端子。根据晶体管的导电型(n沟道型、p沟道型)及对晶体管的三个端子施加的电位的高低,两个输入输出端子中的一方用作源极而另一方用作漏极。因此,在本说明书等中,源极和漏极可以相互调换。在本说明书等中,在说明晶体管的连接关系时,使用“源极和漏极中的一个”(第一电极或第一端子)、“源极和漏极中的另一个”(第二电极或第二端子)的表述。此外,根据晶体管的结构,有时除了上述三个端子以外还包括背栅极。在此情况下,在本说明书等中,有时将晶体管的栅极和背栅极中的一个称为第一栅极,将晶体管的栅极和背栅极的另一个称为第二栅极。并且,在相同晶体管中,有时可以将“栅极”与“背栅极”相互调换。此外,在晶体管包括三个以上的栅极时,在本说明书等中,有时将各栅极称为第一栅极、第二栅极、第三栅极等。

例如在本说明书等中,作为晶体管的一个例子可以采用具有两个以上的栅电极的多栅结构晶体管。当采用多栅结构时,由于将沟道形成区域串联连接,所以成为多个晶体管串联连接的结构。因此,通过采用多栅结构,可以降低关态电流(off-state current),且提高晶体管的耐压性(提高可靠性)。或者,通过利用多栅结构,当晶体管在饱和区域工作时,即便漏极-源极间的电压发生变化,漏极-源极间电流的变化也不太大,从而可以得到倾斜角平坦的电压-电流特性。当利用倾斜角平坦的电压-电流特性时,可以实现理想的电流源电路或电阻值极高的有源负载。其结果是,可以实现特性良好的差动电路或电流反射镜电路等。

此外,电路图示出一个电路元件的情况有时包括该电路元件具有多个电路元件的情况。例如,电路图示出一个电阻器的情况包括两个以上的电阻器串联连接的情况。此外,例如,电路图示出一个电容的情况包括两个以上的电容并联连接的情况。此外,例如,电路图示出一个晶体管的情况包括两个以上的晶体管串联连接且各晶体管的栅极彼此电连接的情况。同样,例如,电路图示出一个开关的情况包括该开关具有两个以上的晶体管,两个以上的晶体管串联电连接或者并联电连接并且各晶体管的栅极彼此电连接的情况。

此外,在本说明书等中,节点也可以根据电路结构或装置结构等称为端子、布线、电极、导电层、导电体或杂质区域等。此外,端子、布线等也可以称为节点。

此外,在本说明书等中,可以适当地调换“电压”和“电位”。“电压”是指与基准电位之间的电位差,例如在基准电位为地电位(接地电位)时,也可以将“电压”称为“电位”。接地电位不一定意味着0V。此外,电位是相对性的,根据基准电位的变化而供应到布线的电位、施加到电路等的电位、从电路等输出的电位等也产生变化。

此外,在本说明书等中,“高电平电位”、“低电平电位”不意味着特定的电位。例如,在两个布线都被记为“用作供应高电平电位的布线”的情况下,两个布线所供应的高电平电位也可以互不相同。同样,在两个布线都被记为“用作供应低电平电位的布线”的情况下,两个布线所供应的低电平电位也可以互不相同。

“电流”是指电荷的移动现象(导电),例如,“发生正带电体的导电”的记载可以替换为“在与其相反方向上发生负带电体的导电”的记载。因此,在本说明书等中,在没有特别的说明的情况下,“电流”是指载流子移动时的电荷的移动现象(导电)。在此,作为载流子可以举出电子、空穴、阴离子、阳离子、络离子等,载流子根据电流流过的系统(例如,半导体、金属、电解液、真空中等)不同。此外,布线等中的“电流的方向”是带正电的载流子移动的方向,以正电流量记载。换言之,带负电的载流子移动的方向与电流方向相反,以负电流量记载。因此,在本说明书等中,在没有特别的说明的情况下,关于电流的正负(或电流的方向),“电流从元件A向元件B流过”等记载可以替换为“电流从元件B向元件A流过”等记载。此外,“对元件A输入电流”等记载可以替换为“从元件A输出电流”等记载。

此外,在本说明书等中,“第一”、“第二”、“第三”等序数词是为了避免构成要素的混淆而附加上的。因此,该序数词不限制构成要素的个数。此外,该序数词不限制构成要素的顺序。此外,例如,本说明书等的实施方式之一中附有“第一”的构成要素有可能在其他的实施方式或权利要求书中附有“第二”的构成要素。此外,例如,在本说明书等中,一个实施方式中的“第一”所指的构成要素有可能在其他实施方式或权利要求书中被省略。

在本说明书中,为了方便起见,有时使用“上”、“下”等表示配置的词句以参照附图说明构成要素的位置关系。此外,构成要素的位置关系根据描述各构成要素的方向适当地改变。因此,不局限于说明书等中所说明的词句,根据情况可以适当地换词句。例如,在“位于导电体的顶面的绝缘体”的表述中,通过将所示的附图的方向旋转180度,也可以称为“位于导电体的下面的绝缘体”。

此外,“上”或“下”这样的术语不局限于构成要素的位置关系为“正上”或“正下”且直接接触的情况。例如,如果是“绝缘层A上的电极B”的表述,则不一定必须在绝缘层A上直接接触地形成有电极B,也可以包括在绝缘层A与电极B之间包括其他构成要素的情况。

此外,在本说明书等中,根据状况,可以互相调换“膜”和“层”等词句。例如,有时可以将“导电层”调换为“导电膜”。此外,有时可以将“绝缘膜”变换为“绝缘层”。此外,根据情况或状态,可以使用其他词句代替“膜”和“层”等词句。例如,有时可以将“导电层”或“导电膜”变换为“导电体”。此外,例如有时可以将“绝缘层”或“绝缘膜”变换为“绝缘体”。

注意,在本说明书等中,“电极”、“布线”、“端子”等的词句不在功能上限定其构成要素。例如,有时将“电极”用作“布线”的一部分,反之亦然。再者,“电极”、“布线”等还包括多个“电极”或“布线”被形成为一体的情况等。此外,例如,有时将“端子”用作“布线”或“电极”的一部分,反之亦然。再者,“端子”的词句包括多个“电极”、“布线”、“端子”等被形成为一体的情况等。因此,例如,“电极”可以为“布线”或“端子”的一部分,例如,“端子”可以为“布线”或“电极”的一部分。此外,“电极”、“布线”、“端子”等的词句有时置换为“区域”等的词句。

在本说明书等中,根据情况或状态,可以互相调换“布线”、“信号线”及“电源线”等词句。例如,有时可以将“布线”变换为“信号线”。此外,例如有时可以将“布线”变换为“电源线”。反之亦然,有时可以将“信号线”或“电源线”变换为“布线”。有时可以将“电源线”变换为“信号线”。反之亦然,有时可以将“信号线”变换为“电源线”。此外,根据情况或状态,可以互相将施加到布线的“电位”变换为“信号”。反之亦然,有时可以将“信号”变换为“电位”。

在本说明书等中,半导体的杂质是指构成半导体膜的主要成分之外的物质。例如,浓度低于0.1atomic%的元素是杂质。当包含杂质时,例如,半导体中的缺陷态密度有可能提高,载流子迁移率有可能降低或结晶性有可能降低。在半导体是氧化物半导体时,作为改变半导体特性的杂质,例如有第1族元素、第2族元素、第13族元素、第14族元素、第15族元素或主要成分之外的过渡金属等,尤其是,例如有氢(也包含于水中)、锂、钠、硅、硼、磷、碳、氮等。具体而言,当半导体是硅层时,作为改变半导体特性的杂质,例如有第1族元素、第2族元素、第13族元素、第15族元素等(有时不包含氧、氢)。