CN106409894B - 半导体器件及其制造方法 - Google Patents

半导体器件及其制造方法 Download PDFInfo

- Publication number

- CN106409894B CN106409894B CN201610404085.9A CN201610404085A CN106409894B CN 106409894 B CN106409894 B CN 106409894B CN 201610404085 A CN201610404085 A CN 201610404085A CN 106409894 B CN106409894 B CN 106409894B

- Authority

- CN

- China

- Prior art keywords

- region

- trench

- semiconductor

- semiconductor device

- insulating film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 260

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 64

- 238000000034 method Methods 0.000 title description 8

- 230000008878 coupling Effects 0.000 claims abstract description 65

- 238000010168 coupling process Methods 0.000 claims abstract description 65

- 238000005859 coupling reaction Methods 0.000 claims abstract description 65

- 239000011229 interlayer Substances 0.000 claims abstract description 29

- 230000000149 penetrating effect Effects 0.000 claims abstract description 8

- 239000000758 substrate Substances 0.000 claims description 55

- 238000005530 etching Methods 0.000 claims description 8

- 230000015556 catabolic process Effects 0.000 abstract description 9

- 238000012545 processing Methods 0.000 abstract description 6

- 239000010408 film Substances 0.000 description 153

- 230000003071 parasitic effect Effects 0.000 description 35

- 210000000746 body region Anatomy 0.000 description 32

- 239000010410 layer Substances 0.000 description 31

- 239000012535 impurity Substances 0.000 description 26

- 238000005468 ion implantation Methods 0.000 description 23

- 230000000903 blocking effect Effects 0.000 description 15

- 239000007789 gas Substances 0.000 description 13

- 238000001312 dry etching Methods 0.000 description 11

- 238000000206 photolithography Methods 0.000 description 10

- 238000002513 implantation Methods 0.000 description 9

- 238000004380 ashing Methods 0.000 description 8

- 230000015572 biosynthetic process Effects 0.000 description 8

- 150000002500 ions Chemical class 0.000 description 8

- 230000002265 prevention Effects 0.000 description 7

- NGVDGCNFYWLIFO-UHFFFAOYSA-N pyridoxal 5'-phosphate Chemical compound CC1=NC=C(COP(O)(O)=O)C(C=O)=C1O NGVDGCNFYWLIFO-UHFFFAOYSA-N 0.000 description 7

- 229910052751 metal Inorganic materials 0.000 description 6

- 239000002184 metal Substances 0.000 description 6

- 238000005229 chemical vapour deposition Methods 0.000 description 5

- 239000013256 coordination polymer Substances 0.000 description 5

- 238000002156 mixing Methods 0.000 description 5

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 4

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 4

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 4

- 229910052796 boron Inorganic materials 0.000 description 4

- 230000000052 comparative effect Effects 0.000 description 4

- 238000000605 extraction Methods 0.000 description 4

- 229910052698 phosphorus Inorganic materials 0.000 description 4

- 239000011574 phosphorus Substances 0.000 description 4

- 238000009751 slip forming Methods 0.000 description 4

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 3

- 230000004888 barrier function Effects 0.000 description 3

- 239000011248 coating agent Substances 0.000 description 3

- 238000000576 coating method Methods 0.000 description 3

- 238000006731 degradation reaction Methods 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- 239000000463 material Substances 0.000 description 3

- 239000005360 phosphosilicate glass Substances 0.000 description 3

- 230000008569 process Effects 0.000 description 3

- 229910052814 silicon oxide Inorganic materials 0.000 description 3

- 238000004544 sputter deposition Methods 0.000 description 3

- 239000004642 Polyimide Substances 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 239000005380 borophosphosilicate glass Substances 0.000 description 2

- 239000000470 constituent Substances 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000006872 improvement Effects 0.000 description 2

- 230000001788 irregular Effects 0.000 description 2

- 238000005224 laser annealing Methods 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 238000002161 passivation Methods 0.000 description 2

- 229920002120 photoresistant polymer Polymers 0.000 description 2

- 229920001721 polyimide Polymers 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- 229910015844 BCl3 Inorganic materials 0.000 description 1

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- 230000002159 abnormal effect Effects 0.000 description 1

- 239000002253 acid Substances 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 238000003486 chemical etching Methods 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 230000010485 coping Effects 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 238000000227 grinding Methods 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- 229910052756 noble gas Inorganic materials 0.000 description 1

- 150000002835 noble gases Chemical class 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 238000011160 research Methods 0.000 description 1

- 239000005368 silicate glass Substances 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- 239000000243 solution Substances 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/739—Transistor-type devices, i.e. able to continuously respond to applied control signals controlled by field-effect, e.g. bipolar static induction transistors [BSIT]

- H01L29/7393—Insulated gate bipolar mode transistors, i.e. IGBT; IGT; COMFET

- H01L29/7395—Vertical transistors, e.g. vertical IGBT

- H01L29/7396—Vertical transistors, e.g. vertical IGBT with a non planar surface, e.g. with a non planar gate or with a trench or recess or pillar in the surface of the emitter, base or collector region for improving current density or short circuiting the emitter and base regions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0607—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration

- H01L29/0611—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices

- H01L29/0615—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE]

- H01L29/0619—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE] with a supplementary region doped oppositely to or in rectifying contact with the semiconductor containing or contacting region, e.g. guard rings with PN or Schottky junction

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0684—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape, relative sizes or dispositions of the semiconductor regions or junctions between the regions

- H01L29/0692—Surface layout

- H01L29/0696—Surface layout of cellular field-effect devices, e.g. multicellular DMOS transistors or IGBTs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/402—Field plates

- H01L29/407—Recessed field plates, e.g. trench field plates, buried field plates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42372—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the conducting layer, e.g. the length, the sectional shape or the lay-out

- H01L29/4238—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the conducting layer, e.g. the length, the sectional shape or the lay-out characterised by the surface lay-out

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66234—Bipolar junction transistors [BJT]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66234—Bipolar junction transistors [BJT]

- H01L29/66325—Bipolar junction transistors [BJT] controlled by field-effect, e.g. insulated gate bipolar transistors [IGBT]

- H01L29/66333—Vertical insulated gate bipolar transistors

- H01L29/66348—Vertical insulated gate bipolar transistors with a recessed gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/73—Bipolar junction transistors

- H01L29/732—Vertical transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/739—Transistor-type devices, i.e. able to continuously respond to applied control signals controlled by field-effect, e.g. bipolar static induction transistors [BSIT]

- H01L29/7393—Insulated gate bipolar mode transistors, i.e. IGBT; IGT; COMFET

- H01L29/7395—Vertical transistors, e.g. vertical IGBT

- H01L29/7396—Vertical transistors, e.g. vertical IGBT with a non planar surface, e.g. with a non planar gate or with a trench or recess or pillar in the surface of the emitter, base or collector region for improving current density or short circuiting the emitter and base regions

- H01L29/7397—Vertical transistors, e.g. vertical IGBT with a non planar surface, e.g. with a non planar gate or with a trench or recess or pillar in the surface of the emitter, base or collector region for improving current density or short circuiting the emitter and base regions and a gate structure lying on a slanted or vertical surface or formed in a groove, e.g. trench gate IGBT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/10—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode not carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/1095—Body region, i.e. base region, of DMOS transistors or IGBTs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/402—Field plates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66234—Bipolar junction transistors [BJT]

- H01L29/66325—Bipolar junction transistors [BJT] controlled by field-effect, e.g. insulated gate bipolar transistors [IGBT]

- H01L29/66333—Vertical insulated gate bipolar transistors

- H01L29/6634—Vertical insulated gate bipolar transistors with a recess formed by etching in the source/emitter contact region

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Electrodes Of Semiconductors (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Abstract

本发明涉及一种半导体器件及其制造方法。半导体器件包括沟槽栅电极、将它们彼此耦合的发射极耦合部、布置在混合子单元区以及无源单元区中的层间绝缘膜,和穿透它的接触沟槽。而且,接触沟槽在混合子单元区与发射极耦合部的延伸方向的交叉区中被分割。而且,设置n+型发射极区以便与分割的接触沟槽的端部隔开。借助在交叉区中未形成接触沟槽的这种构造,可减小接触沟槽的加工失败。而且,因为设置n+型发射极区以便与接触沟槽的端部分开,因此可提高半导体器件的击穿电阻。

Description

相关申请交叉引用

将2015年6月10日提交的日本专利申请No.2015-117796,包括说明书、附图以及摘要的公开内容整体并入本文作为参考。

技术领域

本发明涉及一种半导体器件及其制造方法,且可特别适用于包括IE型IGBT的半导体器件。

背景技术

例如,在日本未审专利申请公布No.2013-140885中,公开了IE型沟槽栅IGBT,其包括具有线性有源单元区的第一线性单位单元区,具有线性空穴集电区的第二线性单位单元区,以及它们之间的线性无源单元区。

而且,在日本未审专利申请公布No.2013-258190中,公开了窄有源单元IE型IGBT,其具有二维变薄结构的有源单元且不具有用于接触的衬底沟槽。

发明内容

本发明人已经致力于包括如上所述的这种IE型IGBT的半导体器件的研究和研发,且已经对其特性改进进行了刻苦研究。特别地,相对于该半导体器件的构造来说,希望提高器件特性,同时还包括综合研究诸如相应部分的布局以及它们的工作精度的各种因素。

从本说明书以及附图的说明将使其他问题和新的特征变得清晰。

在本申请中公开的实施例之中,代表性实施例简要归纳如下。

本申请中公开的一个实施例中所示的半导体器件包括穿透p型体区并到达n-型漂移区的第一沟槽、布置为与第一沟槽隔开的第二沟槽、布置为与第二沟槽隔开的第三沟槽,以及布置在p型体区中且布置为接触第一沟槽的第一侧表面的n+型发射极区。而且,半导体器件包括通过第一绝缘膜布置在第一沟槽内部的第一栅电极、通过第二绝缘膜布置在第二沟槽内部的第二栅电极、通过第三绝缘膜布置在第二沟槽内部的第三栅电极,以及将第二栅电极和第三栅电极彼此耦合的耦合部。而且,半导体器件包括布置在作为第一沟槽和第二沟槽之间的第一区以及在第二沟槽和第三沟槽之间的第二区的无源单元区中的第四绝缘膜、穿透第四绝缘膜并与n+型发射极区接触的第一开口,以及通过第一开口与n+型发射极区耦合的第一电极。而且,第一区在第一方向上延伸,且耦合部在与第一方向交叉的第二方向上延伸。而且,第一开口在第一区与耦合部的延伸方向的交叉区中被分割,且第一开口在第一区中包括布置在交叉区的一侧的第一部以及布置在交叉区的另一侧的第二部。因此,第一开口未布置在交叉区中。

一种制造本申请中公开的一个实施例中所示的半导体器件的方法包括以下步骤:形成到达半导体衬底的中部的第一沟槽、布置为与第一沟槽隔开的第二沟槽,以及布置为与第二沟槽隔开的第三沟槽,且包括第一沟槽、第二沟槽以及第三沟槽内部地在半导体衬底上面经由栅极绝缘膜形成导电膜。而且,制造半导体器件的方法包括以下步骤:在作为第一沟槽和第二沟槽之间的第一区以及在第二沟槽和第三沟槽之间的第二区的无源单元区的第一主表面侧形成p型体区,以及在第一区的p型体区中形成n+型发射极区以便与第一沟槽中的第一绝缘膜接触。而且,制造半导体器件的方法包括以下步骤:在第一区和第二区上面形成层间绝缘膜,通过蚀刻层间绝缘膜形成与n+型发射极区接触的第一开口,以及通过包括第一开口内部地在层间绝缘膜上面形成导电膜而形成第一电极。而且,第一沟槽和第二沟槽形成为在第一方向上延伸,且耦合部形成为在与第一方向交叉的第二方向上延伸。而且,第一开口形成为在第一区与耦合部的延伸方向的交叉区中被分割,且形成为在第一区中包括布置在交叉区的一侧的第一部以及布置在交叉区的另一侧的第二部。换言之,第一开口未布置在交叉区中。

根据本申请中公开的下文示出的代表性实施例中所示的半导体器件,可提高半导体器件的特性。

根据制造本申请中公开的下文所示的代表性实施例中所示的半导体器件的方法,可制造具有优良特性的半导体器件。

附图说明

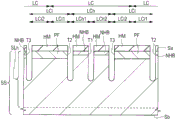

图1是示出第一实施例的半导体器件的构造的截面图。

图2是示出第一实施例的半导体器件的构造的平面图。

图3是示出第一实施例的半导体器件的构造的平面图。

图4是示出第一实施例的半导体器件(半导体芯片)的构造的平面图。

图5是示出第一实施例的半导体器件的构造的截面图。

图6是示出第一实施例的比较实例的半导体器件的构造的平面图。

图7是第一实施例的比较实例的半导体器件的制造步骤过程中的截面图。

图8A是用于解释寄生NPN双极晶体管的操作的电路图。

图8B是用于解释寄生NPN双极晶体管的操作的截面图。

图8C是可能形成寄生NPN双极晶体管的接触沟槽的端部的平面图。

图9是示出第一实施例的半导体器件的制造步骤的截面图。

图10是示出第一实施例的半导体器件的制造步骤的截面图且为示出图9之后的半导体器件的制造步骤的截面图。

图11是示出第一实施例的半导体器件的制造步骤的截面图且为示出图10之后的半导体器件的制造步骤的截面图。

图12是示出第一实施例的半导体器件的制造步骤的截面图且为示出图11之后的半导体器件的制造步骤的截面图。

图13是示出第一实施例的半导体器件的制造步骤的截面图且为示出图12之后的半导体器件的制造步骤的截面图。

图14是示出第一实施例的半导体器件的制造步骤的截面图且为示出图13之后的半导体器件的制造步骤的截面图。

图15是示出第一实施例的半导体器件的制造步骤的截面图且为示出图14之后的半导体器件的制造步骤的截面图。

图16是示出第一实施例的半导体器件的制造步骤的截面图且为示出图15之后的半导体器件的制造步骤的截面图。

图17是示出第一实施例的半导体器件的制造步骤的截面图且为示出图16之后的半导体器件的制造步骤的截面图。

图18是示出第一实施例的半导体器件的制造步骤的截面图且为示出图17之后的半导体器件的制造步骤的截面图。

图19是示出第一实施例的半导体器件的制造步骤的截面图且为示出图18之后的半导体器件的制造步骤的截面图。

图20是示出第一实施例的半导体器件的制造步骤的截面图且为示出图19之后的半导体器件的制造步骤的截面图。

图21是示出第一实施例的半导体器件的制造步骤的截面图(B-B)。

图22是示出第一实施例的半导体器件的制造步骤的截面图且为示出图20之后的半导体器件的制造步骤的截面图。

图23是示出第一实施例的半导体器件的制造步骤的截面图(B-B)且为示出图21之后的半导体器件的制造步骤的截面图。

图24是示出第一实施例的半导体器件的制造步骤的截面图且为示出图22之后的半导体器件的制造步骤的截面图。

图25是示出第一实施例的半导体器件的制造步骤的截面图(B-B)且为示出图23之后的半导体器件的制造步骤的截面图。

图26是示出第一实施例的半导体器件的制造步骤的截面图(C-C)。

图27是示出第一实施例的半导体器件的制造步骤的截面图(D-D)。

图28是示出第一实施例的半导体器件的制造步骤的截面图(E-E)。

图29是示出第一实施例的半导体器件的制造步骤的截面图且为示出图24之后的半导体器件的制造步骤的截面图。

图30是示出第一实施例的半导体器件的制造步骤的截面图且为示出图29之后的半导体器件的制造步骤的截面图。

图31是示出第一实施例的半导体器件的制造步骤的截面图(B-B)。

图32是示出第一实施例的半导体器件的制造步骤的截面图且为示出图30之后的半导体器件的制造步骤的截面图。

图33是示出第二实施例的半导体器件的构造的截面图。

图34是示出第二实施例的半导体器件的构造的平面图。

图35是示出第二实施例的半导体器件的构造的平面图。

图36是示出第二实施例的半导体器件的构造的截面图(B-B)。

图37是示出第二实施例的半导体器件的制造步骤的截面图。

具体实施方式

在以下的实施例中,当出于便利的需要时,虽然将说明分成多个部分或实施例,但是除了特别明确说明的情况之外,它们彼此并不无关,而是一个是另一个的一部分或整体的变型、应用实例、细节解释、补充解释等的关系。而且,在以下实施例中,当提及元件等的量(包括件数、数值、量、范围等)时,除了特别明确说明的情况,显然在原理上限于特定量的情况等之外,它们不限于特定量,且可以等于或大于且等于或小于特定量。

而且,在以下实施例中,除了特别明确说明的情况,被认为是显然在原理上不可或缺的情况等之外,其构成元素(也包括基本步骤等)不是必需的。以类似方式,在以下实施例中,当提及构成元素等的形状、位置关系等时,除了特别明确规定的情况,被认为显然在原理上不是这种情况的情况等之外,它们包含基本上近似或类似于其形状等的情况。这实际上也适用于上述量等(包括件数、数值、量、范围等)。

以下,将根据附图详细解释该实施例。而且,在用于解释该实施例的所有附图中,相同或相关联的参考符号指定具有相同功能的构件,且将省略其赘述。而且,当存在多个类似的构件(部分)时,存在将标志加入通用术语的参考符号以示出分立或特定部分的情况。此外,在以下实施例中,除非特别需要,否则原则上不再重复相同或相似部分的解释。

而且,在该实施例中采用的附图中,也存在即使在截面图中也省略阴影以便有助于附图理解的情况。而且,还存在即使在平面图中也出现阴影以便有助于附图理解的情况。

而且,在截面图和平面图中,存在各个部分的尺寸未对应于实际器件尺寸且特定部分示出为相当大以便有助于附图理解的情况。而且,即使截面图和平面图彼此对应时,也存在特定部分示出为相当大以便有助于附图截面的情况。

(第一实施例)

以下将参考附图详细解释本实施例的半导体器件。本实施例的半导体器件是IGBT(绝缘栅双极晶体管)。特别地,因为其施加在IGBT处于导通态时限制空穴(正空穴)放电至发射极电极侧(表面侧)且增加漂移区中积累的电荷的浓度的IE(注入增强)效应,因此其被称为IE型。而且,本实施例的半导体器件被称为EGE型(发射极-栅极-发射极型),因为设置在排列为以便彼此隔开的三个沟槽栅电极之中的中央的沟槽栅电极(TG1)与栅电极电耦合且设置在两端中的两个沟槽栅电极(TG2、TG3)中的每一个都与发射极电极电耦合。

[结构说明]

图1是示出本实施例的半导体器件的构造的截面图,且图2和图3是示出本实施例的半导体器件的构造的平面图。图1例如对应于图3的截面A-A。图3例如对应于由图2中的双点划线围绕的区域。图4是示出本实施例的半导体器件(半导体芯片)的构造的平面图。

将参考图1至图4说明本实施例的半导体器件的构造。

半导体衬底SS包括上表面(主表面)Sa以及在上表面Sa的相反侧的下表面(主表面)Sb。半导体衬底SS包括上表面Sa侧的n型的半导体层SLn,以及下表面Sb侧的半导体层SLp。

在半导体层SLn的下层部分中,形成n-型漂移区(n型半导体区)ND。在半导体层SLn和半导体层SLp之间,形成n型场停止区(n型半导体区)Ns。这种半导体层SLp对应于p+型集电区(p型半导体区)CL。在半导体衬底SS的下表面Sb中(p+型集电区CL下方)形成集电极电极CE。

在半导体层SLn的上层部分中,布置p型体区PB。在图1的中央部中,在半导体衬底SS的上表面Sa侧,形成沟槽(凹槽、凹槽部)T1。形成沟槽T1以便从上表面Sa穿透p型体区PB且到达半导体层SLn的中部。而且,沟槽T1形成为到达n-型漂移区ND。从这个沟槽T1的上表面观察的形状(将在下文称为平面形状)是在Y方向上具有长边的矩形(线形)。因此,沟槽T1在Y方向上延伸(图2、图3)。

在沟槽T1的内壁上形成栅极绝缘膜GI。在沟槽T1内部中,沟槽栅电极TG1形成在栅极绝缘膜GI上面以便填充沟槽T1(图1)。沟槽栅电极TG1与下述栅电极GE电耦合(参考图4)。而且,沟槽栅电极TG1在平面图中沿Y方向连续形成(图2、图3)。

另一方面,在沟槽T1的两侧,形成沟槽T2和T3以便以预定距离(Wh1、Wh2)隔开。

这里,从沟槽T2至沟槽T3的间隔是混合单元区LCh。在这些沟槽中,从沟槽T2至沟槽T1的间隔形成混合子单元区LCh1,且从沟槽T3至沟槽T1的间隔形成混合子单元区LCh2。因此,可以说沟槽T1是混合单元区LCh的中央部且位于混合子单元区LCh1以及混合子单元区LCh2的边界部中。混合子单元区LCh1在X方向上的宽度是Wh1,且混合子单元区LCh2在X方向上的宽度是Wh2。

而且,无源单元区LCi定位在混合单元区LCh的两侧。更具体地,如图2中所示设置多个混合单元区LCh,且无源单元区LCi设置在混合单元区LCh之间。而且,这些区域在Y方向上延伸。

因此,因为例如在图2中,通过无源单元区LCi重复设置混合单元区LCh,因此在混合单元区LCh的右侧,设置沟槽T2以便隔开无源单元区LCi的宽度(Wi)。而且,在图2中,在混合单元区LCh的左侧,设置沟槽T3以便隔开无源单元区LCi的宽度(Wi)。

而且,这里,单位单元区LC定义为包括混合单元区LCh、混合单元区LCh的一侧(图1中的左侧)的无源单元区LCi的一部分LCi1、以及另一侧(图1中的右侧)的无源单元区LCi的一部分LCi2的区域。部分LCi1是沟槽T2侧的无源单元区LCi的一半的部分。部分LCi2是沟槽T3侧的无源单元区LCi的一半的部分。因此,还可以说在图1中,单位单元区LC在X方向上多次重复设置。这里,更优选混合单元区LCh的宽度比无源单元区LCi的宽度Wi窄(图2)。换言之,更优选混合子单元区LCh1、LCh2的宽度小于无源单元区LCi的宽度Wi的一半。即,更优选混合子单元区LCh1、LCh2的宽度小于无源单元区LCi的部分LCi1、LCi2的宽度。

分别从上表面Sa到达半导体层SLn的中部的沟槽T2和T3设置在沟槽T1两侧,且在平面图中分别在Y方向上延伸。

在沟槽T2和T3中的每一个的内壁上面,形成栅极绝缘膜GI。在沟槽T2的内部中,沟槽栅电极TG2形成在栅极绝缘膜GI上面以便填充沟槽T2。在沟槽T3的内部中,沟槽栅电极TG3形成在栅极绝缘膜GI上面以便填充沟槽T3。沟槽栅电极TG2和TG3与发射极电极EE电耦合。而且,沟槽栅电极TG2和TG3中的每一个在平面图中沿Y方向连续形成。

在混合子单元区LCh1中,p型体区PB形成在沟槽T1和沟槽T2之间,且与形成在沟槽T1的内壁上面的栅极绝缘膜GI以及形成在沟槽T2的内壁上面的栅极绝缘膜GI接触。而且,在混合子单元区LCh2中,p型体区PB形成在沟槽T1和沟槽T3之间,且与形成在沟槽T1的内壁上面的栅极绝缘膜GI以及形成在沟槽T2的内壁上面的栅极绝缘膜GI接触。

而且,在混合子单元区LCh1和LCh2中的每一个中,在半导体衬底SS的上表面Sa侧,n+型发射极区NE仅形成在沟槽栅电极TG1侧。即,在混合子单元区LCh1中,n+型发射极区NE未形成在沟槽栅电极TG2侧,且在混合子单元区LCh2中,n+型发射极区NE未形成在沟槽栅电极TG3侧(图1)。

而且,如图2和图3中所示,n+型发射极区NE在Y方向上以预定距离(LCai)多次设置。因此,在混合子单元区LCh1和LCh2中的每一个中,还存在未形成n+型发射极区NE的区域(截面)。

而且,在混合子单元区LCh1中,n+型发射极区NE形成在沟槽T1和接触沟槽CT之间,且与p型体区PB以及形成在沟槽T1的内壁(沟槽T1的侧表面)上面的栅极绝缘膜GI接触。而且,在混合子单元区LCh2中,n+型发射极区NE形成在沟槽T1和接触沟槽CT之间,且与p型体区PB以及形成在沟槽T1的内壁上面的栅极绝缘膜GI接触。这种n+型发射极区NE的平面形状例如是矩形,在Y方向上的宽度是LCaa,且在X方向上的宽度对应于接触沟槽CT和沟槽T1之间的距离(图3)。

而且,混合子单元区LCh1的n+型发射极区NE与发射极电极EE电耦合,且混合子单元区LCh2的n+型发射极区NE与发射极电极EE电耦合。

在混合子单元区LCh1和LCh2中的每一个中,优选n型空穴阻挡区(n型半导体区)NHB形成在p型体区PB下面。在混合子单元区LCh1和LCh2中的每一个中,n型空穴阻挡区NHB的n型杂质浓度高于n-型漂移区ND的n型杂质浓度,且低于n+型发射极区NE的n型杂质浓度。

混合子单元区LCh1的n型空穴阻挡区NHB形成在沟槽T1和沟槽T2之间,且混合子单元区LCh2的n型空穴阻挡区NHB形成在沟槽T1和沟槽T3之间。

而且,混合子单元区LCh1的n型空穴阻挡区NHB可与p型体区PB、形成在沟槽T1的内壁上面的栅极绝缘膜GI以及形成在沟槽T2的内壁上面的栅极绝缘膜GI接触。而且,混合子单元区LCh2的n型空穴阻挡区NHB可与p型体区PB、形成在沟槽T1的内壁上面的栅极绝缘膜GI以及形成在沟槽T3的内壁上面的栅极绝缘膜GI接触。因此,因为n-型漂移区ND中积累的空穴难以释放至混合子单元区LCh1和LCh2中的发射极电极EE,因此可改善IE效应。

在混合单元区LCh的沟槽T2侧(图1-3中的左侧)的无源单元区LCi中,在半导体衬底SS的上表面Sa侧,p型浮置区(p型半导体区)PF布置在p型体区PB下方。这种p型浮置区PF布置在上述沟槽T2和附图中左端中的沟槽T3之间。而且,在附图中左端中的沟槽T3的内部,沟槽栅电极TG3形成在栅极绝缘膜GI上面以便填充沟槽T3。这些沟槽栅电极TG3中的每一个都在平面图中沿Y方向连续形成。

在混合单元区LCh的沟槽T3侧(图1-3中的右侧)的无源单元区LCi中,在半导体衬底SS的上表面Sa侧,p型浮置区(p型半导体区)PF布置在p型体区PB下方。这种p型浮置区PF布置在上述沟槽T3和附图中右端中的沟槽T2之间。而且,在附图中右端中的沟槽T2的内部,沟槽栅电极TG2形成在栅极绝缘膜GI上面以便填充沟槽T2。这种沟槽栅电极TG2在平面图中沿Y方向连续形成。

而且,在无源单元区LCi的两侧在Y方向上延伸的沟槽栅电极TG2和TG3通过在X方向上延伸的端部沟槽栅电极TGp而彼此电耦合。

而且,无源单元区LCi两侧的沟槽栅电极TG2和TG3通过在X方向上延伸的发射极耦合部TGx而彼此电耦合。发射极耦合部TGx例如由与沟槽栅电极TG2和TG3相同的材料形成。而且,发射极耦合部TGx通过形成在发射极耦合部TGx中的接触沟槽CT(参见图2、图3和图5)与发射极电极EE电耦合。借助这种结构,可在不依靠具有不必要的高成本的精细加工工艺的情况下提高沟槽栅电极TG2和TG3与发射极电极EE之间的电耦合的可靠性。

而且,在混合单元区LCh以及无源单元区LCi中,在半导体衬底SS的上表面Sa上面,形成层间绝缘膜IL(图1)。层间绝缘膜IL形成为覆盖混合子单元区LCh1和LCh2中的每一个中的p型体区PB。而且,在半导体衬底SS的上表面Sa以及层间绝缘膜IL之间,可形成绝缘膜IF。

在这种层间绝缘膜IL中,形成接触沟槽(开口)CT。接触沟槽(开口)CT形成为与n+型发射极区NE接触。

在这种接触沟槽CT的底表面上面,形成p+型体接触区(p型半导体区)PBC。而且,在p+型体接触区PBC下面,形成p+型闩锁防止区(p型半导体区)PLP。通过p+型体接触区PBC以及p+型闩锁防止区PLP形成p+型半导体区PR。

这种p+型体接触区PBC的p型杂质的浓度高于p+型闩锁防止区PLP的p型杂质的浓度。而且,p+型半导体区PR的p型杂质的浓度高于p型体区PB的p型杂质的浓度。

在接触沟槽CT的内部,形成耦合电极CP。这种耦合电极CP与n+型发射极区NE以及p+型半导体区PR接触。

而且,接触沟槽(开口)CT也形成在发射极耦合部TGx上面(参考图2、图3和图5)。

而且,在层间绝缘膜IL上面,布置由导电膜形成的发射极电极EE,且发射极电极EE通过接触沟槽CT与n+型发射极区NE以及p+型体接触区PBC耦合。在图1中所示的实例中,整体形成耦合电极CP以及发射极电极EE。而且,如上所述,发射极电极EE通过接触沟槽CT与发射极耦合部TGx耦合。因此,沟槽栅电极TG2和TG3通过上述发射极耦合部TGx与发射极电极EE电耦合。

在发射极电极EE上面,进一步形成例如由聚酰亚胺系有机绝缘膜等形成的绝缘膜(钝化膜)。

而且,如图2中所示,p型浮置区PFp布置在栅布线抽取区AR2中以便围绕单元形成区AR1。在图2中,p型浮置区PFp、PF是阴影区。而且,这种p型浮置区PFp通过作为暴露在接触沟槽CT的底表面中的部分的p+体接触区PBCp与发射极电极EE电耦合。

这里,在本实施例中,虽然与n+型发射极区NE接触的接触沟槽CT在Y方向上延伸,但是其例如不像沟槽栅电极TG1那样连续形成(图2、图3)。即,与n+型发射极区NE接触的接触沟槽CT被分割地设置。换言之,与n+型发射极区NE接触的接触沟槽CT包括设置在发射极耦合部TGx的一侧(图2、图3中的上侧)的第一部,以及设置在发射极耦合部TGx的另一侧(图2、图3中的下侧)的第二部。而且,换言之,与n+型发射极区NE接触的接触沟槽CT设置为回避混合单元区LCh与发射极耦合部TGx的延伸区的交叉区。即,与n+型发射极区NE接触的接触沟槽CT未设置在混合单元区LCh与发射极耦合部TGx的延伸区的交叉区中(图5)。图5是示出本实施例的半导体器件的构造的截面图。图5例如对应于图3的截面B-B。而且,混合单元区LCh与发射极耦合部TGx的延伸区的交叉区例如对应于由图2中的虚线围绕的区域。

因此,通过将与n+型发射极区NE接触的接触沟槽CT分割布置以避开混合单元区LCh与发射极耦合部TGx的延伸区的交叉区,可避免归因于由发射极耦合部TGx造成的不平坦而产生的加工失败。

图6是示出本实施例的比较实例的半导体器件的构造的平面图,且图7是本实施例的比较实例的半导体器件的制造步骤过程中的截面图。图7例如对应于图6的截面B-B。而且,图6的截面A-A类似于图1。

如图7中所示,在混合单元区LCh以及发射极耦合部TGx的延伸区的交叉区中,产生由发射极耦合部TGx造成的不平坦(台阶)。因此,如图7中所示,当与n+型发射极区NE接触的接触沟槽CT设置在混合单元区LCh与发射极耦合部TGx的延伸区的交叉区中时,需要在不平坦(台阶)上面形成接触沟槽CT。

在这种情况下,可能在抗蚀剂膜(光致抗蚀剂膜)R10的光刻时在不平坦(台阶)中发生光的不规则反射。通过这种光的不规则反射(也称为晕光),存在不能获得抗蚀剂膜R10的所需形状的曝光图案且曝光图案的形状变得异常的风险。而且,当异常形状的曝光图案被显影且作为形成接触沟槽CT的掩膜时,会发生接触沟槽CT的加工失败。

在这点上,根据本实施例,如上所述,通过将与n+型发射极区NE接触的接触沟槽CT分割设置以便避开混合单元区LCh以及发射极耦合部TGx的延伸区的交叉区,可避免归因于由发射极耦合部TGx造成的不平坦而产生的加工失败。

但是,当采用这种构造时,存在大的局部电流通过寄生NPN双极晶体管的操作而流动的风险。为了消除寄生NPN双极晶体管的这种操作的担心,优选设置n+型发射极区NE以便与接触沟槽CT的端部隔开。在本实施例中,如图3中所示,设置n+型发射极区NE以便与接触沟槽CT的端部隔开距离D1。换言之,设置n+型发射极区NE以便不包括接触沟槽CT的端部。

通过由此将n+型发射极区NE与接触沟槽CT的端部彼此分离,可抑制寄生NPN双极晶体管的操作且可提高半导体的特性。

当与n+型发射极区NE接触的接触沟槽CT未形成在混合单元区LCh与发射极耦合部TGx的延伸区的交叉区中时,堵塞了空穴从背表面释放的路径。因此,空穴通过高夹断电阻释放至正表面的发射极侧。此时,当n+型发射极区NE设置在空穴的释放路径中时,能在寄生NPN双极晶体管的发射极基极之间产生rbb'×空穴电流(Ih)部分的电压降且寄生NPN双极晶体管偏移至导通态。

将更具体进行解释。图8A是用于解释寄生NPN双极晶体管的操作的电路图,且图8B是用于解释寄生NPN双极晶体管的操作的截面图。图8C是可能形成寄生NPN双极晶体管的接触沟槽CT的端部的平面图。图8B例如对应于图3的截面E-E。而且,在图8B中,省略了高于层间绝缘膜IL的层。

图8A中所示的寄生NPN双极晶体管(NPN-Bip)利用p型体区PB的突起(沟道部CH)作为基极。寄生NPN双极晶体管的发射极侧与发射极电极EE耦合,且寄生NPN双极晶体管的集电极侧通过二极管与集电极电极CE耦合。在发射极电极EE和集电极电极CE之间,接触电阻器Rc以及pn耗尽层电容器Cpn串联耦合。这些耦合节点以及寄生NPN双极晶体管之间的电阻变成rbb'。

如图8B中所示,接触沟槽CT的端部(由虚线围绕的区域)是已经流过比较高的电阻rbb'的空穴电流Ih聚集的区域。在这个区域中,当n+型发射极区NE设置在纸表面背向方向上时,n+型发射极区NE设置在空穴的释放路径中,且形成寄生NPN双极晶体管。换言之,如图8C的(c1)-(c3)中所示,当设置n+型发射极区NE以便与接触沟槽CT的端部接触时,形成了寄生NPN双极晶体管,且寄生NPN双极晶体管可能变成导通态。

例如,当图8A和图8C中所示的空穴电流Ih大且电阻rbb'大时,从发射极-基极电压VBE=Ih×rbb'的关系,发射极-基极电压VBE变大。而且,当这种发射极-基极电压VBE超过约0.7V时,发射极基极之间的带隙正向偏置,且寄生NPN双极晶体管导通。因此,在其中寄生NPN双极晶体管操作已经发生的单位单元区LC中,不能由MOSFET的栅极偏压控制的大电流在施加漏电压的状态下流动。而且,当由大电流产生热时,这种正反馈会发生:电阻会通过温度上升而降低且更大的电流流动。因此,存在大电流局部流动且半导体器件最终损坏的风险。

另一方面,在本实施例中,如图3中所示,因为设置n+型发射极区NE以便与接触沟槽CT的端部分开距离D1,因此可避免上述寄生NPN双极晶体管的形成。因此,可抑制上述寄生NPN双极晶体管的导通操作,且可提高半导体器件的击穿耐力。

而且,优选n+型发射极区NE与接触沟槽CT的端部之间的距离D1为1μm或更大。通过使距离D1为1μm或更大,可使构造寄生NPN双极晶体管的PN之间的距离变大,且可进一步降低寄生NPN双极晶体管的形成及其操作的可能性。

而且,优选在接触沟槽CT之中,设置在发射极耦合部TGx的一侧(图2、图3中的上侧)的第一部与设置在发射极耦合部TGx的另一侧(图2、图3中的下侧)的第二部相对于发射极耦合部TGx对称设置(图2、图3中的垂直对称)。而且,优选分别设置n+型发射极区NE以便与相应端部分开相同的距离D1。

此外,如上所述,Y方向上的宽度为LCaa的n+型发射极区NE在Y方向上以预定距离(LCai)多次布置。此时,可以设计以便设置区与非设置区的比值为预定比值(1:a)。例如,对于这个比值来说,n+型发射极区NE可以预定距离(LCai)设置以便在发射极耦合部TGx的一侧(图2、图3中的上侧)与另一侧(图2、图3的下侧)彼此对称,同时确保n+型发射极区NE与接触沟槽CT的端部之间的距离D1。而且,n+型发射极区NE可以线形布置在发射极耦合部TGx的一侧(图2、图3中的上侧)与另一侧(图2、图3的下侧),同时实现a=0,即确保n+型发射极区NE与接触沟槽CT的端部之间的距离D1。

[制造方法说明]

以下将说明本实施例的半导体器件的制造步骤,且将使本实施例的半导体器件的结构更加清晰。

图9至图32是示出本实施例的半导体器件的制造步骤的截面图。

首先,如图9中所示,设置由例如引入诸如磷(P)的n型杂质的单晶硅形成的半导体衬底SS。半导体衬底SS包括作为第一主表面的上表面Sa以及作为第二主表面的、在上表面Sa相反侧的下表面Sb。

半导体衬底SS包含n型杂质。杂质浓度例如约为2×l014cm-3。在这个阶段,半导体衬底SS是被称为晶片的平坦且通常为圆形的半导体薄片。半导体衬底SS的厚度例如约为450μm-1,000μm。该半导体衬底SS从上表面Sa至预定深度的层成为半导体层SLn。

随后,在半导体衬底SS的上表面Sa上面的整个表面中,通过涂布等形成用于引入n型空穴阻挡区的抗蚀剂膜(光致抗蚀剂膜)R1且通过常规光刻(曝光和显影)将其图案化,且形成在混合单元区LCh中具有开口的抗蚀剂膜R1。通过例如利用该抗蚀剂膜R1作为掩膜,通过离子注入将n型杂质引入半导体衬底SS的上表面Sa,来形成n型空穴阻挡区NHB。对于这时的离子注入条件来说,例如其中离子种类是磷(P)、剂量约为6×l012cm-2且注入能量约为80KeV的离子注入条件可示例为优选条件。随后,通过灰化等移除已经变得不需要的抗蚀剂膜R1。

随后,如图10中所示,在半导体衬底SS的上表面Sa上面,通过涂布等形成用于引入p型浮置区的抗蚀剂膜R2且通过常规光刻将其图案化,且形成在无源单元区LCi中具有开口的抗蚀剂膜R2。通过例如利用该抗蚀剂膜R2作为掩膜,通过离子注入将p型杂质引入半导体衬底SS的上表面Sa,来形成p型浮置区PF。对于这时的离子注入条件来说,其中离子种类是硼(B)、剂量约为3.5×l013cm-2且注入能量约为75KeV的离子注入条件可示例为优选条件。随后,通过灰化等移除已经变得不需要的抗蚀剂膜R2。而且,当p型浮置区PF形成在单元形成区AR1中时(参考图2),p型浮置区PFp例如形成在栅布线抽取区AR2的最外部(参考图2)。

随后,如图11中所示,在半导体衬底SS的上表面Sa上面,例如通过CVD(化学气相沉积)方法等形成例如由氧化硅形成的硬掩膜HM。硬掩膜HM的厚度例如约为450nm。

随后,在半导体衬底SS的上表面Sa上面,通过涂布等形成用于加工硬掩膜的抗蚀剂膜R3且通过常规光刻将其图案化,且形成在沟槽(T1-T3)中具有开口的抗蚀剂膜R3。例如采用该抗蚀剂膜R3作为掩膜,通过干法蚀刻图案化硬掩膜HM。

随后,如图12中所示,通过灰化等移除已经不需要的抗蚀剂膜R3,且例如采用剩余的硬掩膜HM,通过各向异性干法蚀刻形成沟槽T1、T2以及T3(图13)。此时,形成沟槽T1,其从半导体衬底SS的上表面Sa到达半导体层SLn的中部且在平面图中在Y方向上延伸。而且,形成沟槽T2和T3,它们分别从半导体衬底SS的上表面Sa到达半导体层SLn的中部、设置在沟槽T1的两侧,且在平面图中在Y方向上相应延伸。对于用于这种各向异性干法蚀刻的气体来说,例如Cl2/O2系气体可示例为优选气体。

随后,如图14中所示,例如利用氟酸系蚀刻溶液等,通过湿法蚀刻移除已经变得不需要的硬掩膜HM。

随后,如图15中所示,执行用于p型浮置区PF以及n型空穴阻挡区NHB的拉伸扩散(例如约1,200℃,30分钟)。此时,执行拉伸扩散以便p型浮置区PF的下表面变得低于沟槽T1、T2以及T3的下表面。

因此,p型浮置区PF形成在图15中的左端的沟槽T3和与其相邻的沟槽T2之间,且p型浮置区PF形成在图15中的右端的沟槽T2和与其相邻的沟槽T3之间。优选p型浮置区PF分别与形成在沟槽T2的内壁上面的栅极绝缘膜GI以及形成在沟槽T3的内壁上面的栅极绝缘膜GI接触。

而且,n型空穴阻挡区NHB形成在沟槽T1和与其相邻的沟槽T2之间,以及沟槽T1和与其相邻的沟槽T3之间。优选形成在沟槽T1和沟槽T2之间的n型空穴阻挡区NHB与形成在沟槽T1的内壁上面的栅极绝缘膜GI以及形成在沟槽T2的内壁上面的栅极绝缘膜GI接触。而且,优选形成在沟槽T1和沟槽T3之间的n型空穴阻挡区NHB与形成在沟槽T1的内壁上面的栅极绝缘膜GI以及形成在沟槽T3的内壁上面的栅极绝缘膜GI接触。

而且,在n型半导体衬底SS之中,其中在拉伸扩散时未形成p型浮置区PF以及n型空穴阻挡区NHB的区域变成n-型漂移区ND。换言之,在n型半导体层SLn之中,其中未形成p型浮置区PF以及n型空穴阻挡区NHB的区域变成n-型漂移区ND。而且,在图15中所示的步骤中,n-型漂移区ND从半导体层SLn的内部形成至半导体衬底SS的下表面Sb。

在沟槽T1和沟槽T2之间,n型空穴阻挡区NHB的n型杂质浓度高于n-型漂移区ND的n型杂质浓度,且低于下述n+型发射极区NE的n型杂质浓度。而且,沟槽T1和沟槽T3之间的情况类似于沟槽T1和沟槽T2之间的情况。

随后,例如由氧化硅形成的栅极绝缘膜GI例如通过热氧化方法等形成在半导体衬底SS的上表面Sa上面以及各个沟槽T1、T2以及T3的内壁上面。栅极绝缘膜GI的厚度例如约为0.12μm。

随后,如图16中所示,由其中掺杂了磷(P)的多晶硅形成的导电膜CF例如通过CVD方法等形成在半导体衬底SS的上表面Sa上面以及沟槽T1、T2以及T3内部。导电膜CF的厚度例如约为0.6μm。

随后,如图17和图18中所示,例如通过干法蚀刻等图案化导电膜CF。至少覆盖发射极耦合部形成区的抗蚀剂膜(未示出)例如通过光刻形成,且利用该抗蚀剂膜作为掩膜图案化导电膜CF。此时,调整蚀刻条件(执行回蚀)以便导电膜CF保留在沟槽T1-T3内部。因此,形成由经由栅极绝缘膜GI嵌入沟槽T1内部的导电膜CF形成的沟槽栅电极TG1。而且,形成由经由栅极绝缘膜GI嵌入沟槽T2内部的导电膜CF形成的沟槽栅电极TG2。而且,形成由经由栅极绝缘膜GI嵌入沟槽T3内部的导电膜CF形成的沟槽栅电极TG3。而且,形成发射极耦合部TGx(参考图18、图2以及图3)。

换言之,沟槽栅电极TG1形成在栅极绝缘膜GI上面以便填充沟槽T1,沟槽栅电极TG2形成在栅极绝缘膜GI上面以便填充沟槽T2,且沟槽栅电极TG3形成在栅极绝缘膜GI上面以便填充沟槽T3。而且,形成在上面横跨沟槽栅电极TG2以及沟槽栅电极TG3的发射极耦合部TGx(参考图18、图2以及图3)。对于用于这种蚀刻的气体来说,例如SF6气体等可示例为优选气体。

随后,如图19中所示,通过干法蚀刻等移除除了沟槽T1、T2以及T3内部之外的栅极绝缘膜GI。

随后,如图20中所示,用于进行离子注入的、由相对薄的氧化硅膜(例如类似于栅极绝缘膜GI的程度)形成的绝缘膜CF例如通过热氧化方法或CVD形成在半导体衬底SS的上表面Sa上面。随后,用于引入p型体区的抗蚀剂膜(省略说明)通过常规光刻形成在半导体衬底SS的上表面Sa上面。通过例如采用用于引入p型体区的这种抗蚀剂膜作为掩膜,通过离子注入将p型杂质引入单元形成区AR1的整个表面以及其他所需部分而形成p型体区PB。

更具体地,与形成在沟槽T1内壁上面的栅极绝缘膜GI以及形成在沟槽T2内壁上面的栅极绝缘膜GI接触的p型体区PB形成在沟槽T1和沟槽T2之间。而且,与形成在沟槽T1内壁上面的栅极绝缘膜GI以及形成在沟槽T3内壁上面的栅极绝缘膜GI接触的p型体区PB形成在沟槽T1和沟槽T3之间。这种p型体区PB形成在n型空穴阻挡区NHB上面。而且,在无源单元区LCi中,这种p型体区PB形成在p型浮置区PF上面。

对于这时的离子注入条件来说,其中例如离子种类为硼(B)、剂量约为3×1013cm-2且注入能量约为75KeV的离子注入条件可示例为优选条件。随后,通过灰化等移除已经变得不需要的用于引入p型体区的抗蚀剂膜。

而且,用于引入n+型发射极区的抗蚀剂膜(未示出)通过常规光刻形成在半导体衬底SS的上表面Sa上面。通过例如采用用于引入n+型发射极区的这种抗蚀剂膜作为掩膜,通过离子注入,将n型杂质引入混合单元区LCh的p型体区PB的上层而形成n+型发射极区NE。对于这时的离子注入条件来说,其中例如离子种类为砷(As),剂量约为5×1015cm-2且注入能量约为80KeV的离子注入条件可示例为优选条件。

这种n+型发射极区NE仅形成在混合子单元区LCh1和LCh2中的沟槽栅电极TG1侧。更具体地,与形成在沟槽T1的内壁上面的栅极绝缘膜GI以及p型体区PB接触的n+型发射极区NE形成在沟槽T1和沟槽T2之间。而且,与形成在沟槽T1的内壁上面的栅极绝缘膜GI以及p型体区PB接触的n+型发射极区NE形成在沟槽T1和沟槽T3之间。

而且,如上所述,在Y方向上以预定距离(LCai)多次设置n+型发射极区NE(参考图2和图3)。而且,如上所述,设置n+型发射极区NE以便与接触沟槽CT的端部隔开距离D1(参考图3)。因此,n+型发射极区NE例如不会出现在图21等中所示的截面图(图3的截面B-B)中。

随后,通过灰化等移除已经变得不需要的用于引入n+型发射极区NE的抗蚀剂膜。

随后,如图22和图23中所示,例如由PSG(磷硅酸玻璃)形成的层间绝缘膜IL例如通过CVD方法等形成在半导体衬底SS的上表面Sa上面。形成层间绝缘膜IL以便经由绝缘膜IF覆盖p型体区PB。层间绝缘膜IL的厚度例如约为0.6μm。对于这种层间绝缘膜IL的材料,除了PSG膜之外,BPSG(硼磷硅酸玻璃)膜、NSG(非掺杂硅酸玻璃)膜、SOG(悬涂玻璃)膜或其复合膜等可示例为优选材料。

这里,当层间绝缘膜IL形成在半导体衬底SS的上表面Sa上面时,在图23中所示的截面中(图3的截面B-B),在层间绝缘膜IL的表面上出现不平坦(台阶)。更具体地,在无源单元区LCi中,耦合沟槽T2和沟槽T3的发射极耦合部TGx存在于层间绝缘膜IL的下层中。因此,在无源单元区LCi中的层间绝缘膜IL的表面与位于无源单元区LCi之间的混合单元区LCh的层间绝缘膜IL的表面之间产生高度差。具体地说,混合单元区LCh的层间绝缘膜IL的表面低于无源单元区LCi中的层间绝缘膜IL的表面。而且,当混合单元区LCh的宽度Wh窄于无源单元区LCi的宽度Wi时(参考图2),在混合单元区LCh中产生具有窄宽度的凹陷。

随后,如图24至图28,用于形成接触沟槽的抗蚀剂膜(省略说明)通过常规光刻形成在层间绝缘膜IL上面。随后,例如通过各向异性干法蚀刻等形成接触沟槽CT。更具体地,形成与n+型发射极区NE接触的接触沟槽CT以及在发射极耦合部TGx上面的接触沟槽CT(参考图3)。对于用于这种各向异性干法蚀刻的气体来说,例如Ar气、由CHF3气以及CF4气形成的气体混合物等可示例为优选气体。

图24至图28例如分别对应于图3的截面A-A、B-B、C-C、D-D以及E-E。如这些附图中所示,与n+型发射极区NE接触的接触沟槽CT没有出现在截面B-B和D-D中。更具体地,如参考图3解释的,在本实施例中,因为与n+型发射极区NE接触的接触沟槽CT分割设置以便避开混合单元区LCh与发射极耦合部TGx的延伸区的交叉区,因此该接触沟槽CT不出现在截面B-B和D-D中。

换言之,在上述交叉区中(例如图25中所示的截面B-B),不需要形成接触沟槽CT。因此,如参考图7解释的,可减少归因于层间绝缘膜IL的表面的不平坦(台阶)造成的接触沟槽CT的加工失败。

而且,如上所述,在Y方向上以预定距离(LCai)多次设置n+型发射极区NE(参考图2和图3)。另一方面,设置n+型发射极区NE以便与接触沟槽CT的端部隔开距离D1。换言之,设置n+型发射极区NE以便不包括接触沟槽CT的端部。

因此,例如在图26中(图3中所示的截面C-C),虽然形成了接触沟槽CT,但是不出现n+型发射极区NE。而且,在图28中所示的图3的截面E-E中,在接触沟槽CT的端部的纸面的背向方向上未设置n+型发射极区NE。因此,可避免参考图8解释的寄生NPN双极晶体管的形成。因此,可抑制由这种寄生NPN双极晶体管的导通操作可能造成的半导体器件的击穿,且可提高半导体器件的击穿耐性。

随后,通过灰化等移除已经变得不需要的用于形成接触沟槽的抗蚀剂膜。

随后,如图29中所示,例如通过经由接触沟槽CT的p型杂质的离子注入形成p+型体接触区PBC。这里,对于离子注入条件来说,其中例如离子种类为BF2、剂量约为5×1015cm-2且注入能量约为80KeV的离子注入条件可示例为优选条件。

以类似方式,例如通过经由接触沟槽CT的p型杂质的离子注入,形成p+型闩锁防止区PLP。这里,对于离子注入条件来说,其中例如离子种类为硼(B)、剂量约为3×1015cm-2且注入能量约为80KeV的离子注入条件可示例为优选条件。p+型体接触区PBC中的p型杂质的浓度高于p+型闩锁防止区PLP中p型杂质的浓度。而且,通过p+型体接触区PBC以及p+型闩锁防止区PLP形成p+型半导体区PR。多个p+型半导体区PR中的每一个中的p型杂质浓度都高于p型体区PB中的p型杂质浓度。

随后,如图30和图31中所示,形成发射极电极EE。具体地说,例如执行以下流程。首先,TiW膜例如通过溅射形成在半导体衬底SS的上表面Sa上面作为阻挡金属膜。TiW膜的厚度例如约为0.2μm。TiW膜中的钛的主要部分通过后续热处理移动至硅界面、形成硅化物,且有助于接触特性的改善,但是,因为其步骤复杂,因此在附图中未示出。

随后,例如在氮气气氛下执行约600℃以及约10分钟的硅化退火之后,例如通过溅射在阻挡金属膜上面的整个表面中形成铝系金属膜(例如添加几个%的硅,剩下为铝)以便填充接触沟槽CT。铝系金属膜的厚度例如约为5μm。

随后,通过常规光刻形成用于形成发射极电极的抗蚀剂膜(省略说明)。随后,例如通过干法蚀刻图案化由铝系金属膜以及阻挡金属膜形成的发射极电极EE。对于用于这种干法蚀刻的气体来说,例如Cl2/BCl3气体等可示例为优选气体。随后,通过灰化等移除已经变得不需要的用于形成发射极电极的抗蚀剂膜。

因此,在混合子单元区LCh1中,形成分别嵌入多个接触沟槽CT内部的多个耦合电极CP以及形成在层间绝缘膜IL上面的发射极电极EE。

发射极电极EE通过形成在混合子单元区中的多个耦合电极CP与形成在各个混合子单元区LChl和LCh2中的n+型发射极区NE以及多个p+型半导体区PR电耦合。而且,当形成发射极电极EE时,可形成与沟槽栅电极TG1电耦合的栅电极GE(参考图4)。

而且,当发射极电极EE形成在单元形成区AR1中时(参考图2),栅极布线GL以及栅电极GE(参考图4)可形成在栅极布线抽取区AR2中(参考图2)。

随后,如图32中所示,由例如具有聚酰亚胺的主要成分的有机膜等形成的绝缘膜(钝化膜)FPF形成在发射极电极EE上面。绝缘膜FPF的厚度例如约为2.5μm。

随后,通过常规光刻形成用于形成开口的抗蚀剂膜(省略说明)。随后,穿透绝缘膜FPF并到达发射极电极EE的开口OP1(参考图4)例如通过干法蚀刻以图案化绝缘膜FPF而形成,且形成由暴露于开口OP1的部分的发射极电极EE形成的发射极盘EP(参考图4)。而且,随后,通过灰化等移除已经变得不需要的用于形成开口的抗蚀剂膜。

而且,当绝缘膜FPF形成在单元形成区AR1中的发射极电极EE上面时(参考图4),绝缘膜FPF形成在栅极布线抽取区AR2(参考图4)中的栅电极GE(参考图4)上面,穿透绝缘膜FPF并到达栅电极GE的开口AR2(参考图4)形成在栅极布线抽取区AR2(参考图4)中,且形成由暴露于开口OP2的部分的栅电极GE形成的栅极盘GP。

随后,如图32中所示,通过使半导体衬底SS的下表面Sb经历背表面研磨处理,根据需要例如将约800μm的厚度减薄为例如约30μm-200μm。当击穿电压例如约为600V时,最终厚度约为70μm。因此,在这种已被制成薄膜的半导体衬底SS中,半导体层SLp形成在相对于半导体层SLn的下表面Sb侧的部分的半导体衬底SS内部。而且,根据需要也执行用于移除下表面Sb的损伤的化学蚀刻等。

在已被制成薄膜的这种半导体衬底SS之中,作为相对于其中形成n型场停止区Ns(参考图1)以及其中形成p+型集电极区CL(参考图1)的半导体层而位于下表面Sb侧的半导体层的半导体层制成半导体层SLp。

随后,如图1中所示,例如通过离子注入,通过将n型杂质引入半导体衬底SS的下表面Sb而形成n型场停止区Ns。这里,对于离子注入条件来说,例如其中离子种类为磷(P)、剂量约为7×1012cm-2且注入能量约为350KeV的离子注入条件可示例为优选条件。随后,根据需要对半导体衬底SS的下表面Sb执行激光退火等以活化杂质。

随后,例如通过离子注入,通过将p型杂质引入半导体衬底SS的下表面Sb而形成p+型集电极区CL。这里,对于离子注入条件来说,例如其中离子种类为硼(B)、剂量约为1×1013cm-2且注入能量约为40KeV的离子注入条件可示例为优选条件。随后,根据需要对半导体衬底SS的下表面Sb执行激光退火等以活化杂质。

即,在用于形成p+型集电极区CL的步骤中,p型半导体层SLp形成在相对于半导体层SLn位于下表面Sb侧的部分的半导体衬底SS中,且通过p型半导体层SLp形成p+型集电极区CL。

随后,作为与半导体层SLp,即p+型集电极区CL电耦合的集电极电极CE例如通过溅射形成在半导体衬底SS的下表面Sb上面。随后,半导体器件通过划片等分成半导体衬底SS的芯片区且根据需要密封进封装体中,且由此完成本实施例的半导体器件。

(第二实施例)

在第一实施例中,沟槽栅电极TG2、TG3的上表面的高度通常与沟槽栅电极TG1的上表面的高度相同,但是,沟槽栅电极TG2、TG3的上表面可低于沟槽栅电极TG1的上表面。

以下,将参考附图详细说明本实施例的半导体器件。本实施例的半导体器件是类似于第一实施例情况的IE型IGBT。而且,类似于第一实施例的情况,本实施例的半导体器件是EGE型(发射极-栅极-发射极型),其中在排列为以便彼此隔开的三个沟槽栅电极之中,设置在中央的沟槽栅电极(TG1)与栅电极电耦合且设置在两端的两个沟槽栅电极(TG2、TG3)中的每一个都与发射极电极电耦合。

[结构说明]

图33是示出本实施例的半导体器件的构造的截面图,且图34和图35是示出本实施例的半导体器件的构造的平面图。而且,在本实施例的半导体器件中,除了沟槽栅电极TG2、TG3之外的构造通常与第一实施例的情况相同。

如图33中所示,在本实施例中,虽然沟槽栅电极TG1、TG2分别嵌入形成在半导体衬底SS中的沟槽T2、T3的底部中,但是其上表面位于低于沟槽栅电极TG1的上表面的位置。而且,在沟槽栅电极TG1、TG2的上部以及沟槽T2、T3的内部,嵌入层间绝缘膜IL。

借助这种构造,即使在执行自收缩(self-shrink)时,也可避免归因于栅电容增大而造成的开启损耗退化,且可通过漏偏置结构的寄生PMOS晶体管的存在保持低噪声性能。

具体地说,在图33中所示的半导体器件中,寄生PMOS晶体管包括在其中。更具体地,形成寄生PMOS晶体管,其中p型浮置区PF作为源极,n-型漂移区ND以及n型空穴阻挡区NHB作为沟道,p+型闩锁防止区PLP以及p+型体接触区PBC作为漏极,且沟槽栅电极TG2、TG3作为栅极。

因此,在这种半导体器件中,当空穴注入p型浮置区PF时,寄生PMOS晶体管的源极的电势变高,且在寄生PMOS晶体管的栅极和源极之间产生负的电势差。因此,寄生PMOS晶体管导通,且注入p型浮置区PF的空穴释放至寄生PMOS晶体管的漏极。

如上所述,因为注入p型浮置区PF的空穴从p+型闩锁防止区PLP以及p+型体接触区PBC释放,因此存在开关操作时,在跃迁态中,过多空穴难以保持在p型浮置区PF中的特征。因此,因为可抑制跃迁态中的p型浮置区的不可控电势波动,因此半导体器件在低噪声性能方面是优良的(这类似于第一实施例(图1)的情况)。

但是,例如在第一实施例(图1)中所示的半导体器件中,当进行单元收缩时,虽然可降低栅极和集电极之间的电容(反馈电容),但是不能降低栅极和发射极之间的电容(输入电容)。栅极和集电极之间的电容主要影响关闭损耗。即,当不能降低栅极和发射极之间的电容时,会发生启动损耗退化。

因此,调整沟槽栅电极TG2、TG3的上表面的高度(从沟槽T2、T3的下端至上表面的距离)。更具体地,使沟槽栅电极TG2、TG3的上表面低于沟槽栅电极TG1的上表面,且低于p型体区PB的底表面。

因此,相对于沟槽栅电极TG2、TG3,因为可减小有助于输入电容的面积,因此可降低输入电容。

如上所述,即使执行单元收缩时,在避免归因于栅极电容(特别是栅极和发射极之间的电容(输入电容))的增大造成的开启损耗退化的同时,还能通过漏偏置结构的寄生PMOS晶体管的存在而保持低噪声性能。

在沟槽栅电极TG2、TG3中,其上表面低于沟槽栅电极TG1的上表面的部分例如是图34和图35的黑色区域。因此,除了沟槽栅电极TG2、TG3之外,也可降低端部沟槽栅电极TGp的上表面。

但是,如图35中所示,沟槽栅电极TG2、TG3通过在X方向上延伸的发射极耦合部TGx彼此电耦合。因此,在发射极耦合部TGx中,沟槽栅电极TG2、TG3中的每一个例如由嵌入沟槽T2、T3的上部的导电膜形成(图36)。图36是示出本实施例的半导体器件的构造的截面图。图36例如对应于图3的截面B-B。

而且,在本实施例中,类似于第一实施例的情况,与n+型发射极区NE接触的接触沟槽CT分割设置以便避开混合单元区LCh与发射极耦合部TGx的延伸区的交叉区(图34、图35)。借助这种构造,如第一实施例中详细解释的,可避免归因于发射极耦合部TGx造成的不平坦而导致的接触沟槽CT的加工失败。

而且,在本实施例中,类似于第一实施例的情况,设置n+型发射极区NE以便与接触沟槽CT的端部隔开距离D1(图34、图35)。借助这种构造,如第一实施例中详细说明的,可避免寄生NPN双极晶体管的形成,可抑制寄生NPN双极晶体管的导通操作,且可提高半导体器件的击穿耐性。

而且,也在本实施例中,优选n+型发射极区NE以及接触沟槽CT的端部之间的距离D1为1μm以上。

[制造方法的解释]

图37是示出本实施例的半导体器件的制造步骤的截面图。而且,本实施例的半导体器件的制造步骤基本上类似于第一实施例的情况,除了加入用于沟槽栅电极TG2、TG3的上表面的蚀刻步骤之外。

更具体地,在经过类似于图9-图16中所示的第一实施例的步骤之后,如图17和图18中所示,通过干法蚀刻等图案化沟槽T1、T2以及T3的内部及其上部的导电膜CF。因此,形成了经由栅极绝缘膜GI嵌入沟槽T1内部的导电膜CF形成的沟槽栅电极TG1以及发射极耦合部TGx(参考图2、图3)。此时,在沟槽T2内部,经由栅极绝缘膜GI嵌入导电膜CF直至其上部。而且,在沟槽T3内部,经由栅极绝缘膜GI嵌入导电膜CF直至其上部。

随后,如图37中所示,形成抗蚀剂膜(未示出),其包括沟槽栅电极TG2、TG3的形成区中的开口(即图34和图35的黑色区域),且利用这种抗蚀剂膜作为掩膜蚀刻导电膜CF。因此,移除了沟槽T2、T3内部的导电膜CF的上部,且可降低沟槽栅电极TG2、TG3的上表面。

随后,通过大致类似于图19-图32等中所示的第一实施例的步骤,完成本实施例的半导体器件。

而且,虽然对上述第一和第二实施例中说明的半导体器件应用的产品没有限制,但是这些半导体器件例如可应用于车载以及工业用途的半导体器件。对于车载以及工业用途的半导体器件来说,因为强调负载短路电阻,因此有效地采用上述实施例的半导体器件。而且,对于车载以及工业用途的半导体器件来说,因为需要反向偏压安全可操作性,因此有效地采用上述实施例的半导体器件。特别地,上述实施例的半导体器件在应用于供高压耐性以及应对大电流(例如600V或更大,100A或更大)应用的半导体器件时是有效的。

虽然已经基于实施例在上文具体说明了的本发明人提出的本发明,但是毋容质疑的是本发明不限于上述实施例,且在不背离其实质的范围内能进行各种改变。

Claims (16)

1.一种半导体器件,包括:

半导体衬底,所述半导体衬底包括第一主表面以及在所述第一主表面的相反侧的第二主表面;

第一导电类型的第一半导体区,所述第一半导体区布置在所述半导体衬底的所述第二主表面侧;

第二导电类型的第二半导体区,所述第二半导体区布置在所述半导体衬底的所述第一主表面侧并且在所述第一半导体区上方,所述第二导电类型与所述第一导电类型相反;

第一沟槽、布置为与所述第一沟槽隔开的第二沟槽、以及布置为与所述第二沟槽隔开的第三沟槽,所述第一沟槽、所述第二沟槽以及所述第三沟槽穿透所述第二半导体区并且到达所述第一半导体区;

所述第一导电类型的第三半导体区,所述第三半导体区布置在所述第二半导体区内部并且布置为与所述第一沟槽的第一侧表面接触;

第一栅电极,所述第一栅电极经由第一绝缘膜布置在所述第一沟槽内部;

第二栅电极,所述第二栅电极经由第二绝缘膜布置在所述第二沟槽内部;

第三栅电极,所述第三栅电极经由第三绝缘膜布置在所述第三沟槽内部;

耦合部,所述耦合部将所述第二栅电极和所述第三栅电极彼此耦合;

第四绝缘膜,所述第四绝缘膜布置在所述第一沟槽和所述第二沟槽之间的第一区以及在所述第二沟槽和所述第三沟槽之间的第二区中;

第一开口,所述第一开口穿透所述第四绝缘膜并且与所述第三半导体区接触;以及

第一电极,所述第一电极通过所述第一开口与所述第三半导体区耦合,

其中,所述第一区在第一方向上延伸,

其中,所述第一栅电极、所述第二栅电极以及所述第三栅电极在所述第一方向上延伸,

其中,所述耦合部在与所述第一方向交叉的第二方向上延伸,

其中,所述第一开口在所述第一区和所述耦合部的延伸方向的交叉区中被分割,

其中,所述第一开口在所述第一区中包括布置在所述交叉区的一侧的第一部以及布置在所述交叉区的另一侧的第二部,

其中,所述第一开口未布置在所述交叉区中

其中,所述第三半导体区被设置为与所述第一开口的所述第一部的端部隔开,以及

其中,在所述耦合部的一侧,所述第二栅电极的上表面包括低于所述第一栅电极的上表面的部分。

2.根据权利要求1所述的半导体器件,

其中,所述第三半导体区与所述第一部的端部之间的距离是1μm或更大。

3.根据权利要求1所述的半导体器件,

其中,多个第三半导体区被设置为在所述第一方向上彼此隔开第一距离。

4.根据权利要求1所述的半导体器件,

其中,所述第三半导体区未被设置在所述第二沟槽的与所述第一沟槽的所述第一侧表面相对的侧表面侧。

5.根据权利要求1所述的半导体器件,进一步包括:

第二开口,所述第二开口穿透所述第四绝缘膜并且与所述耦合部接触,

其中,所述第一电极通过所述第二开口与所述耦合部耦合。

6.根据权利要求5所述的半导体器件,进一步包括:

所述第二导电类型的第四半导体区,所述第四半导体区布置在所述半导体衬底的所述第二主表面侧并且在所述第一半导体区下方;以及

第二电极,所述第二电极与所述第四半导体区耦合。

7.根据权利要求6所述的半导体器件,进一步包括:

所述第一导电类型的第五半导体区,所述第五半导体区布置在所述第一区的所述第二半导体区与所述第一半导体区之间。

8.根据权利要求7所述的半导体器件,

其中,所述第一开口到达所述第二半导体区,以及

其中,所述第二导电类型的第六半导体区设置在所述第一开口的底部。

9.根据权利要求8所述的半导体器件,进一步包括:

所述第二导电类型的第七半导体区,所述第七半导体区布置在所述第二区的所述第二半导体区与所述第一半导体区之间。

10.根据权利要求1所述的半导体器件,

其中,所述第一区的宽度比所述第二区的宽度的一半窄。

11.根据权利要求1所述的半导体器件,

其中,在所述交叉区中,所述第一区的所述第四绝缘膜的表面包括低于所述第二区的所述第四绝缘膜的表面的部分。

12.一种制造半导体器件的方法,包括以下步骤:

(a)设置半导体衬底,所述半导体衬底包括第一主表面以及在所述第一主表面的相反侧的第二主表面,并且所述半导体衬底至少在所述第二主表面侧包括第一导电类型的第一半导体区;

(b)形成第一沟槽、布置为与所述第一沟槽隔开的第二沟槽,以及布置为与所述第二沟槽隔开的第三沟槽,所述第一沟槽、所述第二沟槽以及所述第三沟槽到达所述半导体衬底的中部;

(c)经由栅极绝缘膜,在包括所述第一沟槽、所述第二沟槽以及所述第三沟槽的内部的所述半导体衬底上面形成第一导电膜;

(d)通过蚀刻所述第一导电膜,经由第一栅极绝缘膜在所述第一沟槽的内部形成第一栅电极,经由第二栅极绝缘膜在所述第二沟槽的内部形成第二栅电极,以及经由第三栅极绝缘膜在所述第三沟槽的内部形成第三栅电极,并且形成将所述第二栅电极和所述第三栅电极彼此耦合的耦合部;

(e)在所述第一沟槽和所述第二沟槽之间的第一区以及在所述第二沟槽和所述第三沟槽之间的第二区的所述第一主表面侧,形成第二导电类型的第二半导体区,所述第二导电类型与所述第一导电类型相反;

(f)在所述第一区的所述第二半导体区内形成所述第一导电类型的第三半导体区,以便与所述第一栅极绝缘膜接触;

(g)在所述第一区和所述第二区上面形成层间绝缘膜;

(h)通过蚀刻所述层间绝缘膜形成与所述第三半导体区接触的第一开口;以及

(i)通过在包括所述第一开口的内部的所述层间绝缘膜上面形成第二导电膜来形成第一电极,

其中,在所述步骤(c)中,所述第一沟槽、所述第二沟槽以及所述第三沟槽被形成为在第一方向上延伸,

其中,在所述步骤(d)中,所述耦合部被形成为在与所述第一方向交叉的第二方向上延伸,

其中,在所述步骤(h)中,所述第一开口被形成为在所述第一区与所述耦合部的延伸方向的交叉区中被分割,并且在所述第一区中包括布置在所述交叉区的一侧的第一部以及布置的所述交叉区的另一侧的第二部,并且所述第一开口未布置在所述交叉区中,

其中,所述第三半导体区被设置为与所述第一开口的所述第一部的端部隔开,

其中,在所述步骤(d)中,蚀刻所述第一导电膜,使得在所述耦合部的一侧,所述第二栅电极的上表面变得低于所述第一栅电极的上表面。

13.根据权利要求12所述的制造半导体器件的方法,

其中,所述第三半导体区与所述第一部的端部之间的距离是1μm或更大。

14.根据权利要求12所述的制造半导体器件的方法,

其中,多个第三半导体区被设置为在所述第一方向上彼此隔开第一距离。

15.根据权利要求12所述的制造半导体器件的方法,

其中,所述第一区的宽度比所述第二区的宽度的一半窄。

16.根据权利要求12所述的制造半导体器件的方法,

其中,在所述步骤(g)中,在所述交叉区中,所述第一区的所述层间绝缘膜的表面包括低于的所述第二区的所述层间绝缘膜的表面的部分。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015-117796 | 2015-06-10 | ||

| JP2015117796A JP6495751B2 (ja) | 2015-06-10 | 2015-06-10 | 半導体装置および半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN106409894A CN106409894A (zh) | 2017-02-15 |

| CN106409894B true CN106409894B (zh) | 2020-09-11 |

Family

ID=57517179

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201610404085.9A Active CN106409894B (zh) | 2015-06-10 | 2016-06-08 | 半导体器件及其制造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US9871127B2 (zh) |

| JP (1) | JP6495751B2 (zh) |

| CN (1) | CN106409894B (zh) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6448434B2 (ja) * | 2015-03-25 | 2019-01-09 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| JP6495751B2 (ja) * | 2015-06-10 | 2019-04-03 | ルネサスエレクトロニクス株式会社 | 半導体装置および半導体装置の製造方法 |

| JP2017022798A (ja) * | 2015-07-07 | 2017-01-26 | ルネサスエレクトロニクス株式会社 | 電力変換装置および駆動装置 |

| JP6649216B2 (ja) * | 2016-09-16 | 2020-02-19 | 株式会社東芝 | 半導体装置およびその製造方法 |

| IT201600108699A1 (it) * | 2016-10-27 | 2018-04-27 | St Microelectronics Srl | Dispositivo semiconduttore a canale verticale con ridotta tensione di saturazione |

| KR102568562B1 (ko) * | 2017-01-24 | 2023-08-18 | 삼성전자주식회사 | 반도체 장치 |

| JP7000240B2 (ja) * | 2018-04-18 | 2022-01-19 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP7120916B2 (ja) * | 2018-12-27 | 2022-08-17 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| US20220216313A1 (en) * | 2019-06-04 | 2022-07-07 | Rohm Co., Ltd. | Semiconductor device |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102751329A (zh) * | 2011-04-19 | 2012-10-24 | 三菱电机株式会社 | 半导体装置 |

| JP2013120809A (ja) * | 2011-12-07 | 2013-06-17 | Hitachi Ltd | 半導体装置及びそれを用いた電力変換装置 |

| CN103199108A (zh) * | 2012-01-05 | 2013-07-10 | 瑞萨电子株式会社 | Ie型沟槽栅极igbt |

| CN103489905A (zh) * | 2012-06-11 | 2014-01-01 | 瑞萨电子株式会社 | 窄的有源单元ie型沟槽栅极igbt及其制造方法 |

| CN104282744A (zh) * | 2014-10-31 | 2015-01-14 | 无锡同方微电子有限公司 | 一种igbt器件结构 |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005085903A (ja) * | 2003-09-05 | 2005-03-31 | Renesas Technology Corp | 半導体装置およびその製造方法 |

| JP4857566B2 (ja) * | 2005-01-27 | 2012-01-18 | 富士電機株式会社 | 絶縁ゲート型半導体装置とその製造方法 |

| JP5423018B2 (ja) | 2009-02-02 | 2014-02-19 | 三菱電機株式会社 | 半導体装置 |

| JP5216801B2 (ja) * | 2010-03-24 | 2013-06-19 | 株式会社東芝 | 半導体装置 |

| US8809911B2 (en) | 2010-11-30 | 2014-08-19 | Fuji Electric Co., Ltd. | Semiconductor device |

| JP5969771B2 (ja) | 2011-05-16 | 2016-08-17 | ルネサスエレクトロニクス株式会社 | Ie型トレンチゲートigbt |

| JP6290526B2 (ja) | 2011-08-24 | 2018-03-07 | ローム株式会社 | 半導体装置およびその製造方法 |

| KR102087078B1 (ko) * | 2013-11-04 | 2020-03-10 | 삼성전자주식회사 | 반도체 소자 |

| JP6420175B2 (ja) * | 2014-05-22 | 2018-11-07 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP2016076561A (ja) * | 2014-10-03 | 2016-05-12 | 株式会社東芝 | 記憶装置 |

| JP6164201B2 (ja) * | 2014-11-17 | 2017-07-19 | トヨタ自動車株式会社 | 半導体装置 |

| JP2016174027A (ja) * | 2015-03-16 | 2016-09-29 | 株式会社東芝 | 半導体装置 |

| US9391135B1 (en) * | 2015-03-23 | 2016-07-12 | Semiconductor Components Industries, Llc | Semiconductor device |

| JP6448434B2 (ja) * | 2015-03-25 | 2019-01-09 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| JP6385873B2 (ja) * | 2015-03-30 | 2018-09-05 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| JP6495751B2 (ja) * | 2015-06-10 | 2019-04-03 | ルネサスエレクトロニクス株式会社 | 半導体装置および半導体装置の製造方法 |

-

2015

- 2015-06-10 JP JP2015117796A patent/JP6495751B2/ja active Active

-

2016

- 2016-05-10 US US15/151,112 patent/US9871127B2/en active Active

- 2016-06-08 CN CN201610404085.9A patent/CN106409894B/zh active Active

-

2017

- 2017-11-28 US US15/824,523 patent/US10032895B2/en active Active

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102751329A (zh) * | 2011-04-19 | 2012-10-24 | 三菱电机株式会社 | 半导体装置 |

| JP2013120809A (ja) * | 2011-12-07 | 2013-06-17 | Hitachi Ltd | 半導体装置及びそれを用いた電力変換装置 |

| CN103199108A (zh) * | 2012-01-05 | 2013-07-10 | 瑞萨电子株式会社 | Ie型沟槽栅极igbt |

| CN103489905A (zh) * | 2012-06-11 | 2014-01-01 | 瑞萨电子株式会社 | 窄的有源单元ie型沟槽栅极igbt及其制造方法 |

| CN104282744A (zh) * | 2014-10-31 | 2015-01-14 | 无锡同方微电子有限公司 | 一种igbt器件结构 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN106409894A (zh) | 2017-02-15 |

| JP6495751B2 (ja) | 2019-04-03 |

| US20180083130A1 (en) | 2018-03-22 |

| US20160365433A1 (en) | 2016-12-15 |

| US10032895B2 (en) | 2018-07-24 |

| JP2017005117A (ja) | 2017-01-05 |

| US9871127B2 (en) | 2018-01-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN106409894B (zh) | 半导体器件及其制造方法 | |

| US9614066B2 (en) | Semiconductor device provided with an IE type trench IGBT | |

| US9673309B2 (en) | Semiconductor device and method for fabricating semiconductor device | |

| US20120049187A1 (en) | Semiconductor device | |

| JP2988871B2 (ja) | トレンチゲートパワーmosfet | |

| TW201539750A (zh) | 半導體裝置 | |

| JP6633867B2 (ja) | 半導体装置およびその製造方法 | |

| KR20180062379A (ko) | 반도체 장치, rc-igbt 및 반도체 장치의 제조 방법 | |

| JP2015065420A (ja) | 半導体装置 | |

| JP2022121581A (ja) | 半導体装置 | |

| CN106611784B (zh) | 半导体器件及其制造方法 | |

| US8471333B2 (en) | Semiconductor device and manufacturing method of the same | |

| CN106469752B (zh) | 半导体器件及其制造方法 | |

| CN111384162A (zh) | 半导体器件及其制造方法 | |

| US20200303528A1 (en) | Semiconductor Device Including Electrode Trench Structure and Isolation Trench Structure and Manufacturing Method Therefore | |

| JP6606364B2 (ja) | 半導体装置およびその製造方法 | |

| CN113823672A (zh) | 半导体装置及其制造方法 | |

| US20230420550A1 (en) | Semiconductor device and method of manufacturing the same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| GR01 | Patent grant | ||

| GR01 | Patent grant |