CN102217052B - 用于将半导体芯片从薄膜处揭下和移除的方法 - Google Patents

用于将半导体芯片从薄膜处揭下和移除的方法 Download PDFInfo

- Publication number

- CN102217052B CN102217052B CN200980145287.4A CN200980145287A CN102217052B CN 102217052 B CN102217052 B CN 102217052B CN 200980145287 A CN200980145287 A CN 200980145287A CN 102217052 B CN102217052 B CN 102217052B

- Authority

- CN

- China

- Prior art keywords

- semiconductor chip

- chip

- film

- gripper

- pin

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/67005—Apparatus not specifically provided for elsewhere

- H01L21/67011—Apparatus for manufacture or treatment

- H01L21/67132—Apparatus for placing on an insulating substrate, e.g. tape

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/677—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for conveying, e.g. between different workstations

- H01L21/67703—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for conveying, e.g. between different workstations between different workstations

- H01L21/67721—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for conveying, e.g. between different workstations between different workstations the substrates to be conveyed not being semiconductor wafers or large planar substrates, e.g. chips, lead frames

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/683—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L21/6835—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support

- H01L21/6836—Wafer tapes, e.g. grinding or dicing support tapes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/683—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L21/687—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches

- H01L21/68714—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches the wafers being placed on a susceptor, stage or support

- H01L21/68742—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches the wafers being placed on a susceptor, stage or support characterised by a lifting arrangement, e.g. lift pins

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/683—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L21/687—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches

- H01L21/68714—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches the wafers being placed on a susceptor, stage or support

- H01L21/68778—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches the wafers being placed on a susceptor, stage or support characterised by supporting substrates others than wafers, e.g. chips

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T156/00—Adhesive bonding and miscellaneous chemical manufacture

- Y10T156/11—Methods of delaminating, per se; i.e., separating at bonding face

- Y10T156/1126—Using direct fluid current against work during delaminating

- Y10T156/1132—Using vacuum directly against work during delaminating

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T156/00—Adhesive bonding and miscellaneous chemical manufacture

- Y10T156/11—Methods of delaminating, per se; i.e., separating at bonding face

- Y10T156/1168—Gripping and pulling work apart during delaminating

- Y10T156/1179—Gripping and pulling work apart during delaminating with poking during delaminating [e.g., jabbing, etc.]

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T156/00—Adhesive bonding and miscellaneous chemical manufacture

- Y10T156/19—Delaminating means

- Y10T156/1928—Differential fluid pressure delaminating means

- Y10T156/1944—Vacuum delaminating means [e.g., vacuum chamber, etc.]

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T156/00—Adhesive bonding and miscellaneous chemical manufacture

- Y10T156/19—Delaminating means

- Y10T156/1978—Delaminating bending means

- Y10T156/1983—Poking delaminating means

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Container, Conveyance, Adherence, Positioning, Of Wafer (AREA)

Abstract

将半导体芯片(1)从薄膜(3)处揭下和移除依据本发明分三个阶段进行。在第一阶段,利用机械机构,但在芯片抓爪(11)不参与的情况下进行半导体芯片(1)从薄膜(3)处的部分揭下。在第二阶段,将半导体芯片(1)从薄膜(3)处完全揭下,其中,半导体芯片(1)由芯片抓爪(11)保持。在第三阶段,芯片抓爪(11)抬升并移开。

Description

技术领域

本发明涉及一种以机械机构支持的、用于将半导体芯片从薄膜处揭下和移除的方法。

背景技术

半导体芯片典型地在由框架保持的薄膜上提供用于在半导体安装装置上的工作,所述薄膜在专业领域也作为承载带(“Tape”)而公知。半导体芯片附着在薄膜上。带有薄膜的框架由可以移动的晶圆工作台拾取。晶圆工作台周期性地移动,以便在一个地点接着另一个地点上提供半导体芯片,且然后所提供的半导体芯片由芯片抓爪拾取并在基底上定位。所提供的半导体芯片从薄膜的移除得到布置在薄膜下方的芯片推料器(在专业领域中作为晶片顶出器(“Die-Ejector”)而公知)的支持。芯片推料器是带有支承面的工作台,薄膜平放在所述支承面上。工作台包含大量的孔,以便在半导体芯片的揭下过程期间借助真空牢固地保持薄膜。

在许多情况下,布置在芯片推料器内的一个或者多个针支持半导体芯片从薄膜处地揭下。针支持的方法由大量专利所公知,例如由US20040105750或者US 7265035所公知。在US 2008086874中,芯片推料器包含带有大量具有扁平末端的杆的区块和带有大量针的第二区块,其中,针布置在杆之间,且其中,每个杆的扁平末端的面积为针的横截面的数倍。为揭下半导体芯片,首先抬升带杆的区块,且然后抬升带针的区块,直至针突出超过杆。

由WO 2005117022公知一种带有支撑结构的芯片推料器,在整个揭下过程期间薄膜平放在该支撑结构上。该支承结构由带有扁平末端的杆包围,这些杆可以在向着半导体芯片的方向上以及在相反的方向上移动。支撑结构和杆也可以通过大量矩阵式布置的单个推杆形成。

由US 20050059205公知一种具有多个处于彼此并排的板的芯片推料器,这些板为揭下半导体芯片而要么一起抬升且然后从外向内按顺序降下,要么从外向内按顺序抬升,以便形成伸出超过支撑平面的、呈金字塔形的隆起。

公知的还有各种各样的方法,在这些方法中半导体芯片不借助针从薄膜处揭下。在US 4921564中,在半导体芯片下方的薄膜在大量单独的部位处被施加以真空,以便将薄膜在这些部位处从半导体芯片处揭离。在US 20040038498中同样是这种情况,即芯片抓爪在揭下过程完结时,也就是说芯片推料器不能再继续揭下过程时才抓取半导体芯片。因此,这种方法不适用于极薄的半导体芯片,因为会使这些半导体芯片碎裂。在EP 1496422中,薄膜借助冲具而在没有芯片抓爪与半导体芯片辅助的情况下完全脱开。这种方法同样不适用于极薄的半导体芯片,因为会使这些半导体芯片变弯和/或者卷起。在US 2002129899和US 7238593中,将薄膜牵拉超过芯片推料器的棱边并与此同时揭下。在US 6561743中,首先借助真空将薄膜从半导体芯片的边缘区域中揭离,并然后相对于由芯片抓爪牢固地保持的半导体芯片移动,其中,半导体芯片从薄膜处揭下。

半导体芯片从薄膜处的揭下和移除在专业领域称为摘取过程。针支持的标准摘取过程包括以下步骤:

a)移动晶圆工作台,以便提供下一个待拾取的半导体芯片;

b)借助真空将薄膜牢固地保持在芯片推料器上;

c)降下芯片抓爪,直至芯片抓爪触到半导体芯片的表面,以及对芯片抓爪施加以真空,以便牢固地保持半导体芯片;

d)将针抬升到预先确定的高度,其中,这些针抬升半导体芯片,并且薄膜从半导体芯片处部分地脱开;

e)移开芯片抓爪,其中,半导体芯片从薄膜以及针处完全揭下。

半导体芯片从薄膜处的揭下和移除只有当在步骤d)后仍残留的薄膜粘合力小于芯片抓爪的真空吸力时才能成功。否则会出现所谓的摘取失误:不能拾取半导体芯片,非常薄的半导体芯片损坏或者碎裂。

半导体芯片要么借助事先涂覆到基底上的粘合剂,要么借助安置在基底背侧的粘合剂膜即所谓的“晶片贴装膜(Die Attach Film)”在键合时与基底粘合。在后一种情况下,必须将带有粘合剂膜的半导体芯片从薄膜处分离。将基底加热到高于室温的温度上,以便在键合时在半导体芯片与基底之间制造出持久的粘合连接。由于半导体芯片与基底接触,粘合剂膜熔化并将半导体芯片牢固地粘合。通过这种持续几秒钟的粘合过程,芯片抓爪加热。由此,在下一个摘取过程中,在下一个待拾取的半导体芯片中在揭下过程期间就已经出现不希望的粘合剂膜的升温。与此同时,薄膜与粘合剂膜之间的粘合力增加,这可导致上面提到的摘取失误。

在下文中,概念半导体芯片也理解为其背侧以粘合剂膜来涂层的半导体芯片。

发明内容

因此,值得追求的是,提供一种方法,该方法允许半导体芯片特别是带有小于50μm的厚度的非常薄的半导体芯片在尽可能短的时间内从薄膜处移走,从而使得在短暂的接触时间期间半导体芯片通过芯片抓爪引起的升温仅无关紧要地加强在薄膜和半导体芯片之间的粘合连接。

本发明从这种认识出发,即,这在如下时刻实现,即,在半导体芯片(或者说粘合剂膜)与薄膜之间的附着以如下程度变小时,即,使得即使在半导体芯片从薄膜处快速揭下时,在此由于粘合连接而产生的力仍保持为不严重的。在此需要注意的是,不能使用其粘合连接一开始较弱的粘合剂膜,因为在这种情况下存在如下危险,即,在将晶圆分割成单个半导体芯片(锯开)时或者在运输所锯碎的晶圆时,半导体芯片从薄膜处无法控制地揭下。

因此,本发明提出,在第一阶段中,在芯片抓爪与半导体芯片接触且牢固地保持半导体芯片之前,利用机械机构通过将薄膜从半导体芯片处部分脱开来实现粘合连接的削弱,在第二阶段中,使芯片抓爪与半导体芯片进行接触且牢固地保持半导体芯片,并然后利用芯片抓爪的支持将薄膜进一步从半导体芯片处揭下,以及在第三阶段中移开带有半导体芯片的芯片抓爪。

用于将半导体芯片从薄膜处揭下和移除的方法由芯片推料器支持。芯片推料器具有支承面,薄膜平放在该支承面上。依据本发明的方法包括无芯片抓爪参与的第一阶段,具有如下步骤:

在芯片推料器的支承面上提供下一个待拾取的半导体芯片;

对推料器施加以真空,以便将薄膜牢固地保持在芯片推料器上;

利用机械机构将薄膜从所提供的半导体芯片处部分揭下;以及

拍摄半导体芯片的图像并确定半导体芯片的位置或半导体芯片的实际位置与额定位置的偏差;

依据本发明的方法包括第二阶段,具有如下步骤:

降下芯片抓爪,直至芯片抓爪触到半导体芯片的表面;

对芯片抓爪施加以真空,以便牢固地保持半导体芯片;

将薄膜从所提供的半导体芯片处进一步揭下;以及包括第三阶段,具有如下步骤:

抬升和移开芯片抓爪。

依据本发明的方法特别是为厚度低于50μm的非常薄的半导体芯片而研发。在第一阶段中,部分揭下薄膜,也就是说,薄膜以底侧面积的一定比例而不再接触半导体芯片的底侧。在第一阶段结束时,半导体芯片与薄膜仍然保持以如下距离,即,使得半导体芯片首先顶多以如下程度变弯或者弯曲,即,使摄像机可以拍摄到半导体芯片的可评估图像,其次,使得由芯片抓爪在没有芯片推料器的继续支持的情况下还不能从薄膜处移走,而半导体芯片不损坏或者破碎。在第二阶段中,进一步揭下薄膜,也就是说,不再被薄膜接触在上面的底侧面积的比例增大。因为芯片抓爪已经牢固地保持半导体芯片,所以半导体芯片在该阶段中没有变弯。在第二阶段结束时,薄膜要么完全从半导体芯片处揭下,要么薄膜仅以底侧面积的很小比例接触半导体芯片,这种比例小得可以使芯片抓爪在第三阶段中抬升或移开,其中,芯片抓爪在没有损坏危险的情况下携带起半导体芯片。

所说的在第一阶段中半导体芯片从薄膜处的部分揭下优选地通过滑架的移动以如下方式进行,即,使在芯片推料器的支承面内在所提供的半导体芯片的棱边下方形成间隙,其中,在该间隙内存在的真空将薄膜拉入到间隙内并从半导体芯片处揭下。在第二阶段中的进一步揭下通过间隙的进一步加宽来进行。

同样利用针可支持将半导体芯片从薄膜处揭下,这些针可以垂直于或者倾斜于支承面移动。在此,将针尖伸出超过支承面的距离称为高度。在这种情况下,所说的在第一阶段中薄膜从所提供的半导体芯片处的部分揭下通过以下步骤进行:

将针抬升到预先确定的高度z1上,从而使这些针伸出超过支承面;以及

将针降下到小于高度z1的预先确定的高度z2上。

但粘合连接的削弱也可以(单独地或者以辅助支持的方式)通过借助流体(例如冷却气体或者冷却液体)从下面冷却薄膜的方式来进行。

附图说明

下面借助示图对本发明的实施例进行详细阐释。附图所示是示意性的且不是按比例的。

图1a-g示出依据本发明的第一实施例的在摘取过程期间的不同瞬间拍摄记录;

图2a-f示出依据本发明的第二实施例的在摘取过程期间的不同瞬间拍摄记录;以及

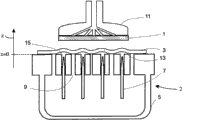

图3以俯视图示出适用于第二实施例的芯片推料器。

具体实施方式

图1a-g示出依据第一实施例在依据本发明的摘取过程期间的逐个时间点上,自动装配机参与将半导体芯片1从薄膜3处揭下和移除的部分(即芯片推料器2和芯片抓爪11)以及薄膜3和半导体芯片1。所参与的部分被简化并且仅在对理解摘取过程必要的程度上示出。芯片推料器2包括可施加真空的室5,该室具有带有上面平放有薄膜3的支承面13的可更换盖。该盖包含大量的孔9和15。优选的是,孔9的直径仅为如下尺寸,即,使得不可将薄膜3吸入到孔9内,也就是说,孔9基本上仅用于牢固地保持薄膜3。在孔15内布置有针7,这些针通常可以垂直于或者倾斜于盖的支承面13移动。针7可以移动的方向称为z方向,其中,盖的支承面13限定零点z=0。针尖突出超过支承面13的距离称为针7的高度。高度的负的z值意味着:针7完全沉入到孔15内并因此不突出超过支承面13。

依据本发明,半导体芯片1从薄膜3处的揭下和移除在准备阶段前后扩展,从而使得整个方法包括三个阶段。第一阶段是准备阶段,在该准备阶段中借助于针7削弱半导体芯片1与薄膜3之间的粘合连接。在第一阶段中芯片抓爪11不参与。第二阶段是与第一阶段直接连接的阶段,在该第二阶段中芯片抓爪11由针7支持进一步地揭下半导体芯片1。在第三阶段中,芯片抓爪11抬升并移开,其中,半导体芯片1在没有通过针7进一步支持的情况下从薄膜3处完全揭下。

第一阶段包括以下步骤:

A)移动晶圆工作台,以便在芯片推料器2的上方提供待拾取的下一个半导体芯片1;

针7在降下的状态下处于孔15内,从而使这些针在步骤A期间不接触薄膜3。

B)对芯片推料器2施加以真空(或低压),以便将薄膜3牢固地保持在芯片推料器2上。

在该步骤中,对室5施加以真空。孔9内存在的真空吸住薄膜3。图1a示出在该步骤后的状态。

C)将针7抬升到预先确定的高度z1上。

高度z1的数值z1>0,也就是说,针7突出超过支承面13。z1的典型数值为0.5mm。在该步骤中,薄膜3的处于针7上的那些区域由芯片推料器2移走。因此半导体芯片1也被抬升,而薄膜3的处于没有针7的孔9上的那些区域则继续停留在芯片推料器2上,进而从半导体芯片1处脱开。该状态在图1b中表示出。

D)将针7降下到预先确定的高度z2上。

在典型地处于0.5和3秒之间的预先确定的持续时间结束后,将针7回移到z2<z1的预先确定的高度z2上。结果是薄膜3的某些区域仍与半导体芯片1粘合,而其它区域则已经从半导体芯片1处揭除。该状态在图1c中为进行说明而夸张地示出,其中,在该例中z2<0。z2<0还是z2=0是无关紧要的。此外,在图1c中示出现在才接近的芯片抓爪11。

进行针7的降下,从而使得摄像机可以测定半导体芯片1的位置。在针7移出时,测定在很大程度上是有问题的,因为此时芯片表面容易部分地拱起,并且在光线垂直入射的情况下,部分地不能由图像处理器识别。然而,当将针7重新完全拉回到孔15内时,可能出现的问题是,半导体芯片1重新在薄膜3上粘住。为避免这种情况,有利的是,选择高度z2>0,以便使针7的尖几乎处于支承面13的上方,从而使得摄像机仍能识别半导体芯片1,且尽管如此,半导体芯片1不会重新在整个薄膜3上粘住。z2有利的数值处于0.0mm至0.2mm的范围内。还要提及的是,针7的运行速度可以在1mm/s和10mm/s之间选择。

E)拍摄半导体芯片1的图像并确定所述半导体芯片的位置或者说所述半导体芯片的实际位置与其额定位置的偏差。

由此,第一阶段进而用于移除半导体芯片1的准备工作完结。在此极其有利的是,对该准备步骤而言不需要芯片抓爪11便可以进行准备,而键合头本身则仍从事于此前移除的半导体芯片的处理工作(键合过程)。这种准备工作需要持续相应时长,而在此不延长总过程时间。此外,这一切均发生在室温下,从而在半导体芯片1从薄膜3处部分揭除时,不一定要由于温度升高而复杂化。

现在开始第二阶段,具有如下步骤:

F)降下芯片抓爪11,直至该芯片抓爪触到半导体芯片1的表面,并且对芯片抓爪11施加以真空,以便牢固地保持半导体芯片1;

这种状态在图1d中表示出。

G)将针7抬升到预先确定的高度z3上。

在该步骤中,针7重新或进一步抬升半导体芯片1,且薄膜3进一步从半导体芯片1处脱开;用于z3的典型数值为0.5mm。在该步骤之后的状态在图1e中表示出。在该步骤中,如下区域扩大,即,在这些区域中薄膜3不再接触半导体芯片1的底侧(在附图中这几乎看不到)。

现在开始第三阶段,具有如下步骤:

H)抬升和移开芯片抓爪11。

在该步骤中,半导体芯片1完全从薄膜3处以及从针7处揭下。

因为由于准备步骤A至C半导体芯片1的许多区域已经从薄膜3处揭下,所以在与芯片推料器2的针7的共同工作下,芯片抓爪11现在实现了无其它问题地将半导体芯片1以高速从薄膜3处完全脱开或移除。由此,芯片移除过程的持续时间,也就是说步骤F至H所需的时间(直至半导体芯片1不再与薄膜3接触),从当未通过阶段1的步骤A至C进行准备工作时的、迄今典型的1秒降低到0.1秒。

图1f示出当芯片抓爪11连同所拾取的半导体芯片1已经从薄膜3处离开一段距离时的瞬间拍摄记录。如图所示,在芯片抓爪11将半导体芯片1从薄膜3处完全揭下时,针7才向下运行到支承面13下。

图1g示出了在针7重新降下到z<0的高度上之后最后的瞬间拍摄记录,从而可以导入下一个半导体芯片的摘取过程。在芯片抓爪11进一步处理刚刚移除的半导体芯片的过程期间,已可以为下一个待移除的半导体芯片开始第一阶段。

取代上述的方法步骤F至H,半导体芯片1的移除也能利用其它方法执行,这些方法匹配于各自的问题情况,而且就像由现有技术公开的那样。但在本发明范围内根本的是,芯片移除的实际阶段领先于用于在无芯片抓爪11参与的情况下将半导体芯片1从薄膜3处至少部分揭下的第一准备阶段和用于在芯片抓爪11参与以及通过芯片推料器2的针7进一步支持的情况下将半导体芯片1从薄膜3处进一步揭下的第二阶段。

图2a-g示出了依据第二实施例的、在依据本发明的摘取过程期间的逐个时间点上,自动装配机参与半导体芯片1从薄膜3处揭下和移除的部分。所参与的部分是简化的,并仅在对理解摘取过程而言必要的程度上表示出。芯片推料器2同样包括能施加以真空的室5,该室具有带有在上面平放有薄膜3的支承面13的盖。支承面13包含例如呈矩形的开口20和大量在至少三侧环绕开口20的孔9。在开口20内布置有可以与盖的支承面13平行地移动的滑架21。滑架21的移动方向称为x方向。在该移动方向上:滑架的长度基本与半导体芯片1的长度同样大,开口20的长度至少是半导体芯片1长度的两倍。图3以俯视图示出芯片推料器2。

半导体芯片1从薄膜3处的揭下和移除同样包括第一准备阶段,在该第一准备阶段中半导体芯片1与薄膜3之间的粘合连接借助于滑架21,但在没有芯片抓爪11的参与下得到削弱。第二阶段是与第一阶段直接连接的阶段,在该第二阶段中芯片抓爪11利用芯片推料器2的支持将半导体芯片1从薄膜3处进一步揭下。

第一阶段包括以下步骤:

A)移动晶圆工作台,以便在芯片推料器2上方提供下一个待拾取的半导体芯片1;

滑架21事先在开口20内以如下方式定位,即,使该滑架处于所提供的半导体芯片1的下方。

B)对芯片推料器2施加以真空(或低压),以便将薄膜3牢固地保持在芯片推料器2上。

孔9(图3)内存在的真空吸住薄膜3。图2a示出在该步骤后的状态(滑架21在该实施例中处于开口20的右边缘)。

C)在移动方向上以预先确定的距离D1移动滑架21(滑架21在该实施例中向左运动)。达到的状态在图2b中表示出。滑架21的移动以典型地约为2-5mm/s的比较缓慢的速度进行。在该步骤中,在支承面13与滑架21之间存在尺寸增大的间隙22。在室5内存在的真空将薄膜3拉入到间隙22内,其中,薄膜3在该区域内从半导体芯片1处揭下。距离D1典型地约为半导体芯片1、1’的长度L的10%-20%。该步骤的作用是:使薄膜3在半导体芯片1的棱边区域内从半导体芯片1处揭下。该步骤必须非常小心地进行,所以滑架21的速度比较慢。因此,该步骤需要一些时间。但如果薄膜在半导体芯片1长度L的约10-20%的边缘区域内一次揭下,那么可以将薄膜以比较快的速度从半导体芯片1的剩余部分处揭离。但这当在芯片抓爪11支持揭下时的第二阶段中才进行。

D)拍摄半导体芯片1的图像并确定所述半导体芯片的位置或者说所述半导体芯片的实际位置与其额定位置的偏差。

由此,第一阶段进而用于移除半导体芯片1的准备工作完结。现在开始第二阶段,具有如下步骤:

E)降下芯片抓爪11,直至该芯片抓爪触到半导体芯片1的表面,并且对芯片抓爪11施加以真空,以便牢固地保持半导体芯片1;

这种状态在图2c中表示出。

F)在与步骤C相同的方向上继续移动滑架21。

因为在该步骤开始时薄膜3已经从半导体芯片1的棱边处揭下,所以滑架21能以比较快的速度进行移动。该速度典型地约为20mm/s,但并不限制在该数值上。在该步骤中,薄膜3由于在室5内和在间隙22内存在的真空而进一步地从半导体芯片1处揭下。图2d示出了在该步骤F期间的瞬间拍摄记录,图2e示出了在步骤F结束时的瞬间拍摄记录。半导体芯片1现在完全从薄膜3处揭下。

现在开始第三阶段,采用的步骤是:

G)抬升和移开芯片抓爪11。

图2f示出在该步骤期间的瞬间拍摄记录。

半导体芯片1从薄膜3处的揭下也可以采用US 20050059205的设备之一进行,其中,芯片抓爪在第一阶段中不参与,且其中,芯片推料器2在第二阶段中将薄膜3从半导体芯片处进一步揭下,而在第三阶段芯片中抓爪11抬升和移开之前,半导体芯片1由芯片抓爪11保持,其中,芯片抓爪携带起半导体芯片1。

所介绍的依据本发明的方法既适用于其背侧利用粘合剂膜来涂层的半导体芯片,也适用于其棱边长度大于10mm且利用涂覆到基底上的粘合剂与基底相粘合的比较大的半导体芯片。在这种情况下,在第一阶段中的粘合连接的削弱也引起了用于移除半导体芯片的过程时间的缩短,因为仅必须在非常短的时间期间利用到芯片抓爪。借助于本发明,半导体芯片从薄膜处的揭下已经可以在芯片抓爪仍从事于前面的半导体芯片键合时进行。

所介绍的实施例仅包含最重要的步骤。这些步骤可以包含其它子步骤,或者可以在相应阶段内以其它顺序来执行。拍摄半导体芯片图像和确定半导体芯片的位置或者说半导体芯片的实际位置与额定位置的偏差的步骤,也可以在半导体芯片部分地从薄膜处揭下之前,也就是当半导体芯片的位置在进一步揭下时不再改变时执行。

半导体芯片从薄膜处的部分揭下也可以利用不同于这里所介绍的机械机构来进行。

Claims (4)

1.用于将半导体芯片(1)从薄膜(3)处揭下和移除的方法,在所述方法中,芯片推料器(2)支持所述半导体芯片(1)从所述薄膜(3)处的揭下,并且芯片抓爪(11)拾取所述半导体芯片(1),其中,所述芯片推料器(2)具有支承面(13),所述薄膜(3)平放在所述支承面上,所述方法包括无所述芯片抓爪(11)参与的第一阶段,所述第一阶段具有如下步骤:

在所述芯片推料器(2)的所述支承面(13)上提供下一个待拾取的半导体芯片(1),所述半导体芯片(1)仍完全粘合连接到所述薄膜(3);

对所述芯片推料器(2)施加以真空,以便将所述薄膜(3)牢固地保持在所述芯片推料器(2)上;

利用机械机构将所述薄膜(3)从所提供的半导体芯片(1)处部分地揭下,从而实现粘合连接的削弱;以及

拍摄所述半导体芯片(1)的图像并确定所述半导体芯片的位置或所述半导体芯片的实际位置与额定位置的偏差;

并且所述方法进一步地包括第二阶段,所述第二阶段具有如下步骤:

降下所述芯片抓爪(11),直至所述芯片抓爪(11)触到所述半导体芯片(1)的表面;

对所述芯片抓爪(11)施加以真空,以便牢固地保持所述半导体芯片(1);

利用所述芯片推料器(2)的支持将所述薄膜(3)从所提供的半导体芯片(1)处进一步揭下;

并且所述方法进一步地包括第三阶段,所述第三阶段具有如下步骤:

抬升和移开所述芯片抓爪(11)。

2.按权利要求1所述的方法,在所述方法中,所提及的将所述半导体芯片(1)从所述薄膜(3)处部分揭下通过移动滑架(21)来进行,从而使得在所述芯片推料器(2)的所述支承面(13)内、在所提供的半导体芯片(1)的棱边的下方形成间隙(22),其中,在所述间隙(22)内存在的真空将所述薄膜(3)拉到所述间隙(22)内,并从所述半导体芯片(1)处揭下。

3.按权利要求1所述的方法,在所述方法中,利用针(7)来支持所述半导体芯片(1)从所述薄膜(3)处的揭下,这些针能够垂直于或者倾斜于所述支承面(13)地移动,并且其中,将所述针(7)的尖伸出所述支承面(13)的距离称为高度,在所述方法中,所提及的将所述薄膜(3)从所提供的半导体芯片(1)处部分揭下通过以下步骤进行:

将所述针(7)抬升到预先确定的高度z1上,从而使得所述针(7)伸出超过所述支承面(13);以及

将所述针(7)降下到小于所述高度z1的预先确定的高度z2上。

4.按权利要求3所述的方法,其特征在于,以如下方式选择所述高度z2,即,使得所述针(7)不伸出超过所述支承面(13)。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11376108P | 2008-11-12 | 2008-11-12 | |

| US61/113,761 | 2008-11-12 | ||

| PCT/EP2009/064535 WO2010054957A1 (de) | 2008-11-12 | 2009-11-03 | Verfahren zum ablösen und entnehmen eines halbleiterchips von einer folie |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN102217052A CN102217052A (zh) | 2011-10-12 |

| CN102217052B true CN102217052B (zh) | 2013-09-25 |

Family

ID=41381913

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN200980145287.4A Active CN102217052B (zh) | 2008-11-12 | 2009-11-03 | 用于将半导体芯片从薄膜处揭下和移除的方法 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US8715457B2 (zh) |

| EP (1) | EP2359398B1 (zh) |

| JP (1) | JP2012508460A (zh) |

| KR (1) | KR20110086698A (zh) |

| CN (1) | CN102217052B (zh) |

| MY (1) | MY155371A (zh) |

| TW (1) | TWI543285B (zh) |

| WO (1) | WO2010054957A1 (zh) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101397750B1 (ko) * | 2012-07-25 | 2014-05-21 | 삼성전기주식회사 | 칩 이젝터 및 이를 이용한 칩 탈착 방법 |

| JP2019029650A (ja) * | 2017-07-26 | 2019-02-21 | 芝浦メカトロニクス株式会社 | 半導体チップのピックアップ装置、半導体チップの実装装置および実装方法 |

| CN107539596A (zh) * | 2017-09-29 | 2018-01-05 | 常熟市荣达电子有限责任公司 | 一种芯片包装盒及其操作方法 |

| US12020967B2 (en) * | 2018-07-30 | 2024-06-25 | Ulvac Techno, Ltd. | Substrate lifting apparatus and substrate transferring method |

| CH715447B1 (de) * | 2018-10-15 | 2022-01-14 | Besi Switzerland Ag | Chip-Auswerfer. |

| CN111341717B (zh) * | 2020-03-10 | 2023-02-07 | 长江存储科技有限责任公司 | 一种拾取装置和拾取方法 |

| JP2023023499A (ja) * | 2021-08-05 | 2023-02-16 | 東京エレクトロン株式会社 | 接合装置および接合方法 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6561743B1 (en) * | 1999-11-09 | 2003-05-13 | Nec Machinery Corporation | Pellet picking method and pellet picking apparatus |

| CN1669119A (zh) * | 2002-07-17 | 2005-09-14 | 松下电器产业株式会社 | 拾取半导体芯片的方法和设备及为此使用的吸引和剥落工具 |

Family Cites Families (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6415000A (en) * | 1987-07-09 | 1989-01-19 | Sumitomo Electric Industries | Chip packaging device |

| US4921564A (en) | 1988-05-23 | 1990-05-01 | Semiconductor Equipment Corp. | Method and apparatus for removing circuit chips from wafer handling tape |

| JPH05283506A (ja) | 1992-04-01 | 1993-10-29 | Sharp Corp | チップ突き上げ装置 |

| JP3498877B2 (ja) * | 1995-12-05 | 2004-02-23 | 株式会社東芝 | 半導体製造装置および半導体装置の製造方法 |

| JP4482243B2 (ja) | 2001-03-13 | 2010-06-16 | 株式会社新川 | ダイのピックアップ方法及びピックアップ装置 |

| TW567574B (en) | 2001-12-05 | 2003-12-21 | Esec Trading Sa | Apparatus for mounting semiconductor chips |

| TWI225279B (en) | 2002-03-11 | 2004-12-11 | Hitachi Ltd | Semiconductor device and its manufacturing method |

| EP1424722A1 (de) * | 2002-11-29 | 2004-06-02 | Esec Trading S.A. | Verfahren zum Aufnehmen von Halbleiterchips von einer Folie und Vorrichtung |

| US20040105750A1 (en) | 2002-11-29 | 2004-06-03 | Esec Trading Sa, A Swiss Corporation | Method for picking semiconductor chips from a foil |

| JP4574251B2 (ja) | 2003-09-17 | 2010-11-04 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| EP1587138B1 (de) * | 2004-04-13 | 2007-05-30 | Oerlikon Assembly Equipment AG, Steinhausen | Einrichtung für die Montage von Halbleiterchips und Verfahren zum Ablösen eines Halbleiterchips von einer Folie |

| US7240422B2 (en) | 2004-05-11 | 2007-07-10 | Asm Assembly Automation Ltd. | Apparatus for semiconductor chip detachment |

| CH697213A5 (de) | 2004-05-19 | 2008-06-25 | Alphasem Ag | Verfahren und Vorrichtung zum Ablösen eines auf eine flexible Folie geklebten Bauteils. |

| JP2006005030A (ja) * | 2004-06-16 | 2006-01-05 | Matsushita Electric Ind Co Ltd | 半導体チップのピックアップ方法および装置 |

| US7238258B2 (en) | 2005-04-22 | 2007-07-03 | Stats Chippac Ltd. | System for peeling semiconductor chips from tape |

| US20070158024A1 (en) * | 2006-01-11 | 2007-07-12 | Symbol Technologies, Inc. | Methods and systems for removing multiple die(s) from a surface |

| JPWO2008004270A1 (ja) | 2006-07-03 | 2009-12-03 | キヤノンマシナリー株式会社 | ピックアップ方法およびピックアップ装置 |

| KR101278236B1 (ko) | 2006-09-12 | 2013-06-24 | 가부시키가이샤 에바라 세이사꾸쇼 | 연마장치 및 연마방법 |

| JP4755634B2 (ja) | 2006-09-29 | 2011-08-24 | 東レエンジニアリング株式会社 | ピックアップ装置及びピックアップ方法 |

| US7665204B2 (en) | 2006-10-16 | 2010-02-23 | Asm Assembly Automation Ltd. | Die detachment apparatus comprising pre-peeling structure |

| US8221583B2 (en) * | 2007-01-20 | 2012-07-17 | Stats Chippac Ltd. | System for peeling semiconductor chips from tape |

| JP4693805B2 (ja) * | 2007-03-16 | 2011-06-01 | 株式会社東芝 | 半導体装置の製造装置及び製造方法 |

| WO2009047214A2 (en) * | 2007-10-09 | 2009-04-16 | Oerlikon Assembly Equipment Ag, Steinhausen | Method for picking up semiconductor chips from a wafer table and mounting the removed semiconductor chips on a substrate |

| JP4985513B2 (ja) * | 2008-03-26 | 2012-07-25 | 富士通セミコンダクター株式会社 | 電子部品の剥離方法及び剥離装置 |

| CN102044404B (zh) * | 2009-10-12 | 2015-12-09 | 桑迪士克科技公司 | 用于使经切分的半导体裸片与裸片贴胶带分离的系统 |

-

2009

- 2009-11-03 WO PCT/EP2009/064535 patent/WO2010054957A1/de active Application Filing

- 2009-11-03 CN CN200980145287.4A patent/CN102217052B/zh active Active

- 2009-11-03 US US13/128,864 patent/US8715457B2/en active Active

- 2009-11-03 JP JP2011535096A patent/JP2012508460A/ja active Pending

- 2009-11-03 EP EP09749087.4A patent/EP2359398B1/de active Active

- 2009-11-03 MY MYPI2011001736A patent/MY155371A/en unknown

- 2009-11-03 KR KR1020117010535A patent/KR20110086698A/ko not_active Application Discontinuation

- 2009-11-10 TW TW098138052A patent/TWI543285B/zh active

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6561743B1 (en) * | 1999-11-09 | 2003-05-13 | Nec Machinery Corporation | Pellet picking method and pellet picking apparatus |

| CN1669119A (zh) * | 2002-07-17 | 2005-09-14 | 松下电器产业株式会社 | 拾取半导体芯片的方法和设备及为此使用的吸引和剥落工具 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP2359398B1 (de) | 2017-05-10 |

| TW201029093A (en) | 2010-08-01 |

| EP2359398A1 (de) | 2011-08-24 |

| MY155371A (en) | 2015-10-15 |

| US20110214819A1 (en) | 2011-09-08 |

| JP2012508460A (ja) | 2012-04-05 |

| US8715457B2 (en) | 2014-05-06 |

| KR20110086698A (ko) | 2011-07-29 |

| WO2010054957A1 (de) | 2010-05-20 |

| CN102217052A (zh) | 2011-10-12 |

| TWI543285B (zh) | 2016-07-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN102217052B (zh) | 用于将半导体芯片从薄膜处揭下和移除的方法 | |

| US20110192547A1 (en) | Control and monitoring system for thin die detachment and pick-up | |

| TW451288B (en) | Semiconductor manufacturing apparatus and manufacture of semiconductor device | |

| JP4906518B2 (ja) | 粘着テープ貼付け方法およびこれを用いた粘着テープ貼付け装置 | |

| CN103367136B (zh) | 将半导体芯片从箔拆下的方法 | |

| JP2008147249A (ja) | 基板貼合せ方法およびこれを用いた装置 | |

| JP2007160431A (ja) | ワイヤソーによる切断方法とワイヤソーの切断ワーク受け部材 | |

| JP2005328054A (ja) | 半導体チップの分離装置及び分離方法 | |

| CN101346046B (zh) | 印刷电路板的粘贴装置和粘贴方法 | |

| KR20010109463A (ko) | 반도체 칩의 박리·반송 방법 및 장치 | |

| EP1323652A3 (en) | Method and apparatus for feeding a panel from a stack | |

| JP2005303308A (ja) | 半導体チップをフォイルから取り外す方法、及び半導体チップを実装するための装置 | |

| EP1604827A3 (en) | A method of manufacturing a nozzle plate | |

| TWI693666B (zh) | 半導體晶圓的安裝方法及半導體晶圓的安裝裝置 | |

| EP1791161A3 (en) | Liquid processing method and liquid processing apparatus | |

| JPWO2014087489A1 (ja) | ダイボンダー装置 | |

| US20170221873A1 (en) | Apparatuses and methods for forming die stacks | |

| CN109256350A (zh) | 一种基于逐级均匀扩展的微器件巨量转移装置及方法 | |

| JP2005191535A (ja) | 貼り付け装置および貼り付け方法 | |

| US20130039733A1 (en) | Pick and place tape release for thin semiconductor dies | |

| JP2001144037A (ja) | 半導体装置の製造方法及び製造装置 | |

| CN101512746A (zh) | 拾取方法及拾取装置 | |

| JP6406942B2 (ja) | 保護テープ剥離方法および保護テープ剥離装置 | |

| JP4015138B2 (ja) | ピーリング装置及びピーリング方法 | |

| JP5373008B2 (ja) | 基板貼合せ方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| REG | Reference to a national code |

Ref country code: HK Ref legal event code: DE Ref document number: 1158360 Country of ref document: HK |

|

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| REG | Reference to a national code |

Ref country code: HK Ref legal event code: GR Ref document number: 1158360 Country of ref document: HK |