CN101924552B - Pll电路 - Google Patents

Pll电路 Download PDFInfo

- Publication number

- CN101924552B CN101924552B CN2010102029063A CN201010202906A CN101924552B CN 101924552 B CN101924552 B CN 101924552B CN 2010102029063 A CN2010102029063 A CN 2010102029063A CN 201010202906 A CN201010202906 A CN 201010202906A CN 101924552 B CN101924552 B CN 101924552B

- Authority

- CN

- China

- Prior art keywords

- frequency

- mentioned

- output

- voltage

- channel number

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L1/00—Stabilisation of generator output against variations of physical values, e.g. power supply

- H03L1/02—Stabilisation of generator output against variations of physical values, e.g. power supply against variations of temperature only

- H03L1/022—Stabilisation of generator output against variations of physical values, e.g. power supply against variations of temperature only by indirect stabilisation, i.e. by generating an electrical correction signal which is a function of the temperature

- H03L1/026—Stabilisation of generator output against variations of physical values, e.g. power supply against variations of temperature only by indirect stabilisation, i.e. by generating an electrical correction signal which is a function of the temperature by using a memory for digitally storing correction values

Landscapes

- Stabilization Of Oscillater, Synchronisation, Frequency Synthesizers (AREA)

Abstract

本发明提供一种能够对全部信道得到寄生特性良好的VCO输出并且能够抑制因温度变化造成的特性变动的PLL电路。在该PLL电路中,控制电路(3)具备温度传感器(31)、与温度对应地对每个信道编号存储了电压控制振荡器的输出的寄生特性良好的分频比的分频比表(32),从分频比表(32)读取与由温度传感器(31)检测出的温度和所输入的信道编号对应的分频比,并设定到PLLIC(2),并且向DDS电路(基准频率生成电路)(4)设定信道编号和分频比,DDS电路(4)根据信道编号和分频比计算出基准频率的值,生成与该值对应的基准频率。

Description

技术领域

本发明涉及PLL电路,特别涉及能够提高寄生特性的PLL电路。

背景技术

[现有技术的说明:图7]

使用图7说明一般的PLL(Phase Locked Loop)电路。图7是表示一般的PLL电路的结构的结构框图。

如图7所示,一般的PLL电路包括VCO(Voltage ControlledOscillator:电压控制振荡器)1、PLLIC2、DDS(Direct DigitalSynthesizer)电路4’、模拟滤波器5。

VCO1与来自模拟滤波器5的控制电压对应地振荡频率。

PLLIC2是以下这样的集成电路,即按照所设定的分频比对VCO1的输出频率进行分频,输出控制为与来自DDS电路4’的基准频率相比,VCO1的输出频率成为规定频率的电压,PLLIC2由单一芯片构成。

DDS电路4’根据所设定的信道编号,生成并输出基准频率信号。

模拟滤波器5取出来自PLLIC2的电压的直流部分,作为VCO1的控制电压而输出。

在上述结构的PLL电路中,PLLIC2按照指定的分频比对输入的VCO1的输出信号进行分频,对来自DDS电路4’的基准频率信号和相位进行比较,输出基于相位差的电压,由模拟滤波器5取出直流分量,作为控制电压施加到VCO1。由此,使VCO1的输出Fout成为规定的频率。

[DDS电路4’:图8]

在此,使用图8,说明现有的PLL电路的DDS电路4’的概要结构。图8是现有的DDS电路4’的概要结构图。

如图8所示,现有的DDS电路4’的基本结构具备控制部件41’、基准频率表43。

基准频率表43存储与信道编号对应的基准频率。

另外,控制部件41’如果输入了信道编号,则参照基准频率表43读取基准频率,输出对应的正弦波的数据。

进而,虽然省略图示,但由D/A变换器变换为模拟信号,经由滤波器而作为基准频率信号输出到PLLIC2。

[寄生恶化:图9]

在使用上述PLL电路作为合成器的情况下,通过改变来自DDS电路4’的基准频率、PLLIC2的分频比的设定,能够输出多个信道。

但是,根据信道,有时在来自DDS电路4’的基准频率、PLLIC2的输出中包含寄生成分,作为结果,在VCO1的输出中会产生寄生。

另外,还有该寄生恶化具有温度依存性的情况。

在此,使用图9,说明在一般的PLL电路中,改变了PLLIC2的分频比(div)的情况下的0~600信道的VCO1的输出寄生特性。图9是一般的PLL电路的VCO1的输出寄生特性的模式说明图。

在图9中,表示了将PLLIC2的分频比改变为133、135、137的情况下的VCO1的输出寄生特性。如图9所示可知,对于任意一个分频比,都有寄生特性显著恶化的信道。即,在每个信道中都有寄生特性良好的分频比和不好的分频比,对每个信道都不同。

[关联技术]

作为与PLL电路有关的技术,有日本特开2004-166179号公报“无线通信用半导体集成电路装置”(申请人:关西日本电气株式会社,专利文献1)、日本特开2003-69426号公报“频率合成器”(申请人:松下电器产业株式会社,专利文献2)。

另外,作为与频率合成器相关的技术,有日本特开2007-208367号公报“同步信号生成装置、发送机和控制方法”(申请人:株式会社ケンウツド,专利文献3)。

在专利文献1中记载了:在PLL电路中,通过从微型计算机设定信道编号,来设定最优的分频数N、A,减轻微型计算机的负荷。

但是,在专利文献1中,并没有记载基准频率fr是固定值,是可变的。

在专利文献2中记载了:在频率合成器中,即使基准频率信号与温度变化对应地变动,通过与温度变化对应地调节分频比,也能够减小输出频率的变动。

但是,在专利文献2中,并没有记载有意图地改变基准频率信号,抑制寄生恶化。

在专利文献3中记载了:针对DDS的输入信号频率和输出信号频率的组合,调整PLL电路的分频比、DDS的输出频率/输入频率等,使得DDS的寄生成为规定电平以下。

但是,在现有的PLL电路中,来自DDS电路的基准频率和PLLIC的分频比根据信道而被固定,并没有考虑到寄生特性,因此有以下的问题点:VCO输出的寄生特性有时恶化,由于恶化依存于温度,所以特性根据温度变化而变动。

发明内容

本发明就是鉴于上述实际情况而提出的,其目的在于:提供一种PLL电路,它能够对全部信道得到寄生特性良好的VCO输出,并且能够抑制因温度变化造成的特性变动。

用于解决上述现有例子的问题点的本发明是具备振荡与控制电压对应的频率的电压控制振荡器的PLL电路,具备:基准频率生成电路,输出与信道编号对应的一定的频率;相位比较单元,对按照设定了的分频比对电压控制振荡器的输出频率进行了分频的频率和基准频率生成电路的输出频率进行比较而输出相位差;循环滤波器,根据相位差而生成控制电压;控制部件,对每个信道编号存储了电压控制振荡器的输出的寄生特性良好的分频比的分频比表,其中,如果从外部输入了信道编号,则从分频比表读取与输入的信道编号对应的分频比,并设定到相位比较单元,并且对基准频率生成电路设定信道编号和分频比,基准频率生成电路根据信道编号和分频比计算出基准频率的值并生成与计算出的对应的值对应的基准频率,具有以下这样的效果:输入了任意的信道编号,都能够成为与希望的电压控制振荡器的输出频率对应的最优的分频比和基准频率,能够使电压控制振荡器输出的寄生特性良好。

另外,在本发明的上述PLL电路中,相位比较单元是把电路集成为单一芯片的PLL集成电路,具有能够使PLL电路全体小型化的效果。

另外,在本发明的上述PLL电路中,相位比较单元具备:按照所设定的分频比对电压控制振荡器的输出频率进行分频的分频器;将分频器的输出变换为数字信号的A/D变换器;对D/A变换器的输出和基准频率进行比较的相位比较器;对相位比较器的输出进行频带限制的数字滤波器;将数字滤波器的输出变换为模拟信号的A/D变换器,其中控制部件对分频器设定分频比,基准频率生成电路将所生成的基准频率输出到相位比较器,具有以下这样的效果:能够实现不使用PLL集成电路也能够使电压控制振荡器输出的寄生特性良好的数字控制PLL电路。

另外,在本发明的上述PLL电路中,在控制部件中具备测定周围的温度的温度传感器,分频比表与温度对应地对每个信道编号存储了电压控制振荡器的输出的寄生特性良好的分频比,控制部件从分频比表读取与所输入的信道编号和由温度传感器检测出的温度对应的分频比,具有以下这样的效果:能够与使用的温度对应地设定为最优的分频比和基准频率,能够抑制因温度变化产生的特性的变动,使电压控制振荡器输出的寄生特性进一步良好。

另外,在本发明的上述PLL电路中,基准频率生成电路具备:使信道编号和电压控制振荡器的输出频率对应起来进行存储的表,其中,如果输入了信道编号和分频比,则从表中读取与所输入的信道编号对应的电压控制振荡器的输出频率,根据电压控制振荡器的输出频率、输入的分频比,将电压控制振荡器的输出频率除以分频比,计算出基准频率的值,具有以下这样的效果:即使在希望的信道编号改变了的情况下,也能够容易地计算出适当的基准频率的值。

附图说明

图1是本实施例的PLL电路的结构框图。

图2是分频比表32的模式说明图。

图3是DDS电路4的概要结构图。

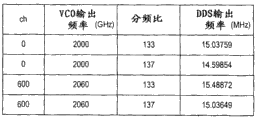

图4是表示了从DDS电路4输出的基准频率的例子的表图。

图5是本PLL电路的VCO1的常温时的输出寄生特性的模式说明图。

图6是适用了本PLL电路的数字控制PLL电路的结构框图。

图7是表示一般的PLL电路的结构的框图。

图8是现有的DDS电路4’的概要结构图。

图9是一般的PLL电路的VCO1的输出寄生特性的模式说明图。

附图标号

1:VCO;2:PLLIC;3、13:控制电路;4、14:DDS电路;5:模拟滤波器;11:分频器;12:A/D变换器;15:相位比较器;16:数字滤波器;18:D/A变换器;19:A/D变换器;31:温度传感器;32:分频比表;41:控制部件;42:VCO输出频率表;43:基准频率表

具体实施方式

[实施例的概要]

参照附图,说明本发明的实施例。

本发明的实施例的PLL电路在控制电路中具备温度传感器,并且与使用温度区域对应地,对每个信道将试验求出的寄生特性良好的分频比存储为分频比表,从外部输入了信道编号时,控制电路读取与由温度传感器检测出的温度数据和信道编号对应的分频比而设定到PLLIC,将信道编号和分频比设定到DDS电路,DDS电路根据信道编号和分频比计算出基准频率,生成基准频率信号并输出,因此,能够在实际使用的温度区域中使希望的信道的VCO输出的寄生特性良好。

[实施例的PLL电路:图1]

使用图1说明本实施例的PLL电路的结构。图1是实施例的PLL电路的结构框图。

如图1所示,本实施例的PLL电路包括VCO1、PLLIC2、控制电路3、DDS电路4、模拟滤波器5,VCO1、PLLIC2、模拟滤波器5的结构和动作与现有技术相同。

另外,PLLIC2相当于权利要求所记载的PLL集成电路,控制电路3相当于控制部件,DDS电路4相当于基准频率生成电路。

说明本PLL电路的特征部分。

[控制电路3]

控制电路3基本上具备计算电路和存储部件,作为本PLL电路的特征,在存储部件中存储分频比表32,还设置有温度传感器31。

温度传感器31测量VCO1等进行温度管理的代表性的部件的周围温度。

分频比表32是本PLL电路的特征部分,与使用温度对应地,对每个信道编号存储了寄生特性良好的分频比。

[分频比表:图2]

在此,使用图2,说明存储在控制电路3中的分频比表32。图2是分频比表32的示意说明图。

如图2所示,分频比表针对实际使用的全部信道,对每个使用温度,存储了寄生特性良好的分频比,在本PLL电路中,针对1~600信道,存储了低温、常温、高温时适当的分频比。在此,假设不满0℃为低温,0℃~50℃为常温,50℃以上为高温。

各表值是预先试验求出的,对每个分频比比较图9所示那样的各信道的寄生特性,选择各信道的寄生特性良好的最优的分频比。

另外,作为本PLL电路的特征,控制电路3根据从外部输入的信道编号和来自温度传感器31的温度数据,从分频比表32读取分频比,向PLLIC2设定分频比,并且向DDS电路4设定信道编号和分频比。由此,在每次向控制电路3设定信道编号时,都向PLLIC2和DDS电路4设定寄生良好的最优的分频比。

[DDS电路4:图3]

接着,使用图3说明本PLL电路的DDS电路4。图3是DDS电路4的概要结构图。

现有的DDS电路4’在输入了信道编号时,将应该生成的基准频率确定为一个,但在本PLL电路的DDS电路4中,根据从控制电路3输入的信道编号和分频比在内部计算基准频率,与之对应地生成基准频率信号。

如图3所示,本PLL电路的DDS电路4基本具备控制部件41和VCO输出频率表42,其他还与现有技术一样地具备正弦波表、D/A变换器、滤波器。

VCO输出频率表42存储了与信道编号对应地规定的VCO1的输出频率的值。在此,对0~600信道存储了VCO1的输出频率。

另外,在本DDS电路4中,控制部件41根据从图1所示的控制电路3输入的信道编号和分频比,计算出应该输出的基准频率的值,根据该值生成基准频率信号,输出到PLLIC2。

[基准频率的计算:图4]

在DDS电路4的控制部件41中,如果输入了从控制电路3输入的信道编号和分频比,则参照VCO输出频率表42,读取与输入的信道编号对应的VCO输出频率。

另外,控制部件41根据基准频率(MHz)=VCO输出频率(GHz)/分频比的计算公式,计算出基准频率。

图4表示具体的计算例子。图4是表示从DDS电路4输出的基准频率的例子的表图。

如图4所示,例如在信道编号为0,分频比为133的情况下,基准频率(在图中记载为“DDS输出频率”)为15.03759MHz,即使是相同的信道编号0,在分频比137的情况下,为14.59854MHz。在本PLL电路中,如图2的分频比表所规定的那样,即使是相同的信道编号,由于温度的不同,最优的分频比也不同,因此,从DDS电路4输出的基准频率也不同。

另外,DDS电路4的控制部件41根据计算出的基准频率的值,输出正弦波的数据,由D/A变换器变换为模拟信号,并经由滤波器将模拟正弦波信号作为基准频率信号输出到PLLIC2。

由此,在DDS电路4中,能够与信道编号或使用温度对应地,根据寄生特性良好的分频比,生成基准频率信号。

[本PLL电路的寄生特性:图5]

接着,使用图5,说明本PLL电路的0~600信道的VCO1的输出寄生特性。图5是本PLL电路的VCO1的常温时的输出寄生特性的示意说明图。

如图5所示可以认为,在本PLL电路中,将对每个信道编号最优的分频比设定到PLLIC2,与之对应地改变DDS电路4的基准频率,由此,在全部信道编号中能够得到比图9的一般的PLL电路的寄生特性更良好的特性。

另外,在图5中,只表示出常温时,但低温时和高温时也成为比现有技术更良好的输出寄生特性。

[本PLL电路的适用例子:图6]

接着,使用图6,说明本PLL电路的适用例子。图6是适用了本PLL电路的数字控制PLL电路的结构框图。

如图6所示,适用了本PLL电路的数字控制PLL电路具备分频器11、A/D变换器12、相位比较器15、数字滤波器16、D/A变换器17,来代替图1的PLLIC2,VCO1、DDS电路14、模拟滤波器18与图1的PLL电路相同。

控制电路13与图1的PLL电路的控制电路3一样,具备温度传感器和分频比表,向A/D变换器12和D/A变换器17指示输出的定时这一点与图1的PLL电路不同。

另外,数字控制PLL电路的控制电路13与图1的PLL电路的控制电路3一样,根据输入的信道编号和检测出的温度数据,从分频比表读取最优的分频比,设定到分频器11。

同时,控制电路13向DDS电路14输出信道编号和分频比,在DDS电路14中,根据输入的信道编号和分频比,计算出基准频率,将正弦波数据输出到相位比较器15。

简单地说明上述结构的数字控制PLL电路的动作。

由分频器11以从控制电路13指定的分频比(N)对VCO1的输出信号进行分频,按照指定的定时在A/D变换器12中进行A/D变换,并输入到相位比较器15。

在相位比较器15中,对来自DDS电路14的基准频率和来自A/D变换器12的输出数据的相位进行比较,检测相位差,由数字滤波器16对相位差信号进行滤波,按照指定的定时在D/A变换器17中变换为模拟信号,在模拟滤波器18中进行频带限制,将控制电压施加到VCO1。

在适用了本PLL电路的数字控制PLL电路中,由于对分频器11和DDS电路14设定与温度和信道对应的最优的分频比,所以具有使VCO1的输出具有良好的寄生特性的效果。

[实施例的效果]

根据本发明的实施例的PLL电路,是以下这样的PLL电路,在控制电路3中设置温度传感器31,与温度对应地具备存储了每个信道的寄生特性最好的分频比的分频比表32,控制电路3根据从外部输入的信道编号、由温度传感器31检测出的温度数据,从分频比表32读取对应的分频比并设定到PLLIC2,将分频比和信道编号设定到DDS电路4,DDS电路4根据所设定的分频比和信道编号,计算出基准频率的值,生成基准频率信号,因此,具有以下的效果:无论在怎样的温度和信道下,都能够防止PLLIC2和DDS电路4中的寄生特性的恶化,能够使VCO输出的寄生特性良好。

另外,在本实施例中,与温度对应地具备设置在控制电路3中的分频比表,但在根据使用本PLL电路的环境而限制温度区域的情况下(例如常温等),也可以只存储与该温度区域对应的分频比。

另外,在因温度造成的特性的变动大的情况下,也可以增多温度区域的区分。

本发明适用于能够提高寄生特性的PLL电路。

Claims (5)

1.一种PLL电路,具备振荡产生与控制电压对应的频率的电压控制振荡器,该PLL电路的特征在于包括:

基准频率生成电路,输出与信道编号对应的一定的频率;

相位比较单元,对按照设定了的分频比对上述电压控制振荡器的输出频率进行了分频的频率和上述基准频率生成电路的输出频率进行比较而输出相位差;

循环滤波器,根据上述相位差而生成控制电压;

控制部件,具备对每个信道编号存储了上述电压控制振荡器的输出的寄生特性良好的分频比的分频比表,其中如果从外部输入了信道编号,则从上述分频比表读取与上述输入的信道编号对应的分频比,并设定到上述相位比较单元,并且对上述基准频率生成电路设定上述信道编号和上述分频比,其中

在控制部件中具备测定周围的温度的温度传感器,

分频比表与温度对应地对每个信道编号存储了电压控制振荡器的输出的寄生特性良好的分频比,

上述控制部件从上述分频比表中读取与输入的信道编号和由上述温度传感器检测出的温度对应的分频比,

上述基准频率生成电路根据上述信道编号和上述分频比计算出基准频率的值,并生成与计算出的该值对应的基准频率。

2.根据权利要求1所述的PLL电路,其特征在于:

相位比较单元是将电路集成在单一芯片中的PLL集成电路。

3.根据权利要求1或2所述的PLL电路,其特征在于:

基准频率生成电路具备对应地存储信道编号和电压控制振荡器的输出频率的表,如果输入了信道编号和分频比,则从对应地存储信道编号和电压控制振荡器的输出频率的上述表中读取与所输入的信道编号对应的电压控制振荡器的输出频率,根据上述电压控制振荡器的输出频率和所输入的分频比,将上述电压控制振荡器的输出频率除以上述所输入的分频比,计算出基准频率的值。

4.根据权利要求1所述的PLL电路,其特征在于:

相位比较单元具备:

按照所设定的分频比对电压控制振荡器的输出频率进行分频的分频器;

将上述分频器的输出变换为数字信号的A/D变换器;

对上述A/D变换器的输出和基准频率进行比较的相位比较器;

对上述相位比较器的输出进行频带限制的数字滤波器;

将上述数字滤波器的输出变换为模拟信号的D/A变换器,

控制部件向上述分频器设定分频比,

基准频率生成电路将所生成的基准频率输出到上述相位比较器。

5.根据权利要求4所述的PLL电路,其特征在于:

基准频率生成电路具备对应地存储信道编号和电压控制振荡器的输出频率的表,如果输入了信道编号和分频比,则从对应地存储信道编号和电压控制振荡器的输出频率的上述表中读取与所输入的信道编号对应的电压控制振荡器的输出频率,根据上述电压控制振荡器的输出频率、所输入的分频比,将上述电压控制振荡器的输出频率除以上述所输入的分频比,计算出基准频率的值。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009141116 | 2009-06-12 | ||

| JP2009-141116 | 2009-06-12 | ||

| JP2010081506A JP4850959B2 (ja) | 2009-06-12 | 2010-03-31 | Pll回路 |

| JP2010-081506 | 2010-03-31 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN101924552A CN101924552A (zh) | 2010-12-22 |

| CN101924552B true CN101924552B (zh) | 2013-08-07 |

Family

ID=43305900

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN2010102029063A Active CN101924552B (zh) | 2009-06-12 | 2010-06-11 | Pll电路 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8446192B2 (zh) |

| JP (1) | JP4850959B2 (zh) |

| CN (1) | CN101924552B (zh) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4933635B2 (ja) * | 2010-02-19 | 2012-05-16 | 日本電波工業株式会社 | Pll回路 |

| JP5863395B2 (ja) | 2011-11-02 | 2016-02-16 | 日本電波工業株式会社 | 発振器 |

| JP2013131985A (ja) * | 2011-12-22 | 2013-07-04 | Anritsu Corp | 信号発生装置及び信号発生方法 |

| US9647672B2 (en) * | 2013-11-25 | 2017-05-09 | Nanowave Technologies Inc. | Digitally compensated phase locked oscillator |

| JP6720532B2 (ja) * | 2016-01-06 | 2020-07-08 | セイコーエプソン株式会社 | 回路装置、発振器、電子機器及び移動体 |

| JP7009113B2 (ja) * | 2017-08-23 | 2022-02-10 | 横河電機株式会社 | 交流信号発生器 |

| DE102019201411B3 (de) | 2019-02-04 | 2020-06-25 | Infineon Technologies Ag | Synchronisation einer integrierten Schaltung mit Sensor |

| US11621645B2 (en) * | 2020-06-04 | 2023-04-04 | Stmicroelectronics International N.V. | Methods and device to drive a transistor for synchronous rectification |

| JP7617801B2 (ja) | 2021-04-07 | 2025-01-20 | 三菱電機株式会社 | 位相同期回路、送信機、受信機、および位相同期回路の制御方法 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1117672A (zh) * | 1994-05-09 | 1996-02-28 | 日本电气株式会社 | Pll频率合成器 |

| CN1169622A (zh) * | 1996-06-28 | 1998-01-07 | 三菱电机株式会社 | 频率合成器 |

| CN101093995A (zh) * | 2006-06-19 | 2007-12-26 | 日本电波工业株式会社 | Pll振荡电路 |

| CN101421929A (zh) * | 2006-02-24 | 2009-04-29 | 日本电波工业株式会社 | Pll电路 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6335017A (ja) * | 1986-07-30 | 1988-02-15 | Japan Radio Co Ltd | 無線周波数安定化装置 |

| JP3344790B2 (ja) * | 1993-10-28 | 2002-11-18 | アイコム株式会社 | 周波数シンセサイザ |

| JPH098551A (ja) * | 1995-06-20 | 1997-01-10 | Fujitsu Ltd | 高安定発振回路 |

| JPH0918336A (ja) * | 1995-06-26 | 1997-01-17 | Yaesu Musen Co Ltd | Pll回路制御方式 |

| JP3395529B2 (ja) * | 1996-06-28 | 2003-04-14 | 三菱電機株式会社 | 周波数シンセサイザ |

| JP2003069426A (ja) | 2001-08-23 | 2003-03-07 | Matsushita Electric Ind Co Ltd | 周波数シンセサイザー |

| JP2004166179A (ja) | 2002-09-17 | 2004-06-10 | Nec Kansai Ltd | 無線通信用半導体集積回路装置 |

| JP2007208367A (ja) | 2006-01-31 | 2007-08-16 | Kenwood Corp | 同期信号生成装置、送信機及び制御方法 |

| JP4824591B2 (ja) * | 2007-02-05 | 2011-11-30 | 日本電波工業株式会社 | 同期掃引シンセサイザ |

| US7609122B2 (en) * | 2007-10-05 | 2009-10-27 | Silicon Storage Technology, Inc. | Method and system for calibration of a tank circuit in a phase lock loop |

-

2010

- 2010-03-31 JP JP2010081506A patent/JP4850959B2/ja active Active

- 2010-06-11 US US12/801,498 patent/US8446192B2/en active Active

- 2010-06-11 CN CN2010102029063A patent/CN101924552B/zh active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1117672A (zh) * | 1994-05-09 | 1996-02-28 | 日本电气株式会社 | Pll频率合成器 |

| CN1169622A (zh) * | 1996-06-28 | 1998-01-07 | 三菱电机株式会社 | 频率合成器 |

| CN101421929A (zh) * | 2006-02-24 | 2009-04-29 | 日本电波工业株式会社 | Pll电路 |

| CN101093995A (zh) * | 2006-06-19 | 2007-12-26 | 日本电波工业株式会社 | Pll振荡电路 |

Non-Patent Citations (2)

| Title |

|---|

| JP特开平7-131343A 1995.05.19 |

| JP特开平9-8551A 1997.01.10 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4850959B2 (ja) | 2012-01-11 |

| US8446192B2 (en) | 2013-05-21 |

| US20100315137A1 (en) | 2010-12-16 |

| JP2011019208A (ja) | 2011-01-27 |

| CN101924552A (zh) | 2010-12-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101924552B (zh) | Pll电路 | |

| US5898325A (en) | Dual tunable direct digital synthesizer with a frequency programmable clock and method of tuning | |

| JP5694696B2 (ja) | 周波数シンセサイザ装置及び変調周波数変位調整方法 | |

| US9215062B1 (en) | Low-noise flexible frequency clock generation from two fixed-frequency references | |

| US8170171B2 (en) | Communication semiconductor integrated circuit | |

| US7253691B2 (en) | PLL clock generator circuit and clock generation method | |

| KR100894236B1 (ko) | Pll 회로, pll 회로의 간섭 방지 방법 및 이 pll회로를 탑재한 광디스크 장치 | |

| CN116671015A (zh) | 数字到时间转换器的参数误差校准 | |

| CN113692708B (zh) | 用于产生可控频率的产生器和方法 | |

| US7283002B2 (en) | Phase locked loop with a modulator | |

| JP2008172512A (ja) | 周波数シンセサイザ及びフェーズロックループ、並びにクロック生成方法 | |

| CN101421929A (zh) | Pll电路 | |

| CN102163971B (zh) | Pll电路 | |

| CN105765867A (zh) | 用于校准频率合成器的方法和装置 | |

| WO2014109974A2 (en) | Method and apparatus for synthesis of wideband low phase noise radio frequency signals | |

| EP2890013A1 (en) | Phase locked loop and control method thereof | |

| KR20100039003A (ko) | 위상 계산 기반의 고속 주파수 비교를 이용한 브이씨오 보정 장치 및 방법 | |

| JP2009004868A (ja) | 拡散スペクトラムクロック生成装置 | |

| TWI530084B (zh) | 用於降低時脈分佈系統之寄生之方法 | |

| JP4499009B2 (ja) | 分周回路、クロック生成回路、およびそれを搭載した電子機器 | |

| US10771071B1 (en) | Redundant DCO tuning with overlapping fractional regions | |

| JP2006262520A (ja) | クロック生成回路、pll及びクロック生成方法 | |

| JP2004312247A (ja) | ローカル信号発生装置 | |

| JP2021145285A (ja) | Pll回路及び送信装置 | |

| JP2018061117A (ja) | 周波数シンセサイザ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant |