CN101395725B - 光电子半导体芯片 - Google Patents

光电子半导体芯片 Download PDFInfo

- Publication number

- CN101395725B CN101395725B CN200680053614XA CN200680053614A CN101395725B CN 101395725 B CN101395725 B CN 101395725B CN 200680053614X A CN200680053614X A CN 200680053614XA CN 200680053614 A CN200680053614 A CN 200680053614A CN 101395725 B CN101395725 B CN 101395725B

- Authority

- CN

- China

- Prior art keywords

- substrate

- semiconductor chip

- semiconductor layer

- layer sequence

- contact layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/20—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a particular shape, e.g. curved or truncated substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/36—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes

- H01L33/40—Materials therefor

- H01L33/42—Transparent materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/26—Materials of the light emitting region

- H01L33/30—Materials of the light emitting region containing only elements of group III and group V of the periodic system

- H01L33/32—Materials of the light emitting region containing only elements of group III and group V of the periodic system containing nitrogen

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/36—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes

- H01L33/40—Materials therefor

- H01L33/405—Reflective materials

Abstract

提供一种具有半导体层序列(2)的光电子半导体芯片(1),该半导体层序列(2)包括适于产生辐射的有源区(3)并具有横向主延伸方向,其中,半导体层序列通过具有侧表面(17)的衬底(4)来布置,该侧表面具有相对于主延伸方向成斜角的侧表面区域(18)和/或切口(21),并且,半导体芯片具有辐射透射性并且导电的接触层(5)。

Description

本发明涉及光电子半导体芯片,特别涉及发射辐射的半导体芯片。

本发明的一个目的是提供改进的光电子半导体芯片,特别是具有增加的耦合输出(couple-out)效率的半导体芯片。

通过具有独立专利权利要求的特征的半导体芯片来实现该目的。从属专利权利要求涉及有利的实施方案。

根据至少一个实施方案,光电子半导体芯片包括具有适于产生辐射的有源区的半导体层序列,其中,半导体层序列优选具有横向主延伸方向。半导体层序列优选布置在衬底上。衬底可包括在其上生长(特别是外延生长)半导体层序列的生长衬底,或者可例如通过图案化或某种其它处理由所述生长衬底形成或由其来具体实现。特别地,衬底可被减薄。通过减薄衬底有利地减小芯片的结构高度。优选地,衬底,特别是例如处理、减薄的衬底在力学上使半导体层序列稳定化。

根据至少一个实施方案,半导体层序列特别是有源区包含或基于氮化物化合物半导体材料。

在本文中,“基于氮化物化合物半导体材料”是指半导体层序列或其至少一个层包含氮化物III/V化合物半导体材料,优选AlnGamIn1-n-mN,其中0≤n≤1,0≤m≤1,并且n+m≤1。这里优选n≠0和/或m≠0的情况。还优选n≠1和/或m≠0的情况。在这种情况下,所述材料不必具有根据上述公式在数学上精确的组成。而是,它可具有基本上不改变AlnGamIn1-n-mN材料的特征物理性能的一种或更多种掺杂剂和添加成分。但是,出于简化的原因,上式仅包含晶格的基本成分(Al、Ga、In、N),尽管它们可部分地被少量的其它物质置换。

氮化物化合物半导体材料特别适于产生在紫外和可见光谱范围特别是从蓝色到绿色光谱范围中的辐射。

对于基于氮化物化合物半导体材料的半导体层序列,包含碳化硅(SiC)、氮化镓(GaN)、氮化铝(AlN)或蓝宝石的衬底特别适于用作(生长)衬底。

根据至少一个实施方案,有源区包括单或多量子阱结构。在本申请的上下文中,表述量子阱结构包括其中由于限域效应而导致电荷载流子可经受或优选经受其能态量子化的任何结构。特别地,表述量子阱结构不包括关于量子化的维度的指示。因此它特别包含量子阱、量子线和量子点以及这些结构的任意组合。量子阱结构特别适于以高内部量子效率产生辐射。

根据至少一个实施方案,衬底对于在有源区中产生的辐射是辐射透射性的。特别地,可以由对于所产生的辐射为透射性的材料来形成衬底。与明显吸收性的衬底相比,这有利于通过衬底将辐射从半导体芯片耦合输出。半导体芯片可由此以简化的方式形成为体积发射器。在体积发射器的情况下,与表面发射器即主要通过半导体层序列的表面、特别是单个表面从芯片耦合输出辐射、例如从芯片耦合输出90%或更多的辐射的半导体芯片不同,还通过衬底从芯片耦合输出大比例的辐射。与表面发射器相比,在体积发射器的情况下,半导体芯片的耦合输出区域上的表面亮度降低,其中,由于耦合输出区域上的降低的表面亮度,其中包含半导体芯片的辐射透射性封装的变色或混浊(由于高的亮度所导致)例如褐变的风险减少。

在半导体芯片用于产生高能量、相对短波例如蓝色或紫外辐射的情况下,这是特别有利的。例如对于基于氮化物化合物半导体的半导体芯片,常常是这种情况。包含反应树脂例如环氧树脂或丙烯酸树脂的封装在高能辐射的照射下特别迅速地变混浊,使得体积发射器在此提供特别的优点。通过包含硅氧烷或硅树脂并且以增加的辐射稳定性为特征的封装,可更大程度地减少辐射导致封装的变色或混浊的风险。

优选地,半导体芯片在半导体层序列和衬底之间没有例如以金属方式形成(embodied)的或形成为布拉格镜的反射体,由此有利于辐射从半导体层序列进入衬底并由此有利于体积发射器的形成。

根据至少一个实施方案,形成衬底的表面特别是面对半导体层序列的衬底的侧面和/或表面作为半导体芯片的辐射耦合输出区域。如果形成面对半导体层序列的衬底表面作为辐射引出区域,那么未被半导体层序列覆盖的所述表面的部分区域优选形成所述表面的耦合输出区域。

根据至少一个实施方案,衬底的折射率大于或等于有源区的折射率,和/或衬底的折射率大于或等于所述层序列的在面对衬底一侧上的结束半导体层序列的半导体层的折射率,特别是限定所述半导体层序列边界的所述层序列的半导体层的折射率。由于在与衬底的界面上的反射减少或全反射可忽略,因此可有利于将辐射从半导体层序列辐射传递到衬底中。对于有源区的折射率,如果适当的话,可使用形成有源区的各层的折射率的平均值,例如算术或几何平均值。

对于氮化物化合物半导体材料,包含SiC或GaN的衬底是特别合适于折射率的以上关系。

根据至少一个实施方案,半导体芯片具有侧表面,其中,侧表面优选具有相对于半导体层序列的横向主延伸方向成斜角的侧表面区域和/或切口(cutout)。所述侧表面优选由衬底的侧表面形成。此外,该侧表面优选沿侧向限定半导体芯片的边界。切口优选从沿半导体层序列的方向远离半导体层序列的衬底表面延伸,特别是从所述表面开始。

通过切口和/或成斜角的侧表面,可增加在半导体层序列中产生并直接地(即没有在衬底中的(多次)反射的情况下)通过切口和/或侧表面从衬底耦合输出的辐射的比例。由此有利地增加通过衬底耦合输出的辐射功率并因此增加光电子半导体芯片的耦合输出效率。在这种情况下,证明成斜角的侧表面区域与半导体层序列形成锐角是特别合适的。

特别是在成斜角的侧表面的成斜角的区域中,随着到半导体层序列的距离增加,衬底可逐渐变细。为此,侧表面有利地以适当的方式呈斜角。在衬底逐渐变细的区域中和/或在切口的区域中,侧表面可具有楼梯状结构或者是弯曲的。

特别地,可在从晶片组件(assemblage)将芯片单一化(singuating)的过程中,通过例如锯片的适当分离工具(优选根据切口和/或斜角确定形状)制造斜角和/或切口部分。可因此相应地锯开衬底。

可通过相对于半导体层序列倾斜地延伸的侧表面区域并且优选通过该侧表面的其它侧表面区域形成切口。优选地,所述其它侧表面区域相对于主延伸方向以一定的角度倾斜,但与首先提到的侧表面区域不同,或者基本上垂直于半导体层序列特别是主延伸方向延伸。当从半导体层序列看时,所述其它侧表面区域优选设置在首先提到的侧表面区域的下游。

根据至少一个实施方案,衬底在远离半导体层序列的一侧的横截面比在面对半导体层序列的一侧的横截面小。

优选地,衬底具有两个侧表面,其中,从远离半导体层序列的衬底表面开始的这些侧表面的两个侧表面区域沿基本上相互平行、例如相互形成小于等于5°特别是小于等于2°的角度或相互平行的半导体层序列的方向延伸。可通过安装工具在基本上平行的侧表面上以简化的方式抓住这种半导体芯片,所述安装工具例如为用于在外部连接导体、如用于有线辐射部件或表面可安装部件的外部连接导体上安装芯片的安装工具。

此外,衬底可在半导体层序列的一部分上具有与半导体层序列的横向主延伸方向基本上相垂直的侧表面区域,例如偏离直角5°或更小、特别是2°或更小或者与所述横向主延伸方向垂直的侧表面区域。该侧表面区域优选合并到切口和/或成斜角的侧面区域中。换句话说,当从半导体层序列观看时,成斜角的侧表面区域和/或切口优选设置在垂直或基本上垂直延伸的侧表面区域的下游。

根据至少一个实施方案,半导体芯片具有辐射透射性并且导电的接触层。由于该接触层对于在有源区中产生的辐射的辐射透射性,因此从半导体芯片耦合输出的辐射可增加。接触层有利地与半导体层序列的有源区电连接。优选地,接触层(特别是在整个区域之上和/或直接地)连接半导体芯片。

根据至少一个实施方案,接触层包含辐射透射性并且导电的氧化物(TCO:透明导电氧化物),特别是金属氧化物,例如为诸如InO的铟锡氧化物、诸如SnO2的锡氧化物、诸如InSnO的氧化铟锡(ITO)或诸如ZnO的锌氧化物。辐射透射性的导电氧化物的特征在于高的辐射透射性同时沿横向具有高的导电率。通过与接触层电连接的例如基于金属或合金的连接件,可在比较小的区域上促使电流进入接触层中。所述的电流可以以较低的电阻在接触层中均匀地横向分布,并在较大的区域上注入半导体层序列中。

包含TCO的接触层可沿横向具有大于或等于40Ωsq的导电率、优选大于或等于100Ωsq的导电率、特别优选大于或等于200Ωsq的导电率。

为了增加沿横向的导电率,接触层可被掺杂。例如,A1适于用作氧化锌的掺杂剂,而Sb例如适于氧化锡。

对于沿横向的高导电率,包含TCO的接触层,特别是包含氧化铟锡的接触层,优选例如以氧缺陷的形式具有亚化学计量的组成。

包含ITO的接触层可进一步包含铟缺陷。铟缺陷可至少部分地被锡占据。这种实施方案特别适合于沿横向的高导电率。

优选地,包含ITO的接触层中氧化铟比例大于氧化锡比例。

结果,可以以简化的方式总体获得n导电类型的接触层。

ITO或氧化锌特别适于与p-导电半导体材料形成电接触。氧化锡特别适于与n-导电半导体材料形成接触。通过辐射透射性的导电氧化物,能够形成辐射透射性的接触层作为具有高的横向导电率的电流扩散层,该电流扩散层有利于良好的、优选无势垒的电接触特别是欧姆接触,也就是说,有利于在接触层和半导体层序列之间具有基本上线性的电流-电压特性的接触。

为了将电流均匀地施加到半导体层序列中,接触层有利地形成为连续的(特别是不间断的)层。此外,接触层覆盖在半导体层序列之上或覆盖半导体层序列,如果适当的话,优选完全地与具有较小面积的边缘侧切口分开。

优选地,接触层布置在半导体层序列的远离衬底的表面上,和/或,接触层邻接半导体层序列的p导电半导体层。

根据至少一个实施方案,在接触层和有源区之间形成隧道接触(tunnel contact)。隧道接触可特别地布置在接触层和有源区之间。隧道接触优选具有以单块方式集成到半导体层序列中的一个或多个(特别是掺杂的)隧道接触层。

隧道接触的隧道接触层优选特别是直接地邻接接触层。在半导体芯片的操作中,与省却隧道接触层的半导体芯片相比,通过有源区和接触层之间的隧道接触层,能够降低接触层/半导体层序列的结上的电压降(“损失电压”)。隧道接触层优选具有与邻接隧道接触的半导体层序列的半导体层不同的导电类型。如果例如以p导电方式形成所述半导体层,那么以n导电方式形成隧道接触层。隧道接触层优选直接邻接接触层。对于半导体芯片的预定的操作电压,由于通过隧道接触减少电压损失,因此在有源区中转变成辐射功率的电功率可增加。

隧道接触层优选具有30nm或更小、特别是优选20nm或更小的厚度。此外,隧道接触层的厚度优选大于或等于3nm。这种厚度已被证明是特别有利的。

隧道接触优选包含其他隧道接触层。通过所述其他隧道接触层,可更大程度上地减少在半导体芯片的操作中的电压损失。

关于厚度,优选根据对于以上的隧道接触层详述的厚度范围来形成所述其他的隧道接触层。

如果隧道接触包含多个隧道接触层,那么以单块方式集成到半导体层序列中的两个隧道接触层优选具有不同的导电类型。

所述其它隧道接触层优选具有与在有源区的一部分上邻接隧道接触(特别是所述其它隧道接触层)的半导体层序列的半导体层相同的导电类型。作为例子,所述其它隧道接触层为此以p导电方式形成。

优选以高度掺杂的方式(p+或n+)形成掺杂的隧道接触层。因此,隧道接触层中的掺杂剂浓度可为1×1019cm-3或更大、优选1×1020cm-3或更大。

隧道接触还优选形成为具有两个不同导电类型的以单块方式集成的隧道接触层作为隧道二极管(tunnel diode)。

当在没有插入的隧道结例如在接触层和半导体层序列之间的关键阻挡pn结(blocking pn junction)的情况下,在接触层和半导体层序列之间的势垒比较高时,隧道接触是特别有利的。

这种明显阻碍电荷载流子进入半导体层序列中或明显有助于损失电压的阻挡pn结可在接触层的n导电TCO(例如n导电ITO)与半导体层序列的直接邻接所述接触层的p导电半导体层(例如基于氮化物化合物半导体的层)之间形成。

通过隧道接触,可以以简单的方式在接触层和半导体层序列之间制造具有比较低的电压损失的电接触,特别是具有欧姆电流-电压特性的接触。

根据至少一个实施方案,在隧道接触层和有源区之间布置中间层。优选以未掺杂的方式形成中间层。中间层可形成为势垒层,该势垒层防碍或完全阻挡掺杂剂从隧道接触层通过势垒层或通过势垒层扩散到隧道接触层中。作为例子,中间层可用作例如Mg的受体的势垒层,利用该受体掺杂布置在远离隧道接触层的半导体层序列的一侧上(特别是远离隧道接触层的中间层的一侧上)的半导体层掺杂。

掺杂剂扩散到隧道接触层中,特别是从具有与隧道接触层的导电类型不同的导电类型的半导体层序列的区域扩散到隧道接触层中可降低隧道接触层的电流承载能力,并由此降低芯片的电流承载能力,并因此(伴随地)导致芯片在常规的操作中失效。中间层优选集成到隧道接触中,并且特别优选布置在具有不同的导电类型的两个隧道接触层之间。中间层优选形成为阻止相应的掺杂剂从上述的其它隧道接触层渗透到隧道接触层中的势垒层。

此外,中间层优选具有10nm或更小的厚度。

如果适当的话,隧道接触的隧道接触层还可形成为多层结构,例如,形成为超晶格结构。

作为设置具有不同导电类型的两个隧道接触层的隧道接触的替代方案,如果适当的话,也可以在接触层和半导体主体之间形成优选为欧姆接触的良好电接触,而没有隧道接触。

特别地,为此,可在半导体主体中布置邻接辐射透射性接触层的连接层(connection layer)。所述连接层被有利地最优化,用于与辐射透射性接触层形成接触。优选以掺杂的方式形成连接层。为了形成与接触层的接触,已证明连接层在面对接触层的一侧并且特别是在连接层的邻接接触层的接触区域中具有与布置在更远离接触层的连接层的区域并且特别是更接近有源区的区域不同的掺杂剂浓度是特别有利的。优选地,连接层中的掺杂剂浓度在接触层的一部分上比在有源区的一部分上更大。

连接层中不同掺杂剂浓度可特别地明显地相互偏离。两种掺杂剂浓度优选相互偏离30%或更大、特别优选40%或更大。在接近接触层的区域特别是直接接触区域中,连接层中掺杂剂浓度可为连接层的更远离接触层和布置为更接近有源区的区域中掺杂剂浓度的1.3倍或更大、优选1.4倍或更大。

连接层优选包含氮化物化合物半导体材料。例如,连接层可包含例如GaN或由其构成。此外,优选形成连接层,使得它以p导电方式被掺杂。已证明使用Mg作为p型掺杂的受体是特别合适的。

连接层中掺杂剂浓度为3×1019cm-3或更高、例如为3×1019cm-3~5×1020cm-3已被证明特别适于接触层和连接层之间的低接触电阻。在远离接触层的连接层的区域中,所述连接层可具有2×1019cm-3或更低的掺杂剂浓度。特别是在与横向主延伸方向垂直的方向上,与掺杂剂浓度在整个层上均匀地较高的情况相比,在与关于接触层的边界区域相比时连接层内的掺杂剂浓度降低的情况下,连接层中的自由电荷载流子的浓度以及由此沿有源区的方向的导电率可更高。但是,关于接触层的接触区域中高掺杂剂浓度使得相对于有源区更容易形成接触层的低电阻、并因此低损失的电接触。特别地,可由此以简化的方式获得与半导体主体的欧姆电接触。

连接层的厚度可以为30nm或更大,特别是优选50nm或更大或者甚至100nm或更大。

根据至少一个实施方案,半导体芯片具有电连接,该电连接件优选与辐射透射性导电接触层进行电连接。所述连接件可形成为接合焊盘,也就是说用于与接合线相接触。优选地,所述连接件包含例如Au的金属。特别地可以以金属的方式或以基于合金的方式形成所述连接件。所述连接件有利地与有源区电连接。

优选地,半导体芯片的连接件布置在远离衬底的半导体层序列的一侧和/或远离半导体层序列的接触层的一侧。

根据至少一个实施方案,在所述电连接件和半导体层序列之间,特别是在接触层和所述连接件之间布置反射体层。反射体层优选包含例如Al或Ag的金属。这些金属的特征在于对于短波辐射具有特别高的反射率。优选以金属的方式或以基于合金的方式形成反射体层。

通过反射体层,可减少所述连接件中辐射的吸收。此外,辐射可通过反射体层反射回到半导体层序列中并从半导体芯片耦合输出,而不是可能在所述连接件中被吸收。结果,能够增加半导体芯片的耦合输出效率,即在半导体芯片中产生的辐射功率与从半导体芯片耦合输出的辐射功率之比。

根据至少一个实施方案,在所述连接件和接触层之间、优选在反射体层和接触层之间配置粘接促进层。粘接促进层优选增加所述连接件和/或反射体层与半导体芯片的粘接,特别是反射体层与接触层的粘接。

粘接促进层优选包含例如Pd或Pt的金属,并特别优选以金属的方式或以基于合金的方式形成。

为了使得在粘接促进层中吸收的辐射功率有利地保持较低,优选以透明或半透明的方式形成粘接促进层。粘接促进层的厚度优选为小于3nm、特别优选小于1nm。可以特别地以岛状方式(优选用多个粘接促进岛)形成粘接促进层。对于促进粘接来说,连续的层是不必要的。

根据至少一个实施方案,半导体芯片形成为发光二极管(luminescence diode),例如发光二极管(light-emitting diode)或激光二极管,其中,体积发射器(volume emitter)的实施方案对于发光二极管当然是特别有利的。

根据至少一个实施方案,半导体芯片包含优选与有源区电连接的反电连接件(electrical counter-connection)。可通过所述电连接件和反电连接件制成与半导体芯片的电接触。所述反连接件优选包含金属并且特别优选以金属的方式或以基于合金的方式形成。

此外,所述电连接件和反电连接件优选布置在半导体层序列的相反的两侧。半导体芯片可因此具有在所述电连接件和反电连接件之间沿垂直方向导电的结构。这有利于简单可靠地将半导体芯片安装在外部连接导体上。

与两个连接件均布置在半导体层序列的同一侧的配置相比,可由此在半导体芯片的制造中选择较小的芯片布置网(chip grid),由此-从半导体晶片的半导体层结构-能够获得比在半导体层序列的同一侧布置所述电连接件和反电连接件的半导体芯片的情况下数量更多的用于各单个半导体芯片的半导体层序列。由于连接件布置,连接件的后一种布置需要更大面积的半导体层序列,用于单个芯片。通过在半导体层序列的不同侧上布置连接件,相比之下能够减少半导体层序列的面积。因此增加由半导体晶片得到的半导体芯片的产量。

优选地,半导体芯片的反电连接件布置在远离半导体层序列的衬底表面上。为了使反电连接件与有源区电连接,有利地以导电的方式形成衬底。如果适当的话,为此,可以例如以掺杂氮的SiC衬底的形式适当地对衬底进行掺杂。

这种反电连接件有利于例如通过粘接剂接合或焊接将芯片电连接到例如用于光电子元件(例如辐射元件或表面可安装元件)的外部连接导体上。表面可安装元件可以以特别地简单且节省空间的方式安装在例如印刷电路板的外部元件载体上。通过在半导体层序列的不同侧上布置的芯片的电连接件和反电连接件,可能的附加引线接合可被省去,这是因为连接件中之一(优选为反连接件)可在没有引线连接情况下通过例如焊料或粘合层的连接层而电连接到并且特别是固定到外部连接导体上。

根据至少一个实施方案,在远离半导体层序列的一侧上,衬底完全或部分地具有镜面层。镜面层优选包含例如Al或Ag的金属,并且特别优选以金属的方式或基于合金的方式形成。特别地,可例如通过溅射或气相淀积将镜面层施加到衬底上。可通过镜面层将辐射反射回到衬底中。由此有利地减少外部连接导体中的吸收损失。此外,穿过面对半导体层序列的衬底表面的辐射功率特别是通过所述表面耦合输出的辐射功率可增加。镜面层可布置在反连接件和衬底之间或横靠所述反连接件。

优选地,衬底的侧表面部分或完全地被镜面涂覆(mirror coated)。作为例子,切口和/或成斜角的侧面区域可部分或完全地镜面涂覆。

特别地,设置在远离半导体层序列的衬底一侧上的镜面层可沿衬底侧表面的成斜角的侧面区域和/或沿口延伸作为连续层。

根据至少一个实施方案,衬底的表面,特别是面对半导体层序列的衬底表面、面对接触层的半导体层序列的表面和/或远离半导体层序列的接触层的表面具有突起和凹陷。可通过规则的特别是优选周期性出现的结构或不规则的粗糙化来形成突起和凹陷。例如可通过优选使用适当掩模的蚀刻或喷砂形成这种结构。作为例子,例如反应离子蚀刻(RIE)的干蚀刻,优选使用金属掩模,或不使用掩模的湿化学蚀刻适于不规则的粗糙化,而使用适当掩模的湿化学蚀刻特别适于规则的结构。如果适当的话,还可通过喷砂形成结构化的表面。

根据至少一个实施方案,半导体层序列特别是有源区、中间层和/或隧道接触层或多个隧道接触层包含氮化物化合物半导体材料。

根据至少一个实施方案,以导电的方式形成反射体层和/或镜面层。优选地,反射体层和/或镜面层电连接于所述有源区、连接件和/或反连接件。

根据至少一个实施方案,面对半导体层序列的衬底表面或面对衬底的半导体层序列的表面的面积与横向限定对半导体芯片边界的侧表面特别是衬底的侧表面的面积之比小于或等于2、优选小于或等于1.5、特别优选小于或等于1.2。对于预定边缘长度的芯片,可通过形成为适当厚度的衬底来获得这些比值。

优选地,关于此点,以无斜角的方式和没有任何切口的情况下形成所述侧表面。侧表面优选基本上垂直于半导体层序列的横向主延伸方向和/或面对半导体层序列的衬底表面、例如偏离直角5°或更小,特别是2°或更小或与其垂直。

这种类型的半导体芯片可具有基本上为平行六面体的包封的基本形式。安装在外部连接导体上的平行六面体芯片优选以如下方式安装在连接导体上,使得较长边延伸远离连接导体(“柱状”安装)。

在具有以上规定的面积比的芯片的实施方案中,与半导体芯片平面图中的芯片表面相比较,侧表面优选具有类似的面积或具有更大的面积。由此有利地以大的方式形成通过侧表面可获得的辐射耦合输出区域。因此,该侧表面上的亮度有利地降低。

对于面对半导体层序列的衬底表面或面对衬底的半导体层序列的表面的面积,如果适当的话,例如在对各表面进行图案化的情况下,可以使用沿横向被所述表面覆盖的区域面积。

由于衬底中的波导,可从衬底侧表面耦合输出更大的辐射功率,因此对于具有高折射率的多重波导衬底(如SiC衬底)来说,这种芯片的实施方案是特别有利的。由于侧表面的大面积的实施方案,因此可以以简化的方式降低亮度。对于将辐射从芯片耦合输出,有利地形成侧表面,使得它没有镜面涂敷。

但是,随着衬底厚度增加,特别是在安装位置中,半导体芯片的总高度也增加。随着高度增加而横向尺寸保持相同,会使得更加难以可靠地在连接导体上安装半导体芯片。特别地,由于芯片的重心随着高度增加而向上偏离安装区域,因此将半导体芯片布置在连接导体上时翻倒的风险增加。

根据至少一个实施方案,上述的面积比大于或等于0.5、优选大于或等于0.7、特别优选大于或等于0.8。可由此减少将芯片布置在连接导体上时翻倒的风险。

0.8~1.2(包括端点)的面积比被证明特别适于侧表面上的低亮度和高的安装可靠性。可通过具有立方体状包封的基本形式的芯片获得这种比值。

应当注意,如果适当的话,还可有利地通过衬底的厚度与芯片的边缘长度例如芯片的最大或最小边缘长度之比来替代性地或另外地形成具有较大面积的衬底侧表面。特别地,这样可获得以上规定的面积比。优选地,为此各芯片边缘长度与衬底的厚度之比满足以上规定的关系。此外,衬底的厚度优选沿横向是恒定的。

在衬底较厚的实施方案或根据以上说明的面积的实施方案的情况下,还通过衬底的侧表面多重地耦合输出在镜面层上反射的辐射,所述镜面层优选设置在远离半导体层序列的衬底一侧上。半导体芯片的体积辐射性能可由此得到强化。对于在相比之下较具有更高折射率的衬底(例如包含SiC的衬底)上的基于氮化物化合物半导体的半导体层序列来说,这是特别重要的。在这种半导体芯片中,由于折射率关系,辐射在从半导体层序列传送到衬底中的过程中在与衬底的界面主要向着表面法线被折射并由此通常远离侧表面。与具有较低的折射率的衬底例如蓝宝石衬底相比,入射到镜面层上的辐射功率由此增加。由于衬底的比较厚的实施方案,在镜面层上被反射并通过衬底的侧表面耦合输出的辐射功率可增加。

此外,衬底的多个侧表面,特别是衬底的所有侧表面可满足上述关系。

根据至少一个实施方案,衬底的厚度小于或等于半导体芯片的边缘长度的一半,特别是小于衬底的边缘长度的一半。衬底的厚度优选为最大厚度。并且,衬底的厚度优选沿横向是恒定的。

优选地,衬底的厚度小于半导体芯片的边缘长度的三分之一。为此,衬底可被适当地减薄,例如被蚀刻掉或被磨掉。

可使用特别是沿横向的芯片最小或者特别是最大边缘长度作为边缘长度。

由于相对较薄的衬底,只有比较小比例的辐射直接从半导体层序列入射到衬底的相应较小面积的侧表面上,使得侧表面上的亮度可有利地降低。当与远离半导体层序列的衬底一侧上的镜面层组合时,这是特别有利的,由此,如上所述,辐射可沿半导体层序列的方向并且特别是通过辐射透射性接触层被反射回来。

与具有比较厚的衬底的芯片(参见以上的解释)相比,这种芯片能够以简化的方式可靠地安装。特别是芯片翻倒的风险减少。当通过衬底形成与半导体芯片的电接触时,这种“薄的”芯片还有利地具有低的正向电压。

与半导体层序列相比具有较高的折射率的衬底例如SiC衬底特别适于降低侧表面的亮度。如上所述,射束在穿行进入具有高折射率的衬底中时被多次折射远离侧表面。侧表面上的亮度由此可降低。

在特别有利的实施方案中,半导体芯片包含具有适于产生辐射的有源区和横向主延伸方向的半导体层序列,其中,半导体层序列布置在衬底上,并且半导体芯片具有辐射透射性并且导电的接触层。

在该配置的第一变化方案中,衬底具有侧表面,该侧表面具有关于主延伸方向成斜角的侧面区域和/或切口。

在该配置的第二变化方案中,衬底的折射率大于等于有源区的折射率,和/或衬底的折射率大于或等于在面对衬底的一侧上结束半导体层序列的半导体层的折射率。

在该配置的第三变化方案中,半导体层序列包含氮化物化合物半导体材料,半导体芯片的电连接件和反电连接件布置在半导体层序列的相反的侧面上。

通过根据这些变化方案的半导体芯片,能够大大增加半导体芯片的耦合输出效率。上文详细解释了各个特征的优点,并且这些优点可通过相应组合而更加明显。

根据结合附图对示例性实施方案进行的以下说明,本发明的其它特征、有利的实施方案和便利将变得显而易见。

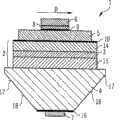

图1表示光电子半导体芯片的示例性实施方案的示意性截面图,

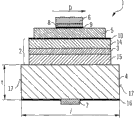

图2表示光电子半导体芯片的另一示例性实施方案的示意性截面图,

图3表示光电子半导体芯片的另一示例性实施方案的示意性截面图,

图4表示光电子半导体芯片的另一示例性实施方案的示意性截面图,

图5表示光电子半导体芯片的另一示例性实施方案的示意性截面图,

图6表示光电子半导体芯片的另一示例性实施方案的示意性截面图,

在图7中,图7A表示光电子半导体芯片的另一示例性实施方案的示意性截面图,图7B和图7C表示该示例性实施方案的两个变化方案,

图8表示光电子半导体芯片的示例性实施方案的示意性平面图。

在附图中,相同的、相同类型的和作用相同的要素具有相同的附图标记。

根据图1~7的示例性实施方案,光电子半导体芯片1均包括包含适于产生辐射的有源区3并具有横向主延伸方向D的半导体层序列2。为了有效地产生辐射,有源区3优选形成为单或多量子阱结构。

可以根据图8所示的平面图来将图1~7所示的半导体芯片形成为平面图。

半导体层序列2布置在衬底4上。优选由生长衬底形成衬底4,在生长衬底上外延生长半导体层序列2。衬底4在力学上使半导体层序列2稳定化并承载它。另外,可例如通过磨掉或蚀刻将衬底减薄。

此外,半导体芯片1包含优选施加到预制的半导体层序列上的辐射透射性的导电性接触层5。接触层5布置在远离衬底4的半导体层序列2的一侧上。优选地,接触层5直接邻接半导体层序列2,尤其是在整个区域上。接触层5导电性地与有源区3连接。并且,接触层5优选形成为连续的、不间断的层。此外,接触层5优选在半导体层序列2之上沿横向主延伸方向在除了边缘侧切除部分以外的基本整个区域上延伸。

可例如通过PVD方法(例如通过优选使用电子束(E束蒸镀)的气相沉积)或溅射从半导体层序列沉积接触层5。这些方法特别适于ITO接触层。CVD方法特别是PECVD方法(PECVD:等离子增强化学气相沉积)也适于接触层特别是ZnO接触层的沉积。

半导体层序列2布置在电连接6和反电连接7之间,电连接6和反电连接7布置在半导体层序列2的不同侧并且有利地与有源区3电连接件。电连接件6布置在远离半导体层序列2的接触层5的一侧上并与接触层电连接。反连接7件布置在远离半导体层序列2的衬底4的一侧上。

连接件6优选形成为接合焊盘并因此用于与接合线电连接,通过该接合线,半导体芯片1可与外部连接导体例如辐射元件或表面可安装元件的外壳的连接导体连接。电连接件6优选与接触层5相比具有较小的面积。特别地,电连接件6优选覆盖接触层5的单邻接区域(singlycontiguous region)。在平面图(参见,图8中的平面图)中,例如可基本上以圆形的方式形成电连接件6。

反电连接件7优选用于通过例如焊料层或粘合层的导电连接层与其他外部连接导体电连接。此外,反电连接件可完全(未明确示出)或部分地覆盖远离半导体层序列的衬底的一侧。

通过在半导体层序列的不同侧上布置连接件6和7,与连接件处于半导体层序列的同一侧,特别是远离衬底的一侧相比,对于具有相同的待耦合输出的辐射功率的半导体芯片,可以以简化的方式选择更小的芯片布置网。而且,由于连接层,因此可以省去另外的引线接合。

反射体层8布置在有源区3和电连接件6之间。有利地形成反射体层8,使得它反射在有源区中产生的辐射。反射体层8优选布置在半导体层序列2和电连接件6之间,特别是接触层5和电连接件6之间。

粘接促进层9布置在电连接件6和有源区3之间。粘接促进层9布置在反射体层8和半导体层序列2之间,特别是反射体层8和接触层5之间。优选地,粘接促进层9一方面直接邻接反射体层8,另一方面直接邻接接触层5。可通过粘接促进层9增加反射体层8与接触层5的粘接。

此外,隧道接触10布置在接触层5和有源区3之间。优选地形成隧道接触10,使得它以单块方式集成到半导体主体中。优选地,隧道接触10包含第一隧道接触层11和第二隧道接触层12(参见,关于图7A的仅作为示例性的详述)。

隧道接触层11和12优选具有不同的导电类型(分别为n导电和p导电)。特别优选地,为此,以不同的方式对隧道接触层进行掺杂。隧道接触层12优选具有与半导体层序列2的半导体层13相同的导电类型,例如为p导电,所述半导体层13邻接有源区3部分上的隧道接触10。优选形成隧道接触层11和12,使得它们被高度掺杂。优选以p导电方式形成隧道接触层12,并且,优选以n导电方式形成隧道接触层11。1×10191/cm3或更大、优选1×10201/cm3或更大的掺杂剂浓度被证明特别适于隧道接触层。通过隧道接触,能够提高优选直接邻接隧道接触的接触层5与有源区的电连接。可通过隧道接触以简化的方式实现具有低电压损失的接触,特别是接触层5和半导体层序列2之间的欧姆接触。

隧道接触层的厚度优选在每一种情况下为3~20nm。

有源区3优选布置在具有不同导电类型的半导体层14和15之间。例如可以以p导电方式形成半导体层14,并且,例如可以以n导电方式形成半导体层15。特别地,半导体层14和15可在每一种情况下具有提高有源区中的电荷载流子分量(component)的势垒或包覆层。可由此增加半导体芯片的内部量子效率。

除了隧道接触层11和12以外,隧道接触10还可具有布置在所述的层之间的未掺杂的中间层(未示出)。所述中间层优选形成为扩散阻挡层,并阻止例如Mg的受体从p导电第二隧道接触层12或p导电半导体层14扩散到n导电第一隧道接触层11中或完全阻止这种扩散。由此可减少由掺杂剂的扩散导致损伤芯片的风险。

此外,一个隧道接触层11和12或多个隧道接触层可形成为多层结构,例如,形成为超晶格结构(未示出)。

中间层优选具有10nm或更小的厚度。如果适当的话,一个单层的中间层的厚度可能已经对于扩散阻挡层来说足够了。

镜面层16布置在远离半导体层序列2的衬底4的表面上。例如可通过溅射或气相沉积将镜面层16施加到例如衬底上。此外,镜面层16可布置在反连接件7和衬底4之间或横靠着所述反连接件。

半导体层序列2优选基于氮化物化合物半导体材料。如上所述,这些材料特别适于产生短波辐射。特别地,隧道接触层11和12、半导体层13、14和15以及有源区3优选包含来自材料体系AlnGamIn1-n-mN的材料。有源区优选包含InGaN。第一隧道接触层11和/或第二隧道接触层12可包含GaN、AlGaN、InGaN或InAlGaN或由其构成。中间层可包含AlN、GaN、AlGaN、InGaN或InAlGaN或由其构成。

电连接件6、反电连接件7、反射体层8、粘接促进层9和/或镜面层16优选包含金属,并且特别优选以金属的方式或基于合金的方式形成。作为例子,Au适合于连接件6和7,Al或Ag由于对于可通过氮化物化合物半导体产生的辐射具有高反射率因而特别适合于反射体层8。Al或Ag相应地适于镜面层16。粘接促进层9优选包含Pt或Pd。这些材料特别适于增进相对于半导体芯片的粘接。

粘接促进层的厚度优选小于或等于1nm。可以特别地以岛状方式形成粘接促进层。

辐射透射性的导电性接触层5优选包含例如ZnO:Al或ITO的TCO材料。尤其适于横向导电率特别高的n导电ITO的是例如具有氧缺陷的亚化学计量组成的ITO或氧化铟与氧化锡在比为90∶10或更大例如为95∶5的ITO。

接触层的厚度优选为100~1000nm,如果同时考虑材料的良好电流扩散和经济使用的话,特别优选为100~300nm。

通过具有比较小的面积的连接件6、反射体层8和粘接促进层9,电流在比较小的注入区域中注入接触层5。由于高横向导电率,因此所述电流沿横向分布在TCO接触层中。尽管电连接件6具有比较小的面积,仍可由此均匀地并且在大的区域上为有源区3供电。同时,与施加在比较大区域上的接触金属化(contact metallization)相反,TCO材料的特征在于高的辐射透射率,使得在有源区中产生的辐射可以以简化的方式辐射通过接触层。

由于通过接触层5实现横向电流分布,因此,可具有吸收性的连接件6可有利地形成为具有较小的面积。

通过反射体层8减少在电连接件6中吸收在有源区3中产生的辐射。反射体层8优选将从有源区3入射到其上的辐射反射回半导体层序列2中,使得如果适当的话辐射可以从半导体芯片1耦合输出。通过粘接促进层9有利地增加反射体层8与接触层5的粘接,由此降低包含连接件和反射体层的叠层脱离接触层的风险并由此降低芯片缺陷的风险。

通过镜面层16,在有源区3中产生并入射到远离半导体层序列2的衬底4的表面上的辐射可沿半导体层序列的方向反射回去,由此降低布置在远离半导体层序列2的镜面层16的一侧上的元件中吸收在半导体芯片1中产生的辐射的风险,所述元件例如为外部连接导体或反连接件7。

优选通过隧道接触10改善接触层与半导体层序列的电连接。特别地,可以降低接触层/半导体层序列的结上的损失电压。如果在没有隧道接触的情况下在接触层5和半导体层14之间会形成具有显著厚度的高电势势垒,那么这是特别重要的。例如对于n导电的ITO或ZnO:Al,可以是这种情况。

作为设置具有不同导电类型的两个隧道接触层的隧道接触10的替代方案,如果适当的话,也可以在没有隧道接触的情况下在接触层5和半导体主体2之间形成优选为欧姆接触的良好电接触。

特别地,为此,可在半导体主体中集成邻接辐射透射性接触层的连接层。在这种情况下,隧道接触的层11(参见图7A)可省略,层12可用作连接层。

所述连接层被有利地优化,用于与辐射透射性接触层形成接触。优选以掺杂的方式形成连接层。为了形成与接触层的接触,已证明连接层在面对接触层的一侧上并且特别是在连接层与接触层邻接的接触区域中具有与布置在更远离接触层并且特别是更接近有源区的连接层区域中不同的掺杂剂浓度是特别有利的。优选地,连接层中的掺杂剂浓度在接触层的一部分上比在有源区的一部分上大。

连接层中的不同掺杂剂浓度可特别地明显相互偏离。两种掺杂剂浓度优选相互偏离30%或更大、特别优选40%或更大。在接近接触层的区域特别是直接接触区域中,连接层中掺杂剂浓度可以是更远离接触层并布置为更接近有源区的连接层区域中掺杂剂浓度的1.3倍或更大、优选1.4倍或更大。

连接层优选包含氮化物化合物半导体材料。连接层可包含例如GaN或由其构成。此外,优选形成连接层,使得它以p导电方式被掺杂。已证明使用Mg作为p型掺杂的受体是特别合适的。

在接触层一部分上的连接层中3×1019cm-3或更大、例如为3×1019cm-3~5×1020cm-3(包括端值)的掺杂剂浓度已被证明特别适于接触层和连接层之间低接触电阻。在远离接触层的连接层的区域中,所述连接层可具有2×1019cm-3或更低的掺杂剂浓度。特别是在与横向主延伸方向相垂直的方向上,与掺杂剂浓度在整个层上均匀地较高的情况相比,在与关于接触层的边界区域相比连接层的内部掺杂剂浓度降低的情况下,连接层中自由电荷载流子的浓度以及由此沿有源区的方向上的导电率可更高。但是,关于接触层的接触区域中的高掺杂剂浓度使得更容易在接触层和有源区之间形成低电阻并由此形成低损失电接触。特别地,可由此以简化的方式获得与半导体主体的欧姆电接触。

连接层的厚度可以为30nm或更大,特别是优选50nm或更大或者甚至100nm或更大。

在WO03/043092中说明了这种连接层,在本专利申请中通过引用明确并入其全部公开内容。我们惊奇地发现,这样形成的连接层不仅特别适于在高吸收性的金属化和半导体材料之间形成接触,而且适于在半导体主体和辐射透射性接触层特别是TCO接触层之间形成电接触。

衬底4包含例如SiC、优选SiC:N或者优选n导电掺杂的GaN。特别地,优选以导电的方式形成衬底4,使得可通过衬底与有源区3形成电接触。此外,优选形成衬底,使得它对于在有源区中产生的辐射是辐射透射性的,使得还可以以简化方式利用衬底以将辐射从半导体芯片耦合输出。

此外,对于基于氮化物化合物半导体的半导体层序列来说,上述用于衬底的材料GaN和SiC的折射率大于(对于SiC)或等于(对于GaN)半导体层序列特别是有源区和/或在衬底4的一部分上限定半导体层序列边界的半导体层15的半导体层的折射率(如果适当的话为平均折射率)。SiC的折射率为约2.7,并且,来自材料体系(In,Al)GaN的材料的典型折射率为约2.5。由于半导体层序列和衬底(特别是关于折射率低于基于GaN的材料的蓝宝石衬底)的界面上的全反射减少或完全被忽略,因此可有利于将辐射从半导体层序列2辐射传递到衬底3中。

此外,在衬底具有高折射率的情况下,衬底可以以简化的方式用于沿着衬底的侧表面17的方向对辐射进行射束引导(beam-guiding)。特别地,可形成衬底用于波导。通过远离半导体层序列的衬底的表面上的反射、特别是通过镜面层上的反射和面对半导体层序列的衬底的表面上的(全)反射,可以沿侧表面的方向引导辐射。侧表面17从而可以多重地用于从半导体芯片1耦合输出辐射。通过利用衬底耦合输出,有利于半导体芯片用作具有比较低的表面亮度的体积发射器(volumeemitter)的实施方案。

在根据图7(图7A、图7B和图7C)中的示例性实施方案的半导体芯片1的情况下,半导体芯片1具有基本上垂直于半导体层序列2的主延伸方向D的侧表面17和基本上垂直于所述侧表面的两个表面,该衬底中沿侧表面17的方向的这种射束引导是特别有利的。

在图7A中基于射束23示意地示出衬底4中的这种射束引导。在这种情况下,对于基于(In,Al)GaN的半导体层序列,采用具有比半导体层序列2高的折射率的衬底,例如SiC衬底。因此,射束23在进入衬底4时在面对半导体层序列2的衬底4的表面25向着表面法线24被折射。在镜面层16上的反射和表面25上的全反射之后,射束通过侧表面17从衬底4耦合输出。

在图7B和图7C中示出根据图7A的半导体芯片的两个有利的实施方案。

这里衬底4在每一种情况下具有厚度t。长度1以及长度w给出芯片的边缘长度(参见图8中的平面图)。

边缘长度1和w可以是不同的,但是优选是相同的,使得芯片在平面图中类似于正方形。此外,边缘长度1优选与衬底的长度对应。厚度t优选沿横向上恒定。

典型的芯片边缘长度1、w为200~300μm,并且例如为250μm。

在根据图7B的示例性实施方案中,衬底具有厚度t和与边缘长度1对应的长度。假定相同的边缘长度(1=w),那么侧表面17中的区域面积由此在每一种情况下为1×t,假定不同的边缘长度,那么该区域面积分别为1×t和w×t。比率1:t优选在每一种情况下为0.8~1.2(包括端值)。特别地可以以类似于立方体的形式形成芯片。另外,在此特别优选1=t的情况。

假定相同的边缘长度1和w,衬底的表面25的区域面积(1×w)以及各侧表面17的区域面积(分别为1×t和w×t)同样具有1:t的比率。

通过的这种尺寸区域面积,可以在可靠地安装芯片的同时有利地减少侧表面17处的亮度。衬底优选具有这种厚度,或者,如果适当的话,被减薄到这种厚度。

由于半导体层序列相对于芯片尺寸来说比较薄,因此衬底厚度决定性地决定芯片高度。特别地,整个芯片可以形成为具有类似立方体包封的基本形式。

在根据图7C的示例性实施方案中,衬底4的厚度t小于或等于(1/2)×1,优选小于或等于(1/3)×1。衬底的厚度可例如为100μm或更小、优选为80μm或更小。为此,衬底4相应地被减薄是有利的。优选在在衬底4上生长半导体层序列2之后实现减薄。特别平坦并且相应地节省空间的半导体芯片可具有衬底的这种薄型实施方案。并且,在导电衬底的情况下,正向电压可有利地降低。

衬底有利地是折射率比半导体层序列高的衬底,诸如在基于氮化物化合物半导体的半导体层序列的情况下为SiC衬底。与诸如折射率低于氮化物化合物半导体材料的蓝宝石衬底的具有低折射率的衬底相比,在有源区3中产生的射束在衬底中更大程度地更陡直地穿行,也就是说,相对于表面法线24以更小的角度穿行。在镜面层16上反射之后重新进入半导体层序列2中并通过远离衬底4的半导体层序列2的一侧耦合输出的辐射比例可由此增加。与具有低折射率的衬底的半导体芯片相比,侧表面17上的亮度有利地降低。

与图7相反,图1~6所示的半导体芯片的示例性实施方案具有包括侧表面区域18的衬底4,这些侧表面区域18关于主延伸方向D成斜角,特别是相对于所述方向呈锐角。特别是在根据图1、图2、图4、图5和图6的示例性实施方案中,通过这种斜角,经由成斜角的侧表面区域18直接耦合输出的辐射比例可增加。

在根据图3的示例性实施方案中,连续的镜面层16也沿侧表面17并且特别是沿成斜角的侧表面区域18延伸。结果,通过镜面层16上的反射,可增加通过面对半导体层序列2的衬底4的表面的未被半导体层序列覆盖的部分区域而从芯片耦合输出的辐射功率。在图3中基于射束19示意性地示出这一点。

在根据图1、图4、图5和图6的示例性实施方案中,衬底具有相互平行地延伸并且特别是基本上与半导体层序列2的主延伸方向D垂直的侧表面区域20。从半导体层序列2的观察时,侧表面区域20优选布置在成斜角的侧表面区域18的下游。在侧表面区域20上,半导体芯片1可以以简化的方式通过安装工具被抓住,并被定位在外部电连接导体上和因此被固定到后者上并电接触连接。

在这种情况下,随着到半导体层序列2的距离增加,衬底4在成斜角的侧表面区域18的区域中逐渐变细,并且在侧表面区域20的区域中具有基本上恒定的横截面。特别地,在这些示例性实施方案中,在衬底4中,在衬底中形成沿半导体层序列的方向从远离半导体层序列2的衬底的表面延伸的切口21。在衬底逐渐变细的区域中或在切口的区域中,侧表面可具有楼梯状结构或者是弯曲的(未示出)。在该区域中直接从衬底耦合输出的辐射功率可由此更广泛地增加。

在根据图4、图5和图6的示例性实施方案中,半导体芯片1具有突起和凹陷22,通过这些突起和凹陷,能够影响辐射在具有突起和凹陷的各界面上的反射的反射角度。特别地,能够干扰所述界面上的全反射。由此可增加从半导体芯片1耦合输出的辐射功率。

可例如在远离半导体层序列的接触层5的一侧(图6)、远离衬底4的半导体层序列2的一侧(图4)或面对半导体层序列2的衬底的一侧(图5)上形成突起和凹陷22。一个凹陷或多个凹陷(优选各层中所有凹陷)的深度优选为100nm或更大。这样,可特别有效地干扰各结构化的界面上的反射。突起和凹陷可形成为具有重复的(优选周期性的)配置的突起和凹陷的规则结构,或形成为具有不规则的(优选基本上统计性的分布的)突起和凹陷的不规则粗糙化。可以例如通过已在上面进一步说明的蚀刻或喷砂在各个层中形成突起和凹陷。

在WO01/61764或WO01/61765中说明了与图1、图4、图5和图6所示半导体芯片类似的半导体芯片,在本专利申请中通过引用在此明确并入其全部公开内容作。可通过用于从晶片组件使芯片单一化的相应成形的锯片来实现在所述图中示意地示出的衬底4的成形。所切割的侧表面并且特别是衬底也不需要用于这种定形的进一步处理。

与在WO01/61764或WO01/61765中说明的芯片相比,在本发明中,半导体芯片的耦合输出效率可增加30%或更大、特别高达50%。

总之,通过上述半导体芯片,可形成体积发射半导体芯片,该体积发射半导体芯片具有降低的表面亮度、增加的耦合输出效率,并且由于辐射透射性的导电接触层,因此具有高载流能力并由此具有增加的ESD强度。

这种半导体芯片特别适于例如显示器的背面照明,用于照明或用于可视化例如用作显示器中的像素或像素的一部分,或用于投影设备中。

由于连接件和反连接件布置在半导体层序列的不同侧,因此,反连接件一部分上的半导体芯片可安装到外部连接导体上,并通过以导电的方式形成的例如银导电粘合剂或焊料的粘合剂以简单的方式被电连接。在半导体层序列的同一侧具有两种连接件的芯片的情况下,直接相互邻近并与半导体层序列和有源区直接邻近的任意两个引线接合,或者在倒装芯片安装的情况下粘接接合是必需的。与粘接接合相比,引线接合制造起来是比较复杂的,而在连接导体上具有粘接接合的倒装芯片安装情况下,芯片短路的风险增加。

本专利申请要求2006年1月27日的德国专利申请10 2006 004172.0和2006年4月4日的德国专利申请10 2006 015 788.5的优先权,在本专利申请中,通过引用在此明确并入它们的全部公开内容。

本发明不限于基于示例性实施方案的说明。而是,本发明包含任意的新特征以及特征的任意组合,该组合特别包含专利权利要求中的特征的任意组合。即使在专利权利要求或示例性实施方案中没有明确规定该特征或其该组合。

Claims (22)

1.一种具有半导体层序列(2)的光电子半导体芯片(1),所述半导体层序列(2)包含适于产生辐射的有源区(3)并具有横向主延伸方向,其中

所述半导体层序列通过具有侧表面(17)的衬底(4)来布置,

所述侧表面具有相对于所述主延伸方向成斜角的侧表面区域(18)和/或切口(21),和

所述半导体芯片具有辐射透射性的导电接触层(5),

其中邻接所述接触层(5)的连接层布置在所述半导体层序列中,并具有掺杂剂浓度,该掺杂剂在所述接触层(5)的一部分上的浓度比在所述有源区(3)的一部分上的浓度更大。

2.如权利要求1所述的半导体芯片,其中所述接触层(5)包含辐射透射性的导电氧化物。

3.如权利要求2所述的半导体芯片,其中所述导电氧化物为金属氧化物。

4.如权利要求3所述的半导体芯片,其中所述金属氧化物包含氧化铟、氧化锡、氧化铟锡或氧化锌。

5.如权利要求1~4中任一项所述的半导体芯片,其中所述半导体层序列(2)包含氮化物化合物半导体材料。

6.如权利要求5所述的半导体芯片,其中所述有源区(3)包含氮化物化合物半导体材料。

7.如权利要求1~4中任一项所述的半导体芯片,其中所述衬底(4)的折射率大于或等于所述有源区(3)的折射率,和/或所述衬底的折射率大于或等于在面对所述衬底的一侧上的结束所述半导体层序列(2)的半导体层的折射率。

8.如权利要求1~4中任一项所述的半导体芯片,其中所述衬底(4)对于在所述有源区(3)中产生的辐射是辐射透射性的。

9.如权利要求1~4中任一项所述的半导体芯片,其中所述衬底(4)的表面形成作为所述半导体芯片(1)的辐射耦合输出区域。

10.如权利要求9所述的半导体芯片,其中所述衬底(4)的所述侧表面和/或面对所述半导体层序列的表面形成作为所述半导体芯片(1)的辐射耦合输出区域。

11.如权利要求1~4中任一项所述的半导体芯片,其中所述切口(21)从所述衬底(4)的远离所述半导体层序列(2)的表面沿所述半导体层序列的方向延伸。

12.如权利要求1~4中任一项所述的半导体芯片,其中利用相对于所述半导体层序列(3)倾斜地延伸的侧表面区域(18)和利用所述侧表面(17)的其他侧表面区域(20)来形成所述切口(21),其中,所述其他侧面区域基本上垂直于所述半导体层序列。

13.如权利要求1~4中任一项所述的半导体芯片,其中随着到所述半导体层序列(2)的距离增加,所述衬底(4)逐渐变细。

14.如权利要求1~4中任一项所述的半导体芯片,其中在所述接触层(5)和所述有源区(3)之间形成隧道接触(10)。

15.如权利要求14所述的半导体芯片,其中所述隧道接触(10)具有以单块方式集成到所述半导体层序列(2)中的隧道接触层(11、12)。

16.如权利要求15所述的半导体芯片,其中所述隧道接触(10)具有以单块方式集成到所述半导体层序列中的具有不同导电类型的两个隧道接触层(11、12)。

17.如权利要求1~4中任一项所述的半导体芯片,其中所述衬底(4)的表面、所述半导体层序列(2)的面对所述接触层(5)的表面和/或所述接触层的远离所述半导体层序列的表面具有突起和凹陷(22)。

18.如权利要求1~4中任一项所述的半导体芯片,其中所述衬底(4)的面对所述半导体层序列的表面的面积与横向限定所述半导体芯片边界的侧表面(17)的面积之比小于或等于2。

19.一种具有半导体层序列(2)的光电子半导体芯片(1),所述半导体层序列(2)包含适于产生辐射的有源区(3)并且布置在衬底(4)上,其中

所述半导体芯片具有辐射透射性的导电接触层(5),和

所述衬底的折射率大于或等于所述有源区的折射率,和/或

所述衬底的折射率大于或等于在面对所述衬底的一侧结束所述半导体层序列的半导体层的折射率,

其中邻接所述接触层(5)的连接层布置在所述半导体层序列中,并具有掺杂剂浓度,该掺杂剂在所述接触层(5)的一部分上的浓度比在所述有源区(3)的一部分上的浓度更大。

20.如权利要求19所述的半导体芯片,其中所述接触层(5)包含辐射透射性的导电氧化物.

21.一种具有半导体层序列(2)的光电子半导体芯片(1),所述半导体层序列(2)包含适于产生辐射的有源区(3)并且布置在衬底(4)上,其中

所述半导体层序列包含氮化物化合物半导体材料,

所述半导体芯片具有辐射透射性的导电接触层(5),所述接触层(5)与所述半导体芯片的电连接件(6)电连接,所述半导体芯片的所述电连接件以及反电连接件(7)布置在所述半导体层序列的相反的两侧,

其中邻接所述接触层(5)的连接层布置在所述半导体层序列中,并具有掺杂剂浓度,该掺杂剂在所述接触层(5)的一部分上的浓度比在所述有源区(3)的一部分上的浓度更大。

22.如权利要求21所述的半导体芯片,其中所述接触层(5)包含辐射透射性的导电氧化物。

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE102006004172 | 2006-01-27 | ||

| DE102006004172.0 | 2006-01-27 | ||

| DE102006015788.5 | 2006-04-04 | ||

| DE102006015788A DE102006015788A1 (de) | 2006-01-27 | 2006-04-04 | Optoelektronischer Halbleiterchip |

| PCT/DE2006/002293 WO2007085218A1 (de) | 2006-01-27 | 2006-12-20 | Optoelektronischer halbleiterchip |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201010277177.8A Division CN101976718B (zh) | 2006-01-27 | 2006-12-20 | 光电子半导体芯片 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN101395725A CN101395725A (zh) | 2009-03-25 |

| CN101395725B true CN101395725B (zh) | 2010-11-10 |

Family

ID=37898325

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN200680053614XA Active CN101395725B (zh) | 2006-01-27 | 2006-12-20 | 光电子半导体芯片 |

| CN201010277177.8A Active CN101976718B (zh) | 2006-01-27 | 2006-12-20 | 光电子半导体芯片 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201010277177.8A Active CN101976718B (zh) | 2006-01-27 | 2006-12-20 | 光电子半导体芯片 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US8581280B2 (zh) |

| EP (1) | EP1977457B1 (zh) |

| JP (1) | JP2009524918A (zh) |

| KR (1) | KR20080091249A (zh) |

| CN (2) | CN101395725B (zh) |

| DE (1) | DE102006015788A1 (zh) |

| TW (1) | TWI350597B (zh) |

| WO (1) | WO2007085218A1 (zh) |

Families Citing this family (32)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5286641B2 (ja) * | 2006-03-29 | 2013-09-11 | 日亜化学工業株式会社 | 半導体発光素子及び半導体発光装置 |

| DE102007002416A1 (de) | 2006-04-13 | 2007-10-18 | Osram Opto Semiconductors Gmbh | Strahlungsemittierender Körper und Verfahren zur Herstellung eines strahlungsemittierenden Körpers |

| DE102006061167A1 (de) | 2006-04-25 | 2007-12-20 | Osram Opto Semiconductors Gmbh | Optoelektronisches Halbleiterbauelement |

| DE102007027641B4 (de) * | 2007-06-15 | 2015-12-03 | Huga Optotech Inc. | Verfahren zum Herstellen einer Licht emittierenden Diode |

| DE102007035687A1 (de) * | 2007-07-30 | 2009-02-05 | Osram Opto Semiconductors Gmbh | Optoelektronisches Bauelement mit einem Schichtenstapel |

| JP5126884B2 (ja) * | 2008-01-16 | 2013-01-23 | シャープ株式会社 | 窒化物半導体発光素子および窒化物半導体発光素子の製造方法 |

| DE102008006987A1 (de) | 2008-01-31 | 2009-08-06 | Osram Opto Semiconductors Gmbh | Strahlungsempfänger und Verfahren zur Herstellung eines Strahlungsempfängers |

| EP2280426B1 (en) * | 2008-04-16 | 2017-07-05 | LG Innotek Co., Ltd. | Light-emitting device |

| DE102008052405A1 (de) * | 2008-10-21 | 2010-04-22 | Osram Opto Semiconductors Gmbh | Optoelektronisches Halbleiterbauelement |

| JP2010192835A (ja) * | 2009-02-20 | 2010-09-02 | Showa Denko Kk | 発光ダイオード及びその製造方法、並びに発光ダイオードランプ |

| DE102009032486A1 (de) * | 2009-07-09 | 2011-01-13 | Osram Opto Semiconductors Gmbh | Optoelektronisches Bauelement |

| JP2012004476A (ja) * | 2010-06-21 | 2012-01-05 | Toshiba Corp | 発光装置 |

| DE102010031237A1 (de) | 2010-07-12 | 2012-01-12 | Osram Opto Semiconductors Gmbh | Optoelektronisches Bauelement |

| DE102010027679A1 (de) | 2010-07-20 | 2012-01-26 | Osram Opto Semiconductors Gmbh | Optoelektronisches Bauelement |

| DE102010038405A1 (de) | 2010-07-26 | 2012-01-26 | Osram Opto Semiconductors Gmbh | Elektronisches Bauelement und Verfahren zur Herstellung eines elektronischen Bauelements |

| DE102010039382A1 (de) | 2010-08-17 | 2012-02-23 | Osram Opto Semiconductors Gmbh | Elektronisches Bauelement und Verfahren zur Herstellung eines elektronischen Bauelements |

| KR101274651B1 (ko) | 2010-11-30 | 2013-06-12 | 엘지디스플레이 주식회사 | 발광 다이오드 및 이의 제조 방법 |

| US8802461B2 (en) * | 2011-03-22 | 2014-08-12 | Micron Technology, Inc. | Vertical light emitting devices with nickel silicide bonding and methods of manufacturing |

| JP6056150B2 (ja) | 2011-04-08 | 2017-01-11 | 日亜化学工業株式会社 | 半導体発光素子 |

| DE102011080458A1 (de) | 2011-08-04 | 2013-02-07 | Osram Opto Semiconductors Gmbh | Optoelektronische anordnung und verfahren zur herstellung einer optoelektronischen anordnung |

| DE102011087543A1 (de) | 2011-12-01 | 2013-06-06 | Osram Opto Semiconductors Gmbh | Optoelektronische anordnung |

| DE102012200416B4 (de) | 2012-01-12 | 2018-03-01 | Osram Opto Semiconductors Gmbh | Optoelektronisches modul und verfahren zur herstellung eines optoelektronischen moduls |

| GB201202222D0 (en) * | 2012-02-09 | 2012-03-28 | Mled Ltd | Enhanced light extraction |

| DE102012202102A1 (de) * | 2012-02-13 | 2013-08-14 | Osram Gmbh | Leuchtvorrichtung mit Volumenstrahler-LED-Chips auf einem gemeinsamen Substrat |

| WO2013134432A1 (en) * | 2012-03-06 | 2013-09-12 | Soraa, Inc. | Light emitting diodes with low refractive index material layers to reduce light guiding effects |

| US9501601B2 (en) | 2013-03-14 | 2016-11-22 | Taiwan Semiconductor Manufacturing Company, Ltd. | Layout optimization of a main pattern and a cut pattern |

| JP2015162631A (ja) * | 2014-02-28 | 2015-09-07 | サンケン電気株式会社 | 発光素子 |

| DE102014107555A1 (de) | 2014-05-28 | 2015-12-03 | Osram Opto Semiconductors Gmbh | Elektrische Kontaktstruktur für ein Halbleiterbauelement und Halbleiterbauelement |

| DE102015103840A1 (de) * | 2015-03-16 | 2016-09-22 | Osram Opto Semiconductors Gmbh | Elektromagnetische Strahlung emittierende Baugruppe |

| DE102016100563B4 (de) | 2016-01-14 | 2021-08-05 | OSRAM Opto Semiconductors Gesellschaft mit beschränkter Haftung | Verfahren zum Herstellen einer optoelektronischen Leuchtvorrichtung und optoelektronische Leuchtvorrichtung |

| DE102018113573B4 (de) * | 2018-06-07 | 2022-11-03 | Semikron Elektronik Gmbh & Co. Kg Patentabteilung | Diode mit einem Halbleiterkörper |

| DE102018115225A1 (de) * | 2018-06-25 | 2020-01-02 | Otto-Von-Guericke-Universität Magdeburg | Lichtemmitierendes Halbleiterbauelement oder Halbleiterbauelementmodul |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE20022541U1 (de) * | 2000-02-15 | 2002-02-28 | Osram Opto Semiconductors Gmbh | Lichtemittierendes Bauelement mit verbesserter Lichtauskopplung |

Family Cites Families (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5132577A (en) * | 1991-04-11 | 1992-07-21 | National Semiconductor Corporation | High speed passgate, latch and flip-flop circuits |

| US5892784A (en) | 1994-10-27 | 1999-04-06 | Hewlett-Packard Company | N-drive p-common surface emitting laser fabricated on n+ substrate |

| JP3165374B2 (ja) | 1995-08-31 | 2001-05-14 | 株式会社東芝 | 化合物半導体の電極の形成方法 |

| US5789265A (en) | 1995-08-31 | 1998-08-04 | Kabushiki Kaisha Toshiba | Method of manufacturing blue light-emitting device by using BCL3 and CL2 |

| US6803243B2 (en) * | 2001-03-15 | 2004-10-12 | Cree, Inc. | Low temperature formation of backside ohmic contacts for vertical devices |

| JP3469484B2 (ja) | 1998-12-24 | 2003-11-25 | 株式会社東芝 | 半導体発光素子およびその製造方法 |

| AU2001239182A1 (en) | 2000-02-15 | 2001-08-27 | Osram Opto Semiconductors Gmbh | Semiconductor component which emits radiation, and method for producing the same |

| DE10006738C2 (de) | 2000-02-15 | 2002-01-17 | Osram Opto Semiconductors Gmbh | Lichtemittierendes Bauelement mit verbesserter Lichtauskopplung und Verfahren zu seiner Herstellung |

| JP3506175B2 (ja) | 2000-10-05 | 2004-03-15 | 日本電気株式会社 | メモリ制御回路とメモリ制御方法 |

| US6791119B2 (en) * | 2001-02-01 | 2004-09-14 | Cree, Inc. | Light emitting diodes including modifications for light extraction |

| US6747298B2 (en) | 2001-07-23 | 2004-06-08 | Cree, Inc. | Collets for bonding of light emitting diodes having shaped substrates |

| DE10155442A1 (de) | 2001-11-12 | 2003-05-28 | Osram Opto Semiconductors Gmbh | Ohmsche Kontaktstruktur und Verfahren zu deren Herstellung |

| JP2003168845A (ja) * | 2001-12-03 | 2003-06-13 | Hitachi Ltd | 半導体レーザ素子及びこれを用いた光モジュール、及び光システム |

| US6878975B2 (en) * | 2002-02-08 | 2005-04-12 | Agilent Technologies, Inc. | Polarization field enhanced tunnel structures |

| TWI228323B (en) | 2002-09-06 | 2005-02-21 | Sony Corp | Semiconductor light emitting device and its manufacturing method, integrated semiconductor light emitting device and manufacturing method thereof, image display device and its manufacturing method, illumination device and manufacturing method thereof |

| JP4143732B2 (ja) * | 2002-10-16 | 2008-09-03 | スタンレー電気株式会社 | 車載用波長変換素子 |

| US20050173724A1 (en) | 2004-02-11 | 2005-08-11 | Heng Liu | Group III-nitride based LED having a transparent current spreading layer |

| TWI240439B (en) | 2003-09-24 | 2005-09-21 | Sanken Electric Co Ltd | Nitride semiconductor device and manufacturing method thereof |

| KR100647279B1 (ko) * | 2003-11-14 | 2006-11-17 | 삼성전자주식회사 | 질화물계 발광소자 및 그 제조방법 |

| JP2005268601A (ja) * | 2004-03-19 | 2005-09-29 | Sumitomo Chemical Co Ltd | 化合物半導体発光素子 |

| US7022550B2 (en) * | 2004-04-07 | 2006-04-04 | Gelcore Llc | Methods for forming aluminum-containing p-contacts for group III-nitride light emitting diodes |

| DE102004040277B4 (de) * | 2004-06-30 | 2015-07-30 | Osram Opto Semiconductors Gmbh | Reflektierendes Schichtsystem mit einer Mehrzahl von Schichten zur Aufbringung auf ein III/V-Verbindungshalbleitermaterial |

| DE102004050891B4 (de) * | 2004-10-19 | 2019-01-10 | Lumileds Holding B.V. | Lichtmittierende III-Nitrid-Halbleitervorrichtung |

| JP2007208047A (ja) * | 2006-02-02 | 2007-08-16 | Fujikura Ltd | 半導体発光素子 |

| DE102008030818B4 (de) * | 2008-06-30 | 2022-03-03 | OSRAM Opto Semiconductors Gesellschaft mit beschränkter Haftung | Oberflächenemittierender Halbleiterlaser mit mehreren aktiven Zonen |

-

2006

- 2006-04-04 DE DE102006015788A patent/DE102006015788A1/de not_active Withdrawn

- 2006-12-20 CN CN200680053614XA patent/CN101395725B/zh active Active

- 2006-12-20 KR KR1020087020617A patent/KR20080091249A/ko not_active Application Discontinuation

- 2006-12-20 JP JP2008551640A patent/JP2009524918A/ja active Pending

- 2006-12-20 WO PCT/DE2006/002293 patent/WO2007085218A1/de active Application Filing

- 2006-12-20 CN CN201010277177.8A patent/CN101976718B/zh active Active

- 2006-12-20 US US12/223,382 patent/US8581280B2/en active Active

- 2006-12-20 EP EP06828719.2A patent/EP1977457B1/de active Active

-

2007

- 2007-01-25 TW TW096102767A patent/TWI350597B/zh not_active IP Right Cessation

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE20022541U1 (de) * | 2000-02-15 | 2002-02-28 | Osram Opto Semiconductors Gmbh | Lichtemittierendes Bauelement mit verbesserter Lichtauskopplung |

Also Published As

| Publication number | Publication date |

|---|---|

| US8581280B2 (en) | 2013-11-12 |

| CN101976718B (zh) | 2014-06-11 |

| CN101976718A (zh) | 2011-02-16 |

| TWI350597B (en) | 2011-10-11 |

| CN101395725A (zh) | 2009-03-25 |

| EP1977457B1 (de) | 2018-05-09 |

| WO2007085218A1 (de) | 2007-08-02 |

| EP1977457A1 (de) | 2008-10-08 |

| TW200737553A (en) | 2007-10-01 |

| US20090315048A1 (en) | 2009-12-24 |

| DE102006015788A1 (de) | 2007-09-13 |

| JP2009524918A (ja) | 2009-07-02 |

| KR20080091249A (ko) | 2008-10-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101395725B (zh) | 光电子半导体芯片 | |

| CN101796656B (zh) | 光电子器件 | |

| KR101054169B1 (ko) | 질화갈륨계 반도체 발광소자 | |

| TWI520379B (zh) | 發光二極體晶片 | |

| US7649193B2 (en) | Semiconductor body and semiconductor chip comprising a semiconductor body | |

| US8067783B2 (en) | Radiation-emitting chip comprising at least one semiconductor body | |

| KR101860973B1 (ko) | 광전 반도체 칩 | |

| US20090309120A1 (en) | LED Semiconductor Element, and Use Thereof | |

| KR100867529B1 (ko) | 수직형 발광 소자 | |

| CN103069568A (zh) | 光电子半导体芯片和用于制造光电子半导体芯片的方法 | |

| CN103026510A (zh) | 发射辐射的半导体芯片和用于制造发射辐射的半导体芯片的方法 | |

| CN103380551A (zh) | 半导体发光元件以及使用它的发光装置 | |

| KR102019858B1 (ko) | 발광소자 및 조명시스템 | |

| KR101954205B1 (ko) | 발광 소자 | |

| CN102106008B (zh) | 光电子半导体芯片 | |

| CN109923682B (zh) | 半导体器件和包括该半导体器件的半导体器件封装 | |

| CN102487115A (zh) | 发光二极管 | |

| US20040262620A1 (en) | Light emitting diode chip with radiation-transmissive electrical current expansion layer | |

| KR102577879B1 (ko) | 반도체 소자 및 이를 포함하는 반도체 소자 패키지 | |

| US10644201B2 (en) | Optoelectronic semiconductor chip | |

| CN103887395A (zh) | 发光元件 | |

| US20240145632A1 (en) | Micro light emitting device and micro light emitting apparatus using the same | |

| KR101827974B1 (ko) | 발광 소자 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant |