CN100541746C - 电抛光具有带虚设结构的沟槽或者通路的晶片上的金属层 - Google Patents

电抛光具有带虚设结构的沟槽或者通路的晶片上的金属层 Download PDFInfo

- Publication number

- CN100541746C CN100541746C CNB028088344A CN02808834A CN100541746C CN 100541746 C CN100541746 C CN 100541746C CN B028088344 A CNB028088344 A CN B028088344A CN 02808834 A CN02808834 A CN 02808834A CN 100541746 C CN100541746 C CN 100541746C

- Authority

- CN

- China

- Prior art keywords

- concave area

- metal level

- metal

- layer

- dummy structures

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 229910052751 metal Inorganic materials 0.000 title claims abstract description 261

- 239000002184 metal Substances 0.000 title claims abstract description 260

- 239000004065 semiconductor Substances 0.000 claims abstract description 99

- 230000004888 barrier function Effects 0.000 claims description 153

- 238000000034 method Methods 0.000 claims description 94

- 238000005498 polishing Methods 0.000 claims description 34

- 239000000463 material Substances 0.000 claims description 26

- 238000012360 testing method Methods 0.000 claims description 18

- 239000000523 sample Substances 0.000 claims description 9

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 claims description 8

- 229910052802 copper Inorganic materials 0.000 claims description 8

- 239000010949 copper Substances 0.000 claims description 8

- 239000013078 crystal Substances 0.000 claims description 7

- 230000015572 biosynthetic process Effects 0.000 claims 1

- 238000005516 engineering process Methods 0.000 description 58

- 238000001020 plasma etching Methods 0.000 description 29

- VIKNJXKGJWUCNN-XGXHKTLJSA-N norethisterone Chemical compound O=C1CC[C@@H]2[C@H]3CC[C@](C)([C@](CC4)(O)C#C)[C@@H]4[C@@H]3CCC2=C1 VIKNJXKGJWUCNN-XGXHKTLJSA-N 0.000 description 24

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 20

- 239000000126 substance Substances 0.000 description 20

- 235000012431 wafers Nutrition 0.000 description 20

- 238000005530 etching Methods 0.000 description 17

- 239000007789 gas Substances 0.000 description 17

- 238000005260 corrosion Methods 0.000 description 16

- 230000007797 corrosion Effects 0.000 description 16

- 238000004519 manufacturing process Methods 0.000 description 13

- 235000012239 silicon dioxide Nutrition 0.000 description 10

- 239000000377 silicon dioxide Substances 0.000 description 10

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 9

- 229910052718 tin Inorganic materials 0.000 description 9

- 239000011135 tin Substances 0.000 description 9

- 208000005189 Embolism Diseases 0.000 description 8

- -1 siloxanes Chemical class 0.000 description 8

- 229910004298 SiO 2 Inorganic materials 0.000 description 7

- 150000002739 metals Chemical class 0.000 description 7

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 6

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 6

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 6

- 239000004642 Polyimide Substances 0.000 description 6

- 239000007788 liquid Substances 0.000 description 6

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 6

- 229920000052 poly(p-xylylene) Polymers 0.000 description 6

- 229920001721 polyimide Polymers 0.000 description 6

- 238000003466 welding Methods 0.000 description 6

- 239000004411 aluminium Substances 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 4

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 4

- 238000000231 atomic layer deposition Methods 0.000 description 4

- 238000005229 chemical vapour deposition Methods 0.000 description 4

- 150000001875 compounds Chemical class 0.000 description 4

- 238000005240 physical vapour deposition Methods 0.000 description 4

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 3

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 3

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 3

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 3

- 229910052793 cadmium Inorganic materials 0.000 description 3

- BDOSMKKIYDKNTQ-UHFFFAOYSA-N cadmium atom Chemical compound [Cd] BDOSMKKIYDKNTQ-UHFFFAOYSA-N 0.000 description 3

- 229910002091 carbon monoxide Inorganic materials 0.000 description 3

- 229910052804 chromium Inorganic materials 0.000 description 3

- 239000011651 chromium Substances 0.000 description 3

- 239000004020 conductor Substances 0.000 description 3

- 238000005137 deposition process Methods 0.000 description 3

- 230000002349 favourable effect Effects 0.000 description 3

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 3

- 229910052737 gold Inorganic materials 0.000 description 3

- 239000010931 gold Substances 0.000 description 3

- 229910052738 indium Inorganic materials 0.000 description 3

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 3

- 229910052742 iron Inorganic materials 0.000 description 3

- 239000011133 lead Substances 0.000 description 3

- 229910052759 nickel Inorganic materials 0.000 description 3

- 229920000620 organic polymer Polymers 0.000 description 3

- 229910052763 palladium Inorganic materials 0.000 description 3

- 238000002161 passivation Methods 0.000 description 3

- 238000007747 plating Methods 0.000 description 3

- 229910052697 platinum Inorganic materials 0.000 description 3

- 229920003209 poly(hydridosilsesquioxane) Polymers 0.000 description 3

- 229920001343 polytetrafluoroethylene Polymers 0.000 description 3

- 239000004810 polytetrafluoroethylene Substances 0.000 description 3

- 238000003908 quality control method Methods 0.000 description 3

- 229910052703 rhodium Inorganic materials 0.000 description 3

- 239000010948 rhodium Substances 0.000 description 3

- MHOVAHRLVXNVSD-UHFFFAOYSA-N rhodium atom Chemical compound [Rh] MHOVAHRLVXNVSD-UHFFFAOYSA-N 0.000 description 3

- 239000005368 silicate glass Substances 0.000 description 3

- 150000004760 silicates Chemical class 0.000 description 3

- 229910052710 silicon Inorganic materials 0.000 description 3

- 239000010703 silicon Substances 0.000 description 3

- 229910052709 silver Inorganic materials 0.000 description 3

- 239000004332 silver Substances 0.000 description 3

- 229910052721 tungsten Inorganic materials 0.000 description 3

- 239000010937 tungsten Substances 0.000 description 3

- 229910052725 zinc Inorganic materials 0.000 description 3

- 239000011701 zinc Substances 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012827 research and development Methods 0.000 description 2

- 239000002887 superconductor Substances 0.000 description 2

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 2

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 2

- 241000208340 Araliaceae Species 0.000 description 1

- BSYNRYMUTXBXSQ-UHFFFAOYSA-N Aspirin Chemical compound CC(=O)OC1=CC=CC=C1C(O)=O BSYNRYMUTXBXSQ-UHFFFAOYSA-N 0.000 description 1

- 235000005035 Panax pseudoginseng ssp. pseudoginseng Nutrition 0.000 description 1

- 235000003140 Panax quinquefolius Nutrition 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000000994 depressogenic effect Effects 0.000 description 1

- 229910003460 diamond Inorganic materials 0.000 description 1

- 239000010432 diamond Substances 0.000 description 1

- 239000003989 dielectric material Substances 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 230000005611 electricity Effects 0.000 description 1

- 235000008434 ginseng Nutrition 0.000 description 1

- 230000001939 inductive effect Effects 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 238000001259 photo etching Methods 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 238000011160 research Methods 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25D—PROCESSES FOR THE ELECTROLYTIC OR ELECTROPHORETIC PRODUCTION OF COATINGS; ELECTROFORMING; APPARATUS THEREFOR

- C25D5/00—Electroplating characterised by the process; Pretreatment or after-treatment of workpieces

- C25D5/48—After-treatment of electroplated surfaces

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25D—PROCESSES FOR THE ELECTROLYTIC OR ELECTROPHORETIC PRODUCTION OF COATINGS; ELECTROFORMING; APPARATUS THEREFOR

- C25D5/00—Electroplating characterised by the process; Pretreatment or after-treatment of workpieces

- C25D5/02—Electroplating of selected surface areas

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25D—PROCESSES FOR THE ELECTROLYTIC OR ELECTROPHORETIC PRODUCTION OF COATINGS; ELECTROFORMING; APPARATUS THEREFOR

- C25D7/00—Electroplating characterised by the article coated

- C25D7/12—Semiconductors

- C25D7/123—Semiconductors first coated with a seed layer or a conductive layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3205—Deposition of non-insulating-, e.g. conductive- or resistive-, layers on insulating layers; After-treatment of these layers

- H01L21/321—After treatment

- H01L21/32115—Planarisation

- H01L21/3212—Planarisation by chemical mechanical polishing [CMP]

- H01L21/32125—Planarisation by chemical mechanical polishing [CMP] by simultaneously passing an electrical current, i.e. electrochemical mechanical polishing, e.g. ECMP

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/7684—Smoothing; Planarisation

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Electrochemistry (AREA)

- Materials Engineering (AREA)

- Organic Chemistry (AREA)

- Metallurgy (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Physics & Mathematics (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

在电抛光半导体晶片上的金属层中,在半导体晶片(未示出)上形成电介质(100)。该电介质(100)形成有凹进区(102)和非凹进区(103)。多个虚设结构(200)是构成的非活动区,以便增加后来形成在电介质(100)上的金属层(106)的平整度。然后形成金属层(106)以便填充凹进区(102)并且覆盖非凹进区(103)和多个虚设结构(200)。然后电抛光该金属层(106)以便露出非凹进区(102)。

Description

相关申请的交叉引用

本申请要求2001年4月24日申请的美国序列号为No.60/286,273、名称为“ELECTROPOLISHING METAL LAYERSON WAFERS HAVING TRENCHES OR VIAS WITH DUMMYSTRUCTURES”的在先申请的优先权,这里全文引入作为参考。

技术领域

本发明总的来说涉及半导体晶片。更具体地说,本发明涉及半导体晶片上沟槽或者通路中的虚设结构。

背景技术

通常,在称为晶片或者切片的半导体材料盘片上制造半导体器件。更具体地说,首先从硅锭上切出晶片。然后对该晶片进行多次掩模、蚀刻和淀积工序,以便形成半导体器件的电子布线。

具体地说,可以利用多次的掩模和蚀刻工序在晶片中形成凹进区,例如沟槽、通路等。在某些应用中,这些凹进区可以形成宽的沟槽。可以使用淀积工序将金属淀积到晶片的宽沟槽和非凹进区。淀积之后,可以从晶片的非凹进区除去金属,使得留在宽沟槽中的金属形成互连。然而,由于宽沟槽的宽度,从凹陷区除去金属时,也会将淀积在宽沟槽中的部分金属除去超过需要的深度。这种称为表面凹陷的过去除会减小互连的截面积,从而增加互连的电阻。这种增加的电阻会引起半导体器件的可靠性问题。

因此,当使用化学机械抛光(CMP)从晶片的非凹进区除去金属时,已经使用在宽沟槽内形成虚设结构以便减小表面凹陷。尤其是,虚设结构能够防止CMP抛光衬垫移过虚设结构并且过抛光宽沟槽中的金属。然而,如果使用电抛光从非凹进区除去金属,那么即使宽沟槽包括虚设结构也会出现表面凹陷。

发明内容

本发明涉及电抛光半导体晶片上的金属层。在本发明的一个实施例中,在半导体晶片上形成电介质。该电介质形成有凹进区和非凹进区。多个虚设结构形成在凹进区内,该虚设结构是构成的非活动区,以便增加后来形成在电介质上的金属层的平整度。然后形成金属层以便填充凹进区和覆盖非凹进区以及多个虚设结构。然后电抛光该金属层以便露出非凹进区。在一个实施例中,接着除去部分非凹进区。

附图说明

通过参考下面结合附图的详细描述能够更好地理解本发明,其中相同的部件由相同的附图标记表示:

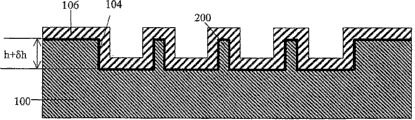

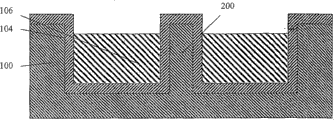

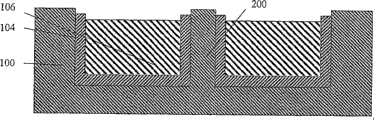

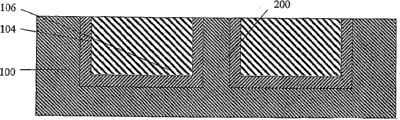

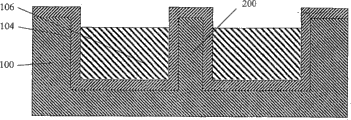

图1A-1D示出了例举的大马士革工艺的截面图;

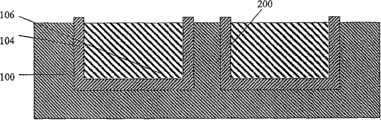

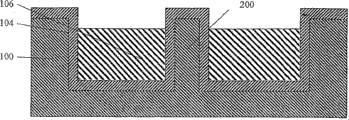

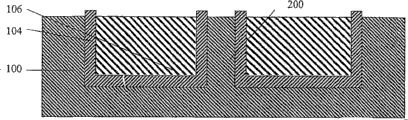

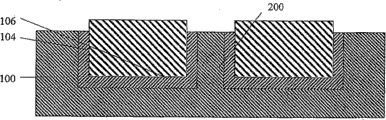

图2A-2D示出了另一个例举的大马士革工艺的截面图;

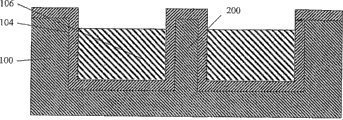

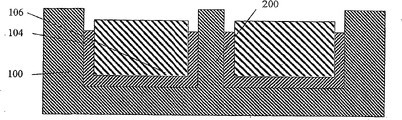

图3A-3E示出了例举的再一个大马士革工艺的截面图;

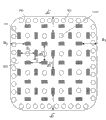

图4示出了例举的宽沟槽结构;

图5是说明根据本发明例举的大马士革工艺步骤的流程图;

图6A-6E示出了例举的用于在半导体器件中形成金属焊盘的工艺;

图7A-7E示出了例举的用于在半导体器件中形成金属焊盘的另一个工艺;

图8A-8D示出了例举的用于在半导体器件中形成金属焊盘的再一个工艺;

图9A和9B示出了例举的、能够利用本发明例举的各种工艺的半导体器件;

图10A和10B示出了另一个例举的、能够利用本发明例举的各种工艺的半导体器件;

图11A和11B示出了再一个例举的、能够利用本发明例举的各种工艺的半导体器件;

图12A和12B示出了又一个例举的、能够利用本发明例举的各种工艺的半导体器件;

图13示出了例举的大矩形结构的布局;

图14示出了另一个例举的大矩形结构的布局;

图15示出了再一个例举的大矩形结构的布局;

图16示出了又一个例举的大矩形结构的布局;

图17A-17AA示出了可以用来形成虚设结构的各种例举的形状;

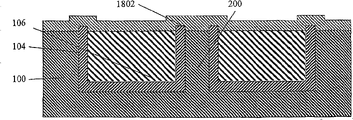

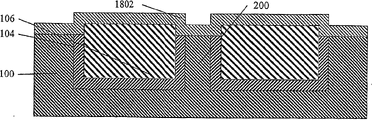

图18A-18E示出了例举的大马士革工艺的截面图;

图19A-19C示出了另一个例举的大马士革工艺的截面图;

图20A-20C示出了再一个例举的大马士革工艺的截面图;

图21A-21D示出了例举的再一个大马士革工艺的截面图;

图22A-22D示出了例举的又一个大马士革工艺的截面图;

图23A-23D示出了例举的另一个大马士革工艺的截面图;

图24A-24D示出了例举的另一个大马士革工艺的截面图;

图25A-25D示出了例举的另一个大马士革工艺的截面图;

图26A-26D示出了例举的另一个大马士革工艺的截面图;

图27A-27D示出了例举的另一个大马士革工艺的截面图;

具体实施方式

为了更好地理解本发明,下面提供了大量的具体细节,例如具体结构、参数、例子等。但是,应理解这些描述不是要限制本发明的范围,而是更好地描述了例举的实施例。

图1示出了例举的可以用来在半导体器件中形成互连的大马士革工艺,该半导体器件包括具有大的宽度、面积等的凹进区。具体来说,参考图1A,该半导体器件可以包括具有凹进区102和非凹进区103的介质100,其中凹进区102可以是如宽沟槽、大矩形结构等的结构。此外,介质100可以包括如二氧化硅等的材料或者是介电常数比二氧化硅低的材料,例如氟化硅酸盐玻璃、聚酰亚胺、氟化聚酰亚胺、杂化物/复合物、硅氧烷、有机聚合物、[α]-C:F、Si-O-C、聚对亚苯基二甲基/氟化聚对亚苯基二甲基、聚四氟乙烯、多纤孔二氧化硅、多纤孔有机物等。可以使用介电常数比二氧化硅低的材料来降低半导体器件中金属互连之间的电容。

在本例的工艺中,可以通过任何常规的淀积方法、例如化学汽相淀积(CVD)、物理汽相淀积(PVD)、原子层淀积(ALD)等在介质100上淀积阻挡层104,使得阻挡层104覆盖凹进区102和非凹进区103。由于介质100可以具有多孔的微观结构,因此阻挡层104可以包括那些能够防止后来淀积的金属层106(图1B)扩散或者渗漏到介质100中去的材料,如下所述。此外,阻挡层104可以由附着于介质100和金属层106(图1B)的导电材料构成。例如,阻挡层104可以包括如钛、钽、钨、氮化钛、氮化钽、氮化钨、氮化钽硅、氮化钨硅等材料。但是,应认识到,在某些应用中可以省略阻挡层104。例如当介质100由抗后来形成的金属层106扩散的材料构成时,或者当后来形成的金属层106的扩散不会严重影响半导体器件的性能时,可以省略阻挡层104。

参考图1B,可以通过任何便利方法例如PVD、CVD、ALD、电镀、化学镀等将金属层106淀积到阻挡层104上。此外,在某些应用中,例如当使用镀覆来淀积金属层106时,可以在淀积金属层106之前将籽晶层淀积到阻挡层104上。该籽晶层可以通过任何常规的方法淀积,例如CVD、PVD、ALD等。为了便于将金属层106淀积和粘结到阻挡层104或者介质100(如果不使用阻挡层104)上,该籽晶层可以包括与金属层106相同的材料。如图所示,金属层106可以填充凹进区102和覆盖非凹进区103。此外,金属层106可以包括各种导电材料,例如铜、铝、镍、铬、锌、镉、银、金、铑、钯、铂、锡、铅、铁、铟和超导材料等。优选,金属层106包括铜。此外,应认识到,金属层106可以包括各种导电材料的任何合金或者超导体化合物。

现在参考图1C,淀积金属层106之后,可以通过便利方法例如CMP、电抛光等从非凹进区103除去金属层106。应认识到,从非凹进区103抛光金属层106可以包括从任何中间层例如淀积到介质100上的阻挡层104等的非凹进区除去金属层106。对于电抛光的描述,参见2000年2月4日申请的美国专利序列号No.09/497894、名称为“METHODS AND APPARATUS FOR ELECTROPOLISHINGMETAL INTERCONNECTIONS ON SEMICONDUCTORDEVICES”,这里全文引入作为参考。

参考图1D,从非凹进区103除去金属层106之后,可以通过任何便利的方法例如湿蚀、干化学蚀刻、干等离子蚀刻和CMP等从非凹进区103除去阻挡层104。具体地说,如果使用等离子蚀刻,可以使用各向异性蚀刻或各向同性蚀刻。此外,用于等离子蚀刻的蚀刻气体可以包括如CF4、SF6、C4F8、O2、Ar、CO等的单个气体或气体组合。如果使用干化学蚀刻,可以使用如HF、H2O、NH4F、N2等的气体蒸气,其中使用N2使HF液体(浓度为49%)起泡以便产生HF和H2O蒸气。如果使用湿蚀,可以使用如HF、NH4F等的蚀刻液体。

如本例的工艺所示,当从非凹进区103除去金属层106时,会从凹进区102除去或者过抛光部分金属层106,从而引起凹进区102内的金属层106的表面与非凹进区103不平。这种凹进区102内金属层106的过抛光或表面凹陷由于凹进区102的大宽度而出现。这种表面凹陷会减小凹进区102内金属层106的截面积,由此增加由金属层106形成的互连的电阻。该增加的电阻会引起半导体器件发生故障。

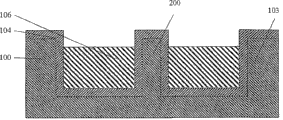

因此,如图2A-2D所示,可以在凹进区102内包括虚设结构200以便减小金属层106与非凹进区103的不平度。但是,如下所述,当使用电抛光法时,如果过抛光金属层106,在每个虚设结构200之间的凹进区内仍然会出现表面凹陷。

图2A-2D所示的工艺在许多方面与图1A-1D所示的工艺相同,除了在凹进区102内包括虚设结构200。具体地说,参考图2A,可以在介质100的凹进区102内包括虚设结构200。虚设结构200可以形成非凹进区103的一部分,并且可以包括与介质100相同的材料,或者根据应用可以包括任何其它材料。例如,虚设结构可以包括:如二氧化硅等的材料;介电常数比二氧化硅低的材料,例如氟化硅酸盐玻璃、聚酰亚胺、氟化聚酰亚胺、杂化物/复合物、硅氧烷、有机聚合物、[α]-C:F、Si-O-C、聚对亚苯基二甲基/氟化聚对亚苯基二甲基、聚四氟乙烯、多纤孔二氧化硅、多纤孔有机物等;和金属,例如铜、铝、镍、铬、锌、镉、银、金、铑、钯、铂、锡、铅、铁和铟等。

如果虚设结构200由与介质100相同的材料构成,那么虚设结构可以与凹进区102同时形成。但是应认识到,即使虚设结构200由与介质100相同的材料构成,也可以在形成凹进区之后形成虚设结构。作为选择,如果虚设结构200由与介质100不同的材料构成,那么可以在形成凹进区102之后形成虚设结构200。例如,在形成凹进区102之后,在凹进区中淀积金属例如铝等。然后可以掩模和蚀刻该金属以便形成由金属构成的虚设结构200。

包含在凹进区102中的虚设结构200的数量和虚设结构200之间的距离W1可以影响淀积到半导体器件上的金属层的平整度,如图2C所示。因此,虚设结构200之间的距离W1与淀积在非凹进区103上的金属层厚度T之比(W1/T)选择在大约1-5的范围内,优选大约小于2。但是,应认识到,根据具体的应用,该比值可以落在上述范围之外。此外,应认识到,可以根据应用使用任意数量的虚设结构。

尽管W1可以影响所淀积的金属层的平整度,但虚设结构200的宽度W2一般不影响所淀积的金属层的平整度。但是,W2可以影响由淀积在凹进区102中的金属层106形成的互连的有效截面积。因此,可以减小W2以便增加互连的有效截面积。具体地说,虚设结构200的宽度W2与淀积在非凹进区103上的金属层厚度T之比(W2/T)可以选择在大约0.1-1的范围内,优选大约0.3。但是,应认识到根据具体的应用,该比值可以落在上述范围之外。

在本例的工艺中,凹进区102中包括虚设结构200之后,可以淀积阻挡层104,使得阻挡层104覆盖凹进区102和非凹进区103,包括虚设结构200。如上所述,应理解,在某些应用中可以省略阻挡层104。

参考图2B-2C,可以在阻挡层104上淀积金属层106,使得金属层106填充凹进区102并且覆盖非凹进区103。如图2C所示,淀积在具有虚设结构200的凹进区102上的金属层106的表面比淀积在没有虚设结构的凹进区102上的金属层106(图1B)更平整。

参考图2D,淀积金属层106之后,可以从非凹进区103电抛光金属层106。然而,如果在从非凹进区103除去了金属层106之后使电抛光继续,在凹进区102中也会出现表面凹陷。尽管希望一定量的过抛光以便减小相邻互连短路的危险,但表面凹陷会影响所淀积的下一层的平整度,例如电介质、钝化层和覆盖层等。依次,所淀积的下一层的平整度影响后续工序,例如用来在后续层中形成互连的光刻等。应理解,使用虚设结构出现的表面凹陷针对电抛光。相比较而言,当仅使用CMP除去金属层106时,虚设结构200可以防止CMP抛光衬垫移过虚设结构200。因此虚设结构200可以防止CMP抛光衬垫从凹进区102过抛光金属层106。

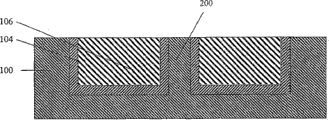

因此,如图3所示,可以除去非凹进区103的与金属层106不平的部分以便增加金属层106与非凹进区103的平整度。图3所示的例示工艺在许多方面与图2所示的工艺相同,除了图3所示的工艺包括从凹进区102过抛光金属层106,然后除去部分非凹进区103以便增加由金属层106形成的表面和非凹进区103的平整度。

具体地说,参考图3A,虚设结构200可以包括在介质100的凹进区102中,并且可以形成部分非凹进区103。凹进区102可以具有h+δh的深度,其中h是最后形成在凹进区102中的金属互连的理想高度,δh是偏移高度,如下所述。在凹进区102中包括虚设结构200之后,可以淀积阻挡层104使得阻挡层104覆盖凹进区102和非凹进区103,包括虚设结构200。如上所述,应理解在某些应用中可以省略阻挡层104。

参图3B和3C,可以在阻挡层104上淀积金属层106,使得金属层106填充凹进区102和覆盖非凹进区103。参考图3D,淀积金属层106之后,可以从非凹进区103电抛光金属层106。从非凹进区103电抛光金属层106可以包括从任何中间层例如淀积到介质100上的阻挡层104等的非凹进区除去金属层106。此外,可以继续电抛光直到从凹进区102将金属层106过抛光偏移高度量δh。根据本发明的一个实施例,该偏移高度可以选择在大约5nm-100nm的范围内。但是,应理解,根据具体的应用,该偏移高度可以是任何高度。

参考图3E从凹进区102过抛光金属层106之后,可以除去与金属层106不平的部分非凹进区103。更具体地说,可以通过任何便利的方法例如湿蚀、干化学蚀刻和干等离子蚀刻等除去阻挡层104、介质100和虚设结构200。具体地,如果使用等离子蚀刻,可以使用各向异性蚀刻或者各向同性蚀刻。此外,用于等离子蚀刻的蚀刻气体可以包括如CF4、SF6、C4F8、O2、Ar、CO等的单个气体或气体组合。如果使用干化学蚀刻,可以使用如HF、H2O、NH4F、N2等的气体蒸气,其中可以使用N2使HF液体(浓度为49%)起泡以便产生HF和H2O蒸气。如果使用湿蚀,可以使用如HF、NH4F等的蚀刻液体。此外,如果在介质100和虚设结构200上没有淀积阻挡层104,那么可以利用平整化工艺例如CMP等除去介质100和虚设结构200。然而,应理解可以通过蚀刻或者任何其它便利的工艺除去介质100和虚设结构200。

参考图4,图4示出了例举的凹进区100(图1-3)的类型。该凹进区是包括虚设结构200的宽沟槽结构,虚设结构200彼此间隔距离L和W。如图所示,虚设结构200可以是不连续的,使得淀积在宽沟槽结构102中的金属层能够在整个金属层内导电。此外,可以定位虚设结构200使得电流能够更均匀地流过金属层,从而增强由金属层形成的互连的可靠性。具体地说,虚设结构402之间的距离L与淀积在宽沟槽结构400的非凹进区上的金属层厚度T之比(L/T)可以选择在大约1-5的范围内,优选大约小于2。然而,应理解,根据具体地应用,该比值可以落在上述范围之外。

参考图5,图5是根据本发明例举的波纹(damascene)工艺的流程图。在步骤500中,可以提供具有凹进区和非凹进区的晶片。在步骤502中,虚设结构可以包括在凹进区中以便形成部分非凹进区。在步骤504中,淀积金属层使得金属层填充凹进区并且覆盖非凹进区。在步骤506中,可以从非凹进区电抛光并且从凹进区过抛光上述金属层。在步骤508中,可以除去与凹进区中的金属层不平的部分非凹进区。

但是,应理解的是,可以对本流程图中描述的工艺进行各种修改。例如,可以在步骤502和504之间添加淀积阻挡层的步骤。此外,应理解,图5所示的每个步骤都可以包括很多步骤。例如,步骤504可以包括在淀积金属层之前淀积籽晶层。此外,应理解图5所示的步骤可以用于任何大马士革工艺,包括单大马士革工艺和双大马士革工艺。

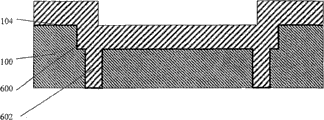

在图6中,示出了例举的用于在半导体器件中形成金属焊盘的工艺。图6所示的工艺在许多方面与图1所示的工艺相同,除了在半导体器件中包括通路602和大矩形结构600。

现在参考图6A和6B,介质100可以包括非凹进区103和形成大矩形结构600的凹进区。大矩形结构600可以与通路602连接。当用金属层106填充时,如下所述,大矩形结构600可以形成焊盘。此外,当用金属层106填充通路602时,如下所述,通路602可以形成栓塞,这些栓塞可以在半导体器件中从一个焊盘到其它焊盘或互连传导电流。如图6A所示,可以在大矩形结构600、通路602和非凹进区103上淀积阻挡层104。但是,如上所述,在某些应用中,可以省略阻挡层104。

下面参考图6C,可以将金属层106淀积到阻挡层104上,使得金属层106填充大矩形结构600、通路602并且覆盖非凹进区103。

参考图6D,淀积金属层106之后,可以从非凹进区103除去金属层106。从非凹进区103除去金属层106可以包括从任何中间层例如淀积到介质100上的阻挡层104等的非凹进区除去金属层106。从非凹进区103除去金属层106之后,参考图6E,可以从非凹进区103除去阻挡层104。

如本例的工艺所示,当从非凹进区103除去金属层106时,可以从大矩形结构600除去或者过抛光部分金属层106,从而引起大矩形结构600内金属层表面与非凹进区103不平。这种大矩形结构600内金属层106的过抛光或者表面凹陷会由于大矩形结构600的大尺寸而出现。这种表面凹陷可以减小大矩形结构600内金属层106的截面积,因此可以增加由金属层106形成的焊盘电阻。这种增加的电阻会引起半导体器件发生故障。

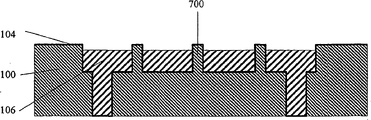

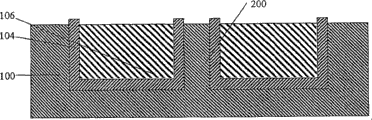

因此,如图7所示,可以在大矩形结构600中包括虚设结构700,以便减小金属层106与非凹进区103的不平度。图7所示的例举工艺在许多方面与图6所示的工艺相同,除了图7所示的工艺包括从大矩形结构600过抛光金属层106,然后除去部分非凹进区103,以便增加由金属层106形成的表面与非凹进区103的平整度。

具体地说,参考图7A和7B,可以在介质100的大矩形结构600中包括虚设结构700,并且可以形成部分非凹进区103。大矩形结构600可以具有h+δh的深度,其中h是最后金属互连的理想高度,δh是偏移高度,如下所述。在大矩形结构600中包括虚设结构700之后,可以淀积阻挡层104,使得阻挡层104覆盖大矩形结构600、通路602和非凹进区103,包括虚设结构700。如上所述,应理解在某些应用中可以省略阻挡层104。此外,如上所述,可以使用任意数量的虚设结构700。

下面参考图7C,可以将金属层106淀积到阻挡层104上,使得金属层106填充大矩形结构600和通路602,并且覆盖非凹进区103。淀积金属层106之后,参考图7D,可以从非凹进区103电抛光金属层106。从非凹进区103电抛光金属层106包括从任何中间层例如淀积到介质100上的阻挡层104等的非凹进区除去金属层106。此外,可以继续电抛光直到从大矩形结构600将金属层106过抛光偏移高度δh。根据本发明的一个实施例,该偏移高度可以选自在大约5-100nm的范围内。然而,应理解,根据具体的应用,该偏移高度可以是任何高度。

现在参考图7E,从大矩形结构600过抛光金属层106之后,可以除去与金属层106不平的部分非凹进区103。更具体地说,可以通过任何便利的方法例如湿蚀、干化学蚀刻和干等离子蚀刻等除去阻挡层104、介质100和虚设结构700。具体地说,如果使用等离子蚀刻,则可以使用各向同性或者各向异性蚀刻。此外,用于等离子蚀刻的蚀刻气体可以包括例如CF4、SF6、C4F8、O2、Ar和CO等的单个气体或者气体组合。如果使用干化学蚀刻,则可以使用例如HF、H2O、NH4F和N2等的气体蒸汽,其中可以利用N2使HF液体(浓度为49%)起泡,以便产生HF和H2O蒸汽。如果使用湿蚀,则可以使用如HF和NH4F等的蚀刻液体。此外,如果在介质100和虚设结构700上没有淀积阻挡层104,那么可以利用平整化工艺例如CMP等除去介质100和虚设结构700。然而,应理解,可以通过蚀刻或者任何其它便利的工艺除去介质100和虚设结构700。

图8示出了例举的另一个工艺。图8所示的例示工艺在许多方面与图7所示的工艺相同,除了在从大矩形结构600上过抛光金属层106之后,可以将非凹进区103的露出部分蚀刻到金属层106的表面以下。

具体地说,参考图8C,在半导体器件上淀积金属层106、使得金属层106填充凹进区600并且覆盖非凹进区103之后,可以从非凹进区103电抛光金属层106直到从大矩形结构600过抛光金属层106。

下面参考图8D,从大矩形结构600过抛光金属层106之后,可以将非凹进区103蚀刻到金属层106的表面以下。更具体地说,可以通过任何便利的方法例如湿蚀、干化学蚀刻和干等离子蚀刻等除去阻挡层104、介质100和虚设结构700。如图8D所示,然后从半导体器件的表面突出部分金属层106。

尽管例举的本工艺一般不用于常规的晶片制造,但该工艺可以用于制造适于进行电测试的晶片,所述电测试用于质量控制或者研究和开发的目的。具体地说,用于电测试的探针可以更牢靠和容易地接触金属层106的表面,从而增加半导体器件的焊盘和电测试设备的探针之间的导电率。这种增加的导电率可以产生更精确的测试结果。

参考图9,图9示出了可以用图7所示的工艺制造的半导体器件的另一个例举实施例。该图9所示的例示半导体器件在许多方面与图7B所示的例示半导体器件相同,除了添加了虚设结构900。这些附加的虚设结构900可以增加淀积在半导体器件上的金属层106的平整度,从而减小淀积在大矩形结构600中的金属层106的表面凹陷量。如前面所述,应理解,根据应用可以包括任意数量的虚设结构。此外,应理解,根据应用可以使用任意结构的虚设结构。

图10示出了可以利用图7所示的工艺制造的半导体器件的另一个例示实施例。图10所示的例示半导体器件在许多方面与图9B所示的例示半导体器件相同,除了大矩形结构600具有圆角。这些圆角可以减小半导体器件中的应力。

图11示出了可以利用图7所示的工艺制造的另一个半导体器件的例示实施例。图11所示的例示半导体器件在许多方面与图10所示的例示半导体器件相同,除了添加了附加虚设结构1100。这些附加的虚设结构1100可以增加淀积在半导体器件上的金属层106的平整度,从而减小淀积在大矩形结构600中的金属层106的表面凹陷量。如前面所述,应理解,根据应用可以包括任意数量的虚设结构。此外,应理解,根据应用可以使用任意结构的虚设结构。

图12示出了可以利用图7所示的工艺制造的另一个半导体的例示实施例。图12所示的例示实施例在许多方面与图11B所示的例示半导体器件相同,除了添加的附加的通路1200。当用金属层106填充时,这些附加的通路1200可以形成栓塞。这些栓塞可以增加相邻焊片之间的导电性,并且可以增强半导体器件中键合焊盘的机械强度。当在半导体器件中使用低介电常数、也就是较低机械强度的介质时,增强键合焊盘的机械强度在键合工艺中尤其有利。具有低介电常数的材料的一些例子包括氢-silsesquioxane(HSQ)、干凝胶、聚合物和气凝胶等。可以使用具有较低介电常数的材料来增加通过互连的信号的速度,所述互连形成在该材料内,并且可以使用具有低介电常数的材料来减小发送信号通过互连所需要的功耗。例如,SiO2具有大约4.0的介电常数,HSQ具有大约3.0-2.5的较低介电常数,干凝胶具有大约2.0的更低的介电常数。

图13示出了可以利用图7所示工艺的大矩形结构的例示布局。具体地说,大矩形结构600可以包括虚设结构900和700。虚设结构700以距离a1和b2彼此间隔,虚设结构900以距离a2和b1彼此间隔。此外,虚设结构700离大矩形结构600边缘的距离为b3,虚设结构900离大矩形结构600边缘的距离为a3。

在本例的布局中,根据图7所示的工艺,虚设结构700和900之间的距离影响淀积在半导体器件的非凹进区103上的、厚度为T的金属层106的平整度。具体地说,可以通过选择虚设结构之间的距离增加淀积在半导体器件上的金属层106的平整度,使得虚设结构之间的距离与厚度之比a1/T、ab/T、a1/T、b2/T和虚设结构与大矩形结构600的边缘之间的距离与厚度之比a3/T和b3/T在大约1-5的范围内,优选大约小于2。然而,应理解,根据具体的应用,可以选择该范围之外的其它比值。

尽管虚设结构之间的距离影响淀积在大矩形结构中的金属层的平整度,但虚设结构700和900的宽度W一般不影响所淀积的金属层的平整度。但是,W可以影响由淀积在大矩形结构600中的金属层形成的焊盘的有效截面积。因此,可以减小W以便增加焊盘的有效截面积。具体地说,虚设结构700和900的宽度W与淀积在非凹进区103上的金属层的厚度T之比(W/T)可以选择在大约0.1-1的范围内,优选大约0.3。但是,应理解,根据具体的应用,该比值可以落在上述范围之外。

图14示出了可以利用图7所示的工艺制造的大矩形结构的另一个例示布局。图14所示的例示布局在许多方面与图13所示的例示布局相同,除了添加的附加通路1200。如上所述,当用金属层106填充时,这些附加通路1200可以形成栓塞,这些栓塞可以增加相邻焊盘之间的导电率,并且可以增强半导体器件中键合焊盘的机械强度。如上所述,当在半导体器件中使用具有低介电常数、也就是较低机械强度的介质时,增强键合焊盘的机械强度在键合工艺中尤其有利。

图15示出了可以利用图7所示的工艺制造的大矩形结构的另一个例示布局。图15所示的例示布局在许多方面与图14所示的例示布局相同,除了添加了附加通路1500。如上所述,当用金属层106填充时,这些附加通路1500可以形成栓塞,这些栓塞能够增加相邻焊盘之间的导电率,并且能够增强半导体器件中键合焊盘的机械强度。如上所述,当在半导体器件中使用具有低介电常数、也就是较低机械强度的介质时,增强键合焊盘的机械强度在键合工艺中尤其有利。

图16示出了可以利用图7所示的工艺制造的大矩形结构的再一个例示布局。图16所示的例示布局在许多方面与图13所示的例示布局相同,除了虚设结构700和900的整个图形旋转了角度α,其中α可以选择为任意的角度,例如0°和360°之间的角度。

图17A-17AA示出了可以用来形成虚设结构的各种例示形状。具体地说,可以使用例如矩形、圆形、椭圆形、三角形、梯形、八边形、六边形、五边形等形状。应理解,尽管图17A-17AA示出了例示的具体形状,但根据具体的应用,可以使用任何形状来形成虚设结构。虚设结构可以由下列各种材料制成:例如二氧化硅等的材料;介电常数比二氧化硅低的材料,例如氟化硅酸盐玻璃、聚酰亚胺、氟化聚酰亚胺、杂化物/复合物、硅氧烷、有机聚合物、[α]-C:F、Si-O-C、聚对亚苯基二甲基/氟化聚对亚苯基二甲基、聚四氟乙烯、多纤孔二氧化硅、多纤孔有机物等;和金属,例如铜、铝、镍、铬、锌、镉、银、金、铑、钯、铂、锡、铅、铁和铟等。如上所述,在某些应用中,虚设结构可以由与所使用的介质相同的材料制成。

如图18所示,当根据上述工艺使用虚设结构时会出现问题。图18所示的工艺与图3所示的工艺相同,除了当除去部分非凹进区103时可以过除去阻挡层104。具体地说,参考图18C和18D,从凹进区102过抛光金属层106之后,可以除去与金属层106不平的部分非凹进区103。具体地说,可以通过蚀刻、CMP或者任何其它便利的工艺除去阻挡层104的暴露部分。

参考图18E,除去阻挡层104的暴露部分之后,可以在半导体器件上淀积覆盖层或者钝化层1802。该覆盖层或者钝化层1802可以包括绝缘材料,例如SiN、金刚石等。然而,如果在前面的步骤中过除去阻挡层104,那么在金属层106和介质100之间形成间隙1800,尤其当覆盖层1802没有填充由于阻挡层104的过除去而形成的空间时。当使用特定的金属和介质材料时,例如当金属层106由铜构成和介质100是具有低介电常数的材料时,间隙1800可以使金属层106扩散进入介质100。这种金属层106扩散进入介质100可以引起半导体器件的可靠性问题。

因此,图19-27示出了解决图18所存在问题的各种实施例。在一些例举的实施例中,可以除去非凹进区103,使得阻挡层104与介质100处于相同或者相近的水平面上。在其它一些实施例中,可以除去非凹进区103使得阻挡层104突出于介质100的表面。

图19示出了一个例示工艺,其中除去非凹进区103使得阻挡层104、金属层106和介质100每个都具有在相同或者相近水平面的表面。具体地说,参考图19A,从凹进区102过抛光金属层106之后(图18),可以以相同的速率除去阻挡层104和介质100,以便使阻挡层104和介质100的表面处于相同或者相近水平面上。具体地说,参考图19B,可以通过任何便利的方法例如湿蚀、干化学蚀刻、干等离子蚀刻和CMP等除去阻挡层104和介质100。例如,如果使用等离子蚀刻,等离子蚀刻可以包括低密度等离子(反应离子蚀刻)、高密度等离子(感应耦合等离子(ICP)、螺旋(Helicon)等离子(HP)、电子回旋共振(ECR)、常压等离子(无声放电等离子)等,等离子功率可以选择在大约500W和2000W之间,优选大约1000W。此外,在本例中,真空压力可以选择在大约30毫乇和100毫乇之间,优选大约50毫乇,半导体器件的温度可以选择为大约20℃,如果使用气体C4F8、O2和Ar,其流速分别约为8sccm、2sccm和100sccm。此外,可以按大约150nm/分钟的速度除去可以用作阻挡层104的TaN,可以按大约150nm/分钟的速度除去可以用作介质100的SiO2。

在本例的实施例中,参考图19C,按需要除去阻挡层104和介质100的部分之后,可以在半导体器件上淀积覆盖层1802。如图所示,当阻挡层104、介质100和金属层106具有相同或者相近的水平面时,可以消除间隙1800(图18),并且可以减少金属层106扩散到介质100中。

图20示出了一个例示工艺,其中除去非凹进区103使得阻挡层104突出于金属层106和介质100的表面。具体地说,参考图20A,从凹进区102过抛光金属层106之后(图18),可以以比介质100低的速度除去阻挡层104,以便使阻挡层104突出于介质100和金属层106的表面。具体地说,可以通过任何便利的方法例如湿蚀、干化学蚀刻、干等离子蚀刻、CMP等除去阻挡层104和介质100。例如,如果采用等离子蚀刻,等离子功率可以选择在大约500W和2000W之间,优选大约1000W。此外,在本例中,真空压力可以选择在大约50毫乇和120毫乇之间,优选大约90毫乇,半导体器件的温度可以选择为大约20℃,如果使用气体C4F8、O2和Ar,其流速可以分别约为8.5sccm、6.7sccm和115sccm。此外,如果使用TaN,可以按大约70nm/分钟的速度除去阻挡层104,如果使用TiN,可以按大约90nm/分钟的速度除去阻挡层104。另外,可以按大约300nm/分钟的速率除去可以用作介质100的SiO2。

在本例的例中,参考图20C,除去阻挡层104和介质100的想要部分之后,可以在半导体器件上淀积覆盖层1802。如图所示,当阻挡层104突出于介质100和金属层106的表面时,可以消除间隙1800(图18),并且可以减小金属层106扩散到介质100中。此外,与阻挡层104和介质100及金属层106形成在相同或者相近的水平面上相比,阻挡层104以上述方式突出可以更好地防止扩散。但是,当阻挡层104以上述方式突出时,会损失覆盖层1802的一些平整度。如所描述的,当形成半导体器件的后续层时,这种平整度的损失会引起一些问题。然而,根据应用,这种平整度的损失是可以接受的。

图21示出了例举的另一个工艺,其中除去非凹进区103使得阻挡层104突出于金属层106和介质100的表面。具体地说,参考图21A,从凹进区102过抛光金属层106之后(图18),可以在两个步骤中除去阻挡层104和介质100。参考图21B,在第一步骤中,可以按相同的速度除去阻挡层104和介质100。参考图21C,在第二步骤中,可以按比阻挡层104更高的速率除去介质100,以便使阻挡层104突出于介质100和金属层106的水平面。在某些应用中,可以在第二步骤停止除去阻挡层104,使得速率为0。此外,可以通过任何便利的方法,例如湿蚀、干化学蚀刻、干等离子蚀刻和CMP等除去阻挡层104和介质100。例如,在第一步骤中,可以使用等离子蚀刻,等离子功率可以选择在约500W和2000W之间,优选大约1000W。此外,在本例中,真空压力可以选择在约30毫乇和100毫乇之间,优选大约50毫乇,半导体器件的温度可以选择为约20C,如果使用气体C4F8,O2和Ar,其流速分别为约8sccm,2sccm和100sccm。此外,包括TaN的阻挡层104和包括SiO2的介质100都可以按约150nm/分钟的速率除去。

在本例的第二步骤中,可以使用等离子蚀刻,等离子功率可以选择在约500W和2000W之间,优选大约1000W。此外,在本例中,真空压力可以选择在约30毫乇和100毫乇之间,优选大约80毫乇,半导体器件的温度可以选择为约20C,如果使用SF6,其流速约为50sccm。此外,如果使用TaN,可以按约250nm/分钟的速率除去阻挡层104,如果使用TiN,使用大约300nm/分钟的速率。此外,可以使用SiO2作为介质100,并且按大约20nm/分钟的速率除去。

在本例的实施例中,参考图21D,除去阻挡层104和介质100的想要部分之后,可以在半导体器件上淀积覆盖层1802。如图所示,当阻挡层104突出于介质100和金属层106的表面时,可以消除间隙1800(图18),并且可以减少金属层106扩散到介质100中。如上所述,阻挡层104以上述方式突出会损失覆盖层1802的一些平整度。然而,根据应用,这种平整度的损失是可以接受的。

图22示出了例举的再一个工艺,其中除去非凹进区103使得阻挡层104突出于金属层106的表面。具体地说,参考图22A,从凹进区102过抛光金属层106之后(图18),可以在两个步骤中除去阻挡层104和介质100。参考图22B,在第一步骤中,可以按比介质100高的速率除去阻挡层104。参考图22C,在第二步骤中,可以按更高的速率除去介质100,而阻挡层104的除去速率为零,以便使阻挡层104突出于介质100和金属层106的表面。具体地说,可以通过任何便利的方法、例如湿蚀、干化学蚀刻、干等离子蚀刻和CMP等除去阻挡层104和介质100。

例如,在第一步骤中,可以使用等离子蚀刻,等离子功率可以选择在约500W和2000W之间,优选大约1000W。此外,在本例中,真空压力可以选择在约30毫乇和100毫乇之间,优选大约80毫乇,半导体器件的温度可以选择为约20C,如果使用SF6,其流速约为50sccm。此外,如果使用TaN,可以按约250nm/分钟的速率除去阻挡层104,如果使用TiN,按大约300nm/分钟的速率除去。此外,包括SiO2的介质100按大约20nm/分钟的速率除去。在本例的第二步骤中,用于第一步骤的设置可以相同,除了可以停止阻挡层104的除去并且将速率设置为零。

在本例的实施例中,参考图22D,除去阻挡层104和介质100的想要部分之后,可以在半导体器件上淀积覆盖层1802。如图所示,当阻挡层104突出于介质100和金属层106的表面时,可以消除间隙1800(图18),并且可以减少金属层106扩散到介质100中。如上所述,阻挡层104以上述方式突出会损失覆盖层1802的一些平整度。然而,根据应用,这种平整度的损失是可以接受的。

图23示出了例举的又一个工艺,其中除去非凹进区103使得阻挡层104、金属层106和介质100每个都具有相同或者相近的水平面。具体地说,参考图23A,从凹进区102过抛光金属层106之后(图18),可以在两个步骤中除去阻挡层104和介质100。参考图23B,在第一步骤中,可以按比介质100高的速率除去阻挡层104。参考图23C,在第二步骤中,可以按比阻挡层104高的速率除去介质100,以便使阻挡层104和介质100形成相同或者相近的水平面。具体地说,可以通过任何便利的方法、例如湿蚀、干化学蚀刻、干等离子蚀刻和CMP等除去阻挡层104和介质100。

例如,在第一步骤中,可以使用等离子蚀刻,等离子功率可以选择在约500W和2000W之间,优选大约1000W。此外,在本例中,真空压力可以选择在约30毫乇和100毫乇之间,优选大约80毫乇,半导体器件的温度可以选择为约20C,如果使用SF6,其流速约为50sccm。此外,如果使用TaN,可以按约250nm/分钟的速率除去阻挡层104,如果使用TiN,按大约300nm/分钟的速率除去。此外,包括SiO2的介质100可以按大约20nm/分钟的速率除去。

在本例的第二步骤中,可以使用等离子蚀刻,等离子功率可以选择在约500W和2000W之间,优选大约1000W。此外,在本例中,真空压力可以选择在约50毫乇和120毫乇之间,优选大约90毫乇,半导体器件的温度可以选择为约20C,如果使用气体C4F8、O2和Ar,其流速分别约为8.5sccm、6.7sccm和115sccm。此外,如果使用TaN,可以按约70nm/分钟的速率除去阻挡层104,如果使用TiN,可以按大约90nm/分钟的速率除去。此外,包括SiO2的介质100可以按大约300nm/分钟的速率除去。

在本例的实施例中,参考图23D,除去阻挡层104和介质100的想要部分之后,可以在半导体器件上淀积覆盖层1802。如图所示,当阻挡层104、介质100和金属层106具有相同或者相近的水平面时,可以消除间隙1800(图18),并且可以减少金属层106扩散到介质100中。尽管由本例举的工艺制造的半导体器件的平整度会比包括突出于介质100和金属层106的阻挡层104的半导体器件更好,但与包括突出于介质100和金属层106的阻挡层104的半导体器件相比,由本例举的工艺制造的半导体器件增加了金属层106扩散进入介质100的危险。

图24示出了例举的再一个工艺,其中除去非凹进区103使得阻挡层104、介质100和金属层106都具有相同或者相近的水平面。具体地说,参考图24A,从凹进区102过抛光金属层106之后(图18),可以在两个步骤中除去阻挡层104和介质100。参考图24B,在第一步骤中,可以按较高的速率除去阻挡层104,同时介质100以零速率除去。参考图24C,在第二步骤中,可以按比较高的速率除去介质100,而阻挡层104可以按零速率除去,以便使阻挡层104和介质100形成相同或者相近的水平面。具体地说,可以通过任何便利的方法、例如湿蚀、干化学蚀刻、干等离子蚀刻和CMP等除去阻挡层104和介质100。

在本例的实施例中,参考图24D,除去阻挡层104和介质100的想要部分之后,可以在半导体器件上淀积覆盖层1802。如图所示,当阻挡层104、介质100和金属层106具有相同或者相近的水平面时,可以消除间隙1800(图18),并且可以减少金属层106扩散到介质100中。尽管半导体器件的平整度会比包括突出于介质100和金属层106的阻挡层104的半导体器件更好,但与包括突出于介质100和金属层106的阻挡层104的半导体器件相比,由本例举的工艺制造的半导体器件增加了金属层106扩散进入介质100的危险。

图25示出了例举的又一个工艺,其中除去非凹进区103使得阻挡层104、介质100和金属层106具有相同或者相近的水平面。具体地说,参考图25A,从凹进区102过抛光金属层106之后(图18),可以在两个步骤中除去阻挡层104和介质100。参考图25B,在第一步骤中,可以按比介质100低的速率除去阻挡层104。参考图25C,在第二步骤中,可以按比较高的速率除去阻挡层104,而以零速率除去介质100,以便使阻挡层104和介质100形成相同或者相近的表面。具体地说,可以通过任何便利的方法、例如湿蚀、干化学蚀刻、干等离子蚀刻和CMP等除去阻挡层104和介质100。例如,在第一步骤中,可以使用等离子蚀刻,等离子功率可以选择在约500W和2000W之间,优选大约1000W。此外,在本例中,真空压力可以选择在约50毫乇和120毫乇之间,优选大约90毫乇,半导体器件的温度可以选择为约20C,如果使用气体C4F8、O2和Ar,其流速分别约为8.5sccm、6.7sccm和115sccm。此外,如果使用TaN,可以按约70nm/分钟的速率除去阻挡层104,如果使用TiN,按大约90nm/分钟的速率除去。此外,包括SiO2的介质100可以按大约300nm/分钟的速率除去。在本例的第二步骤中,可以使用与第一步骤相同的设置,除了可以停止介质100的除去并且设置为零速率。

在例举的本实施例中,参考图25D,除去阻挡层104和介质100的想要部分之后,可以在半导体器件上淀积覆盖层1802。如图所示,当阻挡层104、介质100和金属层106具有相同或者相近的水平面时,可以消除间隙1800(图18),并且可以减少金属层106扩散到介质100中。尽管半导体器件的平整度会比包括突出于介质100和金属层106的阻挡层104的半导体器件更好,但与包括突出于介质100和金属层106的阻挡层104的半导体器件相比,由本例举的工艺制造的半导体器件增加了金属层106扩散进入介质100的危险。

图26示出了例举的又一个工艺,其中除去非凹进区103使得金属层106突出于介质100和阻挡层104的水平面。尽管本例举的工艺一般不用于常规的晶片制造,但该工艺可以用于制造适于进行电测试的晶片,所述电测试用于质量控制或者研究及开发。具体地说,用于电测试的探针能够更牢靠和更容易地接触金属层106的表面,从而增加半导体器件的焊盘和电测试装置的探针之间的导电率。这种增加的导电率可以产生更精确的测试结果。

参考图26A,从凹进区102过抛光金属层106之后(图18),可以在两个步骤中除去阻挡层104和介质100。参考图26B,在第一步骤中,可以按比介质100高的速率除去阻挡层104。参考图26C,在第二步骤中,可以按比较高的速率除去介质100,而以零速率除去阻挡层104。具体地说,可以通过任何便利的方法、例如湿蚀、干化学蚀刻、干等离子蚀刻和CMP等除去阻挡层104和介质100。

在本例的工艺中,参考图26D,除去阻挡层104和介质100的想要部分之后,可以在半导体器件上淀积覆盖层1802。可以使用覆盖层1802来防止本层扩散进入后来形成的层。

图27示出了另一个例举的工艺,其中除去非凹进区103,使得金属层106突出于介质100和阻挡层104的平面。与图26所示的工艺相同,例举的本实例一般不用于常规的晶片制造,但本工艺可以用于制造适于进行电测试的晶片,所述电测试用于质量控制或者研究和开发。具体地说,用于电测试的探针可以更牢靠和容易地接触金属层106的表面,从而增加半导体器件的焊盘和电测试装置的探针之间的导电率。这种增加的导电率可以产生更精确的测试结果。

参考图27A,从凹进区102过抛光金属层106之后(图18),可以在两个步骤中除去阻挡层104和介质100。参考图27B,在第一步骤中,可以按较高的速率除去阻挡层104,而以零速率除去介质100。参考图26C,在第二步骤中,可以按比较高的速率除去介质100,而以零速率除去阻挡层104。具体地说,可以通过任何便利的方法、例如湿蚀、干化学蚀刻、干等离子蚀刻和CMP等除去阻挡层104和介质100。

在本例的实施例中,参考图27D,除去阻挡层104和介质100的想要部分之后,可以在半导体器件上淀积覆盖层1802。可以使用覆盖层1802来防止本层扩散进入后来形成的层。

表1提供了参考图19-27描述的各种例示实施例的总结。具体地说,每列包括在第一步骤中除去阻挡层104和介质100的速率的不同组合,每行包括在第二步骤中除去阻挡层104和介质100的速率的不同组合。

| 步骤1:以相同的速率除去阻挡层和介质 | 步骤1:以比介质高的速率除去阻挡层 | 步骤1:以比阻挡层高的速率除去介质 | |

| 没有步骤2 | 图19 | N/A | 图20 |

| 步骤2:以相同的速率除去阻挡层和介质 | N/A | N/A | N/A |

| 步骤2:以比介质高的速率除去阻挡层 | N/A | N/A | 图25 |

| 步骤2:以比阻挡层高的速率除去介质 | 图21 | 图22、图23、图24、图26、图27 | N/A |

表1

表1示出了除去介质100和阻挡层104的速率的具体组合,然而,应理解,根据应用可以使用其它除去速率的组合。

尽管已经根据某些实施例、例子和应用描述了本发明,但对于本领域技术人员来说显而易见,在不离开本发明的情况下可以进行各种修改和改变。

Claims (68)

1.一种电抛光半导体晶片上的金属层的方法,包括:

在半导体晶片上形成电介质层,

其中该电介质层形成有凹进区和非凹进区;

在凹进区内形成多个虚设结构,

其中构成的虚设结构是用于增加随后形成在电介质层上的金属层的平整度的非活动区;

形成一个金属层以便填充凹进区并且覆盖所述非凹进区和所述多个虚设结构;和

电抛光所述金属层以便露出所述非凹进区。

2.权利要求1的方法,其中凹进区具有与电抛光之后留在凹进区内的金属层的厚度相应的深度和与电抛光之后露出的非凹进区的表面和电抛光之后留在凹进区内的金属层表面之间的距离对应的偏移高度。

3.权利要求2的方法,进一步包括将露出的非凹进区除去与偏移高度相等的深度。

4.权利要求3的方法,其中偏移高度在5纳米和100纳米之间。

5.权利要求1的方法,其中形成金属层包括淀积金属层。

6.权利要求1的方法,其中形成金属层包括电镀金属层。

7.权利要求1的方法,其中多个虚设结构中的每一个都具有一个宽度,

其中金属层具有一个厚度,

其中该厚度取决于淀积在非凹进区上的金属层,和

其中所述宽度与所述厚度之比在0.1至1之间。

8.权利要求7的方法,其中所述宽度与所述厚度之比为0.3。

9.权利要求1的方法,

其中多个虚设结构彼此间隔一定的距离,

其中金属层具有一个厚度,

其中该厚度取决于淀积在非凹进区上的金属层,且

所述距离与厚度之比在1至5之间。

10.权利要求9的方法,其中所述距离与厚度之比小于2。

11.权利要求1的方法,进一步包括:在形成金属层之前,在电介质层上形成阻挡层。

12.权利要求1的方法,进一步包括:在形成金属层之前,在电介质层上形成籽晶层。

13.权利要求1的方法,进一步包括:电抛光金属层之后,在半导体晶片上形成覆盖层。

14.权利要求1的方法,其中凹进区是构成的宽沟槽,以便当用金属层填充时形成互连。

15.权利要求1的方法,其中凹进区是构成的大矩形结构,以便当用金属层填充时形成焊盘。

16.权利要求15的方法,进一步包括:除去在电抛光的金属层表面上方的露出的非凹进区,以便形成突出于电介质层的焊盘,便于焊盘和用于电测试的探针之间的接触。

17.权利要求15的方法,其中大矩形结构具有圆形角。

18.权利要求1的方法,其中金属层是铜。

19.权利要求1的方法,其中所述多个虚设结构包括与电介质层相同的材料。

20.权利要求1的方法,其中所述多个虚设结构包括金属。

21.权利要求1的方法,进一步包括:

过抛光超过露出的非凹进区表面的金属层;和

除去在电抛光之后与凹进区中的金属层不平的露出的非凹进区部分。

22.权利要求21的方法,其中所除去的非凹进区部分具有5纳米至100纳米之间的厚度。

23.一种电抛光半导体晶片上的金属层的方法,包括:

在半导体晶片上形成电介质层,

其中该电介质层形成有凹进区和非凹进区;

在凹进区内形成多个虚设结构,

其中该多个虚设结构是非活动区,用于增加后来形成在电介质层上的金属层的平整度;

形成一个阻挡层以便覆盖凹进区、非凹进区和多个虚设结构;

形成一个金属层以便填充所述凹进区并覆盖所述非凹进区和所述多个虚设结构;

电抛光金属层以便露出淀积在所述非凹进区上的所述阻挡层;

以第一速率除去露出的阻挡层;和

以第二速率除去电介质层的非凹进区。

24.权利要求23的方法,其中在以第一速率除去露出的阻挡层和以第二速率除去电介质层的非凹进区之后,露出的阻挡层和电介质层的非凹进区具有平的表面。

25.权利要求23的方法,其中在以第一速率除去露出的阻挡层和以第二速率除去非凹进区之后,露出的阻挡层突出于非凹进区。

26.权利要求23的方法,其中第一速率等于第二速率。

27.权利要求23的方法,其中第一速率小于第二速率。

28.权利要求23的方法,进一步包括:

以第三速率除去露出的阻挡层;和

以第四速率除去介质的非凹进区。

29.权利要求28的方法,其中第三速率比第四速率高。

30.权利要求29的方法,其中第四速率是零。

31.权利要求28的方法,其中第四速率高于第三速率。

32.权利要求31的方法,其中第三速率为零。

33.权利要求28的方法,其中第一速率高于第二速率。

34.权利要求28的方法,其中在以第三速率除去露出的阻挡层和以第四速率除去非凹进区之后,露出的阻挡层和非凹进区具有平的表面。

35.权利要求28的方法,其中在以第三速率除去露出的阻挡层和以第四速率除去非凹进区之后,露出的阻挡层突出于非凹进区。

36.权利要求23的方法,

其中多个虚设结构中的每一个都具有宽度,

其中金属层具有厚度,

其中该厚度取决于淀积在非凹进区上的金属层,和

其中宽度与厚度之比在0.1至1之间。

37.权利要求23的方法,

其中多个虚设结构彼此间隔一定的距离,

其中金属层具有厚度,

其中该厚度取决于淀积在非凹进区上的金属层,和

其中距离与厚度之比在1至5之间。

38.权利要求23的方法,进一步包括:在淀积金属层之前,在电介质层上淀积籽晶层。

39.权利要求23的方法,进一步包括:在电抛光金属层之后,在半导体晶片上淀积覆盖层。

40.权利要求23的方法,

其中构成的凹进区是宽的沟槽,以便当用金属层填充时形成互连。

41.权利要求23的方法,其中凹进区是构成的大矩形结构,以便当用金属层填充时形成焊盘。

42.权利要求41的方法,进一步包括:除去露出的阻挡层和超过金属层表面的介质的非凹进区,以便形成突出于电介质层的焊盘,便于该焊盘和用于电测试的探针之间的接触。

43.权利要求41的方法,其中大矩形结构具有圆形角。

44.权利要求23的方法,其中金属层是铜。

45.权利要求23的方法,其中所述多个虚设结构包括与半导体晶片相同的材料。

46.权利要求23的方法,其中所述多个虚设结构包括金属。

47.权利要求23的方法,其中形成金属层包括淀积金属层。

48.权利要求23的方法,其中形成金属层包括电镀金属层。

49.一种电抛光半导体晶片上的金属层的方法,包括:

在半导体晶片上形成电介质层,

其中该电介质层形成有凹进区和非凹进区;

在凹进区内形成至少一个虚设结构;

形成金属层以覆盖虚设结构和非凹进区,并且填充凹进区;和

从凹进区和非凹进区过抛光金属层,以便露出非凹进区,

其中过抛光使非凹进区突出于凹进区中的金属层表面。

50.权利要求49的方法,进一步包括除去突出于该表面的非凹进区部分。

51.权利要求50的方法,其中所除去的非凹进区部分具有5至100纳米之间的厚度。

52.权利要求49的方法,其中形成金属层包括淀积金属层。

53.权利要求49的方法,其中形成金属层包括电镀金属层。

54.权利要求49的方法,

其中虚设结构具有宽度,

其中金属层具有厚度,

其中该厚度取决于淀积在非凹进区上的金属层,和

其中该宽度与厚度之比在0.1至1之间。

55.权利要求54的方法,其中所述宽度与厚度之比值为0.3。

56.权利要求49的方法,

其中虚设结构与非凹进区隔开一定的距离,

其中金属层具有厚度,

其中该厚度取决于淀积在非凹进区上的金属层,和

其中所述距离与所述厚度之比在1至5之间。

57.权利要求49的方法,进一步包括:在形成金属层之前,在电介质层上形成阻挡层。

58.权利要求49的方法,进一步包括在形成金属层之前,在电介质层上形成籽晶层。

59.权利要求49的方法,进一步包括在电抛光金属层之后,在半导体晶片上形成覆盖层。

60.权利要求49的方法,其中凹进区是构成的宽沟槽,以便当用金属层填充时形成互连。

61.权利要求49的方法,其中凹进区是构成的大矩形结构,以便当用金属层填充时形成焊盘。

62.权利要求61的方法,进一步包括除去露出的超过金属层表面的非凹进区,以便形成突出于电介质层的焊盘,便于该焊盘和用于电测试的探针之间的接触。

63.权利要求49的方法,其中金属层是铜。

64.权利要求50的方法,其中虚设结构包括与电介质层相同的材料。

65.权利要求49的方法,其中虚设结构包括金属。

66.一种根据权利要求1的方法形成在半导体晶片上的线。

67.一种根据权利要求15的方法形成在半导体晶片上的焊盘结构。

68.一种根据权利要求14的方法形成在半导体晶片上的互连结构。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US28627301P | 2001-04-24 | 2001-04-24 | |

| US60/286,273 | 2001-04-24 | ||

| US10/108,614 US6638863B2 (en) | 2001-04-24 | 2002-03-27 | Electropolishing metal layers on wafers having trenches or vias with dummy structures |

| US10/108,614 | 2002-03-27 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1663036A CN1663036A (zh) | 2005-08-31 |

| CN100541746C true CN100541746C (zh) | 2009-09-16 |

Family

ID=26806086

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB028088344A Expired - Fee Related CN100541746C (zh) | 2001-04-24 | 2002-04-04 | 电抛光具有带虚设结构的沟槽或者通路的晶片上的金属层 |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US6638863B2 (zh) |

| EP (1) | EP1382065A4 (zh) |

| JP (1) | JP2004527126A (zh) |

| KR (1) | KR101018187B1 (zh) |

| CN (1) | CN100541746C (zh) |

| TW (1) | TWI258814B (zh) |

| WO (1) | WO2002086961A1 (zh) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104637862A (zh) * | 2013-11-14 | 2015-05-20 | 盛美半导体设备(上海)有限公司 | 半导体结构形成方法 |

Families Citing this family (49)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6939795B2 (en) * | 2002-09-23 | 2005-09-06 | Texas Instruments Incorporated | Selective dry etching of tantalum and tantalum nitride |

| US8021976B2 (en) * | 2002-10-15 | 2011-09-20 | Megica Corporation | Method of wire bonding over active area of a semiconductor circuit |

| US6991526B2 (en) * | 2002-09-16 | 2006-01-31 | Applied Materials, Inc. | Control of removal profile in electrochemically assisted CMP |

| US6848970B2 (en) * | 2002-09-16 | 2005-02-01 | Applied Materials, Inc. | Process control in electrochemically assisted planarization |

| US6962524B2 (en) | 2000-02-17 | 2005-11-08 | Applied Materials, Inc. | Conductive polishing article for electrochemical mechanical polishing |

| US20040182721A1 (en) * | 2003-03-18 | 2004-09-23 | Applied Materials, Inc. | Process control in electro-chemical mechanical polishing |

| US20040253809A1 (en) * | 2001-08-18 | 2004-12-16 | Yao Xiang Yu | Forming a semiconductor structure using a combination of planarizing methods and electropolishing |

| US6837983B2 (en) * | 2002-01-22 | 2005-01-04 | Applied Materials, Inc. | Endpoint detection for electro chemical mechanical polishing and electropolishing processes |

| WO2003088316A2 (en) * | 2002-04-12 | 2003-10-23 | Acm Research, Inc. | Electropolishing and electroplating methods |

| US20060234508A1 (en) * | 2002-05-17 | 2006-10-19 | Mitsuhiko Shirakashi | Substrate processing apparatus and substrate processing method |

| KR100467803B1 (ko) * | 2002-07-23 | 2005-01-24 | 동부아남반도체 주식회사 | 반도체 소자 제조 방법 |

| US20050061674A1 (en) * | 2002-09-16 | 2005-03-24 | Yan Wang | Endpoint compensation in electroprocessing |

| US7112270B2 (en) * | 2002-09-16 | 2006-09-26 | Applied Materials, Inc. | Algorithm for real-time process control of electro-polishing |

| US6812069B2 (en) * | 2002-12-17 | 2004-11-02 | Taiwan Semiconductor Manufacturing Co., Ltd | Method for improving semiconductor process wafer CMP uniformity while avoiding fracture |

| JP2004273438A (ja) * | 2003-02-17 | 2004-09-30 | Pioneer Electronic Corp | エッチング用マスク |

| US7042065B2 (en) * | 2003-03-05 | 2006-05-09 | Ricoh Company, Ltd. | Semiconductor device and method of manufacturing the same |

| US6693357B1 (en) * | 2003-03-13 | 2004-02-17 | Texas Instruments Incorporated | Methods and semiconductor devices with wiring layer fill structures to improve planarization uniformity |

| JP4575651B2 (ja) * | 2003-06-04 | 2010-11-04 | 富士ゼロックス株式会社 | 積層構造体の製造方法および積層構造体 |

| US7223685B2 (en) * | 2003-06-23 | 2007-05-29 | Intel Corporation | Damascene fabrication with electrochemical layer removal |

| KR100546354B1 (ko) * | 2003-07-28 | 2006-01-26 | 삼성전자주식회사 | 원하는 분석 위치를 용이하게 찾을 수 있는 반도체 소자 |

| JP2005057003A (ja) * | 2003-08-01 | 2005-03-03 | Sanyo Electric Co Ltd | 半導体集積回路装置 |

| US6818517B1 (en) * | 2003-08-29 | 2004-11-16 | Asm International N.V. | Methods of depositing two or more layers on a substrate in situ |

| US7071074B2 (en) * | 2003-09-24 | 2006-07-04 | Infineon Technologies Ag | Structure and method for placement, sizing and shaping of dummy structures |

| US20080306126A1 (en) * | 2004-01-05 | 2008-12-11 | Fonseca Vivian A | Peroxisome proliferator activated receptor treatment of hyperhomocysteinemia and its complications |

| KR100580110B1 (ko) * | 2004-05-28 | 2006-05-12 | 매그나칩 반도체 유한회사 | 반도체 소자의 더미 패턴 구조 |

| US7339272B2 (en) * | 2004-06-14 | 2008-03-04 | Taiwan Semiconductor Manufacturing Company, Ltd. | Semiconductor device with scattering bars adjacent conductive lines |

| JP2006173501A (ja) * | 2004-12-17 | 2006-06-29 | Sanyo Electric Co Ltd | 半導体装置及びその製造方法 |

| US7655565B2 (en) * | 2005-01-26 | 2010-02-02 | Applied Materials, Inc. | Electroprocessing profile control |

| CN101142668A (zh) | 2005-03-16 | 2008-03-12 | 富士通株式会社 | 半导体装置及其制造方法 |

| KR100724191B1 (ko) * | 2005-12-28 | 2007-05-31 | 동부일렉트로닉스 주식회사 | 반도체소자의 화학적기계 연마방법 |

| US7422982B2 (en) * | 2006-07-07 | 2008-09-09 | Applied Materials, Inc. | Method and apparatus for electroprocessing a substrate with edge profile control |

| JP5055980B2 (ja) * | 2006-11-29 | 2012-10-24 | 富士通セミコンダクター株式会社 | 電子装置の製造方法および半導体装置の製造方法 |

| KR100910447B1 (ko) * | 2007-05-18 | 2009-08-04 | 주식회사 동부하이텍 | 금속 패드 형성 방법 |

| US8957484B2 (en) * | 2008-02-29 | 2015-02-17 | University Of Washington | Piezoelectric substrate, fabrication and related methods |

| KR101487370B1 (ko) * | 2008-07-07 | 2015-01-30 | 삼성전자주식회사 | 마스크 레이아웃의 형성 방법 및 마스크 레이 아웃 |

| JP5412517B2 (ja) * | 2008-08-20 | 2014-02-12 | エーシーエム リサーチ (シャンハイ) インコーポレーテッド | バリア層除去方法及び装置 |

| KR20100060309A (ko) * | 2008-11-27 | 2010-06-07 | 주식회사 동부하이텍 | 반도체 소자 |

| US8604898B2 (en) * | 2009-04-20 | 2013-12-10 | International Business Machines Corporation | Vertical integrated circuit switches, design structure and methods of fabricating same |

| KR101377240B1 (ko) * | 2009-06-26 | 2014-03-20 | 가부시키가이샤 사무코 | 실리콘 웨이퍼의 세정 방법 및, 그 세정 방법을 이용한 에피택셜 웨이퍼의 제조 방법 |

| US8432031B1 (en) * | 2009-12-22 | 2013-04-30 | Western Digital Technologies, Inc. | Semiconductor die including a current routing line having non-metallic slots |

| US9443796B2 (en) * | 2013-03-15 | 2016-09-13 | Taiwan Semiconductor Manufacturing Company, Ltd. | Air trench in packages incorporating hybrid bonding |

| US9159670B2 (en) | 2013-08-29 | 2015-10-13 | Qualcomm Incorporated | Ultra fine pitch and spacing interconnects for substrate |

| US8772951B1 (en) * | 2013-08-29 | 2014-07-08 | Qualcomm Incorporated | Ultra fine pitch and spacing interconnects for substrate |

| CN103474393B (zh) | 2013-09-11 | 2015-07-08 | 华进半导体封装先导技术研发中心有限公司 | 免cmp的电镀面铜去除及阻挡层复用的工艺方法 |

| CN104793298B (zh) * | 2015-04-13 | 2017-03-22 | 华进半导体封装先导技术研发中心有限公司 | 一种带侧面焊盘的载板结构及其制作方法 |

| US10312141B2 (en) * | 2016-08-16 | 2019-06-04 | Northrop Grumman Systems Corporation | Preclean methodology for superconductor interconnect fabrication |

| CN106803495B (zh) * | 2016-12-28 | 2019-11-22 | 上海集成电路研发中心有限公司 | 金属埋层凸起的去除方法以及空气隙的制备方法 |

| JP7353121B2 (ja) | 2019-10-08 | 2023-09-29 | キヤノン株式会社 | 半導体装置および機器 |

| US11976002B2 (en) * | 2021-01-05 | 2024-05-07 | Applied Materials, Inc. | Methods for encapsulating silver mirrors on optical structures |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1264162A (zh) * | 1999-02-13 | 2000-08-23 | 国际商业机器公司 | 用于铝化学抛光的虚拟图形 |

Family Cites Families (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4127459A (en) | 1977-09-01 | 1978-11-28 | Jumer John F | Method and apparatus for incremental electro-polishing |

| US4190513A (en) | 1978-09-18 | 1980-02-26 | Jumer John F | Apparatus for containerless portable electro-polishing |

| US5256565A (en) * | 1989-05-08 | 1993-10-26 | The United States Of America As Represented By The United States Department Of Energy | Electrochemical planarization |

| JPH0438852A (ja) * | 1990-06-04 | 1992-02-10 | Hitachi Ltd | 多層配線を有する半導体装置 |

| US5486234A (en) * | 1993-07-16 | 1996-01-23 | The United States Of America As Represented By The United States Department Of Energy | Removal of field and embedded metal by spin spray etching |

| JP3297220B2 (ja) * | 1993-10-29 | 2002-07-02 | 株式会社東芝 | 半導体装置の製造方法および半導体装置 |

| US5602423A (en) * | 1994-11-01 | 1997-02-11 | Texas Instruments Incorporated | Damascene conductors with embedded pillars |

| JPH08195393A (ja) * | 1995-01-17 | 1996-07-30 | Toshiba Corp | メタル配線形成方法 |

| JP3382467B2 (ja) * | 1995-09-14 | 2003-03-04 | キヤノン株式会社 | アクティブマトリクス基板の製造方法 |

| US6309956B1 (en) | 1997-09-30 | 2001-10-30 | Intel Corporation | Fabricating low K dielectric interconnect systems by using dummy structures to enhance process |

| US6045434A (en) | 1997-11-10 | 2000-04-04 | International Business Machines Corporation | Method and apparatus of monitoring polishing pad wear during processing |

| US6395152B1 (en) * | 1998-07-09 | 2002-05-28 | Acm Research, Inc. | Methods and apparatus for electropolishing metal interconnections on semiconductor devices |

| US6232231B1 (en) * | 1998-08-31 | 2001-05-15 | Cypress Semiconductor Corporation | Planarized semiconductor interconnect topography and method for polishing a metal layer to form interconnect |

| US6315883B1 (en) * | 1998-10-26 | 2001-11-13 | Novellus Systems, Inc. | Electroplanarization of large and small damascene features using diffusion barriers and electropolishing |

| US6709565B2 (en) | 1998-10-26 | 2004-03-23 | Novellus Systems, Inc. | Method and apparatus for uniform electropolishing of damascene ic structures by selective agitation |

| US6413388B1 (en) | 2000-02-23 | 2002-07-02 | Nutool Inc. | Pad designs and structures for a versatile materials processing apparatus |

| US6395607B1 (en) * | 1999-06-09 | 2002-05-28 | Alliedsignal Inc. | Integrated circuit fabrication method for self-aligned copper diffusion barrier |

| JP2001044195A (ja) * | 1999-07-28 | 2001-02-16 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| US6234870B1 (en) | 1999-08-24 | 2001-05-22 | International Business Machines Corporation | Serial intelligent electro-chemical-mechanical wafer processor |

| JP4513145B2 (ja) * | 1999-09-07 | 2010-07-28 | ソニー株式会社 | 半導体装置の製造方法および研磨方法 |

| US6653226B1 (en) * | 2001-01-09 | 2003-11-25 | Novellus Systems, Inc. | Method for electrochemical planarization of metal surfaces |

| US6383917B1 (en) * | 1999-10-21 | 2002-05-07 | Intel Corporation | Method for making integrated circuits |

| JP2002158278A (ja) | 2000-11-20 | 2002-05-31 | Hitachi Ltd | 半導体装置およびその製造方法ならびに設計方法 |

| US6627550B2 (en) * | 2001-03-27 | 2003-09-30 | Micron Technology, Inc. | Post-planarization clean-up |

| US6852630B2 (en) | 2001-04-23 | 2005-02-08 | Asm Nutool, Inc. | Electroetching process and system |

-

2002

- 2002-03-27 US US10/108,614 patent/US6638863B2/en not_active Expired - Lifetime

- 2002-04-04 EP EP02764165A patent/EP1382065A4/en not_active Withdrawn

- 2002-04-04 CN CNB028088344A patent/CN100541746C/zh not_active Expired - Fee Related

- 2002-04-04 JP JP2002584381A patent/JP2004527126A/ja active Pending

- 2002-04-04 KR KR1020037013852A patent/KR101018187B1/ko not_active IP Right Cessation

- 2002-04-04 WO PCT/US2002/010500 patent/WO2002086961A1/en active Application Filing

- 2002-04-15 TW TW091107631A patent/TWI258814B/zh not_active IP Right Cessation

-

2003

- 2003-09-16 US US10/664,783 patent/US20040080053A1/en not_active Abandoned

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1264162A (zh) * | 1999-02-13 | 2000-08-23 | 国际商业机器公司 | 用于铝化学抛光的虚拟图形 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104637862A (zh) * | 2013-11-14 | 2015-05-20 | 盛美半导体设备(上海)有限公司 | 半导体结构形成方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20020175419A1 (en) | 2002-11-28 |

| CN1663036A (zh) | 2005-08-31 |

| EP1382065A1 (en) | 2004-01-21 |

| US20040080053A1 (en) | 2004-04-29 |

| EP1382065A4 (en) | 2009-04-15 |

| US6638863B2 (en) | 2003-10-28 |

| KR20030093327A (ko) | 2003-12-06 |

| JP2004527126A (ja) | 2004-09-02 |

| TWI258814B (en) | 2006-07-21 |

| WO2002086961A1 (en) | 2002-10-31 |

| KR101018187B1 (ko) | 2011-02-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100541746C (zh) | 电抛光具有带虚设结构的沟槽或者通路的晶片上的金属层 | |

| US7741698B2 (en) | Post last wiring level inductor using patterned plate process | |

| US6297554B1 (en) | Dual damascene interconnect structure with reduced parasitic capacitance | |

| KR100652243B1 (ko) | 반도체장치 및 그 제조방법 | |

| US9165883B2 (en) | Interconnection structure for an integrated circuit | |

| US6610596B1 (en) | Method of forming metal interconnection using plating and semiconductor device manufactured by the method | |

| US6239021B1 (en) | Dual barrier and conductor deposition in a dual damascene process for semiconductors | |

| CN101577247B (zh) | 把金属和超低k值电介质集成 | |

| CN101924094A (zh) | 半导体器件和制造半导体器件的方法 | |

| US7144761B2 (en) | Semiconductor device and method for fabricating the same | |

| US6465867B1 (en) | Amorphous and gradated barrier layer for integrated circuit interconnects | |

| US6403466B1 (en) | Post-CMP-Cu deposition and CMP to eliminate surface voids | |

| US6086777A (en) | Tantalum barrier metal removal by using CF4 /o2 plasma dry etch | |

| US6583051B2 (en) | Method of manufacturing an amorphized barrier layer for integrated circuit interconnects | |

| KR100818108B1 (ko) | 다마신 공정을 이용한 반도체 소자의 다층 금속배선형성방법 | |

| US6479898B1 (en) | Dielectric treatment in integrated circuit interconnects | |

| US6649511B1 (en) | Method of manufacturing a seed layer with annealed region for integrated circuit interconnects | |

| US6590288B1 (en) | Selective deposition in integrated circuit interconnects | |

| JP3924501B2 (ja) | 集積回路装置の製造方法 | |

| US6504251B1 (en) | Heat/cold amorphized barrier layer for integrated circuit interconnects | |

| US20070228572A1 (en) | Formation of an integrated circuit structure with reduced dishing in metallization levels |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20090916 Termination date: 20180404 |