WO2024225407A1 - 炭化珪素半導体装置 - Google Patents

炭化珪素半導体装置 Download PDFInfo

- Publication number

- WO2024225407A1 WO2024225407A1 PCT/JP2024/016352 JP2024016352W WO2024225407A1 WO 2024225407 A1 WO2024225407 A1 WO 2024225407A1 JP 2024016352 W JP2024016352 W JP 2024016352W WO 2024225407 A1 WO2024225407 A1 WO 2024225407A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- layer

- region

- cell region

- jfet

- gate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D12/00—Bipolar devices controlled by the field effect, e.g. insulated-gate bipolar transistors [IGBT]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/80—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials

- H10D62/81—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials of structures exhibiting quantum-confinement effects, e.g. single quantum wells; of structures having periodic or quasi-periodic potential variation

Definitions

- This disclosure relates to a silicon carbide (hereinafter also referred to as SiC) semiconductor device having a semiconductor element with a trench gate structure.

- SiC silicon carbide

- a gate insulating film is extended to the periphery of a cell region in which the MOSFET is formed, and a field oxide film is disposed thereon.

- the gate electrode of the MOSFET provided in the cell region is extended onto the gate insulating film and field insulating film disposed to the periphery of the cell region, and is connected to the gate wiring.

- thin insulating films such as a gate insulating film are easily destroyed by the flow of a displacement current during high-speed switching.

- the distance from the source contact in the cell region to the step portion that is the boundary between the gate insulating film and the field insulating film is set short to shorten the distance of the current path. This reduces the current path resistance, suppresses the destruction of the gate insulating film caused by the displacement current, and improves the switching resistance.

- An object of the present disclosure is to provide a SiC semiconductor device capable of improving switching withstand capability regardless of the location that determines the withstand capability.

- One aspect of the present disclosure is a SiC semiconductor device having a cell region in which a semiconductor element of a trench gate structure is formed, and an outer periphery surrounding the cell region, the outer periphery being provided with a peripheral voltage-withstanding structure portion constituting a peripheral voltage-withstanding structure and a connecting portion located between the peripheral voltage-withstanding structure portion and the cell region, the device having a substrate made of SiC of a first conductivity type or a second conductivity type, and a first impurity region of the first conductivity type formed on the surface of the substrate and having a lower impurity concentration than the substrate.

- the cell region is configured with a semiconductor element having a JFET layer made of SiC of a first conductivity type formed in a surface layer portion of the first impurity region and having a higher impurity concentration than the first impurity region, a deep layer made of SiC of a second conductivity type formed in the surface layer portion of the first impurity region and arranged alternately with the JFET layer in the surface direction of the substrate, a base layer made of SiC of the second conductivity type formed on the JFET layer and the deep layer, a gate insulating film formed on an inner wall surface of a plurality of gate trenches arranged deeper than the base layer and with one direction as the longitudinal direction, and a gate electrode formed on the gate insulating film in the gate trench, a second impurity region made of SiC of the first conductivity type formed in contact with the trench gate structure in the surface layer portion of the base layer and having a higher impurity concentration than the first impurity region, a first electrode electrically connected to the second impurity region

- the connecting portion includes a gate insulating film extending from the cell region and formed on the first impurity region, a gate electrode extending from the cell region and disposed on the gate insulating film, and a gate wiring connected to the gate electrode.

- the outer peripheral end position which is the end position on the outer peripheral side of the cell region in the JFET layer, is located closer to the cell region than the inner peripheral end position, which is the end position on the cell region side of the gate wiring.

- the electric field applied to the gate insulating film is likely to be large especially below the gate wiring, but the JFET layer is not formed in that area, and the outer periphery end position of the JFET layer is closer to the cell region than the inner periphery end position of the gate wiring.

- This structure reduces the impurity concentration of the p-type layer and n-type layer that make up the pn junction, making it possible to reduce the displacement current that occurs when the voltage suddenly increases during switching. This reduces the electric field concentration caused by the displacement current, suppresses breakdown of the gate insulating film, and improves the switching tolerance. This effect can be obtained regardless of the location where the tolerance is rate-determining. It is therefore possible to obtain a SiC semiconductor device that can improve the switching tolerance regardless of the location where the tolerance is rate-determining.

- the JFET layer is formed only on the cell region side of the cell region and the connecting portion.

- the JFET layer is formed on the cell region and on the cell region side of the connecting portion, but the JFET layer is not formed on the outside. Therefore, the pn junction in the outer edge side of the connecting portion is composed of a low concentration layer and a deep layer. This makes it possible to obtain the effect of the first aspect.

- the JFET layer is also formed in the junction, and the portion of the JFET layer that is outside the inner periphery end position, which is the end position on the cell region side of the gate wiring, has a first conductivity type impurity concentration equal to or lower than that of the first impurity region.

- the time change dV/dt becomes smaller and the displacement current can be reduced, improving the switching tolerance, making it possible to obtain a SiC semiconductor device in which the switching tolerance can be improved regardless of the rate-limiting location of the tolerance.

- FIG. 1 is a plan view of a SiC semiconductor device according to a first embodiment.

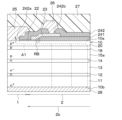

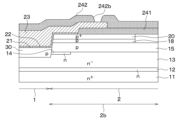

- FIG. 2 is a perspective cross-sectional view of an area RA in FIG. 1 as viewed from a direction II.

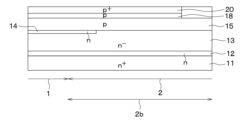

- FIG. 2 is a cross-sectional view taken along line III-III in FIG. 4 is a cross-sectional view taken along line IV-IV in FIG. 1.

- FIG. 11 is a cross-sectional view illustrating a displacement current generated in the outer circumferential region.

- 3A to 3C are cross-sectional views showing a manufacturing process of the SiC semiconductor device of the first embodiment.

- 6B is a cross-sectional view showing a manufacturing process following FIG. 6A.

- 6C is a cross-sectional view showing a manufacturing process following FIG. 6B.

- FIG. 6D is a cross-sectional view showing a manufacturing process following FIG. 6C.

- FIG. 6B is a cross-sectional view showing a manufacturing process following FIG. 6D.

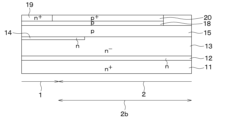

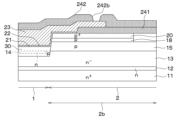

- FIG. 11 is a cross-sectional view of a SiC semiconductor device according to a second embodiment.

- 6A to 6C are cross-sectional views showing a manufacturing process of the SiC semiconductor device of the second embodiment.

- 8B is a cross-sectional view showing a manufacturing process following FIG. 8A.

- FIG. 8C is a cross-sectional view showing a manufacturing process following FIG. 8B.

- 8D is a cross-sectional view showing a manufacturing process following FIG. 8C.

- FIG. 8E is a cross-sectional view showing a manufacturing process following FIG. 8D.

- the SiC semiconductor device of the present embodiment has a cell region 1 which is an active region in which an element operates, and a peripheral region 2 which surrounds the cell region 1.

- various pads 3 are formed for controlling elements provided in the cell region 1 of the SiC semiconductor device, for temperature detection, etc.

- the peripheral region 2 has a guard ring portion 2a that corresponds to the peripheral voltage-resistant structure portion in which the peripheral voltage-resistant structure is configured, and a connecting portion 2b that is arranged inside the guard ring portion 2a.

- the peripheral region 2 has a guard ring portion 2a and a connecting portion 2b that is arranged between the cell region 1 and the guard ring portion 2a.

- a SiC semiconductor device having an n-channel vertical MOSFET as a semiconductor element with a trench gate structure in the cell region 1 will be described with reference to Figs. 2 to 4.

- one direction in the surface direction of the semiconductor substrate 10 described later is defined as the X-axis direction

- a direction intersecting with the one direction in the surface direction of the semiconductor substrate 10 is defined as the Y-axis direction

- a direction intersecting with the X-axis direction and the Y-axis direction is defined as the Z-axis direction.

- the X-axis direction, the Y-axis direction, and the Z direction are mutually orthogonal.

- the Z-axis direction corresponds to the thickness direction of the semiconductor substrate 10 described later, and also corresponds to the stacking direction of the substrate 11 and the low concentration layer 13 described later.

- the Y-axis direction is, for example, the ⁇ 11-20> direction.

- the SiC semiconductor device is constructed using a semiconductor substrate 10 on which a vertical MOSFET element is formed.

- the semiconductor substrate 10 is constructed by forming various semiconductor layers made of SiC on an n + type substrate 11 made of SiC.

- the substrate 11 has an off angle of 0 to 8° with respect to the (0001) Si surface, an n-type impurity concentration of nitrogen, phosphorus, etc. of 1.0 ⁇ 10 19 /cm 3 , and a thickness of about 300 ⁇ m.

- the substrate 11 constitutes a drain region.

- an n-type buffer layer 12 made of SiC is formed on the surface of the substrate 11.

- the buffer layer 12 is formed by epitaxial growth on the surface of the substrate 11.

- the buffer layer 12 has an n-type impurity concentration between that of the substrate 11 and the low concentration layer 13 described below, and has a thickness of about 1 ⁇ m.

- n - type low-concentration layer 13 made of SiC is formed on the surface of the buffer layer 12, and has an n-type impurity concentration of, for example, 5.0 ⁇ 10 15 to 2.0 ⁇ 10 16 /cm 3 and a thickness of about 7 to 15 ⁇ m.

- the low-concentration layer 13 may have a constant impurity concentration in the Z-axis direction, but it is preferable that the concentration distribution is inclined so that the low-concentration layer 13 is higher on the substrate 11 side than on the side away from the substrate 11.

- the low-concentration layer 13 corresponds to a first impurity region.

- the JFET layer 14 and the first deep layer 15 are formed in the surface portion of the low concentration layer 13 in the cell region 1.

- the JFET layer 14 and the first deep layer 15 each extend along the X-axis direction and have linear portions arranged alternately and repeatedly in the Y-axis direction.

- the JFET layer 14 and the first deep layer 15 are each formed in stripes extending along the X-axis direction in the normal direction (hereinafter simply referred to as the normal direction) to the surface of the substrate 11, and are arranged alternately along the Y-axis direction.

- the normal direction to the surface of the substrate 11 it can also be said that when viewed from the normal direction to the surface of the substrate 11.

- the normal direction to the surface of the substrate 11 is also the direction along the stacking direction of the drift layer 17 and the base layer 18 described later, and is the direction along the Z-axis direction.

- the JFET layer 14 is of n-type with a higher impurity concentration than the low concentration layer 13, and has a thickness of 0.3 to 1.5 ⁇ m.

- the JFET layer 14 has an n-type impurity concentration of about 5.0 ⁇ 10 16 to 1.0 ⁇ 10 17 /cm 3.

- the first deep layer 15 has a p-type impurity concentration of about 2.0 ⁇ 10 17 to 2.0 ⁇ 10 18 /cm 3 .

- the first deep layer 15 may be the same depth as the JFET layer 14, or may be deeper or shallower than the JFET layer 14.

- the first deep layer 15 is formed shallower than the JFET layer 14. That is, the first deep layer 15 is formed so that its bottom is located within the JFET layer 14. In other words, the first deep layer 15 is formed so that the JFET layer 14 is located between the first deep layer 15 and the low concentration layer 13. This suppresses the spread of the depletion layer into the JFET layer 14 between the first deep layers 15, thereby reducing the on-resistance.

- the JFET layer 14 and the first deep layer 15 are formed by appropriately ion-implanting impurities into the surface layer of the low concentration layer 13.

- a number of p-type guard rings 16 are provided as a peripheral voltage-resistant structure, surrounding the cell region 1.

- the top surface layout of the guard rings 16 is a square or a circle with rounded corners in the normal direction.

- a p-type connecting layer 15a is provided on the surface portion of the low concentration layer 13 in the connecting portion 2b of the peripheral region 2.

- the connecting layer 15a is disposed so that its inner edge side surrounds the cell region 1, and its outer edge side is disposed up to the boundary position with the guard ring portion 2a.

- the connecting layer 15a is formed by extending the first deep layer 15 up to the connecting portion 2b, and has the same depth and p-type impurity concentration as the first deep layer 15.

- a JFET layer 14 is formed in a portion of the connecting portion 2b in the outer peripheral region 2, specifically, on the cell region 1 side of the connecting portion 2b, but the JFET layer 14 is not formed on the outside of that. Therefore, in a position where the JFET layer 14 is formed deeper than the first deep layer 15, the JFET layer 14 exists below the cell region 1 side of the connecting layer 15a, but the JFET layer 14 does not exist on the outer edge side of the connecting portion 2b or on the guard ring portion 2a side.

- a base layer 18, a source region 19, a contact region 20, etc. are formed on the JFET layer 14 and the first deep layer 15 in the cell region 1.

- the base layer 18 is of p-type and is formed on the JFET layer 14 and the first deep layer 15. Therefore, the first deep layer 15 is connected to the base layer 18.

- the base layer 18 has, for example, a p-type impurity concentration of 5.0 ⁇ 10 16 to 2.0 ⁇ 10 19 /cm 3 and a thickness of about 2.0 ⁇ m.

- the source region 19 is n + type and is formed in the surface layer of the base layer 18.

- the contact region 20 is p + type and is formed in the surface layer of the base layer 18. Specifically, the source region 19 is formed so as to contact the side of a trench 21 described later, and the contact region 20 is formed on the opposite side of the source region 19 to the trench 21 described later.

- the source region 19 has an n-type impurity concentration in the surface layer, i.e., a surface concentration of, for example, 1.0 ⁇ 10 18 /cm 3 , and a thickness of about 0.3 ⁇ m.

- the contact region 20 has a p-type impurity concentration in the surface layer, i.e., a surface concentration of, for example, 1.0 ⁇ 10 21 /cm 3 , and a thickness of about 0.3 ⁇ m.

- the source region 19 corresponds to a second impurity region.

- the base layer 18, contact region 20, and surface portion of the low concentration layer 13 are formed on the low concentration layer 13, JFET layer 14, first deep layer 15, and connecting layer 15a in the connecting portion 2b of the outer peripheral region 2.

- the base layer 18 and contact region 20 are formed on the connecting layer 15a and extend from the cell region 1.

- the base layer 18 and contact region 20 are not formed, and the surface portion of the low concentration layer 13 is formed.

- the base layer 18 and contact region 20 in the outer peripheral region 2 are extended from the cell region 1 and formed halfway in the connecting portion 2b, and are not formed in the connecting portion 2b and guard ring portion 2a outside of that.

- the entire surface layer of the connecting portion 2b is made into the contact region 20, and outside of that, the entire surface layers of the connecting portion 2b and the guard ring portion 2a are made into the low concentration layer 13.

- the semiconductor substrate 10 is configured to include the substrate 11, buffer layer 12, low concentration layer 13, JFET layer 14, first deep layer 15, base layer 18, source region 19, contact region 20, etc. And since each layer that configures the semiconductor substrate 10 is configured from SiC, it can be said that the semiconductor substrate 10 is configured from SiC. Also, in this embodiment, on the inner edge side of the cell region 1 and the connecting portion 2b, one surface 10a of the semiconductor substrate 10 is configured from the source region 19, contact region 20, etc., and the other surface 10b of the semiconductor substrate 10 is configured from the substrate 11.

- the JFET layer 14, the first deep layer 15, the connecting layer 15a, the guard ring 16, the base layer 18, the source region 19, and the contact region 20 are composed of ion-implanted layers formed by ion implantation.

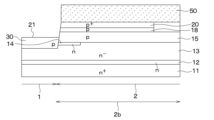

- a trench 21 is formed in the semiconductor substrate 10, penetrating the source region 19, base layer 18, etc., and reaching the JFET layer 14 and first deep layer 15 from the one surface 10a side.

- the trench 21 corresponds to a gate trench, has a depth such that its bottom surface is located within the JFET layer 14 and first deep layer 15, and has a width of, for example, 0.4 to 0.8 ⁇ m.

- the trenches 21 are formed so that multiple ones extend along the Y-axis direction, and are arranged at equal intervals of B1 in the X-axis direction to form a stripe shape, as shown in FIG. 3.

- the trenches 21 are formed so that their longitudinal direction is perpendicular to the longitudinal direction of the first deep layer 15.

- the second deep layer 30 is composed of a p-type layer with a lower impurity concentration than the first deep layer 15.

- the second deep layer 30 is formed along the longitudinal direction of the trench 21.

- the second deep layer 30 extends along the Y-axis direction intersecting with the first deep layer 15.

- the second deep layer 30 in this embodiment is formed so that its bottom surface reaches the low concentration layer 13, penetrating the JFET layer 14 and the first deep layer 15.

- the second deep layer 30 By forming the second deep layer 30 along the bottom surface of the trench 21, it is possible to suppress the penetration of the electric field into the gate insulating film 22 located at the bottom of the trench 21, and to suppress the breakdown of the oxide film. In addition, by forming the second deep layer 30 so as to be in contact with the bottom surface of the trench 21, it is possible to reduce the electrostatic capacitance between the gate electrode 23 and the lower electrode 28, i.e., the feedback capacitance, and to improve the switching speed. Furthermore, since the second deep layer 30 is formed so that the bottom surface thereof penetrates the JFET layer 14 and the first deep layer 15 and reaches the low concentration layer 13, the creeping up of the electric field to the JFET layer 14 disposed between the second deep layers 30 is suppressed, and the breakdown voltage can be improved. In addition, since breakdown is more likely to occur in the second deep layer 30 that protrudes downward when an overvoltage is applied, breakdown is more likely to occur in the cell region 1, and the avalanche resistance can be improved.

- the second deep layer 30 may be divided into multiple parts along the Y-axis direction. However, the second deep layer 30 is formed so as to be electrically connected to the base layer 18 via the first deep layer 15.

- a gate insulating film 22 is formed on the inner wall surface of the trench 21, and a gate electrode 23 made of doped Poly-Si or the like is formed on the gate insulating film 22.

- the gate insulating film 22 is formed by thermally oxidizing the inner wall surface of the trench 21, or by forming an insulating film by a CVD (short for chemical vapor deposition) method.

- the gate insulating film 22 has a thickness of about 100 nm on both the side and bottom sides of the trench 21.

- the gate insulating film 22 is formed on the inner wall surface of the trench 21 as well as on one surface 10a of the semiconductor substrate 10. In the cell region 1, a contact hole 22a is formed in the gate insulating film 22, exposing the source region 19 and the contact region 20.

- a field oxide film 241 is formed on one surface 10a of the semiconductor substrate 10 so as to surround the outer edge of the cell region 1, and an interlayer insulating film 242 is formed to cover the gate electrode 23, gate insulating film 22, field oxide film 241, etc.

- the interlayer insulating film 242 is made of BPSG (short for borophosphosilicate glass) or the like. Note that in FIG. 2, the field oxide film 241 and interlayer insulating film 242, etc. located above the one surface 10a of the semiconductor substrate 10 are omitted.

- the interlayer insulating film 242 has a contact hole 242a formed in the cell region 1, which communicates with the contact hole 22a and exposes the source region 19 and the contact region 20.

- the interlayer insulating film 242 has a contact hole 242b formed in the cell region 1, which exposes the portion of the gate electrode 23 that extends to the connecting portion 2b.

- An upper electrode 25 is formed on the interlayer insulating film 242, and is electrically connected to the source region 19 and the contact region 20 through the contact holes 22a and 242a.

- the upper electrode 25 is adapted to be electrically connected to the outside.

- the upper electrode 25 corresponds to the first electrode.

- a gate wiring 26 is formed on the interlayer insulating film 242, and is electrically connected to the gate electrode 23 through the contact hole 242b.

- the gate wiring 26 is formed along the outer edge of the cell region 1, and is formed, for example, along the right, left, and lower sides of the SiC semiconductor device that is a rectangular chip shown in FIG. 1.

- the JFET layer 14 is formed only on the cell region 1 side of the cell region 1 and the connecting portion 2b, but is not arranged below the gate wiring 26.

- the outer periphery termination position Po located on the outer periphery side of the cell region 1 of the JFET layer 14 shown in FIG. 4 is closer to the cell region 1 than the inner periphery termination position Pi located on the cell region 1 side of the gate wiring 26.

- a connecting layer 15a is formed or a low concentration layer 13 is arranged outside the inner periphery termination position Pi.

- the upper electrode 25 in this embodiment is composed of multiple metals, such as Ni/Al.

- the portion of the multiple metals that contacts the n-type SiC, i.e., the portion that constitutes the source region 19, is composed of a metal that can make ohmic contact with the n-type SiC.

- At least the portion of the multiple metals that contacts the p-type SiC, i.e., the contact region 20, is composed of a metal that can make ohmic contact with the p-type SiC.

- the gate wiring 26 may be composed in the same manner as the upper electrode 25, or may be composed of Al-Si, etc.

- a protective film 27 made of polyimide or the like is formed to cover the connecting portion 2b and the guard ring portion 2a.

- the protective film 27 is formed from the outer peripheral region 2 to the outer edge of the cell region 1 in order to suppress the occurrence of creeping discharge between the upper electrode 25 and a lower electrode 28 described below.

- the protective film 27 is formed in the cell region 1 so as to cover the portion of the upper electrode 25 on the outer peripheral region 2 side while exposing the portion of the upper electrode 25 on the inner edge side.

- a lower electrode 28 is formed on the other surface 10b of the semiconductor substrate 10, and is electrically connected to the substrate 11.

- the lower electrode 28 corresponds to the second electrode.

- this structure forms an n-channel inversion type trench gate MOSFET.

- n - type, n-type, and n + type correspond to the first conductivity type

- p-type and p + type correspond to the second conductivity type.

- the first deep layer 15 and the JFET layer 14 are provided at a position deeper than the trench 21. Therefore, the depletion layer formed between the first deep layer 15 and the JFET layer 14 suppresses the rise of the equipotential lines due to the influence of the drain voltage, making it difficult for a high electric field to penetrate the gate insulating film 22. Furthermore, since the second deep layer 30, which serves as an electric field relaxation layer, is provided at the bottom of the trench 21, it becomes even more difficult for a high electric field to penetrate the gate insulating film 22. Therefore, in this embodiment, it is possible to suppress the gate insulating film 22 from being destroyed.

- the JFET layer 14 is arranged only on the cell region 1 side of the cell region 1 and the connecting portion 2b, and is not arranged outside of that. This configuration improves the switching tolerance when the vertical MOSFET is turned on and off based on the application of a gate voltage. This switching tolerance is explained below.

- Figure 5 shows a comparative example in which the JFET layer 14 is formed not only in the cell region 1 but also in the connecting portion 2b, etc.

- Figure 5 shows the displacement current A1 at a cross section of the SiC semiconductor device cut along the Y direction, which is the longitudinal direction of the trench gate structure, between adjacent trench gate structures, i.e., at a position that is not a trench gate structure.

- a displacement current A1 flows as shown by the dashed arrow in FIG. 5. That is, in the peripheral region 2, it proceeds from the lower electrode 28 through the substrate 11, the low-concentration layer 13, and the JFET layer 14 to the bridging layer 15a. From there, it reaches the base layer 18 and the contact region 20, and the displacement current A1 flows to the upper electrode 25 while moving in the surface direction of the semiconductor substrate 10 within the contact region 20.

- the displacement current A1 at this time is proportional to the time change dV/dt of the high voltage generated during switching.

- the JFET layer 14 is formed in the bridging portion 2b as in the comparative example shown in FIG. 5, the pn junction is composed of the JFET layer 14 and the bridging layer 15a, and the impurity concentration becomes larger.

- the displacement current A1 becomes large and electric field concentration occurs, the thin gate insulating film 22 is destroyed and switching resistance cannot be obtained.

- dielectric breakdown occurs at the boundary position RB between the gate insulating film 22 and the field oxide film 241 shown in the figure.

- the JFET layer 14 is not provided at least on the outer edge side of the connecting portion 2b as in this embodiment, the pn junction in that portion is composed of the low concentration layer 13 and the first deep layer 15. Because of this structure, in this embodiment, the impurity concentrations of the p-type layer and n-type layer that make up the pn junction are lower than in the comparative example, and the displacement current A1 that occurs when the voltage suddenly increases during switching can be reduced. As a result, the electric field concentration caused by the displacement current A1 is mitigated, destruction of the gate insulating film 22 can be suppressed, and the switching tolerance can be improved.

- the electric field applied to the gate insulating film 22 is likely to be large below the gate wiring 26.

- Figures 6A to 6E show the manufacturing process corresponding to the cross section of the cell region 1 and the connecting portion 2b in Figure 4.

- a substrate 11 is prepared, and then a buffer layer 12 and a low-concentration layer 13 are epitaxially grown on one side of the substrate 11. Then, a mask (not shown) with an opening corresponding to the JFET layer 14 is placed on the surface of the low-concentration layer 13, and n-type impurities are ion-implanted to form the JFET layer 14.

- a mask (not shown) with an opening corresponding to the first deep layer 15 is formed again, and p-type impurities are ion-implanted to form the first deep layer 15 as shown in FIG. 6B.

- the JFET layer 14 is formed up to the portion that will become the first deep layer 15, but by increasing the dose of the p-type impurities, the first deep layer 15 can be formed by turning them back to p-type.

- a mask (not shown) with an opening corresponding to the base layer 18 is formed, and p-type impurities are ion-implanted to form the base layer 18.

- a mask with an opening corresponding to the contact region 20 is used to further ion-implant the p-type impurities to form the contact region 20 on the base layer 18.

- a mask (not shown) with an opening corresponding to the source region 19 is formed, and n-type impurities are ion-implanted to form the source region 19 as shown in FIG. 6C.

- the contact region 20 is formed up to the part that will become the source region 19, but by increasing the dose of the n-type impurity, it is possible to drive it back to n-type and form the source region 19.

- a mask 50 is placed with an opening corresponding to the trench 21, and then the trench 21 is formed by dry etching.

- the same mask 50 is also used to ion-implant p-type impurities to form a second deep layer 30 at the bottom of the trench 21.

- a gate insulating film 22 is formed by thermal oxidation or CVD, and then a gate electrode 23 is formed by depositing and patterning doped polysilicon. Furthermore, after performing the steps of forming a field oxide film 241 and an interlayer insulating film 242, contact holes 242a, 242b are formed in the interlayer insulating film 242. Thereafter, the steps of forming an upper electrode 25 and a gate wiring 26, a step of forming a protective film 27, and a step of forming a lower electrode 28 on the back side of the substrate 11 are performed using conventional steps. This completes the SiC semiconductor device according to this embodiment.

- the SiC semiconductor device thus formed has a structure in which the JFET layer 14 is formed on the cell region 1 side of the connecting portion 2b, but the JFET layer 14 is not formed on the outside of that.

- the JFET layer 14 is not disposed below the gate wiring 26 of the connecting portion 2b, but is disposed only on the cell region 1 side of the gate wiring 26.

- the JFET layer 14 is formed on the cell region 1 side of the connecting portion 2b, but the JFET layer 14 is not formed on the outside of the connecting portion 2b. Therefore, the pn junction of the outer edge side of the connecting portion 2b is composed of the low concentration layer 13 and the first deep layer 15. Because of this structure, the impurity concentration of the p-type layer and the n-type layer that constitute the pn junction is reduced, and the displacement current A1 generated when the voltage suddenly increases during switching can be reduced. Therefore, the electric field concentration caused by the displacement current A1 is alleviated, the destruction of the gate insulating film 22 can be suppressed, and the switching resistance can be improved.

- the electric field applied to the gate insulating film 22 is likely to be large below the gate wiring 26, but the JFET layer 14 is not formed in that area, and the outer periphery end position Po of the JFET layer 14 is closer to the cell region 1 than the inner periphery end position Pi of the gate wiring 26. This makes it possible to further suppress breakdown of the gate insulating film 22 and improve switching resistance.

- Patent Document 1 when the distance of the current path is shortened, the ends of structures such as source contacts, field oxide films, and trenches become crowded, making it difficult to manufacture each component with precision, which makes the manufacturing process unstable and reduces yields.

- the configuration of this embodiment can improve switching tolerance regardless of the distance of the current path, thereby suppressing decreases in yields.

- the switching tolerance can be improved by simply limiting the formation position of the JFET layer 14 to the cell region 1 side of the connecting portion 2b and the cell region 1 side, it is only necessary to change the mask for forming the JFET layer 14 from the conventional manufacturing method. This makes it possible to simplify the manufacturing process.

- Second Embodiment The second embodiment will be described. This embodiment is different from the first embodiment in that the range of formation of the JFET layer 14 is changed, and other aspects are the same as those of the first embodiment, so only the differences from the first embodiment will be described.

- the JFET layer 14 was formed on the cell region 1 and on the cell region 1 side of the connecting portion 2b, but in this embodiment, the JFET layer 14 is formed only on the cell region 1.

- the formation ranges of the ion implantation layers for forming the JFET layer 14 and the source region 19 were set separately.

- the formation ranges of the ion implantation layers for forming the JFET layer 14 and the source region 19 are aligned in the normal direction to the surface of the substrate 11.

- the JFET layer 14 is formed only in the cell region 1, and is not formed in the peripheral region 2 including the connecting portion 2b.

- the formation range of the ion implantation layer when forming the JFET layer 14 is set to be only in the cell region 1.

- the ion implantation range of the n-type impurity when forming the source region 19 is set to be the same as the formation range of the JFET layer 14.

- the formation range of the ion implantation layer for forming the JFET layer 14 means the entire range where n-type impurity ions are implanted when forming the JFET layer 14 as viewed from the normal direction of the substrate 11. This range also includes the part that becomes the p-type first deep layer 15 as a result of the return of p-type impurities.

- the formation range of the ion implantation layer for forming the source region 19 means the entire range where n-type impurity ions are implanted when forming the source region 19 as viewed from the normal direction of the substrate 11. This range also includes the part that becomes the p-type contact region 20 as a result of the return of p-type impurities.

- the formation range of the ion implantation layer is preferably the same, but it means that it is manufactured with the aim of having the same formation range, and it does not matter if there is a manufacturing error.

- the dashed line shown in FIG. 7 indicates the ion implantation range of n-type impurity ions when forming the source region 19.

- a buffer layer 12 and a low concentration layer 13 are formed on a substrate 11 in the same manner as in FIG. 6A, and then a JFET layer 14 is formed.

- a mask 51 having an opening corresponding to the JFET layer 14 is placed on the surface of the low concentration layer 13, and n-type impurities are ion-implanted to form the JFET layer 14, so that ion implantation is performed only in the cell region 1.

- the mask 51 used when forming the JFET layer 14 is used as is to ion-implant n-type impurities to form a source region 19. Note that the implantation depths of the JFET layer 14 and the source region 19 are made different by changing the ion implantation energy.

- the first deep layer 15, base layer 18, and contact region 20 are formed by performing a process similar to that shown in FIG. 6C.

- the source region 19 is formed up to the portion that will become the contact region 20, but by increasing the dose of the p-type impurity, it is possible to drive it back to p-type and form the contact region 20.

- FIG. 8D a process similar to that of FIG. 6D is performed to form a trench 21, and then a second deep layer 30 is formed.

- FIG. 8E a process similar to that of FIG. 6E is performed to form a gate insulating film 22, a gate electrode 23, a field oxide film 241 and an interlayer insulating film 242, and contact holes 242a and 242b in the interlayer insulating film 242.

- the processes of forming an upper electrode 25 and a gate wiring 26, a protective film 27, and a lower electrode 28 on the back surface of the substrate 11 are performed. This completes the SiC semiconductor device according to this embodiment.

- the formation ranges of the ion implantation layers for forming the JFET layer 14 and the source region 19 are aligned. This allows the ion implantation masks for the JFET layer 14 and the source region 19 to be shared, simplifying the manufacturing process and reducing manufacturing costs.

- the connecting portion 2b is structured to include the base layer 18 and the contact region 20 in the surface layer of the low concentration layer 13, but one or both of these may not be included in the connecting portion 2b.

- the base layer 18 can also be formed using the ion implantation mask for the JFET layer 14 and the source region 19 as in the second embodiment. In this way, the ion implantation mask for the base layer 18 can be shared in addition to the JFET layer 14 and the source region 19, which further simplifies the manufacturing process and reduces manufacturing costs.

- the outer peripheral end position Po of the JFET layer 14 of the connecting portion 2b is located closer to the cell region 1 than the inner peripheral end position Pi of the gate wiring 26, and the outside of that is either a connecting layer 15a or a low concentration layer 13.

- the JFET layer 14 is not formed outside the inner peripheral end position Pi of the gate wiring 26.

- the JFET layer 14 may be formed outside the inner peripheral end position Pi of the gate wiring 26, while the n-type impurity concentration of that portion is set to be equal to or lower than the low concentration layer 13.

- the impurity concentration of the p-type layer and n-type layer that constitute the pn junction in the outer peripheral region 2 is lowered, and the source-drain capacitance can be reduced. Therefore, the same effect as in the first embodiment can be obtained.

- the bottom surface of the second deep layer 30 may be shallow and located within the JFET layer 14 and the first deep layer 15.

- the second deep layer 30 may be formed so as not to reach the low concentration layer 13. This makes it difficult for the depletion layer to extend from the second deep layer 30, thereby reducing the on-resistance.

- the JFET layer 14, the first deep layer 15, the base layer 18, the contact region 20, and the source region 19 are formed by ion implantation. Some or all of these may be composed of epitaxial layers formed by epitaxial growth.

- the base layer 18 is formed on the surfaces of the JFET layer 14 and the first deep layer 15, but an n-type current spreading layer having a higher n-type impurity concentration than the low concentration layer 13 may be formed between them.

- p-type connection layers may be formed on both sides of the trench 21, and the base layer 18 may be formed on these current spreading layers and connection layers.

- the first deep layer 15 and the base layer 18 are connected through the connection layers.

- the low concentration layer 13, the JFET layer 14, and the current spreading layer are connected, and the drift layer 17 is formed by these.

- the second deep layer 30 may be formed deeper than the first deep layer 15, or may be formed to a depth within the thickness of the first deep layer 15.

- a vertical MOSFET with an n-channel type trench gate structure in which the first conductivity type is n-type and the second conductivity type is p-type is given as an example of the semiconductor element provided in the cell region 1.

- this is merely one example, and it may be a vertical MOSFET with a p-channel type trench gate structure in which the conductivity types of each component are inverted from the n-channel type.

- a vertical IGBT with a similar structure may be used instead of a vertical MOSFET. In the case of an IGBT, it is the same as the vertical MOSFET described in the above embodiment, except that the conductivity type of the substrate 11 in each of the above embodiments is changed from n-type to p-type.

- a bar (-) When indicating the crystal orientation, a bar (-) should normally be placed above the desired number, but due to limitations on expression based on electronic filing, a bar has been placed before the desired number in this specification.

Landscapes

- Junction Field-Effect Transistors (AREA)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202480026118.3A CN121003031A (zh) | 2023-04-26 | 2024-04-25 | 碳化硅半导体装置 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2023-072621 | 2023-04-26 | ||

| JP2023072621A JP2024157941A (ja) | 2023-04-26 | 2023-04-26 | 炭化珪素半導体装置 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| WO2024225407A1 true WO2024225407A1 (ja) | 2024-10-31 |

Family

ID=93256764

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| PCT/JP2024/016352 Pending WO2024225407A1 (ja) | 2023-04-26 | 2024-04-25 | 炭化珪素半導体装置 |

Country Status (3)

| Country | Link |

|---|---|

| JP (1) | JP2024157941A (enExample) |

| CN (1) | CN121003031A (enExample) |

| WO (1) | WO2024225407A1 (enExample) |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2019159657A1 (ja) * | 2018-02-14 | 2019-08-22 | 富士電機株式会社 | 半導体装置 |

| JP2022044997A (ja) * | 2020-09-08 | 2022-03-18 | 富士電機株式会社 | 半導体装置および半導体装置の製造方法 |

| JP2022154849A (ja) * | 2021-03-30 | 2022-10-13 | 富士電機株式会社 | 半導体装置 |

| JP2022175975A (ja) * | 2021-05-14 | 2022-11-25 | 株式会社デンソー | 炭化珪素半導体装置 |

| JP2022180233A (ja) * | 2021-05-24 | 2022-12-06 | 富士電機株式会社 | 炭化珪素半導体装置 |

-

2023

- 2023-04-26 JP JP2023072621A patent/JP2024157941A/ja active Pending

-

2024

- 2024-04-25 CN CN202480026118.3A patent/CN121003031A/zh active Pending

- 2024-04-25 WO PCT/JP2024/016352 patent/WO2024225407A1/ja active Pending

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2019159657A1 (ja) * | 2018-02-14 | 2019-08-22 | 富士電機株式会社 | 半導体装置 |

| JP2022044997A (ja) * | 2020-09-08 | 2022-03-18 | 富士電機株式会社 | 半導体装置および半導体装置の製造方法 |

| JP2022154849A (ja) * | 2021-03-30 | 2022-10-13 | 富士電機株式会社 | 半導体装置 |

| JP2022175975A (ja) * | 2021-05-14 | 2022-11-25 | 株式会社デンソー | 炭化珪素半導体装置 |

| JP2022180233A (ja) * | 2021-05-24 | 2022-12-06 | 富士電機株式会社 | 炭化珪素半導体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2024157941A (ja) | 2024-11-08 |

| CN121003031A (zh) | 2025-11-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7808003B2 (en) | Silicon carbide semiconductor device | |

| CN101401212B (zh) | 绝缘栅极型半导体器件及其制造方法 | |

| CN104054179B (zh) | 半导体装置 | |

| US10243067B2 (en) | Semiconductor device and method for manufacturing the same | |

| CN107180855B (zh) | 半导体装置 | |

| US11469318B2 (en) | Superjunction semiconductor device having parallel PN structure with column structure and method of manufacturing the same | |

| US10256229B2 (en) | Semiconductor device and manufacturing method | |

| JP7593225B2 (ja) | 炭化珪素半導体装置 | |

| WO2014163060A1 (ja) | 半導体装置 | |

| WO2010110246A1 (ja) | 半導体装置 | |

| CN113707707B (zh) | 功率半导体器件及其制造方法 | |

| US11101345B2 (en) | Semiconductor device | |

| US12205983B2 (en) | Semiconductor device and manufacturing method of semiconductor device | |

| CN107833920B (zh) | 半导体装置 | |

| JP7526010B2 (ja) | 半導体装置 | |

| JP2017037964A (ja) | 半導体装置 | |

| CN117099213A (zh) | 半导体装置及其制造方法 | |

| US10707301B2 (en) | Semiconductor device and method of manufacturing semiconductor device | |

| WO2023112547A1 (ja) | 半導体装置 | |

| CN115954360A (zh) | 半导体装置及其制造方法 | |

| JP7704007B2 (ja) | 半導体装置の製造方法 | |

| JP3914852B2 (ja) | ダイオード素子とトランジスタ素子 | |

| WO2022138743A1 (ja) | 炭化珪素半導体装置 | |

| WO2024225407A1 (ja) | 炭化珪素半導体装置 | |

| CN117581382A (zh) | 半导体装置和半导体装置的制造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| 121 | Ep: the epo has been informed by wipo that ep was designated in this application |

Ref document number: 24797152 Country of ref document: EP Kind code of ref document: A1 |