WO2022013676A1 - 半導体装置、及び電子機器 - Google Patents

半導体装置、及び電子機器 Download PDFInfo

- Publication number

- WO2022013676A1 WO2022013676A1 PCT/IB2021/055988 IB2021055988W WO2022013676A1 WO 2022013676 A1 WO2022013676 A1 WO 2022013676A1 IB 2021055988 W IB2021055988 W IB 2021055988W WO 2022013676 A1 WO2022013676 A1 WO 2022013676A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- circuit

- transistor

- wiring

- terminal

- switch

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Ceased

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D88/00—Three-dimensional [3D] integrated devices

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/06—Physical realisation, i.e. hardware implementation of neural networks, neurons or parts of neurons

- G06N3/063—Physical realisation, i.e. hardware implementation of neural networks, neurons or parts of neurons using electronic means

- G06N3/065—Analogue means

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5642—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06G—ANALOGUE COMPUTERS

- G06G7/00—Devices in which the computing operation is performed by varying electric or magnetic quantities

- G06G7/48—Analogue computers for specific processes, systems or devices, e.g. simulators

- G06G7/60—Analogue computers for specific processes, systems or devices, e.g. simulators for living beings, e.g. their nervous systems ; for problems in the medical field

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/04—Architecture, e.g. interconnection topology

- G06N3/0464—Convolutional networks [CNN, ConvNet]

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/04—Architecture, e.g. interconnection topology

- G06N3/048—Activation functions

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/54—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using elements simulating biological cells, e.g. neuron

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0408—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors

- G11C16/0441—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors comprising cells containing multiple floating gate devices, e.g. separate read-and-write FAMOS transistors with connected floating gates

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/06—Sense amplifiers; Associated circuits, e.g. timing or triggering circuits

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B20/00—Read-only memory [ROM] devices

- H10B20/20—Programmable ROM [PROM] devices comprising field-effect components

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/02—Manufacture or treatment characterised by using material-based technologies

- H10D84/03—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology

- H10D84/038—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology using silicon technology, e.g. SiGe

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/80—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs

- H10D84/811—Combinations of field-effect devices and one or more diodes, capacitors or resistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/80—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs

- H10D84/82—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs of only field-effect components

- H10D84/83—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs of only field-effect components of only insulated-gate FETs [IGFET]

- H10D84/85—Complementary IGFETs, e.g. CMOS

- H10D84/856—Complementary IGFETs, e.g. CMOS the complementary IGFETs having different architectures than each other, e.g. high-voltage and low-voltage CMOS

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D88/00—Three-dimensional [3D] integrated devices

- H10D88/01—Manufacture or treatment

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/403—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells with charge regeneration common to a multiplicity of memory cells, i.e. external refresh

- G11C11/404—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells with charge regeneration common to a multiplicity of memory cells, i.e. external refresh with one charge-transfer gate, e.g. MOS transistor, per cell

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/403—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells with charge regeneration common to a multiplicity of memory cells, i.e. external refresh

- G11C11/405—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells with charge regeneration common to a multiplicity of memory cells, i.e. external refresh with three charge-transfer gates, e.g. MOS transistors, per cell

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/4076—Timing circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/41—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming static cells with positive feedback, i.e. cells not needing refreshing or charge regeneration, e.g. bistable multivibrator or Schmitt trigger

- G11C11/413—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing, timing or power reduction

- G11C11/417—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing, timing or power reduction for memory cells of the field-effect type

- G11C11/419—Read-write [R-W] circuits

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/08—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using semiconductor devices

- H03K19/0806—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using semiconductor devices using charge transfer devices (DTC, CCD)

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/033—Making the capacitor or connections thereto the capacitor extending over the transistor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/05—Making the transistor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6729—Thin-film transistors [TFT] characterised by the electrodes

- H10D30/673—Thin-film transistors [TFT] characterised by the electrodes characterised by the shapes, relative sizes or dispositions of the gate electrodes

- H10D30/6733—Multi-gate TFTs

- H10D30/6734—Multi-gate TFTs having gate electrodes arranged on both top and bottom sides of the channel, e.g. dual-gate TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6755—Oxide semiconductors, e.g. zinc oxide, copper aluminium oxide or cadmium stannate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6757—Thin-film transistors [TFT] characterised by the structure of the channel, e.g. transverse or longitudinal shape or doping profile

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/421—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer

- H10D86/423—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer comprising semiconductor materials not belonging to the Group IV, e.g. InGaZnO

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

Definitions

- One aspect of the present invention relates to a semiconductor device and an electronic device.

- one aspect of the present invention is not limited to the above technical fields.

- the technical field of the invention disclosed in the present specification and the like relates to a product, a driving method, or a manufacturing method.

- one aspect of the invention relates to a process, machine, manufacture, or composition (composition of matter). Therefore, more specifically, the technical fields of one aspect of the present invention disclosed in the present specification include semiconductor devices, display devices, liquid crystal display devices, light emitting devices, power storage devices, image pickup devices, storage devices, signal processing devices, and processors. , Electronic devices, systems, their driving methods, their manufacturing methods, or their inspection methods.

- the mechanism of the brain is incorporated as an electronic circuit, and it has a circuit corresponding to "neurons” and "synapses" of the human brain. Therefore, such integrated circuits are sometimes called “neuromorphic”, “brainmorphic”, “brain-inspired” and the like.

- the integrated circuit has a non-von Neumann architecture, and is expected to be able to perform parallel processing with extremely low power consumption as compared with the von Neumann architecture in which the power consumption increases as the processing speed increases.

- Non-Patent Document 1 and Non-Patent Document 2 disclose an arithmetic unit in which an artificial neural network is configured by using SRAM (Static Random Access Memory).

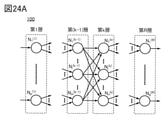

- a calculation is performed by multiplying the synaptic connection strength (sometimes called a weighting factor) that connects two neurons with the signal transmitted between the two neurons.

- the connection strength of each synapse between the plurality of first neurons in the first layer and one of the second neurons in the second layer, and the plurality of first neurons in the first layer. It is necessary to multiply and add each signal input to one of the second neurons of the second layer from, that is, to perform a product-sum calculation of the connection strength and the signal.

- the number of the coupling strengths and the number of parameters indicating the signals used in the product-sum calculation are determined according to the scale of the artificial neural network.

- the second neuron performs an operation by the activation function using the result of the product-sum calculation of the synaptic connection strength and the signal output by the first neuron, and uses the calculation result as a signal in the third layer.

- the circuit constituting the chip has circuit elements that are not easily affected by temperature. Moreover, if the characteristics of the transistor, current source, etc. contained in the chip vary, the calculation result also varies.

- the multiplication cell is provided with a storage element such as a capacity for holding the weighting coefficient, but the data held in the storage element may deteriorate with the passage of time and the value of the weighting coefficient may change. Data degradation is caused by a decrease in the charge held in the storage element.

- the cause of the decrease in electric charge is, for example, the leak current flowing from the storage element, and the types of the leak current are, for example, the leak current flowing in the off state in a switching element such as a transistor, and between a pair of electrodes in a capacitive element.

- the leak current flowing in the off state in a switching element such as a transistor, and between a pair of electrodes in a capacitive element.

- the influence of the leak current can be reduced by increasing the capacitance value of the capacitive element.

- the arithmetic circuit including the multiplication cell needs measures other than increasing the capacitance value of the capacitance element.

- the countermeasure it is possible to periodically rewrite the weighting coefficient to the storage element of the multiplication cell.

- the rewriting of data means the operation of rewriting the same data as the data originally held in the cell.

- rewriting data is also an operation of replenishing the cell whose absolute value of the retained charge amount has become smaller with the same amount of charge originally retained in order to restore the data. It shall point.

- One aspect of the present invention is to provide a semiconductor device or the like that performs product-sum calculation and / or function calculation.

- one aspect of the present invention is to provide a semiconductor device for rewriting the data held in the multiplication cell.

- one aspect of the present invention is to provide a semiconductor device that holds a digital value, performs digital-to-analog conversion on the digital value, and performs an operation based on the analog value.

- one aspect of the present invention is to provide a semiconductor device or the like that performs convolution processing such as CNN (Convolutional Neural Network).

- one aspect of the present invention is to provide a semiconductor device for AI (Artificial Integrity) or the like.

- one aspect of the present invention is to provide a semiconductor device or the like for a DNN (Deep Neural Network).

- DNN Deep Neural Network

- one aspect of the present invention is to provide a semiconductor device or the like having low power consumption.

- one aspect of the present invention is to provide a semiconductor device or the like that is not easily affected by the temperature of the environment.

- one aspect of the present invention is to provide a semiconductor device or the like that is not easily affected by variations in transistor characteristics.

- one aspect of the present invention is to provide a semiconductor device or the like that is not easily affected by variations in the characteristics of a current source.

- one aspect of the present invention is to provide a new semiconductor device or the like.

- the problem of one aspect of the present invention is not limited to the problems listed above.

- the issues listed above do not preclude the existence of other issues.

- Other issues are issues not mentioned in this item, which are described below. Issues not mentioned in this item can be derived from the description of the description, drawings, etc. by those skilled in the art, and can be appropriately extracted from these descriptions.

- one aspect of the present invention solves at least one of the above-listed problems and other problems. It should be noted that one aspect of the present invention does not need to solve all of the above-listed problems and other problems.

- One aspect of the present invention is a semiconductor device including a first circuit, a second circuit, and a third circuit.

- the first circuit has a current source and a first switch

- the second circuit has a first transistor, a third transistor, a fourth transistor, and a first capacitance, and a third circuit.

- the first terminal of the first transistor is electrically connected to the control terminal of the first switch

- the second terminal of the first transistor is electrically connected to the first terminal of the fourth transistor

- the second terminal of the fourth transistor is connected.

- the 2 terminals are electrically connected to the 1st terminal of the 1st capacitance, and the gate of the 4th transistor is electrically connected to the 2nd terminal of the 1st capacitance and the 1st terminal of the 3rd transistor.

- the first terminal of the switch is electrically connected to the output terminal of the current source, and the second terminal of the first switch is electrically connected to the first terminal of the second transistor.

- one aspect of the present invention may be configured to have a fourth circuit including a latch circuit in the above (1). Further, in the electrical connection between the first terminal of the first transistor and the control terminal of the first switch, the first terminal of the fourth circuit is electrically connected to the first terminal of the first transistor, and the first terminal of the fourth circuit is electrically connected. It is assumed that the second terminal is electrically connected to the control terminal of the first switch.

- one aspect of the present invention is a semiconductor device including a first circuit, a second circuit, a third circuit, and a sense amplifier.

- the first circuit has a current source and a first switch

- the second circuit has a first transistor and a first capacitance

- the third circuit has a second transistor.

- the first terminal of the first transistor is electrically connected to the control terminal of the first switch via a sense amplifier

- the second terminal of the first transistor is electrically connected to the first terminal of the first capacitance.

- the first terminal of the first switch is electrically connected to the output terminal of the current source

- the second terminal of the first switch is electrically connected to the first terminal of the second transistor.

- one aspect of the present invention may be a configuration in which the gate of the first transistor is electrically connected to the gate of the second transistor in any one of the above (1) to (3).

- one aspect of the present invention is a semiconductor device having a first circuit, a second circuit, and a third circuit.

- the first circuit has a current source and a first switch

- the second circuit has a first transistor, a third transistor, and a first capacitance

- the third circuit has a second transistor.

- the first terminal of the first transistor is electrically connected to the control terminal of the first switch

- the first terminal of the third transistor is electrically connected to the first terminal of the first capacitance and the gate of the first transistor.

- the first terminal of the first switch is electrically connected to the output terminal of the current source

- the second terminal of the first switch is electrically connected to the first terminal of the second transistor.

- one aspect of the present invention may be configured to include a fourth circuit including a latch circuit. Further, in the electrical connection between the first terminal of the first transistor and the control terminal of the first switch, the first terminal of the fourth circuit is electrically connected to the first terminal of the first transistor, and the first terminal of the fourth circuit is electrically connected. It is assumed that the second terminal is electrically connected to the control terminal of the first switch.

- one aspect of the present invention may be configured in the above (5) or (6) in which the second terminal of the first capacitance is electrically connected to the gate of the second transistor.

- the transistor included in the second circuit may have a metal oxide in the channel forming region.

- one aspect of the present invention is a semiconductor device having a first circuit and a fifth circuit.

- the first circuit has a first current source, a second current source, a first switch, a fifth transistor, and a sixth transistor

- the fifth circuit has a seventh transistor and an eighth transistor.

- the output terminal of the first current source is electrically connected to the first terminal of the first switch

- the output terminal of the second current source is the gate of the fifth transistor, the gate of the sixth transistor, and the sixth transistor. It is preferably electrically connected to the first terminal.

- the first terminal of the seventh transistor is electrically connected to the first terminal of the eighth transistor, the first terminal of the second switch, and the first terminal of the third switch, and is the gate of the seventh transistor. Is preferably electrically connected to the second terminal of the eighth transistor and the first terminal of the second capacitance.

- the second terminal of the first switch is electrically connected to the second terminal of the second switch, and the first terminal of the current comparison circuit is electrically connected to the second terminal of the third switch for current comparison.

- the second terminal of the circuit is preferably electrically connected to the first terminal of the fifth transistor.

- one aspect of the present invention is a semiconductor device having a first circuit and a fifth circuit, which is different from the above (9).

- the first circuit has a first current source, a third current source, a first switch, and a fourth switch

- the fifth circuit has a seventh transistor, an eighth transistor, and a second capacitance.

- a second switch, a third switch, a fifth switch, and a current comparison circuit It is preferable that the output terminal of the first current source is electrically connected to the first terminal of the first switch, and the input terminal of the third current source is electrically connected to the first terminal of the fourth switch. ..

- the first terminal of the seventh transistor is electrically connected to the first terminal of the eighth transistor, the first terminal of the second switch, and the first terminal of the third switch, and is the gate of the seventh transistor. Is preferably electrically connected to the second terminal of the eighth transistor and the first terminal of the second capacitance. It is preferable that the second terminal of the first switch is electrically connected to the second terminal of the second switch, and the second terminal of the fourth switch is electrically connected to the first terminal of the fifth switch. .. It is preferable that the first terminal of the current comparison circuit is electrically connected to the second terminal of the third switch, and the second terminal of the current comparison circuit is electrically connected to the second terminal of the fifth switch. ..

- the seventh transistor has silicon in the channel forming region, and the eighth transistor has a metal oxide in the channel forming region. May be good.

- the fifth circuit may have a configuration including a ninth transistor, a tenth transistor, a third capacitance, and a sixth switch.

- the first terminal of the ninth transistor is electrically connected to the first terminal of the tenth transistor, the first terminal of the second switch, and the first terminal of the sixth switch, and the gate of the ninth transistor is It is preferable that the second terminal of the tenth transistor and the first terminal of the third capacitance are electrically connected to each other. Further, it is preferable that the second terminal of the sixth switch is electrically connected to the first terminal of the fifth switch and the second terminal of the fourth switch. It is preferable that the gate of the 8th transistor and the gate of the 10th transistor are not directly connected.

- each of the 7th transistor and the 9th transistor has silicon in the channel forming region

- each of the 8th transistor and the 10th transistor has silicon in the channel forming region. It may be configured to have a metal oxide.

- one aspect of the present invention is an electronic device having the semiconductor device according to any one of (1) to (13) above and a housing.

- the semiconductor device is a device that utilizes semiconductor characteristics, and refers to a circuit including a semiconductor element (transistor, diode, photodiode, etc.), a device having the same circuit, and the like. It also refers to all devices that can function by utilizing semiconductor characteristics.

- a semiconductor element transistor, diode, photodiode, etc.

- the storage device, the display device, the light emitting device, the lighting device, the electronic device, and the like may be a semiconductor device itself, and may have a semiconductor device.

- an element for example, a switch, a transistor, a capacitive element, an inductor, a resistance element, a diode, a display

- One or more devices, light emitting devices, loads, etc. can be connected between X and Y.

- the switch has a function of controlling on / off. That is, the switch is in a conducting state (on state) or a non-conducting state (off state), and has a function of controlling whether or not a current flows.

- a circuit that enables functional connection between X and Y for example, a logic circuit (inverter, NAND circuit, NOR circuit, etc.), signal conversion) Circuits (digital-analog conversion circuit, analog-to-digital conversion circuit, gamma correction circuit, etc.), potential level conversion circuit (power supply circuit (boost circuit, step-down circuit, etc.), level shifter circuit that changes the potential level of the signal, etc.), voltage source, current source , Switching circuit, amplifier circuit (circuit that can increase signal amplitude or current amount, operational amplifier, differential amplifier circuit, source follower circuit, buffer circuit, etc.), signal generation circuit, storage circuit, control circuit, etc.) It is possible to connect one or more to and from. As an example, even if another circuit is sandwiched between X and Y, if the signal output from X is transmitted to Y, it is assumed that X and Y are functionally connected. do.

- X and Y are electrically connected, it means that X and Y are electrically connected (that is, another element between X and Y). Or when they are connected by sandwiching another circuit) and when X and Y are directly connected (that is, they are connected without sandwiching another element or another circuit between X and Y). If there is) and.

- X and Y, the source (or the first terminal, etc.) and the drain (or the second terminal, etc.) of the transistor are electrically connected to each other, and the X, the source (or the second terminal, etc.) of the transistor are connected to each other. (1 terminal, etc.), the drain of the transistor (or the 2nd terminal, etc.), and Y are electrically connected in this order.

- the source of the transistor (or the first terminal, etc.) is electrically connected to X

- the drain of the transistor (or the second terminal, etc.) is electrically connected to Y

- the first terminal, etc.), the drain of the transistor (or the second terminal, etc.), and Y are electrically connected in this order.

- X is electrically connected to Y via the source (or first terminal, etc.) and drain (or second terminal, etc.) of the transistor, and X, the source (or first terminal, etc.) of the transistor.

- the terminals, etc.), the drain of the transistor (or the second terminal, etc.), and Y are provided in this connection order.

- the source (or first terminal, etc.) and drain (or second terminal, etc.) of the transistor can be separated. Separately, the technical scope can be determined. It should be noted that these expression methods are examples, and are not limited to these expression methods.

- X and Y are objects (for example, devices, elements, circuits, wirings, electrodes, terminals, conductive films, layers, etc.).

- the circuit diagram shows that the independent components are electrically connected to each other, the case where one component has the functions of a plurality of components together.

- one conductive film has both the function of the wiring and the function of the component of the function of the electrode. Therefore, the electrical connection in the present specification also includes the case where one conductive film has the functions of a plurality of components in combination.

- the “resistance element” may be, for example, a circuit element having a resistance value higher than 0 ⁇ , wiring higher than 0 ⁇ , or the like. Therefore, in the present specification and the like, the “resistance element” includes wiring having a resistance value, a transistor in which a current flows between a source and a drain, a diode, a coil, and the like. Therefore, the term “resistance element” may be paraphrased into terms such as “resistance”, “load”, and “region having a resistance value”. On the contrary, the terms “resistance”, “load”, and “region having a resistance value” may be paraphrased into terms such as “resistance element”.

- the resistance value can be, for example, preferably 1 m ⁇ or more and 10 ⁇ or less, more preferably 5 m ⁇ or more and 5 ⁇ or less, and further preferably 10 m ⁇ or more and 1 ⁇ or less. Further, for example, it may be 1 ⁇ or more and 1 ⁇ 10 9 ⁇ or less.

- the “capacitance element” means, for example, a circuit element having a capacitance value higher than 0F, a wiring region having a capacitance value higher than 0F, a parasitic capacitance, and a transistor. It can be the gate capacitance of. Therefore, in the present specification and the like, the “capacitive element” includes a pair of electrodes and a circuit element including a dielectric contained between the electrodes. In addition, terms such as “capacitive element”, “parasitic capacitance”, and “gate capacitance” may be paraphrased into terms such as "capacity”.

- the term “capacity” may be paraphrased into terms such as “capacitive element”, “parasitic capacitance”, and “gate capacitance”.

- the term “pair of electrodes” of “capacity” can be paraphrased as “pair of conductors", “pair of conductive regions", “pair of regions” and the like.

- the value of the capacitance can be, for example, 0.05 fF or more and 10 pF or less. Further, for example, it may be 1 pF or more and 10 ⁇ F or less.

- the transistor has three terminals called a gate, a source, and a drain.

- the gate is a control terminal that controls the conduction state of the transistor.

- the two terminals that function as sources or drains are the input and output terminals of the transistor.

- One of the two input / output terminals becomes a source and the other becomes a drain depending on the high and low potentials given to the conductive type (n-channel type and p-channel type) of the transistor and the three terminals of the transistor. Therefore, in the present specification and the like, the terms source and drain may be paraphrased with each other.

- the transistor when explaining the connection relationship of transistors, "one of the source or drain” (or the first electrode or the first terminal), “the other of the source or drain” (or the second electrode, or the second electrode, or The notation (second terminal) is used.

- it may have a back gate in addition to the above-mentioned three terminals.

- one of the gate or the back gate of the transistor may be referred to as a first gate

- the other of the gate or the back gate of the transistor may be referred to as a second gate.

- the terms “gate” and “backgate” may be interchangeable.

- the respective gates When the transistor has three or more gates, the respective gates may be referred to as a first gate, a second gate, a third gate, and the like in the present specification and the like.

- a transistor having a multi-gate structure having two or more gate electrodes can be used as an example of a transistor.

- the multi-gate structure since the channel formation regions are connected in series, a structure in which a plurality of transistors are connected in series is obtained. Therefore, the multi-gate structure can reduce the off-current and improve the withstand voltage of the transistor (improve the reliability).

- the multi-gate structure even if the voltage between the drain and the source changes when operating in the saturation region, the current between the drain and the source does not change much, and the slope is flat. The characteristics can be obtained. By utilizing the voltage / current characteristics with a flat slope, it is possible to realize an ideal current source circuit or an active load having a very high resistance value. As a result, it is possible to realize a differential circuit or a current mirror circuit having good characteristics.

- the circuit element may have a plurality of circuit elements.

- one resistance is described on the circuit diagram, it includes the case where two or more resistances are electrically connected in series.

- one capacity is described on the circuit diagram, it includes a case where two or more capacities are electrically connected in parallel.

- one transistor is described on the circuit diagram, two or more transistors are electrically connected in series, and the gates of the respective transistors are electrically connected to each other.

- Shall include.

- the switch has two or more transistors, and two or more transistors are electrically connected in series or in parallel. It is assumed that the gates of the respective transistors are electrically connected to each other.

- a node can be paraphrased as a terminal, a wiring, an electrode, a conductive layer, a conductor, an impurity region, etc., depending on a circuit configuration, a device structure, and the like.

- terminals, wiring, etc. can be paraphrased as nodes.

- ground potential ground potential

- the potentials are relative, and when the reference potential changes, the potential given to the wiring, the potential applied to the circuit, the potential output from the circuit, and the like also change.

- the terms “high level potential” and “low level potential” do not mean a specific potential.

- the high level potentials provided by both wirings do not have to be equal to each other.

- the low-level potentials provided by both wirings do not have to be equal to each other. ..

- the "current” is a charge transfer phenomenon (electrical conduction).

- the description “electrical conduction of a positively charged body is occurring” means “electrical conduction of a negatively charged body in the opposite direction”. Is happening. " Therefore, in the present specification and the like, “current” refers to a charge transfer phenomenon (electrical conduction) associated with carrier transfer, unless otherwise specified.

- the carrier here include electrons, holes, anions, cations, complex ions, and the like, and the carriers differ depending on the system in which the current flows (for example, semiconductor, metal, electrolyte, in vacuum, etc.).

- the "current direction” in wiring or the like is the direction in which the carrier that becomes a positive charge moves, and is described as a positive current amount.

- the direction in which the carrier that becomes a negative charge moves is opposite to the direction of the current, and is expressed by the amount of negative current. Therefore, in the present specification and the like, if there is no disclaimer regarding the positive or negative current (or the direction of the current), the description such as “current flows from element A to element B” means “current flows from element B to element A”. Can be rephrased as. Further, the description such as “a current is input to the element A” can be rephrased as "a current is output from the element A” or the like.

- the ordinal numbers “1st”, “2nd”, and “3rd” are added to avoid confusion of the components. Therefore, the number of components is not limited. Moreover, the order of the components is not limited. For example, the component referred to in “first” in one of the embodiments of the present specification and the like may be the other embodiment or the component referred to in “second” in the scope of claims. There can also be. Further, for example, the component referred to in “first” in one of the embodiments of the present specification and the like may be omitted in other embodiments or in the scope of claims.

- the terms “upper” and “lower” do not limit the positional relationship of the components to be directly above or directly below and to be in direct contact with each other.

- the terms “electrode B on the insulating layer A” it is not necessary that the electrode B is formed in direct contact with the insulating layer A, and another configuration is formed between the insulating layer A and the electrode B. Do not exclude those that contain elements.

- words such as “membrane” and “layer” can be interchanged with each other depending on the situation.

- the terms “insulating layer” and “insulating film” may be changed to the term "insulator”.

- Electrode may be used as part of a “wiring” and vice versa.

- terms such as “electrode” and “wiring” include the case where a plurality of “electrodes”, “wiring” and the like are integrally formed.

- a “terminal” may be used as part of a “wiring”, “electrode”, etc., and vice versa.

- the term “terminal” includes a case where a plurality of "electrodes", “wiring”, “terminals” and the like are integrally formed.

- the "electrode” can be a part of “wiring” or “terminal”, and for example, “terminal” can be a part of “wiring” or “electrode”. Further, terms such as “electrode”, “wiring”, and “terminal” may be replaced with terms such as "area” in some cases.

- terms such as “wiring”, “signal line”, and “power line” can be interchanged with each other in some cases or depending on the situation.

- the reverse is also true, and it may be possible to change terms such as “signal line” and “power line” to the term “wiring”.

- a term such as “power line” may be changed to a term such as "signal line”.

- a term such as “signal line” may be changed to a term such as “power line”.

- the term “potential” applied to the wiring may be changed to a term such as “signal” in some cases or depending on the situation.

- the reverse is also true, and terms such as “signal” may be changed to the term “potential”.

- the semiconductor impurities refer to, for example, other than the main components constituting the semiconductor layer.

- an element having a concentration of less than 0.1 atomic% is an impurity.

- the inclusion of impurities may result in, for example, an increase in the defect level density of the semiconductor, a decrease in carrier mobility, a decrease in crystallinity, and the like.

- the impurities that change the characteristics of the semiconductor include, for example, group 1 element, group 2 element, group 13 element, group 14 element, group 15 element, and other than the main component.

- the impurities that change the characteristics of the semiconductor include, for example, Group 1 elements, Group 2 elements, Group 13 elements, Group 15 elements and the like (however, oxygen, Does not contain hydrogen).

- the switch means a switch that is in a conductive state (on state) or a non-conducting state (off state) and has a function of controlling whether or not a current flows.

- the switch means a switch having a function of selecting and switching a path through which a current flows. Therefore, the switch may have two or three or more terminals through which a current flows, in addition to the control terminals.

- an electric switch, a mechanical switch, or the like can be used. That is, the switch is not limited to a specific switch as long as it can control the current.

- Examples of electrical switches include transistors (for example, bipolar transistors, MOS transistors, etc.), diodes (for example, PN diodes, PIN diodes, shotkey diodes, MIM (Metal Insulator Metal) diodes, and MIS (Metal Insulator Semiconductor) diodes. , Diode-connected transistors, etc.), or logic circuits that combine these.

- transistors for example, bipolar transistors, MOS transistors, etc.

- diodes for example, PN diodes, PIN diodes, shotkey diodes, MIM (Metal Insulator Metal) diodes, and MIS (Metal Insulator Semiconductor) diodes. , Diode-connected transistors, etc.

- the "conduction state" of the transistor is, for example, a state in which the source electrode and the drain electrode of the transistor can be regarded as being electrically short-circuited, and a current is applied between the source electrode and the drain electrode. It means a state where it

- the "non-conducting state" of the transistor means a state in which the source electrode and the drain electrode of the transistor can be regarded as being electrically cut off.

- the polarity (conductive type) of the transistor is not particularly limited.

- An example of a mechanical switch is a switch that uses MEMS (Micro Electro Mechanical Systems) technology.

- the switch has an electrode that can be moved mechanically, and by moving the electrode, conduction and non-conduction are controlled and operated.

- parallel means a state in which two straight lines are arranged at an angle of -10 ° or more and 10 ° or less. Therefore, the case of ⁇ 5 ° or more and 5 ° or less is also included.

- substantially parallel or approximately parallel means a state in which two straight lines are arranged at an angle of -30 ° or more and 30 ° or less.

- vertical means a state in which two straight lines are arranged at an angle of 80 ° or more and 100 ° or less. Therefore, the case of 85 ° or more and 95 ° or less is also included.

- substantially vertical or “approximately vertical” means a state in which two straight lines are arranged at an angle of 60 ° or more and 120 ° or less.

- a semiconductor device or the like that performs a product-sum calculation and / or a function calculation.

- a semiconductor device for rewriting the data held in the multiplication cell can provide a semiconductor device that holds a digital value, performs digital-to-analog conversion on the digital value, and performs an operation based on the analog value.

- a semiconductor device or the like that performs a convolution process such as CNN.

- a semiconductor device or the like for AI can be provided.

- a semiconductor device or the like for DNN can be provided.

- a semiconductor device or the like having low power consumption it is possible to provide a semiconductor device or the like that is not easily affected by the temperature of the environment.

- a semiconductor device or the like that is not easily affected by variations in the characteristics of the transistor it is possible to provide a semiconductor device or the like that is not easily affected by variations in the characteristics of the current source.

- a novel semiconductor device or the like can be provided.

- the effect of one aspect of the present invention is not limited to the effects listed above.

- the effects listed above do not preclude the existence of other effects.

- the other effects are the effects not mentioned in this item, which are described below. Effects not mentioned in this item can be derived from the description in the specification, drawings, etc. by those skilled in the art, and can be appropriately extracted from these descriptions.

- one aspect of the present invention has at least one of the above-listed effects and other effects. Therefore, one aspect of the present invention may not have the effects listed above in some cases.

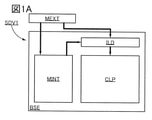

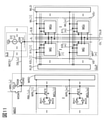

- FIG. 1A and 1B are block diagrams showing a configuration example of a semiconductor device

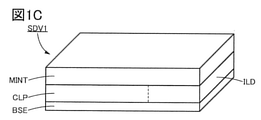

- FIG. 1C is a perspective view showing a configuration example of the semiconductor device

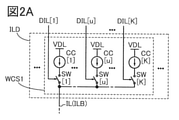

- 2A to 2C are circuits showing a configuration example of a circuit included in the semiconductor device.

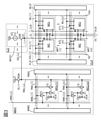

- FIG. 3 is a circuit diagram showing a configuration example of a circuit included in a semiconductor device.

- FIG. 4 is a circuit diagram showing a configuration example of a circuit included in a semiconductor device.

- FIG. 5 is a circuit diagram showing a configuration example of a circuit included in a semiconductor device.

- FIG. 6 is a circuit diagram showing a configuration example of a circuit included in a semiconductor device.

- 7A to 7E are circuit diagrams showing a configuration example of a circuit included in the semiconductor device.

- FIG. 1A and 1B are block diagrams showing a configuration example of a semiconductor device

- FIG. 1C is a perspective view showing a configuration example of the semiconductor device.

- FIG. 3 is a circuit diagram showing a configuration

- FIG. 8 is a circuit diagram showing a configuration example of a circuit included in the semiconductor device.

- FIG. 9 is a circuit diagram showing a configuration example of a circuit included in the semiconductor device.

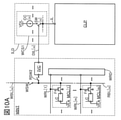

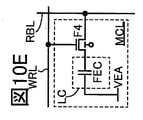

- 10A is a circuit diagram showing a configuration example of a circuit included in the semiconductor device, and

- FIGS. 10B to 10E are circuit diagrams showing a configuration example of a memory cell included in the semiconductor device.

- FIG. 11 is a circuit diagram showing a configuration example of a circuit included in the semiconductor device.

- FIG. 12 is a circuit diagram showing a configuration example of a circuit included in the semiconductor device.

- FIG. 13 is a circuit diagram showing a configuration example of a circuit included in the semiconductor device.

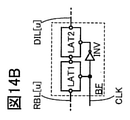

- FIG. 14A is a circuit diagram showing a configuration example of a circuit included in the semiconductor device, and FIG.

- FIG. 14B is a circuit diagram showing a configuration example of a part of the circuit included in the circuit.

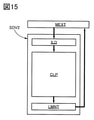

- FIG. 15 is a block diagram showing a configuration example of a semiconductor device.

- FIG. 16 is a block diagram showing a configuration example of a semiconductor device.

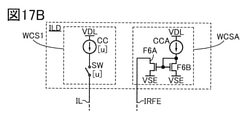

- FIG. 17A is a block diagram showing a configuration example of a semiconductor device, and

- FIG. 17B is a circuit diagram showing a configuration example of a circuit included in the semiconductor device.

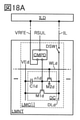

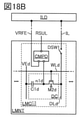

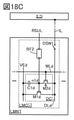

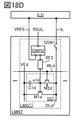

- 18A to 18D are circuit diagrams showing a configuration example of a semiconductor device.

- FIG. 19 is a circuit diagram showing a configuration example of a circuit included in a semiconductor device.

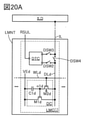

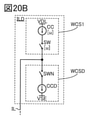

- FIG. 20A is a circuit diagram showing a configuration example of a semiconductor device, and FIG.

- 20B is a circuit diagram showing a configuration example of a circuit included in the semiconductor device.

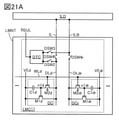

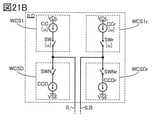

- 21A is a circuit diagram showing a configuration example of a semiconductor device

- FIG. 21B is a circuit diagram showing a configuration example of a circuit included in the semiconductor device.

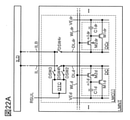

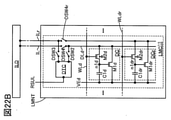

- 22A and 22B are circuit diagrams showing a configuration example of a semiconductor device.

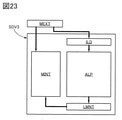

- FIG. 23 is a block diagram showing a configuration example of the semiconductor device.

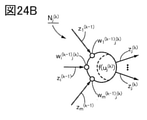

- 24A and 24B are diagrams illustrating a hierarchical neural network.

- FIG. 25 is a circuit diagram showing a configuration example of a circuit included in the semiconductor device.

- FIG. 26 is a circuit diagram showing a configuration example of a circuit included in a semiconductor device.

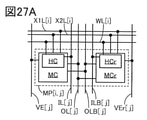

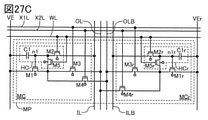

- 27A to 27C are circuit diagrams showing a configuration example of a circuit included in the semiconductor device.

- FIG. 28 is a circuit diagram showing a configuration example of a circuit included in the semiconductor device.

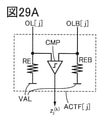

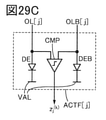

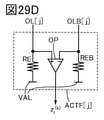

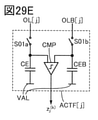

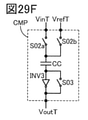

- 29A to 29F are circuit diagrams showing a configuration example of a circuit included in the semiconductor device.

- FIG. 30 is a circuit diagram showing a configuration example of a circuit included in a semiconductor device.

- FIG. 31 is a circuit diagram showing a configuration example of a circuit included in the semiconductor device.

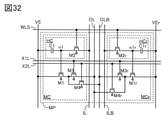

- FIG. 32 is a circuit diagram showing a configuration example of a circuit included in the semiconductor device.

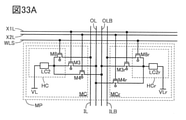

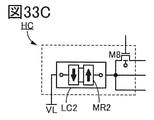

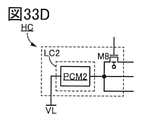

- 33A to 33E are circuit diagrams showing a configuration example of a circuit included in the semiconductor device.

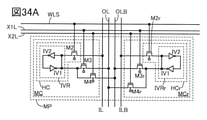

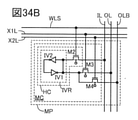

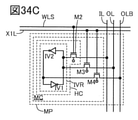

- 34A to 34C are circuit diagrams showing a configuration example of a circuit included in the semiconductor device.

- FIG. 35 is a schematic cross-sectional view showing a configuration example of a semiconductor device.

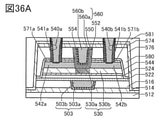

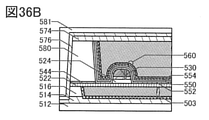

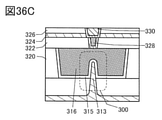

- FIG. 36A to 36C are schematic cross-sectional views showing a configuration example of a transistor.

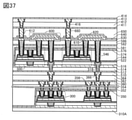

- FIG. 37 is a schematic cross-sectional view showing a configuration example of a semiconductor device.

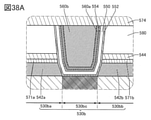

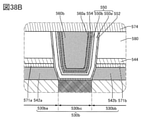

- 38A and 38B are schematic cross-sectional views showing a configuration example of a transistor.

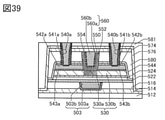

- FIG. 39 is a schematic cross-sectional view showing a configuration example of the transistor.

- FIG. 40A is a diagram for explaining the classification of the crystal structure of IGZO

- FIG. 40B is a diagram for explaining the XRD spectrum of crystalline IGZO

- FIG. 40C is a diagram for explaining the microelectron diffraction pattern of crystalline IGZO.

- .. 41A is a perspective view showing an example of a semiconductor wafer

- FIG. 41A is a perspective view showing an example of a semiconductor wafer

- FIG. 41B is a perspective view showing an example of a chip

- FIGS. 41C and 41D are perspective views showing an example of an electronic component.

- FIG. 42 is a schematic view showing an example of an electronic device.

- 43A to 43C are schematic views showing an example of an electronic device.

- the synaptic connection strength can be changed by giving existing information to the neural network.

- the process of giving existing information to the neural network and determining the bond strength may be called "learning”.

- neural network models include Hopfield type and hierarchical type.

- a neural network having a multi-layer structure may be referred to as a “deep neural network” (DNN), and machine learning by a deep neural network may be referred to as “deep learning”.

- DNN deep neural network

- machine learning by a deep neural network may be referred to as “deep learning”.

- a metal oxide is a metal oxide in a broad sense. Metal oxides are classified into oxide insulators, oxide conductors (including transparent oxide conductors), oxide semiconductors (also referred to as Oxide Semiconductor or simply OS) and the like. For example, when a metal oxide is contained in the channel forming region of a transistor, the metal oxide may be referred to as an oxide semiconductor. That is, when a metal oxide can form a channel forming region of a transistor having at least one of an amplification action, a rectifying action, and a switching action, the metal oxide is referred to as a metal oxide semiconductor. be able to. Further, when the term "OS transistor" is used, it can be rephrased as a transistor having a metal oxide or an oxide semiconductor.

- a metal oxide having nitrogen may also be collectively referred to as a metal oxide. Further, the metal oxide having nitrogen may be referred to as a metal oxynitride.

- the configuration shown in each embodiment can be appropriately combined with the configuration shown in other embodiments to form one aspect of the present invention. Further, when a plurality of configuration examples are shown in one embodiment, the configuration examples can be appropriately combined with each other.

- the content described in one embodiment (may be a part of the content) is different from the content described in the embodiment (may be a part of the content) and one or more different implementations. It is possible to apply, combine, or replace at least one content with the content described in the form of (may be a part of the content).

- figure (which may be a part) described in one embodiment is different from another part of the figure, another figure (which may be a part) described in the embodiment, and one or more different figures.

- the figure (which may be a part) described in the embodiment is different from another part of the figure, another figure (which may be a part) described in the embodiment, and one or more different figures.

- more figures can be formed.

- the code is used for identification such as "_1", “[n]”, “[m, n]”. May be added and described. Further, in the drawings and the like, when the reference numerals such as “_1”, “[n]” and “[m, n]” are added to the reference numerals, when it is not necessary to distinguish them in the present specification and the like, when it is not necessary to distinguish them.

- the identification code may not be described.

- FIG. 1A is a block diagram showing a configuration example of the semiconductor device SDV1 which is one aspect of the present invention.

- the semiconductor device SDV1 has, for example, a storage device MINT, a circuit ILD, and a calculation unit CLP. Further, FIG. 1A also shows a storage device TEXT in order to show the configuration of an electrical connection with the semiconductor device SDV1.

- the storage device MEM is provided outside the semiconductor device SDV1 as an example.

- the storage device MEM holds data for performing an operation in the arithmetic unit CLP.

- the storage device MEXT transmits the data to the storage device MINT as a digital voltage signal or the like.

- the storage device MEXT may transmit the data not only to the storage device MINT but also to the circuit ILD described later. That is, the semiconductor device SDV1 may be configured so that the storage device MINT and the circuit ILD can be switched as the transmission destination of the storage device MEM.

- the semiconductor device SDV1 when the semiconductor device SDV1 is configured so that the storage device MINT and the circuit ILD can be switched as the transmission destination of the signal output from the storage device MEXT, when data is transmitted from the storage device MEXT to the storage device MINT, it is stored. In order to reduce the memory capacity of the device MINT, the number of bits of the data may be reduced. Further, when data is transmitted from the storage device MEM to the circuit ILD, the number of bits of the data may be increased. Alternatively, when data is transmitted from the storage device MEXT to the storage device MINT, a high bit value of the data is transmitted in order to reduce the memory capacity of the storage device MINT, and a low bit value is required. A low bit value may be input from the storage device TEXT to the circuit ILD. That is, the storage device MINT and the storage device MEM may be input to the circuit ILD at the same time.

- the storage device MEM can be, for example, a storage such as an HDD (hard disk drive) or SSD (solid state drive).

- HDD hard disk drive

- SSD solid state drive

- the semiconductor device SDV1 can be manufactured, for example, by forming a circuit element or the like on one substrate BSE.

- various substrates can be used.

- various substrates include semiconductor substrates (for example, single crystal substrate or silicon substrate), SOI substrates, glass substrates, quartz substrates, plastic substrates, sapphire glass substrates, metal substrates, stainless steel substrates, and stainless still foils.

- glass substrates include barium borosilicate glass, aluminoborosilicate glass, and soda lime glass.

- Examples of flexible substrates, laminated films, base films, etc. include the following.

- plastics typified by polyethylene terephthalate (PET), polyethylene naphthalate (PEN), polyether sulfone (PES), and polytetrafluoroethylene (PTFE).

- PET polyethylene terephthalate

- PEN polyethylene naphthalate

- PES polyether sulfone

- PTFE polytetrafluoroethylene

- a synthetic resin such as acrylic.

- polypropylene polyester, polyvinyl fluoride, polyvinyl chloride and the like.

- polyamide, polyimide, aramid, epoxy resin, inorganic thin-film film, papers and the like are examples of plastics typified by polyethylene terephthalate (PET), polyethylene naphthalate (PEN), polyether sulfone (PES), and polytetrafluoroethylene (PTFE).

- acrylic polypropylene

- polyester polyvinyl fluoride

- polyvinyl chloride polyvinyl chloride

- a transistor using a semiconductor substrate, a single crystal substrate, an SOI substrate, or the like, it is possible to manufacture a transistor having a high current capacity and a small size with little variation in characteristics, size, or shape. ..

- a circuit is configured with such transistors, it is possible to reduce the power consumption of the circuit or increase the integration of the circuit.

- a flexible substrate may be used as the substrate BSE, and a transistor may be formed directly on the flexible substrate.

- a release layer may be provided between the substrate and the transistor. The release layer can be used to separate a part or all of the semiconductor device from the substrate and transfer it to another substrate. At that time, the transistor can be reprinted on a substrate having inferior heat resistance, a flexible substrate, or the like.

- a structure in which an inorganic film of a tungsten film and a silicon oxide film is laminated, a structure in which an organic resin film such as polyimide is formed on a substrate, or the like can be used.

- a transistor may be formed using one substrate, then the transistor may be transposed to another substrate, and the transistor may be arranged on another substrate (for example, substrate BSE).

- substrate BSE a substrate on which the transistor is translocated

- silk, cotton, linen synthetic fibers

- nylon, polyurethane, polyester or recycled fibers (including acetate, cupra, rayon, recycled polyester), leather substrates, rubber substrates, etc.

- a part of the circuit necessary for realizing a predetermined function is formed on one board, and another part of the circuit necessary for realizing a predetermined function is formed on another board. It is possible. For example, a part of the circuit necessary to realize a predetermined function is formed on a glass substrate, and another part of the circuit necessary to realize a predetermined function is a single crystal substrate (or SOI substrate). Can be formed into. Then, a single crystal substrate (also referred to as an IC chip) on which another part of the circuit necessary for realizing a predetermined function is formed is connected to the glass substrate by COG (Chip On Glass) to be connected to the glass substrate.

- COG Chip On Glass

- the IC chip can be placed in the glass.

- the IC chip can be connected to a glass substrate using a TAB (Tape Automated Bonding), COF (Chip On Film), SMT (Surface Mount Technology), a printed circuit board, or the like.

- TAB Transmission Automated Bonding

- COF Chip On Film

- SMT Surface Mount Technology

- a printed circuit board or the like.

- a circuit having a large drive voltage or a circuit having a high drive frequency often consumes a large amount of power. Therefore, such a circuit is formed on a substrate (for example, a single crystal substrate) different from the pixel portion to form an IC chip. By using this IC chip, it is possible to prevent an increase in power consumption.

- each of the transistor included in the arithmetic unit CLP and the transistor included in the circuit ILD can be formed on the substrate BSE as Si transistors. ..

- the transistor included in the storage device MINT as an OS transistor, the storage device MINT can be provided above the arithmetic unit CLP and / or the circuit ILD. That is, as an example, the semiconductor device SDV1 has a configuration in which a calculation unit CLP and a circuit ILD are provided above the substrate BSE, and a storage device MINT is provided above the calculation unit CLP and the circuit ILD, as shown in FIG. 1C. Can be.

- the storage device MINT provided in the semiconductor device SDV1 has a function of acquiring information read by a storage device MEM provided outside the semiconductor device SDV1 and holding the information. Further, the storage device MINT has a function of reading the information held in the storage device MINT and transmitting the information to the circuit ILD.

- the information sent from the storage device MEXT to the storage device MINT is treated as data for performing a calculation by the calculation unit CLP described later.

- the storage device MINT will be described as a configuration for storing digital values.

- the storage device MINT as a storage device that stores as a digital value, even if the absolute value of the amount of charge held in the storage element decreases, the range of potential at which data can be read out is large, so it is the same as when writing. No data can be read.

- the data stored in the storage element can be easily refreshed, so that the potential (charge) held in the storage element can be maintained for a long time. Therefore, it is preferable that the storage device MINT has a function of refreshing the data held periodically.

- the refresh operation may be performed after the data is transmitted to the arithmetic unit CLP (circuit ILD) described later.

- data refresh means that the voltage corresponding to the data of the storage element is read out and the voltage is boosted or stepped down to an appropriate level by an amplifier circuit such as a sense amplifier. , The operation of writing back to the storage element.

- the data may be read from the storage device MEM and written to the memory cell.

- the storage device MINT according to the semiconductor device of the present invention may be configured to store not only digital values but also multi-valued values, analog values and the like.

- the number of bits of the memory cell should be smaller than the number of bits held in the multiplication cell of the arithmetic unit CLP.

- a plurality of memory cells of the storage device MINT can be associated with one multiplication cell of the arithmetic unit CLP. For example, if a 4-bit value can be held in one memory cell of the storage device MINT and an 8-bit value can be held in one multiplication cell of the arithmetic unit CLP, two 4-bit values can be held in the memory cell of the storage device MINT. By writing, an 8-bit value can be written in the multiplication cell of the arithmetic unit CLP.

- examples of the metal oxide contained in the channel forming region of the OS transistor include indium, an In-M-Zn oxide having element M and zinc (element M is aluminum, gallium, ittrium, tin, copper and vanadium). , Berylium, boron, titanium, iron, nickel, germanium, zirconium, molybdenum, lanthanum, cerium, neodymium, hafnium, tantalum, tungsten, magnesium, etc.).

- a transistor having silicon in the channel forming region hereinafter, referred to as a Si transistor may be applied.

- the silicon for example, single crystal silicon, amorphous silicon (sometimes referred to as hydride amorphous silicon), microcrystalline silicon, polycrystalline silicon, or the like can be used.

- the transistor other than the OS transistor and the Si transistor for example, a transistor in which Ge and the like are included in the channel forming region, and a compound semiconductor such as ZnSe, CdS, GaAs, InP, GaN, and SiGe are included in the channel forming region.

- Transistors, transistors in which carbon nanotubes are contained in the channel forming region, transistors in which organic semiconductors are contained in the channel forming region, and the like can be used.

- the circuit ILD functions as a current source circuit for supplying a current to the arithmetic unit CLP as an example. Specifically, the circuit ILD supplies a current corresponding to the information read from the storage device MINT to the circuit included in the arithmetic unit CLP.

- the circuit ILD is not a current source circuit for supplying a current to the arithmetic unit CLP, but a voltage source circuit for inputting a voltage corresponding to the information read from the storage device MINT to the arithmetic unit CLP, for example. (Voltage generation circuit) may be used.

- the arithmetic unit CLP has a plurality of circuits that function as multiplication cells. Further, as an example, the multiplication cell has a function of holding data used for calculation as an analog value. Further, in the arithmetic unit CLP, it is assumed that the circuits are arranged in a matrix. Further, the circuit holds the information (for example, current, voltage, etc.) sent from the circuit ILD, and then inputs the voltage corresponding to the multiplier to the arithmetic unit CLP, so that the value corresponding to the information is obtained. The product of and the multiplier can be calculated.

- the information for example, current, voltage, etc.

- the sum of the currents is obtained by adding the currents output from the plurality of circuits to each other (each information held in the plurality of circuits). For example, it can be an amount corresponding to the value of the sum of products of current, voltage, etc.) and a plurality of multipliers. Further, it is assumed that the arithmetic unit CLP also includes a drive circuit for operating the multiplication cell.