WO2015151426A1 - 半導体装置、積層型半導体装置、封止後積層型半導体装置、及びこれらの製造方法 - Google Patents

半導体装置、積層型半導体装置、封止後積層型半導体装置、及びこれらの製造方法 Download PDFInfo

- Publication number

- WO2015151426A1 WO2015151426A1 PCT/JP2015/001433 JP2015001433W WO2015151426A1 WO 2015151426 A1 WO2015151426 A1 WO 2015151426A1 JP 2015001433 W JP2015001433 W JP 2015001433W WO 2015151426 A1 WO2015151426 A1 WO 2015151426A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- insulating layer

- semiconductor device

- electrode

- semiconductor element

- forming

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 369

- 238000004519 manufacturing process Methods 0.000 title claims description 74

- 229910052751 metal Inorganic materials 0.000 claims abstract description 147

- 239000002184 metal Substances 0.000 claims abstract description 147

- 229910000679 solder Inorganic materials 0.000 claims abstract description 43

- 229920005989 resin Polymers 0.000 claims description 71

- 239000011347 resin Substances 0.000 claims description 71

- 238000000034 method Methods 0.000 claims description 67

- 239000000758 substrate Substances 0.000 claims description 57

- 238000007747 plating Methods 0.000 claims description 48

- 239000002131 composite material Substances 0.000 claims description 32

- WSFSSNUMVMOOMR-UHFFFAOYSA-N Formaldehyde Chemical group O=C WSFSSNUMVMOOMR-UHFFFAOYSA-N 0.000 claims description 27

- 238000007789 sealing Methods 0.000 claims description 27

- 230000000149 penetrating effect Effects 0.000 claims description 22

- -1 methylol groups Chemical group 0.000 claims description 19

- 238000000059 patterning Methods 0.000 claims description 19

- 238000001459 lithography Methods 0.000 claims description 18

- 230000015572 biosynthetic process Effects 0.000 claims description 17

- 229910007637 SnAg Inorganic materials 0.000 claims description 16

- 238000010030 laminating Methods 0.000 claims description 16

- 125000004432 carbon atom Chemical group C* 0.000 claims description 15

- 125000000962 organic group Chemical group 0.000 claims description 15

- 239000000853 adhesive Substances 0.000 claims description 14

- 230000001070 adhesive effect Effects 0.000 claims description 14

- 230000001681 protective effect Effects 0.000 claims description 12

- 125000003545 alkoxy group Chemical group 0.000 claims description 10

- 125000000217 alkyl group Chemical group 0.000 claims description 10

- 229920002120 photoresistant polymer Polymers 0.000 claims description 10

- 229920001296 polysiloxane Polymers 0.000 claims description 10

- 238000004544 sputter deposition Methods 0.000 claims description 10

- 238000004528 spin coating Methods 0.000 claims description 9

- 239000002253 acid Substances 0.000 claims description 8

- 239000011248 coating agent Substances 0.000 claims description 8

- 238000000576 coating method Methods 0.000 claims description 8

- 239000002904 solvent Substances 0.000 claims description 8

- 239000003431 cross linking reagent Substances 0.000 claims description 7

- 150000002989 phenols Chemical class 0.000 claims description 7

- 125000002924 primary amino group Chemical group [H]N([H])* 0.000 claims description 7

- 239000007767 bonding agent Substances 0.000 claims description 6

- 150000001875 compounds Chemical class 0.000 claims description 6

- 229920000642 polymer Polymers 0.000 claims description 6

- 238000009413 insulation Methods 0.000 claims description 5

- 238000003825 pressing Methods 0.000 claims description 4

- 238000011049 filling Methods 0.000 claims description 3

- 238000009501 film coating Methods 0.000 claims description 3

- 238000002844 melting Methods 0.000 claims description 3

- 230000008018 melting Effects 0.000 claims description 3

- 239000000203 mixture Substances 0.000 claims description 3

- 125000001183 hydrocarbyl group Chemical group 0.000 claims 2

- 239000010410 layer Substances 0.000 description 238

- 239000010408 film Substances 0.000 description 112

- 238000001723 curing Methods 0.000 description 11

- 239000011810 insulating material Substances 0.000 description 9

- 238000011417 postcuring Methods 0.000 description 6

- 239000000463 material Substances 0.000 description 5

- 229920002725 thermoplastic elastomer Polymers 0.000 description 5

- 239000010409 thin film Substances 0.000 description 5

- 239000004698 Polyethylene Substances 0.000 description 4

- 238000009713 electroplating Methods 0.000 description 4

- 239000005020 polyethylene terephthalate Substances 0.000 description 4

- 229920000139 polyethylene terephthalate Polymers 0.000 description 4

- 239000000126 substance Substances 0.000 description 4

- ARXJGSRGQADJSQ-UHFFFAOYSA-N 1-methoxypropan-2-ol Chemical compound COCC(C)O ARXJGSRGQADJSQ-UHFFFAOYSA-N 0.000 description 3

- 238000005530 etching Methods 0.000 description 3

- 238000010438 heat treatment Methods 0.000 description 3

- 150000002430 hydrocarbons Chemical group 0.000 description 3

- 238000003475 lamination Methods 0.000 description 3

- 229920000573 polyethylene Polymers 0.000 description 3

- 238000004804 winding Methods 0.000 description 3

- JOLQKTGDSGKSKJ-UHFFFAOYSA-N 1-ethoxypropan-2-ol Chemical compound CCOCC(C)O JOLQKTGDSGKSKJ-UHFFFAOYSA-N 0.000 description 2

- YEJRWHAVMIAJKC-UHFFFAOYSA-N 4-Butyrolactone Chemical compound O=C1CCCO1 YEJRWHAVMIAJKC-UHFFFAOYSA-N 0.000 description 2

- 229920000089 Cyclic olefin copolymer Polymers 0.000 description 2

- PPBRXRYQALVLMV-UHFFFAOYSA-N Styrene Chemical compound C=CC1=CC=CC=C1 PPBRXRYQALVLMV-UHFFFAOYSA-N 0.000 description 2

- JHIVVAPYMSGYDF-UHFFFAOYSA-N cyclohexanone Chemical compound O=C1CCCCC1 JHIVVAPYMSGYDF-UHFFFAOYSA-N 0.000 description 2

- BGTOWKSIORTVQH-UHFFFAOYSA-N cyclopentanone Chemical compound O=C1CCCC1 BGTOWKSIORTVQH-UHFFFAOYSA-N 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- LZCLXQDLBQLTDK-UHFFFAOYSA-N ethyl 2-hydroxypropanoate Chemical compound CCOC(=O)C(C)O LZCLXQDLBQLTDK-UHFFFAOYSA-N 0.000 description 2

- 239000003960 organic solvent Substances 0.000 description 2

- LLHKCFNBLRBOGN-UHFFFAOYSA-N propylene glycol methyl ether acetate Chemical compound COCC(C)OC(C)=O LLHKCFNBLRBOGN-UHFFFAOYSA-N 0.000 description 2

- 229920002050 silicone resin Polymers 0.000 description 2

- 239000000243 solution Substances 0.000 description 2

- 239000002344 surface layer Substances 0.000 description 2

- WGTYBPLFGIVFAS-UHFFFAOYSA-M tetramethylammonium hydroxide Chemical compound [OH-].C[N+](C)(C)C WGTYBPLFGIVFAS-UHFFFAOYSA-M 0.000 description 2

- 238000002560 therapeutic procedure Methods 0.000 description 2

- 229920005992 thermoplastic resin Polymers 0.000 description 2

- LJHFIVQEAFAURQ-ZPUQHVIOSA-N (NE)-N-[(2E)-2-hydroxyiminoethylidene]hydroxylamine Chemical class O\N=C\C=N\O LJHFIVQEAFAURQ-ZPUQHVIOSA-N 0.000 description 1

- LEEANUDEDHYDTG-UHFFFAOYSA-N 1,2-dimethoxypropane Chemical compound COCC(C)OC LEEANUDEDHYDTG-UHFFFAOYSA-N 0.000 description 1

- WKBPZYKAUNRMKP-UHFFFAOYSA-N 1-[2-(2,4-dichlorophenyl)pentyl]1,2,4-triazole Chemical compound C=1C=C(Cl)C=C(Cl)C=1C(CCC)CN1C=NC=N1 WKBPZYKAUNRMKP-UHFFFAOYSA-N 0.000 description 1

- LIPRQQHINVWJCH-UHFFFAOYSA-N 1-ethoxypropan-2-yl acetate Chemical compound CCOCC(C)OC(C)=O LIPRQQHINVWJCH-UHFFFAOYSA-N 0.000 description 1

- KUMMBDBTERQYCG-UHFFFAOYSA-N 2,6-bis(hydroxymethyl)-4-methylphenol Chemical compound CC1=CC(CO)=C(O)C(CO)=C1 KUMMBDBTERQYCG-UHFFFAOYSA-N 0.000 description 1

- XNWFRZJHXBZDAG-UHFFFAOYSA-N 2-METHOXYETHANOL Chemical compound COCCO XNWFRZJHXBZDAG-UHFFFAOYSA-N 0.000 description 1

- ZNQVEEAIQZEUHB-UHFFFAOYSA-N 2-ethoxyethanol Chemical compound CCOCCO ZNQVEEAIQZEUHB-UHFFFAOYSA-N 0.000 description 1

- JSGVZVOGOQILFM-UHFFFAOYSA-N 3-methoxy-1-butanol Chemical compound COC(C)CCO JSGVZVOGOQILFM-UHFFFAOYSA-N 0.000 description 1

- MFKRHJVUCZRDTF-UHFFFAOYSA-N 3-methoxy-3-methylbutan-1-ol Chemical compound COC(C)(C)CCO MFKRHJVUCZRDTF-UHFFFAOYSA-N 0.000 description 1

- DKPFZGUDAPQIHT-UHFFFAOYSA-N Butyl acetate Natural products CCCCOC(C)=O DKPFZGUDAPQIHT-UHFFFAOYSA-N 0.000 description 1

- WXYXQGQNLHWHPX-UHFFFAOYSA-N C(C)(=O)OC(COC(CCCCC)(C)C)C Chemical compound C(C)(=O)OC(COC(CCCCC)(C)C)C WXYXQGQNLHWHPX-UHFFFAOYSA-N 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- 239000004713 Cyclic olefin copolymer Substances 0.000 description 1

- YXHKONLOYHBTNS-UHFFFAOYSA-N Diazomethane Chemical class C=[N+]=[N-] YXHKONLOYHBTNS-UHFFFAOYSA-N 0.000 description 1

- XXRCUYVCPSWGCC-UHFFFAOYSA-N Ethyl pyruvate Chemical compound CCOC(=O)C(C)=O XXRCUYVCPSWGCC-UHFFFAOYSA-N 0.000 description 1

- 229920000877 Melamine resin Polymers 0.000 description 1

- 239000005062 Polybutadiene Substances 0.000 description 1

- 239000004743 Polypropylene Substances 0.000 description 1

- 239000004820 Pressure-sensitive adhesive Substances 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- FAPWRFPIFSIZLT-UHFFFAOYSA-M Sodium chloride Chemical compound [Na+].[Cl-] FAPWRFPIFSIZLT-UHFFFAOYSA-M 0.000 description 1

- 239000002174 Styrene-butadiene Substances 0.000 description 1

- XSQUKJJJFZCRTK-UHFFFAOYSA-N Urea Chemical compound NC(N)=O XSQUKJJJFZCRTK-UHFFFAOYSA-N 0.000 description 1

- 239000012790 adhesive layer Substances 0.000 description 1

- 150000001336 alkenes Chemical class 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- MTAZNLWOLGHBHU-UHFFFAOYSA-N butadiene-styrene rubber Chemical compound C=CC=C.C=CC1=CC=CC=C1 MTAZNLWOLGHBHU-UHFFFAOYSA-N 0.000 description 1

- 229940043232 butyl acetate Drugs 0.000 description 1

- 239000004202 carbamide Substances 0.000 description 1

- 239000003054 catalyst Substances 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- 238000003851 corona treatment Methods 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- SBZXBUIDTXKZTM-UHFFFAOYSA-N diglyme Chemical compound COCCOCCOC SBZXBUIDTXKZTM-UHFFFAOYSA-N 0.000 description 1

- 125000000118 dimethyl group Chemical group [H]C([H])([H])* 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 238000001035 drying Methods 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 150000002148 esters Chemical class 0.000 description 1

- 150000002170 ethers Chemical class 0.000 description 1

- BHXIWUJLHYHGSJ-UHFFFAOYSA-N ethyl 3-ethoxypropanoate Chemical compound CCOCCC(=O)OCC BHXIWUJLHYHGSJ-UHFFFAOYSA-N 0.000 description 1

- 229940116333 ethyl lactate Drugs 0.000 description 1

- 229940117360 ethyl pyruvate Drugs 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- LNEPOXFFQSENCJ-UHFFFAOYSA-N haloperidol Chemical compound C1CC(O)(C=2C=CC(Cl)=CC=2)CCN1CCCC(=O)C1=CC=C(F)C=C1 LNEPOXFFQSENCJ-UHFFFAOYSA-N 0.000 description 1

- FUZZWVXGSFPDMH-UHFFFAOYSA-N hexanoic acid Chemical compound CCCCCC(O)=O FUZZWVXGSFPDMH-UHFFFAOYSA-N 0.000 description 1

- 238000005304 joining Methods 0.000 description 1

- 150000002576 ketones Chemical class 0.000 description 1

- JDSHMPZPIAZGSV-UHFFFAOYSA-N melamine Chemical compound NC1=NC(N)=NC(N)=N1 JDSHMPZPIAZGSV-UHFFFAOYSA-N 0.000 description 1

- 150000007974 melamines Chemical class 0.000 description 1

- BDJSOPWXYLFTNW-UHFFFAOYSA-N methyl 3-methoxypropanoate Chemical compound COCCC(=O)OC BDJSOPWXYLFTNW-UHFFFAOYSA-N 0.000 description 1

- IZJVVXCHJIQVOL-UHFFFAOYSA-N nitro(phenyl)methanesulfonic acid Chemical class OS(=O)(=O)C([N+]([O-])=O)C1=CC=CC=C1 IZJVVXCHJIQVOL-UHFFFAOYSA-N 0.000 description 1

- JRZJOMJEPLMPRA-UHFFFAOYSA-N olefin Natural products CCCCCCCC=C JRZJOMJEPLMPRA-UHFFFAOYSA-N 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 125000001997 phenyl group Chemical group [H]C1=C([H])C([H])=C(*)C([H])=C1[H] 0.000 description 1

- 238000000016 photochemical curing Methods 0.000 description 1

- 229920002857 polybutadiene Polymers 0.000 description 1

- 229920000515 polycarbonate Polymers 0.000 description 1

- 239000004417 polycarbonate Substances 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920006254 polymer film Polymers 0.000 description 1

- 229920000098 polyolefin Polymers 0.000 description 1

- 229920001155 polypropylene Polymers 0.000 description 1

- 230000002265 prevention Effects 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 150000003839 salts Chemical class 0.000 description 1

- 230000035945 sensitivity Effects 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 239000011115 styrene butadiene Substances 0.000 description 1

- 229920003048 styrene butadiene rubber Polymers 0.000 description 1

- 229920003002 synthetic resin Polymers 0.000 description 1

- 239000000057 synthetic resin Substances 0.000 description 1

- JAELLLITIZHOGQ-UHFFFAOYSA-N tert-butyl propanoate Chemical compound CCC(=O)OC(C)(C)C JAELLLITIZHOGQ-UHFFFAOYSA-N 0.000 description 1

- 238000011282 treatment Methods 0.000 description 1

- 150000003918 triazines Chemical class 0.000 description 1

- 150000003672 ureas Chemical class 0.000 description 1

- 239000011800 void material Substances 0.000 description 1

- 238000005406 washing Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/562—Protection against mechanical damage

-

- C—CHEMISTRY; METALLURGY

- C08—ORGANIC MACROMOLECULAR COMPOUNDS; THEIR PREPARATION OR CHEMICAL WORKING-UP; COMPOSITIONS BASED THEREON

- C08L—COMPOSITIONS OF MACROMOLECULAR COMPOUNDS

- C08L83/00—Compositions of macromolecular compounds obtained by reactions forming in the main chain of the macromolecule a linkage containing silicon with or without sulfur, nitrogen, oxygen or carbon only; Compositions of derivatives of such polymers

- C08L83/14—Compositions of macromolecular compounds obtained by reactions forming in the main chain of the macromolecule a linkage containing silicon with or without sulfur, nitrogen, oxygen or carbon only; Compositions of derivatives of such polymers in which at least two but not all the silicon atoms are connected by linkages other than oxygen atoms

-

- C—CHEMISTRY; METALLURGY

- C09—DYES; PAINTS; POLISHES; NATURAL RESINS; ADHESIVES; COMPOSITIONS NOT OTHERWISE PROVIDED FOR; APPLICATIONS OF MATERIALS NOT OTHERWISE PROVIDED FOR

- C09D—COATING COMPOSITIONS, e.g. PAINTS, VARNISHES OR LACQUERS; FILLING PASTES; CHEMICAL PAINT OR INK REMOVERS; INKS; CORRECTING FLUIDS; WOODSTAINS; PASTES OR SOLIDS FOR COLOURING OR PRINTING; USE OF MATERIALS THEREFOR

- C09D163/00—Coating compositions based on epoxy resins; Coating compositions based on derivatives of epoxy resins

-

- C—CHEMISTRY; METALLURGY

- C09—DYES; PAINTS; POLISHES; NATURAL RESINS; ADHESIVES; COMPOSITIONS NOT OTHERWISE PROVIDED FOR; APPLICATIONS OF MATERIALS NOT OTHERWISE PROVIDED FOR

- C09D—COATING COMPOSITIONS, e.g. PAINTS, VARNISHES OR LACQUERS; FILLING PASTES; CHEMICAL PAINT OR INK REMOVERS; INKS; CORRECTING FLUIDS; WOODSTAINS; PASTES OR SOLIDS FOR COLOURING OR PRINTING; USE OF MATERIALS THEREFOR

- C09D183/00—Coating compositions based on macromolecular compounds obtained by reactions forming in the main chain of the macromolecule a linkage containing silicon, with or without sulfur, nitrogen, oxygen, or carbon only; Coating compositions based on derivatives of such polymers

- C09D183/14—Coating compositions based on macromolecular compounds obtained by reactions forming in the main chain of the macromolecule a linkage containing silicon, with or without sulfur, nitrogen, oxygen, or carbon only; Coating compositions based on derivatives of such polymers in which at least two but not all the silicon atoms are connected by linkages other than oxygen atoms

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C14/00—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C14/00—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material

- C23C14/04—Coating on selected surface areas, e.g. using masks

- C23C14/042—Coating on selected surface areas, e.g. using masks using masks

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C14/00—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material

- C23C14/22—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material characterised by the process of coating

- C23C14/34—Sputtering

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25D—PROCESSES FOR THE ELECTROLYTIC OR ELECTROPHORETIC PRODUCTION OF COATINGS; ELECTROFORMING; APPARATUS THEREFOR

- C25D5/00—Electroplating characterised by the process; Pretreatment or after-treatment of workpieces

- C25D5/02—Electroplating of selected surface areas

- C25D5/022—Electroplating of selected surface areas using masking means

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25D—PROCESSES FOR THE ELECTROLYTIC OR ELECTROPHORETIC PRODUCTION OF COATINGS; ELECTROFORMING; APPARATUS THEREFOR

- C25D5/00—Electroplating characterised by the process; Pretreatment or after-treatment of workpieces

- C25D5/48—After-treatment of electroplated surfaces

- C25D5/50—After-treatment of electroplated surfaces by heat-treatment

- C25D5/505—After-treatment of electroplated surfaces by heat-treatment of electroplated tin coatings, e.g. by melting

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25D—PROCESSES FOR THE ELECTROLYTIC OR ELECTROPHORETIC PRODUCTION OF COATINGS; ELECTROFORMING; APPARATUS THEREFOR

- C25D7/00—Electroplating characterised by the article coated

- C25D7/12—Semiconductors

- C25D7/123—Semiconductors first coated with a seed layer or a conductive layer

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/0035—Multiple processes, e.g. applying a further resist layer on an already in a previously step, processed pattern or textured surface

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/004—Photosensitive materials

- G03F7/075—Silicon-containing compounds

- G03F7/0757—Macromolecular compounds containing Si-O, Si-C or Si-N bonds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups H01L21/06 - H01L21/326

- H01L21/4814—Conductive parts

- H01L21/4846—Leads on or in insulating or insulated substrates, e.g. metallisation

- H01L21/4853—Connection or disconnection of other leads to or from a metallisation, e.g. pins, wires, bumps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups H01L21/06 - H01L21/326

- H01L21/4814—Conductive parts

- H01L21/4846—Leads on or in insulating or insulated substrates, e.g. metallisation

- H01L21/486—Via connections through the substrate with or without pins

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

- H01L21/565—Moulds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/12—Mountings, e.g. non-detachable insulating substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/31—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape

- H01L23/3107—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed

- H01L23/3114—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed the device being a chip scale package, e.g. CSP

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49827—Via connections through the substrates, e.g. pins going through the substrate, coaxial cables

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5384—Conductive vias through the substrate with or without pins, e.g. buried coaxial conductors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5386—Geometry or layout of the interconnection structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5389—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates the chips being integrally enclosed by the interconnect and support structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L24/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L24/23—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process

- H01L24/24—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process of an individual high density interconnect connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/82—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by forming build-up interconnects at chip-level, e.g. for high density interconnects [HDI]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L24/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L25/0657—Stacked arrangements of devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/10—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices having separate containers

- H01L25/105—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices having separate containers the devices being of a type provided for in group H01L27/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/50—Multistep manufacturing processes of assemblies consisting of devices, each device being of a type provided for in group H01L27/00 or H01L29/00

-

- C—CHEMISTRY; METALLURGY

- C08—ORGANIC MACROMOLECULAR COMPOUNDS; THEIR PREPARATION OR CHEMICAL WORKING-UP; COMPOSITIONS BASED THEREON

- C08G—MACROMOLECULAR COMPOUNDS OBTAINED OTHERWISE THAN BY REACTIONS ONLY INVOLVING UNSATURATED CARBON-TO-CARBON BONDS

- C08G59/00—Polycondensates containing more than one epoxy group per molecule; Macromolecules obtained by polymerising compounds containing more than one epoxy group per molecule using curing agents or catalysts which react with the epoxy groups

- C08G59/18—Macromolecules obtained by polymerising compounds containing more than one epoxy group per molecule using curing agents or catalysts which react with the epoxy groups ; e.g. general methods of curing

- C08G59/20—Macromolecules obtained by polymerising compounds containing more than one epoxy group per molecule using curing agents or catalysts which react with the epoxy groups ; e.g. general methods of curing characterised by the epoxy compounds used

- C08G59/32—Epoxy compounds containing three or more epoxy groups

- C08G59/3254—Epoxy compounds containing three or more epoxy groups containing atoms other than carbon, hydrogen, oxygen or nitrogen

- C08G59/3281—Epoxy compounds containing three or more epoxy groups containing atoms other than carbon, hydrogen, oxygen or nitrogen containing silicon

-

- C—CHEMISTRY; METALLURGY

- C08—ORGANIC MACROMOLECULAR COMPOUNDS; THEIR PREPARATION OR CHEMICAL WORKING-UP; COMPOSITIONS BASED THEREON

- C08G—MACROMOLECULAR COMPOUNDS OBTAINED OTHERWISE THAN BY REACTIONS ONLY INVOLVING UNSATURATED CARBON-TO-CARBON BONDS

- C08G77/00—Macromolecular compounds obtained by reactions forming a linkage containing silicon with or without sulfur, nitrogen, oxygen or carbon in the main chain of the macromolecule

- C08G77/48—Macromolecular compounds obtained by reactions forming a linkage containing silicon with or without sulfur, nitrogen, oxygen or carbon in the main chain of the macromolecule in which at least two but not all the silicon atoms are connected by linkages other than oxygen atoms

- C08G77/50—Macromolecular compounds obtained by reactions forming a linkage containing silicon with or without sulfur, nitrogen, oxygen or carbon in the main chain of the macromolecule in which at least two but not all the silicon atoms are connected by linkages other than oxygen atoms by carbon linkages

- C08G77/52—Macromolecular compounds obtained by reactions forming a linkage containing silicon with or without sulfur, nitrogen, oxygen or carbon in the main chain of the macromolecule in which at least two but not all the silicon atoms are connected by linkages other than oxygen atoms by carbon linkages containing aromatic rings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

- H01L21/568—Temporary substrate used as encapsulation process aid

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/0401—Bonding areas specifically adapted for bump connectors, e.g. under bump metallisation [UBM]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/04105—Bonding areas formed on an encapsulation of the semiconductor or solid-state body, e.g. bonding areas on chip-scale packages

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/12105—Bump connectors formed on an encapsulation of the semiconductor or solid-state body, e.g. bumps on chip-scale packages

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/1302—Disposition

- H01L2224/13025—Disposition the bump connector being disposed on a via connection of the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

- H01L2224/131—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/13101—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of less than 400°C

- H01L2224/13111—Tin [Sn] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16135—Disposition the bump connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/16145—Disposition the bump connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L2224/19—Manufacturing methods of high density interconnect preforms

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L2224/23—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process

- H01L2224/24—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process of an individual high density interconnect connector

- H01L2224/241—Disposition

- H01L2224/24151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/24221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/24225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/24226—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation the HDI interconnect connecting to the same level of the item at which the semiconductor or solid-state body is mounted, e.g. the item being planar

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32135—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/32145—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73267—Layer and HDI connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/82—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by forming build-up interconnects at chip-level, e.g. for high density interconnects [HDI]

- H01L2224/82001—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by forming build-up interconnects at chip-level, e.g. for high density interconnects [HDI] involving a temporary auxiliary member not forming part of the bonding apparatus

- H01L2224/82005—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by forming build-up interconnects at chip-level, e.g. for high density interconnects [HDI] involving a temporary auxiliary member not forming part of the bonding apparatus being a temporary or sacrificial substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/82—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by forming build-up interconnects at chip-level, e.g. for high density interconnects [HDI]

- H01L2224/82009—Pre-treatment of the connector or the bonding area

- H01L2224/8203—Reshaping, e.g. forming vias

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/91—Methods for connecting semiconductor or solid state bodies including different methods provided for in two or more of groups H01L2224/80 - H01L2224/90

- H01L2224/92—Specific sequence of method steps

- H01L2224/921—Connecting a surface with connectors of different types

- H01L2224/9212—Sequential connecting processes

- H01L2224/92122—Sequential connecting processes the first connecting process involving a bump connector

- H01L2224/92125—Sequential connecting processes the first connecting process involving a bump connector the second connecting process involving a layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/91—Methods for connecting semiconductor or solid state bodies including different methods provided for in two or more of groups H01L2224/80 - H01L2224/90

- H01L2224/92—Specific sequence of method steps

- H01L2224/922—Connecting different surfaces of the semiconductor or solid-state body with connectors of different types

- H01L2224/9222—Sequential connecting processes

- H01L2224/92242—Sequential connecting processes the first connecting process involving a layer connector

- H01L2224/92244—Sequential connecting processes the first connecting process involving a layer connector the second connecting process involving a build-up interconnect

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/93—Batch processes

- H01L2224/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L2224/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06513—Bump or bump-like direct electrical connections between devices, e.g. flip-chip connection, solder bumps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06548—Conductive via connections through the substrate, container, or encapsulation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06555—Geometry of the stack, e.g. form of the devices, geometry to facilitate stacking

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06582—Housing for the assembly, e.g. chip scale package [CSP]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/10—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers

- H01L2225/1005—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/1011—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00 the containers being in a stacked arrangement

- H01L2225/1017—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00 the containers being in a stacked arrangement the lowermost container comprising a device support

- H01L2225/1035—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00 the containers being in a stacked arrangement the lowermost container comprising a device support the device being entirely enclosed by the support, e.g. high-density interconnect [HDI]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/10—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers

- H01L2225/1005—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/1011—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00 the containers being in a stacked arrangement

- H01L2225/1047—Details of electrical connections between containers

- H01L2225/1058—Bump or bump-like electrical connections, e.g. balls, pillars, posts

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49811—Additional leads joined to the metallisation on the insulating substrate, e.g. pins, bumps, wires, flat leads

- H01L23/49816—Spherical bumps on the substrate for external connection, e.g. ball grid arrays [BGA]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L24/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L24/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L24/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/73—Means for bonding being of different types provided for in two or more of groups H01L24/10, H01L24/18, H01L24/26, H01L24/34, H01L24/42, H01L24/50, H01L24/63, H01L24/71

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/91—Methods for connecting semiconductor or solid state bodies including different methods provided for in two or more of groups H01L24/80 - H01L24/90

- H01L24/92—Specific sequence of method steps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/35—Mechanical effects

- H01L2924/351—Thermal stress

- H01L2924/3511—Warping

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/18—Printed circuits structurally associated with non-printed electric components

- H05K1/182—Printed circuits structurally associated with non-printed electric components associated with components mounted in the printed circuit board, e.g. insert mounted components [IMC]

- H05K1/185—Components encapsulated in the insulating substrate of the printed circuit or incorporated in internal layers of a multilayer circuit

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10431—Details of mounted components

- H05K2201/10507—Involving several components

- H05K2201/10515—Stacked components

Definitions

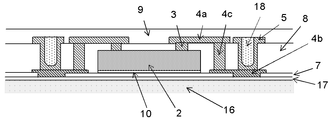

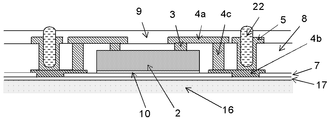

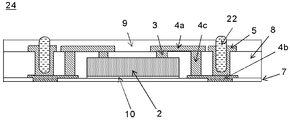

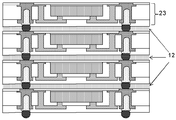

- the present invention relates to a semiconductor device, a stacked semiconductor device, a post-sealing stacked semiconductor device, and a manufacturing method thereof.

- a photosensitive insulating material or a stacked semiconductor device that can cope with an increase in substrate area in productivity improvement and can be used in a high-density mounting technology such as a chip size package, a chip scale package (CSP), or three-dimensional stacking. Therefore, development of the manufacturing method is desired.

- Patent Documents 1 and 2 show an example in which a semiconductor element is placed on a wiring board without using wire bonding, and a method of placing the semiconductor element on a board on which wiring is performed by three-dimensionally stacking the semiconductor elements.

- Patent Document 1 shows an example of a method for manufacturing a semiconductor device having a semiconductor element such as a light receiving element or a light emitting element.

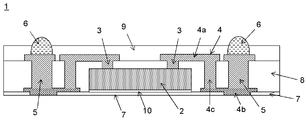

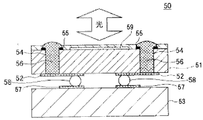

- the semiconductor device 50 includes an Al through a through electrode 56.

- the electrode pad 55 and the rewiring pattern 52 are connected, and the rewiring pattern 52 of the semiconductor device and the rewiring pattern 57 on the wiring board 53 are connected via the solder bumps 58.

- a device formation layer 59 and a plurality of Al electrode pads 55 are formed on the upper surface of the semiconductor device.

- a through hole 54 penetrating the semiconductor device is provided between the Al electrode pad 55 and the rewiring pattern 52 by dry etching, and a through electrode 56 is formed in the through hole 54 by Cu plating.

- the device formation layer 59 is disposed on the upper surface of the semiconductor device and receives light or emits light. According to this method, the semiconductor element 51 and the wiring substrate 53 are not bonded by wire bonding, but rewiring must be performed on the semiconductor device and solder bumps must be disposed. In reality, it is difficult to achieve finer wiring and higher density solder bumps.

- Patent Document 2 discloses a manufacturing method of a semiconductor device useful for three-dimensional stacking of a plurality of semiconductor elements.

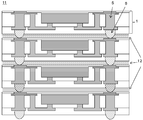

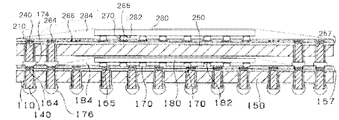

- a structure in which a semiconductor element 180 and a semiconductor element 280 are stacked is shown. Illustrated.

- Each semiconductor element to be laminated includes solder bumps (170, 270) on a substrate (110, 210) having a core substrate (150, 250), through electrodes (140, 240), and wiring layers (157, 257).

- the semiconductor element (180, 280) is bonded via the pad (182, 282) of the semiconductor element.

- the wiring layers (157, 257) include mounting pads (165, 265), connection pads (164, 264), and wiring (266).

- Patent Document 2 discloses a method of bonding and laminating substrates on which such semiconductor elements are bonded via solder bumps (174, 176).

- Patent Document 2 since the semiconductor element is bonded to the wiring board by solder bumps, as in Patent Document 1, it is extremely important to increase the density of the solder bumps accompanying the downsizing of the semiconductor elements. You will face difficulties.

- the formation of the through electrode provided on the second substrate 210 has a problem that the process is complicated and not easy.

- Patent Document 3 shows an example of a semiconductor device mounted on a wiring board, a manufacturing method thereof, or a semiconductor device in which semiconductor elements are assembled in a laminated structure, and a manufacturing method thereof.

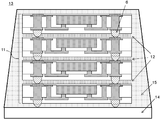

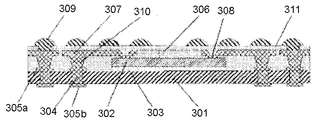

- Patent Document 3 as shown in FIG. 27, an organic substrate 301, a through via 304 that penetrates the organic substrate 301 in the thickness direction, and an external portion that is provided on both surfaces of the organic substrate 301 and is electrically connected to the through via 304.

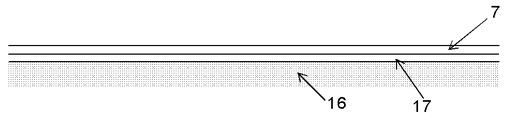

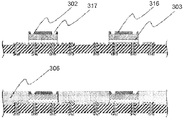

- Patent Document 3 as shown in FIG. 28, a photosensitive resin layer 316 applied to the surface layer of a semiconductor element is patterned to form an opening 317, whereby a via portion 308 formed on the semiconductor element 302 is formed. And Further, the insulating material layer 306 formed around the semiconductor element is formed by spin coating or the like.

- the resin since the resin has to be supplied twice, the process of applying the photosensitive resin layer 316 to the surface layer of the semiconductor element 302 and the process of forming the insulating material layer 306 around the semiconductor element 302, the process is complicated.

- the height of the semiconductor element 302 is important, and when the height exceeds tens of ⁇ m, the semiconductor element is overcome and a void is generated. It is actually difficult to supply the insulating material layer 306.

- the formation of the via portion 308 of the photosensitive resin layer 316 and the formation of the metal via 310 of the insulating material layer 306 are performed in separate processes, and an example in which the processing of the metal via 310 is performed by a laser or the like are shown. These processes are cumbersome and unreasonable.

- the photosensitive resin layer 316 and the insulating material layer 306 can be simultaneously supplied to the peripheral portion of the semiconductor element 302 and the circuit formation surface, there is actually no specific method illustrated, and a gap is formed around the semiconductor element. It is difficult to supply these resin layers without generating them.

- the via portion 308 of the photosensitive resin layer 316 and the metal via 310 of the insulating material layer 306 can be formed at the same time, a specific method is not described.