WO2014136375A1 - 酸化物半導体薄膜トランジスタ用基板 - Google Patents

酸化物半導体薄膜トランジスタ用基板 Download PDFInfo

- Publication number

- WO2014136375A1 WO2014136375A1 PCT/JP2014/000354 JP2014000354W WO2014136375A1 WO 2014136375 A1 WO2014136375 A1 WO 2014136375A1 JP 2014000354 W JP2014000354 W JP 2014000354W WO 2014136375 A1 WO2014136375 A1 WO 2014136375A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- oxide semiconductor

- insulating layer

- protective insulating

- layer

- substrate

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 237

- 239000000758 substrate Substances 0.000 title claims abstract description 121

- 239000010409 thin film Substances 0.000 title claims abstract description 103

- 239000000463 material Substances 0.000 claims abstract description 107

- 229910052751 metal Inorganic materials 0.000 claims abstract description 85

- 239000002184 metal Substances 0.000 claims abstract description 85

- 239000001257 hydrogen Substances 0.000 claims abstract description 62

- 229910052739 hydrogen Inorganic materials 0.000 claims abstract description 62

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 claims abstract description 60

- 150000003377 silicon compounds Chemical class 0.000 claims abstract description 18

- 230000001681 protective effect Effects 0.000 claims description 168

- 239000010408 film Substances 0.000 claims description 134

- 238000000034 method Methods 0.000 claims description 52

- 238000004519 manufacturing process Methods 0.000 claims description 36

- 229910052782 aluminium Inorganic materials 0.000 claims description 30

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 claims description 28

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 19

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 17

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 16

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 16

- 238000005268 plasma chemical vapour deposition Methods 0.000 claims description 15

- 229910052733 gallium Inorganic materials 0.000 claims description 12

- 229910052738 indium Inorganic materials 0.000 claims description 12

- 229910052725 zinc Inorganic materials 0.000 claims description 11

- 230000002829 reductive effect Effects 0.000 claims description 8

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 6

- 239000012298 atmosphere Substances 0.000 claims description 6

- 239000010703 silicon Substances 0.000 claims description 6

- 229910052710 silicon Inorganic materials 0.000 claims description 5

- 229910000838 Al alloy Inorganic materials 0.000 claims description 2

- 125000004429 atom Chemical group 0.000 abstract description 23

- 125000004435 hydrogen atom Chemical class [H]* 0.000 abstract description 2

- 239000010410 layer Substances 0.000 description 372

- 239000002585 base Substances 0.000 description 138

- 230000000052 comparative effect Effects 0.000 description 64

- 239000007789 gas Substances 0.000 description 60

- 230000015572 biosynthetic process Effects 0.000 description 43

- 238000005530 etching Methods 0.000 description 25

- 238000004544 sputter deposition Methods 0.000 description 20

- 238000011156 evaluation Methods 0.000 description 15

- 239000000243 solution Substances 0.000 description 14

- MUBZPKHOEPUJKR-UHFFFAOYSA-N Oxalic acid Chemical compound OC(=O)C(O)=O MUBZPKHOEPUJKR-UHFFFAOYSA-N 0.000 description 12

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 12

- 150000002500 ions Chemical class 0.000 description 12

- 239000000126 substance Substances 0.000 description 11

- 239000011701 zinc Substances 0.000 description 11

- 238000007743 anodising Methods 0.000 description 10

- 238000005452 bending Methods 0.000 description 10

- 230000000694 effects Effects 0.000 description 10

- 239000011521 glass Substances 0.000 description 10

- 229910045601 alloy Inorganic materials 0.000 description 9

- 239000000956 alloy Substances 0.000 description 9

- 230000004888 barrier function Effects 0.000 description 9

- 238000005259 measurement Methods 0.000 description 9

- 239000000203 mixture Substances 0.000 description 9

- 229910052750 molybdenum Inorganic materials 0.000 description 9

- 238000007872 degassing Methods 0.000 description 8

- 238000009413 insulation Methods 0.000 description 8

- 230000002411 adverse Effects 0.000 description 7

- 239000011148 porous material Substances 0.000 description 7

- 239000011347 resin Substances 0.000 description 7

- 229920005989 resin Polymers 0.000 description 7

- 238000012360 testing method Methods 0.000 description 7

- 239000011787 zinc oxide Substances 0.000 description 7

- QTBSBXVTEAMEQO-UHFFFAOYSA-N Acetic acid Chemical compound CC(O)=O QTBSBXVTEAMEQO-UHFFFAOYSA-N 0.000 description 6

- LFQSCWFLJHTTHZ-UHFFFAOYSA-N Ethanol Chemical compound CCO LFQSCWFLJHTTHZ-UHFFFAOYSA-N 0.000 description 6

- 229910001182 Mo alloy Inorganic materials 0.000 description 6

- 238000000137 annealing Methods 0.000 description 6

- 229910044991 metal oxide Inorganic materials 0.000 description 6

- 150000004706 metal oxides Chemical class 0.000 description 6

- 239000010955 niobium Substances 0.000 description 6

- 229910001220 stainless steel Inorganic materials 0.000 description 6

- 239000010936 titanium Substances 0.000 description 6

- 229910004298 SiO 2 Inorganic materials 0.000 description 5

- 239000002253 acid Substances 0.000 description 5

- 238000000576 coating method Methods 0.000 description 5

- 238000007733 ion plating Methods 0.000 description 5

- 238000000206 photolithography Methods 0.000 description 5

- 238000000053 physical method Methods 0.000 description 5

- 238000007639 printing Methods 0.000 description 5

- 239000000523 sample Substances 0.000 description 5

- 239000010935 stainless steel Substances 0.000 description 5

- 238000001771 vacuum deposition Methods 0.000 description 5

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Chemical compound O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 5

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 4

- QAOWNCQODCNURD-UHFFFAOYSA-N Sulfuric acid Chemical compound OS(O)(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-N 0.000 description 4

- 238000003917 TEM image Methods 0.000 description 4

- 238000004458 analytical method Methods 0.000 description 4

- 239000000969 carrier Substances 0.000 description 4

- -1 cesium ions Chemical class 0.000 description 4

- 230000008859 change Effects 0.000 description 4

- 150000001875 compounds Chemical class 0.000 description 4

- 239000000470 constituent Substances 0.000 description 4

- 239000010949 copper Substances 0.000 description 4

- 238000001312 dry etching Methods 0.000 description 4

- 239000011777 magnesium Substances 0.000 description 4

- 239000011733 molybdenum Substances 0.000 description 4

- 229910052758 niobium Inorganic materials 0.000 description 4

- 235000006408 oxalic acid Nutrition 0.000 description 4

- VLTRZXGMWDSKGL-UHFFFAOYSA-N perchloric acid Chemical compound OCl(=O)(=O)=O VLTRZXGMWDSKGL-UHFFFAOYSA-N 0.000 description 4

- 230000008569 process Effects 0.000 description 4

- 229910052715 tantalum Inorganic materials 0.000 description 4

- 229910052719 titanium Inorganic materials 0.000 description 4

- 229960001296 zinc oxide Drugs 0.000 description 4

- 238000002441 X-ray diffraction Methods 0.000 description 3

- 239000003513 alkali Substances 0.000 description 3

- 239000007864 aqueous solution Substances 0.000 description 3

- 229910052792 caesium Inorganic materials 0.000 description 3

- 238000005229 chemical vapour deposition Methods 0.000 description 3

- 230000008602 contraction Effects 0.000 description 3

- 238000000151 deposition Methods 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- 229910001195 gallium oxide Inorganic materials 0.000 description 3

- 239000012535 impurity Substances 0.000 description 3

- 239000012212 insulator Substances 0.000 description 3

- 230000003647 oxidation Effects 0.000 description 3

- 238000007254 oxidation reaction Methods 0.000 description 3

- 239000001301 oxygen Substances 0.000 description 3

- 229910052760 oxygen Inorganic materials 0.000 description 3

- 238000001020 plasma etching Methods 0.000 description 3

- 238000004528 spin coating Methods 0.000 description 3

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 3

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 2

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 2

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 2

- GRYLNZFGIOXLOG-UHFFFAOYSA-N Nitric acid Chemical compound O[N+]([O-])=O GRYLNZFGIOXLOG-UHFFFAOYSA-N 0.000 description 2

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- 229910000831 Steel Inorganic materials 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 2

- 150000007513 acids Chemical class 0.000 description 2

- 239000010407 anodic oxide Substances 0.000 description 2

- 238000002048 anodisation reaction Methods 0.000 description 2

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 239000004020 conductor Substances 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 239000013527 degreasing agent Substances 0.000 description 2

- 238000005237 degreasing agent Methods 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 2

- 238000004090 dissolution Methods 0.000 description 2

- 238000005868 electrolysis reaction Methods 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 229910003437 indium oxide Inorganic materials 0.000 description 2

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 2

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 2

- 238000003475 lamination Methods 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- 229910052749 magnesium Inorganic materials 0.000 description 2

- 230000000873 masking effect Effects 0.000 description 2

- 150000002739 metals Chemical class 0.000 description 2

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 2

- 229910017604 nitric acid Inorganic materials 0.000 description 2

- 230000002265 prevention Effects 0.000 description 2

- 239000011241 protective layer Substances 0.000 description 2

- 238000001552 radio frequency sputter deposition Methods 0.000 description 2

- 239000002994 raw material Substances 0.000 description 2

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 2

- VSZWPYCFIRKVQL-UHFFFAOYSA-N selanylidenegallium;selenium Chemical compound [Se].[Se]=[Ga].[Se]=[Ga] VSZWPYCFIRKVQL-UHFFFAOYSA-N 0.000 description 2

- 230000035945 sensitivity Effects 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- 239000010959 steel Substances 0.000 description 2

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 2

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 2

- 229910001887 tin oxide Inorganic materials 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 1

- 229920000049 Carbon (fiber) Polymers 0.000 description 1

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 1

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 1

- 229910007541 Zn O Inorganic materials 0.000 description 1

- GPFIZJURHXINSQ-UHFFFAOYSA-N acetic acid;nitric acid Chemical compound CC(O)=O.O[N+]([O-])=O GPFIZJURHXINSQ-UHFFFAOYSA-N 0.000 description 1

- IZQZNLBFNMTRMF-UHFFFAOYSA-N acetic acid;phosphoric acid Chemical compound CC(O)=O.OP(O)(O)=O IZQZNLBFNMTRMF-UHFFFAOYSA-N 0.000 description 1

- 230000002378 acidificating effect Effects 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- 239000011230 binding agent Substances 0.000 description 1

- 239000004917 carbon fiber Substances 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000005097 cold rolling Methods 0.000 description 1

- 238000005336 cracking Methods 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 238000002425 crystallisation Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000010292 electrical insulation Methods 0.000 description 1

- 239000003792 electrolyte Substances 0.000 description 1

- LUCJEPREDVDXKU-UHFFFAOYSA-N ethene silane Chemical compound [SiH4].C=C LUCJEPREDVDXKU-UHFFFAOYSA-N 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 239000010419 fine particle Substances 0.000 description 1

- BHEPBYXIRTUNPN-UHFFFAOYSA-N hydridophosphorus(.) (triplet) Chemical compound [PH] BHEPBYXIRTUNPN-UHFFFAOYSA-N 0.000 description 1

- 150000002431 hydrogen Chemical class 0.000 description 1

- 238000011835 investigation Methods 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 238000001755 magnetron sputter deposition Methods 0.000 description 1

- VNWKTOKETHGBQD-UHFFFAOYSA-N methane Chemical compound C VNWKTOKETHGBQD-UHFFFAOYSA-N 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 239000003960 organic solvent Substances 0.000 description 1

- ZDYUUBIMAGBMPY-UHFFFAOYSA-N oxalic acid;hydrate Chemical compound O.OC(=O)C(O)=O ZDYUUBIMAGBMPY-UHFFFAOYSA-N 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- 230000036961 partial effect Effects 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 230000035699 permeability Effects 0.000 description 1

- 239000012466 permeate Substances 0.000 description 1

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 1

- 229920000767 polyaniline Polymers 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 229920000128 polypyrrole Polymers 0.000 description 1

- 229920000123 polythiophene Polymers 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 239000013074 reference sample Substances 0.000 description 1

- 230000003014 reinforcing effect Effects 0.000 description 1

- 238000007788 roughening Methods 0.000 description 1

- 238000001179 sorption measurement Methods 0.000 description 1

- 230000003746 surface roughness Effects 0.000 description 1

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 1

- 230000000007 visual effect Effects 0.000 description 1

- 238000005406 washing Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78603—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the insulating substrate or support

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

Definitions

- the present invention relates to a substrate used for an oxide semiconductor thin film transistor that can be used in a flexible device such as a display device using liquid crystal or an organic EL element, electronic paper, or an X-ray sensor, a semiconductor device, and a manufacturing method thereof.

- Patent Document 1 a thin film transistor (TFT) using an In—Ga—Zn—O-based oxide semiconductor (InGaZnO) as an active layer can be formed at a relatively low temperature, and a resin substrate can be used. For this reason, it is described that this is a technique suitable for making a flat panel display (FPD) thinner, lighter, and flexible.

- FPD flat panel display

- the threshold voltage of the oxide semiconductor thin film transistor is greatly deviated from 0V. It is disclosed that the problem can be solved by providing a protective layer on the protective layer.

- Patent Document 1 also describes that not only a resin substrate but also a metal substrate such as aluminum whose surface is insulated may be used.

- Patent Document 2 is a patent document relating to a flexible substrate, which has higher heat resistance than a resin substrate by forming an aluminum oxide insulating layer having a porous (porous) structure by anodizing treatment on a metal surface, It is disclosed that a flexible substrate that is excellent in thermal dimensional stability and does not cause a failure such as a short circuit can be obtained.

- Patent Document 3 is a patent document relating to a resin-made flexible substrate, and a gas barrier layer containing a silicon compound is provided on the surface of the resin substrate in order to reduce the permeated gas that permeates the resin substrate.

- a gas barrier layer containing a silicon compound is provided on the surface of the resin substrate in order to reduce the permeated gas that permeates the resin substrate.

- Patent Document 1 describes that a TFT may be manufactured using a metal substrate whose surface is insulated.

- a specific example of the metal substrate and a mode and a specific example of a TFT manufactured using the metal substrate are not described.

- an oxide semiconductor thin film transistor having a configuration described in Patent Document 1 was formed on a metal substrate having a porous aluminum anodized insulating film described in Patent Document 2.

- the manufactured oxide semiconductor thin film transistor does not operate normally. Specifically, the mobility and threshold voltage of the oxide semiconductor thin film transistor did not fall within a predetermined range despite the use of a metal substrate that is expected to have high heat resistance and high gas barrier properties.

- the threshold voltage is slightly minus near zero volts, and is preferably turned off in a state where a slightly negative bias is applied.

- the present invention has been made in view of the above circumstances, a substrate for a flexible oxide semiconductor thin film transistor capable of forming an oxide semiconductor thin film transistor having high mobility and a threshold voltage within a predetermined range, and a substrate for the same.

- a flexible semiconductor device obtained by use is provided.

- the present inventors have adsorbed gas to the porous layer on the surface of the anodized aluminum substrate because the time required for evacuation is long when an aluminum substrate having a porous anodized insulating film is put into a vacuum apparatus. It was speculated that the threshold voltage of the InGaZnO-TFT was greatly changed from 0 V because the adsorbed gas was released during the production or diffused after the production.

- an anodized aluminum substrate provided with a gas barrier layer described in Patent Document 3 was prepared, and an oxide semiconductor thin film transistor was formed thereon to manufacture an oxide semiconductor device.

- a semiconductor device having desired characteristics still cannot be obtained.

- the surface roughness of the anodized aluminum substrate is large, and therefore the gas barrier layer described in Patent Document 3 has one reason that the substrate surface coverage is not sufficient. I understood. Therefore, as a result of further detailed examination of the film configuration of the substrate and the manufacturing method, the above problems have been finally solved and the present invention has been completed.

- a substrate for a flexible oxide semiconductor thin film transistor includes a base material provided with a porous layer formed on at least one surface of a metal base, and the porous layer. And a protective insulating layer containing hydrogen as a main component and containing hydrogen, and the hydrogen concentration in the protective insulating layer is 3.5 ⁇ 10 21 atoms / cm 3 or more and 3.5 ⁇ 10 It is 22 atoms / cm 3 or less, and the thickness of the protective insulating layer is 100 nm or more and 2000 nm or less.

- the silicon compound is preferably at least one selected from silicon nitride, silicon oxide, and silicon oxynitride.

- the porous layer is preferably an anodic oxide film of aluminum or aluminum alloy. Furthermore, the porous layer is preferably formed on both surfaces of the metal base.

- the protective insulating layer is preferably provided at least over the entire region where the active layer formed of an oxide semiconductor is formed.

- the active layer made of an oxide semiconductor preferably contains In, Ga, and Zn.

- the active layer made of an oxide semiconductor is preferably amorphous.

- An oxide semiconductor thin film transistor has at least a gate electrode, a gate insulating film, an active layer made of an oxide semiconductor, a source and a drain electrode.

- the oxide semiconductor thin film transistor is preferably formed over a substrate and includes at least a gate electrode, a gate insulating film, an active layer made of an oxide semiconductor, and a source and drain electrodes in this order. Furthermore, it is preferable that the gate insulating film of the oxide semiconductor thin film transistor has silicon oxide as a main component.

- the method for producing a flexible semiconductor device of the present invention provides a base material having a porous layer on at least one surface on a metal base, and a silicon compound as a main component on at least a part of the porous layer,

- a protective insulating layer having a hydrogen concentration of 3.5 ⁇ 10 21 atoms / cm 3 or more and 3.5 ⁇ 10 22 atoms / cm 3 or less and a thickness of 100 nm or more and 2000 nm or less is formed by plasma CVD (CVD: Chemical Vapor).

- CVD Chemical Vapor

- the substrate having the porous layer before forming the protective insulating layer, it is preferable to heat the substrate having the porous layer under reduced pressure from the atmosphere at 350 ° C. or higher.

- a layer that is provided on the porous layer and mainly contains a silicon compound is referred to as a protective insulating layer.

- main component means that 60% by mass or more of the material constituting the layer is composed of the specified compound.

- an “oxide semiconductor thin film transistor” means a thin film transistor having at least a gate electrode, a gate insulating film, an active layer made of an oxide semiconductor, and source / drain electrodes.

- ... is provided in direct contact with the surface of It shall include both cases where another layer exists and is provided on that layer. Further, in that case,... May be provided in the whole area of ⁇ , or may be provided only in part.

- the substrate for an oxide semiconductor thin film transistor of the present invention includes a porous layer on the surface of the metal base, and further includes a protective insulating layer containing a silicon compound as a main component and containing hydrogen on the porous layer,

- the hydrogen concentration in the protective insulating layer is 3.5 ⁇ 10 21 atoms / cm 3 or more and 3.5 ⁇ 10 22 atoms / cm 3 or less, and the thickness of the protective insulating layer is 100 nm or more and 2000 nm or less.

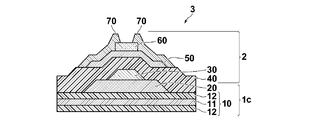

- FIG. 1 is a diagram schematically showing an embodiment of a flexible semiconductor device.

- a flexible oxide semiconductor thin film transistor substrate 1 a includes a base material 10 and a protective insulating layer 20 provided on the base material 10.

- the substrate 10 includes a metal base 11 and a porous layer 12 provided thereon.

- the porous layer 12 is located between the metal base 11 and the protective insulating layer provided thereon, and has a function of improving adhesion of the layer provided thereon by roughening the surface.

- the protective insulating layer 20 prevents the gas adsorbed on the surface of the porous layer 12 from being released into the manufacturing apparatus during the manufacturing process or adversely affecting the oxide semiconductor layer due to diffusion after the manufacturing. Have a role.

- the protective insulating layer 20 also has a role of preventing the base material 10 from being damaged by chemicals such as acid and alkali used, plasma during dry etching and sputtering film formation, and the like during the manufacturing process.

- the protective insulating layer 20 covers the porous layer 12 and has a silicon compound as a main component and a hydrogen concentration of 3.5 ⁇ 10 21 in order to ensure an adsorption gas release prevention function and a manufacturing process damage prevention function.

- a film thickness of atoms / cm 3 or more and 100 nm or more is required. Moreover, in order to ensure the flexibility of the base material 10 and to prevent the protective insulating layer 20 from cracking, the upper limit of the film thickness is 2000 nm.

- the characteristics of the oxide semiconductor thin film transistor are affected by the amount of hydrogen contained in the protective insulating layer 20.

- the protective insulating layer is formed so that the hydrogen concentration is 3.5 ⁇ 10 22 atoms / cm 3 or less.

- the protective insulating layer 20 has a hydrogen concentration set in a range of 3.5 ⁇ 10 21 atoms / cm 3 to 3.5 ⁇ 10 22 atoms / cm 3 and a thickness of 100 nm to 2000 nm.

- the active layer 50 is made of an oxide semiconductor containing at least one element selected from In, Ga, and Zn.

- Patent Document 1 it is known that the threshold voltage of an oxide semiconductor thin film transistor greatly deviates from around 0 V when the active layer is exposed to the atmosphere.

- the base material 10 having the metal base 11 reduces the intrusion of air and water vapor from the outside, the protective insulating layer 20 reduces the gas emission from the porous layer 12, and the protective insulating layer 20 itself also adversely affects the threshold voltage. Therefore, the threshold voltage of the oxide semiconductor thin film transistor is in the vicinity of 0V.

- the substrate the metal base, the porous layer, the protective insulating layer, and the oxide semiconductor thin film transistor will be described in order.

- the substrate 10 includes a metal base 11 and a porous layer 12 formed on at least one surface of the metal base.

- the base material 10 including the metal base 11 and the porous layer 12 is suitable as a flexible substrate for an oxide semiconductor thin film transistor because it has flexibility, gas barrier properties, and process resistance.

- the substrate 10 can be preferably used as long as it has at least the metal base 11 and the porous layer 12, but the metal base 11 is made of a clad material in which aluminum, stainless steel or a steel plate and an aluminum thin plate are integrated. Further, it is more preferable because the anodizing treatment of the aluminum thin plate is simplified and the durability of the base material is increased. Furthermore, in the base material obtained by anodizing the surface of the aluminum thin plate in the clad material in which both surfaces of the steel plate are sandwiched between the aluminum thin plates, the substrate caused by the difference in the thermal expansion coefficient of the material constituting the base material It is more preferable because warpage, film peeling, and the like can be suppressed.

- the substrate 10 provided with the porous layer 12 is preferably subjected to degassing treatment under reduced pressure before forming a protective insulating layer 20 described later.

- degassing treatment By carrying out the degassing treatment, the amount of gas adsorbed on the porous layer can be reduced, which is more preferable.

- a degassing process is performed by heating a substrate provided with a porous layer at 350 ° C. or higher while evacuating the chamber Can be implemented.

- the degassing treatment it is preferable to perform the degassing treatment with a film formation apparatus for forming the protective insulating layer 20 because the protective insulating layer can be provided without being exposed to the atmosphere after the degassing treatment. Further, it is more preferable to perform the treatment in the pretreatment chamber because the possibility that the released gas is taken in again when the protective insulating layer is formed can be reduced.

- This degassing treatment of the porous layer is preferably performed in as short a time as possible in order to avoid deterioration in productivity during mass production.

- the metal base 11 is at least partially made of metal and has a gas barrier property. Further, when a metal base having a thin plate shape is selected, it is preferable because flexibility can be provided while maintaining gas barrier properties.

- Examples of the material of the metal base 11 include aluminum (Al), iron (Fe), zirconium (Zr), titanium (Ti), magnesium (Mg), copper (Cu), niobium (Nb), and tantalum (Ta).

- a substrate containing at least one selected metal or an alloy of the above metals is preferred. Aluminum is preferable from the viewpoint of availability and light weight.

- the metal base 11 may be a single layer or a laminate of a plurality of layers, and the material may be a simple substance or an alloy. For example, for the purpose of adjusting expansion and contraction and warpage due to thermal expansion, it is possible to form a multilayer structure of multiple layers or use an alloy.

- the metal base refers to all portions excluding the porous layer.

- interposed into the porous of both surfaces shall be called a metal base.

- the metal base has a plurality of layers, at least one layer is made of metal.

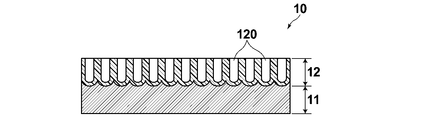

- FIG. 2 shows an example in which the metal base 11 is composed of a plurality of layers.

- FIG. 2 shows a mode in which the metal base portion 11 has a three-layer configuration, and shows a configuration in which the auxiliary base portion 11a is sandwiched between the main base portions 11b.

- a laminated structure in which the auxiliary base portion 11a and the main base portion 11b are formed one by one is also suitable.

- at least one layer may be a metal, and the other layer may be a metal or not a metal.

- the material used for the metal base may be, for example, a stainless plate or a plate made of carbon fiber.

- the auxiliary base 11a may be employed for the purpose of adjusting the expansion / contraction rate, reinforcing the base material, and reducing the gas permeability.

- a metal thin plate is preferably used, and a stainless steel material is preferably used.

- the total thickness of the metal base 11 (the sum in the case where it is composed of a plurality of layers) can be appropriately selected depending on the application.

- Porous layer 12 is provided on the metal base 11.

- the porous layer 12 is provided on at least a part of the surface of the metal base, and can insulate the surface of the metal base 11 and improve the adhesion of the layer provided thereon by the anchor effect.

- the porous layer 12 is also excellent in the flexibility of the layer itself. From the viewpoint of flexibility, the pore diameter of the porous layer 12 is preferably about 10 nm.

- the porous layer 12 is preferably provided on one entire surface of the metal base, and more preferably on the entire both surfaces of the metal base. When a porous layer is provided equally on both surfaces of the metal base, it is more preferable that the stress becomes uniform and the substrate is less likely to warp.

- FIG. 1 and 2 show a mode in which the metal base 11 and the porous layer 12 are in direct contact with each other, but another layer may be provided between them as necessary.

- an insulating layer for further improving the insulating property of the metal base surface or an underlayer for easily attaching a porous layer may be provided.

- the material of the porous layer 12 is preferably an insulating metal oxide, and more preferably an oxide containing the same metal as the metal base 11.

- the porous layer 12 may be made by any manufacturing method, and a porous layer may be formed by applying a liquid in which insulating porous fine particles and a binder are dispersed to the surface of the metal base 11. May be formed into a porous layer.

- a mode in which a part of the metal base portion is anodized to form a porous layer is preferable.

- the thickness of the porous layer 12 can be appropriately selected depending on the application, but is preferably 0.1 ⁇ m to 100 ⁇ m, more preferably 0.5 ⁇ m to 50 ⁇ m, and more preferably 5 ⁇ m to 20 ⁇ m from the viewpoint of insulation and adhesion. Is most preferred.

- a layer made of a metal oxide is provided as the porous layer 12, it is preferable that the thickness is 50 ⁇ m or less because flexibility is easily secured. Further, it is preferable to set the thickness to 0.5 ⁇ m or more because insulation is easily secured.

- the method for forming the porous layer by the anodizing treatment is not particularly limited, and any method can be used as long as the anodized porous layer can be formed on the metal surface. Below, the porous layer formed by anodic oxidation is demonstrated.

- a method for producing a porous layer using anodization has been known as a simple method capable of forming nanometer-order pores.

- this porous layer is a metal oxide, it is known to have high insulation. Specifically, when a metal substrate is immersed in an acidic or alkaline electrolyte such as sulfuric acid, oxalic acid, or phosphoric acid, and this is used as an anode, oxidation and dissolution occur on the surface of the metal substrate. Simultaneously, an oxide film having pores on its surface can be formed.

- the metal for forming the porous layer using anodization can be selected as appropriate.

- At least one metal selected from copper (Cu), niobium (Nb) and tantalum (Ta), or an alloy of the above metals is preferable.

- FIG. 4 shows a schematic diagram of a porous layer obtained by anodizing treatment.

- FIG. 4 shows an embodiment in which a porous layer 12 is provided by anodizing only one side of the metal base 11.

- the surface to be treated of the metal base 11 is uniformly changed to a metal oxide, and nanometer-order pores 120 are formed. Since the surface to be treated is uniformly treated by the anodizing treatment, high insulation can be ensured.

- the porous layer is formed by treating the surface of the original metal base, the metal base 11 and the porous layer 12 are strongly bonded and do not easily peel off.

- the next layer (not shown) is formed on the porous layer, the components of the next layer enter the pores 120 at the time of film formation, so that adhesion is secured by a so-called anchor effect.

- the metal base made of the prepared metal or alloy is washed with water, it is degreased with a metal degreasing agent to remove dirt adhering to the surface, and the degreasing agent is washed away with water washing.

- the nitric acid is washed with a 5% by mass to 20% by mass nitric acid aqueous solution, and then washed again with water.

- the metal base is anodized at a predetermined current density in a sulfuric acid bath or an oxalic acid bath to form a porous anodized film on the surface of the metal base.

- the optimum value of the current flowing during the anodic oxidation process varies depending on the metal species. However, if the current value is too small, the dissolution of the metal becomes dominant and the required porous layer may not be formed. Further, if the current value is too large, the porous layer grows rapidly, so that there is a possibility that the surface is not uniform or a part of the porous layer is easily peeled off.

- a protective insulating layer 20 is provided on at least a part of the surface of the porous layer 12.

- the protective insulating film 20 prevents the gas adsorbed on the surface of the porous layer 12 from being released into the manufacturing apparatus during the manufacturing process or adversely affecting the oxide semiconductor layer due to diffusion after the manufacturing. Have a role.

- the protective insulating layer 20 also has a role of preventing the substrate 10 from being damaged by chemicals such as acids and alkalis used in the manufacturing process, plasma during dry etching and sputtering film formation, and the like.

- FIG. 3 shows a schematic cross-sectional view of a mode in which the protective insulating layer 20 is provided on a part of the porous layer 12.

- the protective insulating layer 20 is preferably provided at least in a region where the active layer 50 of the oxide semiconductor thin film transistor 2 is formed. Moreover, it is more preferable to provide at least the formation region of the oxide semiconductor thin film transistor 2, and it is even more preferable to provide the entire porous layer. Covering only part of the surface of the porous layer with the protective insulating layer can also provide the effect of the invention, but covering the entire surface of the porous layer causes gas to be released from the porous layer during the manufacturing process.

- damage to the substrate 10 due to exposure to plasma, acid / alkali chemicals, and organic solvents during the process of manufacturing the oxide semiconductor thin film transistor is more preferable because the protective insulating layer reduces the damage.

- the protective insulating layer 20 and the base material 10 are described so as to be in direct contact with each other, but another layer may be provided therebetween.

- a planarization layer for reducing unevenness of the porous layer or a base layer for improving adhesion between the porous layer and the protective insulating layer may be provided.

- the protective insulating layer 20 is a layer mainly containing a silicon compound and containing hydrogen.

- any silicon compound may be used as the silicon compound, silicon oxide, silicon nitride, silicon oxynitride, and the like can be prevented in that the base material 10 can be prevented from being damaged during the manufacturing process of the oxide semiconductor thin film transistor 2. It is preferable to do this.

- Such silicon compounds are known to incorporate hydrogen into the film when formed by sputtering or CVD.

- the protective insulating layer is protected by having a silicon compound as a main component, a hydrogen concentration of 3.5 ⁇ 10 21 atoms / cm 3 or more, and a film thickness of 100 nm or more. It was found to function as an insulating layer.

- the function as the protective insulating layer is as follows: (1) Gas adsorbed on the surface of the porous layer 12 is released into the manufacturing apparatus during the manufacturing process, or adversely affects the oxide semiconductor layer by diffusion after manufacturing. (2) The protective insulating layer 20 is damaged during the manufacturing process due to chemicals such as acids and alkalis used in the manufacturing process, plasma during dry etching and sputter deposition, and the like. Three functions: (3) flexibility.

- the base material 10 has a porous layer, and therefore the surface irregularities are severe.

- a protective insulating layer it is necessary to cover a porous layer.

- the hydrogen concentration of the protective insulating layer is less than 3.5 ⁇ 10 21 atoms / cm 3 , the film becomes dense and hard.

- cracks are generated and coverage is poor, it is difficult to satisfactorily coat the porous layer. It was also clarified that even when the hydrogen concentration is 3.5 ⁇ 10 21 atoms / cm 3 or more, a film thickness of 100 nm is required to cover the porous layer with a rough surface.

- the applicants diffuse hydrogen contained in the protective insulating layer and enter the active layer of the oxide semiconductor thin film transistor to increase the amount of carriers in the active layer, thereby increasing the mobility and threshold voltage of the oxide semiconductor thin film transistor. Elucidated the effect. As a result of examining the protective insulating layer in detail, it was found that the threshold voltage of the oxide semiconductor thin film transistor can be controlled within a predetermined range by setting the hydrogen concentration of the protective insulating layer to 3.5 ⁇ 10 22 atoms / cm 3 or less.

- the hydrogen concentration of the protective insulating layer provided on the substrate 10 should be 3.5 ⁇ 10 21 atoms / cm 3 or more and 3.5 ⁇ 10 22 atoms / cm 3 or less.

- atoms / cm 3 means the number of atoms contained per 1 cm 3 .

- the protective insulating layer 20 is provided so as to have the above hydrogen concentration range and film thickness, if the film thickness is too thick, the protective insulating layer 20 cracks when the semiconductor device 3 is bent. As a result, the protective insulating layer 20 may be peeled off, and gas may enter to deteriorate characteristics such as mobility degradation of the oxide semiconductor thin film transistor 2. As a result of investigations by the present inventors, it has been found that, in addition to adjusting the hydrogen concentration, a protective insulating layer having a thickness of 100 nm to 2000 nm is important for solving the problem.

- the protective insulating layer is a layer containing a silicon compound as a main component, and may be a single layer or a plurality of layers of silicon compounds.

- the total film thickness of the plurality of layers is set in a range of 100 nm to 2000 nm.

- the hydrogen concentration of the protective insulating layer closest to the side where the oxide semiconductor thin film transistor is provided is at least 3.5 ⁇ 10 21 atoms / cm 3 among the plurality of protective insulating layers. 5 ⁇ 10 22 atoms / cm 3 or less.

- SIMS Secondary Ion Mass Spectroscopy

- the hydrogen concentration of the protective insulating layer can be measured by a measuring method called dynamic SIMS (D-SIMS: Dynamic-SIMS).

- D-SIMS dynamic SIMS

- the measurement result is obtained as a profile in the depth direction of the constituent element, and the absolute value of the element concentration can be obtained by referring to the profile of the measurement result of the standard substrate whose element content is known in advance.

- cesium ions are used as the primary ions to be collided. Further, since the detection sensitivity is very high, measurement is carried out under ultra-high vacuum (1.0 ⁇ 10- 5 Pa or less).

- the protective insulating layer 20 may be formed by any method, but it is easy to adjust the hydrogen concentration to a range of 3.5 ⁇ 10 21 atoms / cm 3 or more and 3.5 ⁇ 10 22 atoms / cm 3 or less, and 500 ° C. It is preferable that the following low-quality insulating film is formed by plasma CVD (also known as PE-CVD, Plasma Enhanced-CVD) from the viewpoint that a relatively high film formation rate can be realized.

- plasma CVD a reactive gas is brought into a plasma state to generate active radicals and ions, and a chemical reaction is performed in an active environment to form a desired film on an adherend.

- capacitively coupled plasma CVD CCP-CVD

- the hydrogen concentration of the protective insulating layer 20 can be adjusted by the flow rate of the source gas introduced during film formation, the temperature of the substrate on which the protective insulating layer is formed, and the annealing temperature after film formation.

- SiH 4 , NH 3, and H 2 gas are used as the source gas.

- the hydrogen concentration in the protective insulating layer can be adjusted.

- the hydrogen concentration may be adjusted by using a plurality of adjustment methods described above. From the viewpoint of hydrogen concentration reproducibility, hydrogen concentration adjustment by substrate temperature and hydrogen concentration adjustment by H 2 gas flow rate are preferable.

- the protective insulating layer is electrically insulating. Electrical insulation means that the sheet resistance value of the protective insulating layer is 1.0 ⁇ 10 7 ⁇ / ⁇ or more. 1.0 ⁇ 10 9 ⁇ / ⁇ or more is more preferable. The sheet resistance value is preferable because it does not cause a leak or a short circuit between elements of the oxide semiconductor thin film transistor.

- FIG. 1 illustrates a mode in which the oxide semiconductor thin film transistor 2 is provided directly on the protective insulating layer 20, another layer may be provided between the protective insulating layer 20 and the oxide semiconductor thin film transistor 2.

- a planarization film that improves the flatness of the substrate, an insulating layer that further improves insulation, or a base layer that improves adhesion between the oxide semiconductor thin film transistor 2 and the protective insulating layer may be provided.

- a semiconductor device refers to a device including an oxide semiconductor thin film transistor including at least a gate electrode, a gate insulating film, an active layer made of an oxide semiconductor, and source / drain electrodes on a substrate.

- An oxide semiconductor thin film transistor is easy to form on a flexible substrate because of its low film formation temperature, and is a technology that contributes to thinning, lightening, and flexibility of a display device using the oxide semiconductor thin film transistor.

- a device using such an oxide semiconductor generates carriers in the oxide semiconductor when a small amount of impurities are mixed from the outside, so that the base material is thinner than a conventional thin film transistor using silicon as an active layer.

- the impurity content of the adjacent layer is important.

- FIG. 1 includes a gate electrode 30, a gate insulating film 40, an active layer 50, an etching stopper layer 60, and a source / drain electrode 70.

- a bottom gate type oxide semiconductor thin film transistor is described in FIG. 1, a top gate type or a type having a plurality of gate electrodes are within the scope of the present invention.

- the etching stopper layer 60 is shown in FIG. 1, a configuration in which the etching stopper layer 60 is not provided when not particularly necessary is also within the scope of the present invention. Further, other configurations can be changed within the scope of the present invention.

- each part (active layer, etching stopper layer, gate electrode, gate insulating film, source / drain electrode) constituting the oxide semiconductor thin film transistor will be described with reference to FIG.

- the active layer 50 is made of an oxide semiconductor.

- Oxide semiconductors have a relatively low deposition temperature and high mobility even without a high-temperature crystallization step.

- an oxide semiconductor containing at least one element selected from In, Ga, and Zn is used as a material for the active layer 50.

- an oxide semiconductor (InGaZnO) containing In, Ga, and Zn is preferable because high mobility can be obtained.

- an oxide semiconductor carriers are generated by mixing hydrogen without depending on the composition thereof, which causes a problem that the threshold voltage deviates greatly from the vicinity of 0V. Therefore, the effects of the invention can be exhibited in an apparatus including an oxide semiconductor thin film transistor that employs a substrate having a metal base and a porous layer and uses an oxide semiconductor as an active layer.

- the active layer 50 functions as a layer that generates carriers when a voltage is applied to the gate electrode 30.

- the oxide semiconductor constituting the active layer 50 include In 2 O 3 , ZnO, Indium-Zinc-Oxide (InZnO), Gallium-Zinc-Oxide (GaZnO), Indium-Gallium-Oxide (InGaO), and Indium— Gallium-Zinc-Oxide (InGaZnO) is used.

- InGaZnO is preferable in that high mobility and low off-state current can be obtained.

- the active layer 50 is preferably composed of an amorphous oxide semiconductor that can be formed over a substrate having low heat resistance among oxide semiconductors.

- a crystalline oxide semiconductor can be selected.

- an amorphous oxide semiconductor containing at least In, Ga, or Zn is preferable.

- the amorphous oxide semiconductor used for the active layer 50 is configured as an oxide containing In, Ga, and Zn, and is amorphous with a composition in a crystalline state represented by InGaO 3 (ZnO) m (m is a natural number of 5 or less).

- An oxide semiconductor is preferable, and an amorphous oxide semiconductor represented by InGaZnO 4 is particularly preferable.

- an amorphous oxide semiconductor having this composition the electron mobility tends to increase as the electrical conductivity increases.

- the electric conductivity can be controlled by adjusting the oxygen partial pressure during film formation. Whether or not the oxide semiconductor is amorphous can be confirmed by X-ray diffraction measurement. When X-ray diffraction measurement is performed and no diffraction peak is observed, the film is amorphous.

- the active layer 50 preferably has a thickness of 1 nm to 200 nm, more preferably 2.5 nm to 100 nm.

- the method for manufacturing the active layer 50 is not particularly limited. For example, it is formed using a wet method such as a printing method or a coating method, a physical method such as a vacuum deposition method, a sputtering method, or an ion plating method, or a chemical method such as CVD or plasma CVD method.

- a forming method is appropriately selected in consideration of suitability with the material constituting the active layer 50.

- an oxide semiconductor containing In, Ga, and Zn is used as the active layer, it is preferably formed by a sputtering method from the viewpoint that a high-quality film can be formed even at a low temperature.

- oxide semiconductors particularly oxide semiconductor thin film transistors using an amorphous oxide semiconductor as an active layer

- oxide semiconductor thin film transistors using an amorphous oxide semiconductor as an active layer can obtain high mobility even when manufactured on a substrate with a rough surface. Therefore, it is suitable as a thin film transistor provided over the substrate of the present invention.

- a thin film transistor using Si as an active layer and a thin film transistor using an organic semiconductor as an active layer are sensitive to the surface shape of the substrate, and desired characteristics cannot be obtained unless the substrate surface is flat. Therefore, it is not suitable as a transistor provided over the substrate of the present invention having relatively large surface irregularities.

- the etching stopper layer 60 functions as an etching stopper that protects the active layer 50, particularly the channel region C, from being etched when the source / drain electrodes 70 are patterned.

- the etching stopper layer also serves to prevent impurities from entering the active layer from the outside.

- This etching stopper layer 60 is preferably provided so as to cover at least the channel region C of the active layer 50.

- the etching stopper layer is preferably made of silicon or gallium oxide. For example, silicon oxide, gallium oxide, silicon nitride, silicon oxynitride, and titanium oxide are preferably used.

- the etching stopper layer 60 preferably has a thickness of 10 nm to 300 nm, more preferably 50 nm to 150 nm.

- the manufacturing method of the etching stopper layer 60 is not particularly limited, but is a wet method such as a printing method and a coating method, a physical method such as a vacuum deposition method, a sputtering method, and an ion plating method, CVD, plasma CVD. It is formed using a chemical method such as a method. Among these, a forming method is appropriately selected in consideration of suitability with the material constituting the etching stopper layer 60. For example, when silicon oxide is used as the etching stopper layer 60, a plasma CVD method is preferably used.

- the gate electrode 30 is made of, for example, a metal such as Al, Mo, Cr, Ta, Ti, Au, or Ag, or an alloy thereof, an alloy such as Al—Nd, APC, tin oxide, zinc oxide, indium oxide, or indium tin oxide. It is formed using a metal oxide conductive material such as (ITO) or indium zinc oxide (InZnO), an organic conductive compound such as polyaniline, polythiophene, or polypyrrole, or a mixture thereof. As the gate electrode 30, it is preferable to use Mo, an Mo alloy (Mo-5 at% Nb or the like) or Cr.

- the thickness of the gate electrode 30 is, for example, 10 nm to 1000 nm. Further, it is more preferably 20 nm to 500 nm, and further preferably 40 nm to 100 nm.

- the formation method of the gate electrode 30 is not particularly limited. For example, it is formed using a wet method such as a printing method or a coating method, a physical method such as a vacuum deposition method, a sputtering method, or an ion plating method, or a chemical method such as CVD or plasma CVD method. Among these, a formation method is appropriately selected in consideration of suitability with the material constituting the gate electrode 30. For example, when the gate electrode 30 is formed using Mo or Mo alloy, it is preferable to use a DC sputtering method.

- the gate insulating film 40 includes an insulator such as SiO 2 , SiN x , SiON, Al 2 O 3 , Y s O 3 , Ta 2 O 5 , or HfO 2 , or a mixed crystal compound containing at least two of these compounds. Is used.

- SiO 2 is most preferably used from the viewpoint of insulation. In the oxide semiconductor thin film transistor, it is preferable to use SiO 2 for the gate insulating film because an excellent semiconductor device having both high mobility and low off-state current can be realized.

- the thickness of the gate insulating film 40 is preferably 10 nm to 10 ⁇ m.

- the gate insulating film 40 needs to be thick to some extent in order to reduce leakage current and increase voltage resistance.

- the thickness of the gate insulating film 40 is more preferably 50 nm to 1000 nm. More preferably, it is 100 nm to 500 nm.

- a high dielectric constant insulator such as HfO 2 can be used for the gate insulating film 40.

- the oxide semiconductor thin film transistor can be driven at a low voltage.

- the formation method of the gate insulating film 40 is not particularly limited. For example, it is formed using a wet method such as a printing method or a coating method, a physical method such as a vacuum deposition method, a sputtering method, or an ion plating method, or a chemical method such as CVD or plasma CVD method.

- the source electrode / drain electrode 70 is made of, for example, a metal such as Al, Mo, Cr, Ta, Ti, Au, or Ag, or an alloy thereof, an alloy such as Al—Nd, APC, tin oxide, zinc oxide, indium oxide, It is formed using a metal oxide conductive material such as indium tin oxide (ITO) or indium zinc oxide (InZnO).

- ITO indium tin oxide

- InZnO indium zinc oxide

- the ITO may be amorphous ITO or crystallized ITO.

- the source / drain electrode 70 it is preferable to use Mo or Mo alloy.

- the thickness of the source / drain electrode 70 is, for example, 10 nm to 1000 nm. A particularly preferred range is 50 nm to 400 nm.

- the formation method of the source electrode / drain electrode 70 is not particularly limited.

- the conductive film having the above composition is, for example, a printing method, a wet method such as a coating method, a physical method such as a vacuum deposition method, a sputtering method, or an ion plating method, a chemical method such as CVD or a plasma CVD method, etc. It is formed using.

- the source / drain electrode 70 is formed of Mo, Mo alloy, or amorphous ITO

- a resist pattern is formed on the Mo film, Mo alloy film, or amorphous ITO film using a photolithography method, and an acid etching solution is used. Then, the source electrode / drain electrode 70 is formed by etching the Mo film, the Mo alloy film, or the amorphous ITO film.

- the protective film may be an inorganic film such as silicon oxide or silicon nitride, an organic film such as an acrylic resin or a polyimide resin, or a laminated structure of an inorganic film / organic film.

- a pixel electrode is provided and is electrically connected to a source electrode of the oxide semiconductor thin film transistor.

- the flexible oxide semiconductor thin film transistor substrate of the present invention and the semiconductor device using the substrate have been described based on the preferred embodiments, but the present invention is not limited to the above embodiments.

- the semiconductor device of the present invention can be used for a display device using liquid crystal, an EL element, electronic paper, and an X-ray sensor.

- the display device using the semiconductor device of this embodiment can be applied to a wide range of fields including a mobile phone display, a personal digital assistant (PDA), a computer display, an automobile information display, and a TV monitor.

- PDA personal digital assistant

- the semiconductor device of the present invention will be specifically described based on examples, but the present invention is not limited thereto.

- the base material used by the Example of this invention and a comparative example is demonstrated.

- -Manufacture of substrate A- A method for manufacturing the substrate 10 having the configuration shown in FIG. 1 will be described.

- a commercially available high-purity aluminum (purity 99.99%) was rolled to prepare an aluminum thin plate having a thickness of 40 ⁇ m.

- the end face of this thin plate was covered with a masking film, then ultrasonically cleaned with ethanol, and electropolished with an acetic acid + perchloric acid solution.

- a porous layer (aluminum anodic oxide film) is formed on the surface of aluminum (both surfaces of two layers of aluminum) by constant-voltage electrolysis at 40 V in an 80 g / L oxalic acid aqueous solution. B was obtained.

- the cross-section TEM of the obtained base material B was measured, it was the structure of the base material 10 of FIG.

- the thickness of the auxiliary base portion 11a (made of stainless steel) was 50 ⁇ m

- the thickness of the main base portion 11b (made of aluminum). Both were 20 ⁇ m

- the thickness of the porous layer 12 was about 10 ⁇ m on both sides.

- the average pore size of the porous layer 12 was confirmed from the cross-sectional TEM image, it was about 10 nm.

- Example 1 Degassing treatment of base material and formation of protective insulating layer ⁇

- the base material A was put into the pretreatment chamber of the protective insulating layer deposition apparatus, and the pretreatment chamber was evacuated to 10 Pa or less, and then the base material A was heated to 450 ° C. and subjected to degassing for 30 minutes. .

- the substrate A When the temperature of the substrate A is lowered, the substrate A is moved from the pretreatment chamber to the film formation chamber, and silicon nitride is formed on the porous layer of the substrate A under the conditions described in the following film formation conditions 1-1 in Table 1. A protective insulating layer containing as a main component was formed on both sides. As a result, an oxide semiconductor thin film transistor substrate having the configuration shown in FIG. 1a was obtained (hereinafter, the substrate having this configuration is referred to as substrate A).

- the film formation temperature represents the average temperature of the base material during the formation of the protective insulating layer.

- the annealing temperature indicates the processing temperature when annealing is performed by heating after the protective insulating layer is formed. In this case, the annealing time is constant at 60 minutes.

- a support made of alkali-free glass having a thickness of 0.7 mm is separately prepared, and the substrate A and the alkali-free glass substrate are bonded (not shown) with a heat-foamable adhesive (Riva Alpha 31950E manufactured by Nitto Denko Corporation). A substrate was obtained. In this manner, the flexible substrate can be easily handled by bonding to a highly rigid support, and the influence of warpage and expansion / contraction can be reduced.

- oxide semiconductor thin-film transistor 2 of FIG. 1 the manufacturing method of the oxide semiconductor thin-film transistor 2 of FIG. 1 is demonstrated.

- the substrate A described above was used as the oxide semiconductor thin film transistor substrate 1a in FIG.

- a MoNb (Mo-5 at% Nb) film having a thickness of 50 nm is used on the surface of the substrate A (the surface of the porous layer 20) by DC magnetron sputtering using Ar gas as the sputtering gas at a substrate temperature of room temperature.

- Ar gas as the sputtering gas at a substrate temperature of room temperature.

- a resist film (TSMR-8900LB, manufactured by Tokyo Ohka Kogyo Co., Ltd.) is formed on the MoNb film by spin coating, and a predetermined pattern is exposed and developed by a photolithography method (Developer: Tokyo Ohka Kogyo Co., Ltd., NMD). -W) to form a resist pattern.

- the MoNb film at the opening of the resist film was etched using phosphoric acid-acetic acid water (Hayashi Junyaku Kogyo Co., Ltd., Mo etchant TSL). Thereafter, the resist film was peeled off (stripping solution: manufactured by Tokyo Ohka Kogyo Co., Ltd., stripping solution 104). As a result, the gate electrode 30 made of MoNb was formed on the protective insulating layer of the substrate A as shown in FIG.

- a gate insulating film 40 made of silicon oxide having a thickness of 200 nm was formed using an RF gas sputtering method so as to cover the gate electrode 30 and using Ar gas and O 2 gas as sputtering gases.

- the substrate temperature was set to room temperature

- the flow rate of Ar gas was 30 sccm

- the flow rate of O 2 gas was 4.0 sccm

- the pressure when introducing Ar gas and O 2 gas was 0.16 Pa.

- an active layer 50 made of InGaZnO having a thickness of 50 nm was formed on the gate insulating film 40 by DC sputtering without opening to the atmosphere.

- the active layer was formed using a polycrystalline sintered body having a composition of InGaZnO 4 as a target and using Ar gas and O 2 gas as sputtering gases.

- the flow rate of Ar gas was 97 sccm

- the flow rate of O 2 gas was 4.2 sccm

- the pressure when introducing Ar gas and O 2 gas was 0.37 Pa.

- an active layer was separately formed on a glass substrate, and X-ray diffraction measurement was performed. Since no diffraction peak was observed, it was confirmed that the active layer was amorphous.

- a resist film (TSMR-8900LB, manufactured by Tokyo Ohka Kogyo Co., Ltd.) is formed on the active layer 50 by spin coating, and is exposed and developed into a predetermined pattern by a photolithography method (developer: manufactured by Tokyo Ohka Kogyo Co., Ltd., NMD-W) to form a resist pattern.

- the active layer 50 at the opening of the resist film was etched using oxalic acid water (ITO-06N, manufactured by Kanto Chemical Co., Inc.). Thereafter, the resist film was peeled off (stripping solution: manufactured by Tokyo Ohka Kogyo Co., Ltd., stripping solution 104).

- an active layer 50 made of an InGaZnO film was formed on the gate insulating film 40 as shown in FIG.

- a silicon oxide film having a thickness of 100 nm was formed as an etching stopper layer 60 so as to cover the active layer 50 by RF sputtering using Ar gas and O 2 gas as sputtering gases.

- the substrate temperature was set to room temperature

- the flow rate of Ar gas was 30 sccm

- the flow rate of O 2 gas was 4.0 sccm

- the pressure when introducing Ar gas and O 2 gas was 0.16 Pa.

- a resist film manufactured by Tokyo Ohka Kogyo Co., Ltd., SMR-8900LB

- the resist film was patterned by exposing and developing (developing solution: stripping solution 104 manufactured by Tokyo Ohka Kogyo Co., Ltd.) so that the resist covering the channel region C (see FIG. 1) remains.

- developer solution stripping solution 104 manufactured by Tokyo Ohka Kogyo Co., Ltd.

- the etching stopper layer 60 exposed in the opening of the resist film was etched by dry etching using CHF 3 gas with an RIE (Reactive ion etching) apparatus. After etching, the resist film was peeled off after oxygen ashing using an RIE apparatus (stripping solution: NMD-W, manufactured by Tokyo Ohka Kogyo Co., Ltd.).

- a molybdenum film having a thickness of 200 nm was formed as the source / drain electrode 70 so as to cover the patterned active layer 50 and the etching stopper layer 60.

- the film was formed by DC sputtering using Ar gas as the sputtering gas and the substrate temperature at room temperature.

- a resist film (manufactured by Tokyo Ohka Kogyo Co., Ltd., SMR-8900LB) is formed on the molybdenum film, and a predetermined pattern is exposed and developed by a photolithography method (developer: Tokyo Ohka Kogyo Co., Ltd., NMD-W).

- a photolithography method developer: Tokyo Ohka Kogyo Co., Ltd., NMD-W

- the molybdenum film in the resist opening was etched using phosphorous nitrate acetic acid (Kanto Chemical Co., Ltd., Al etching solution). Thereafter, the resist film was peeled off (stripping solution: manufactured by Tokyo Ohka Kogyo Co., Ltd., stripping solution 104).

- stripping solution manufactured by Tokyo Ohka Kogyo Co., Ltd., stripping solution 104.

- source / drain electrodes 70 made of molybdenum were formed.

- the active layer 50 of the oxide semiconductor thin film transistor 2 manufactured in this example is covered with the etching stopper layer 60 and the source / drain electrodes 70, and has no structure exposed to the outside air. With this configuration, a semiconductor device 3 that is not affected by the outside air environment can be manufactured without forming a protective film over the oxide semiconductor thin film transistor 2.

- the obtained laminate was placed on a hot plate and heated to 200 ° C., whereby the support made of non-alkali glass and the substrate A were peeled off. Further, the substrate A (the oxide semiconductor thin film transistor provided) obtained by peeling was annealed at 250 ° C. for 1 hour.

- the manufactured oxide semiconductor thin film transistor has a channel length of 30 ⁇ m and a channel width of 90 ⁇ m.

- the semiconductor device of Example 1 was obtained by the above method.

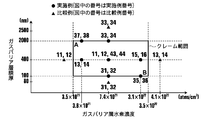

- the hydrogen concentration, mobility, threshold voltage, and flexibility of the protective insulating layer of the obtained semiconductor device were measured by the following methods, and the results are shown in Table 3.

- the hydrogen concentration of the protective insulating layer 20 provided on the substrate 10 was measured as follows.

- the obtained oxide semiconductor thin film transistor was put into a D-SIMS apparatus (AMETEK, IMS-6f), the inside of the chamber was evacuated to a high vacuum, and then the primary ion was formed in the region provided with the active layer made of the oxide semiconductor.

- the sample was set so as to be irradiated. While digging a sample by sputtering, mass analysis of secondary ions was performed. Cesium ions were used as primary ions. A profile in the depth direction of the elements composing the sample was obtained. The position of the protective insulating layer was identified from the profile of the constituent elements, and the average amount of hydrogen atoms detected in the entire protective insulating layer was defined as the hydrogen concentration of the protective insulating layer.

- the hydrogen concentration obtained by measuring a standard substrate in which the amount of doped hydrogen is known in advance under exactly the same conditions as the sample is used.

- the hydrogen concentration in the protective insulating layer was calibrated.

- the standard substrate is made of the same material as the protective insulating layer.

- the protective insulating film is mainly composed of silicon nitride (SiN)

- SiN substrate is used as the standard substrate.

- the protective insulating film is mainly composed of silicon oxide (SiO 2 )

- the standard substrate is composed of SiO 2.

- a substrate is used.

- the voltage between the drain and gate electrodes is fixed at 10 V

- the voltage between the gate and source electrodes is manipulated from ⁇ 10 V to 15 V

- the current flowing between the drain and gate electrodes is Measured (FIG. 5).

- the measurement was performed using a semiconductor parameter analyzer 4156C (manufactured by Agilent Technologies) at room temperature in a dark room. Based on this measurement result, the mobility of the oxide semiconductor thin film transistor was calculated. In this measurement region, the oxide semiconductor thin film transistor is in the saturation region, and thus the mobility was calculated using the following equation.

- Mobility ⁇ [2L / (W * Cox)] ⁇ ( ⁇ Id / ⁇ Vg) 1/2 (L: channel length of oxide semiconductor thin film transistor, W: channel width of oxide semiconductor thin film transistor, Cox: capacitance per unit area of gate insulating film, Id: drain-gate current, Vg: gate-source voltage ) Evaluation was given as follows according to the obtained mobility value.

- V on the threshold voltage of the oxide semiconductor thin film transistor

- evaluation was performed based on the following criteria. When the threshold voltage falls within the range of evaluation A, the driving voltage of the thin film transistor can be lowered, and the current when off (for example, the gate voltage is 0 V) can be reduced.

- the obtained oxide semiconductor thin film transistor was continuously bent 10 times so as to have a curvature radius of 100 mm, and then the mobility of the oxide semiconductor thin film transistor was measured. The obtained mobility was compared with the mobility before bending, and evaluation was given as follows.

- Example 2 A semiconductor device in the same manner as in Example 1 except that the base material A in Example 1 was changed to the base material B (the substrate B was degassed and the substrate provided with the protective insulating layer was referred to as the substrate B). Were manufactured and evaluated.

- Example 3 A semiconductor device was manufactured and evaluated in the same manner as in Example 1 except that the film formation condition 1-1 of the protective insulating layer in Example 1 was changed to the film formation condition 1-2.

- Example 4 A semiconductor device was manufactured and evaluated in the same manner as in Example 3 except that the base material A in Example 3 was changed to the base material B.

- Example 5 A semiconductor device was manufactured and evaluated in the same manner as in Example 1 except that the film forming condition 1-1 of the protective insulating layer in Example 1 was changed to the film forming condition 1-3.

- Example 6 A semiconductor device was manufactured and evaluated in the same manner as in Example 5 except that the base material A in Example 5 was changed to the base material B.

- Example 1 The semiconductor is the same as in Example 1 except that the porous layer and the protective insulating layer obtained by replacing the base material A of Example 1 with a glass substrate are not provided, and that the bonding with the support is not performed. A device was manufactured and evaluated.

- Example 1 A semiconductor device was manufactured and evaluated in the same manner as in Example 1 except that the film formation condition 1-1 of the protective insulating layer in Example 1 was changed to the film formation condition 1-S in Table 2 below. It was. Note that in the method of film formation condition 1-S, the annealing treatment after the formation of the protective insulating layer is not performed.

- Example 2 A semiconductor device was manufactured and evaluated in the same manner as in Example 1 except that the film formation condition 1-1 of the protective insulating layer in Example 1 was changed to the film formation condition 1-4 in Table 1.

- Comparative Example 3 A semiconductor device was manufactured and evaluated in the same manner as in Comparative Example 2 except that the base material A in Comparative Example 2 was replaced with the base material B.

- Example 4 A semiconductor device was manufactured and evaluated in the same manner as in Example 1 except that the film formation condition 1-1 of the protective insulating layer in Example 1 was changed to the film formation condition 1-5 in Table 1.