WO2010073711A1 - スパッタリング装置、スパッタリング方法及び電子デバイスの製造方法 - Google Patents

スパッタリング装置、スパッタリング方法及び電子デバイスの製造方法 Download PDFInfo

- Publication number

- WO2010073711A1 WO2010073711A1 PCT/JP2009/007278 JP2009007278W WO2010073711A1 WO 2010073711 A1 WO2010073711 A1 WO 2010073711A1 JP 2009007278 W JP2009007278 W JP 2009007278W WO 2010073711 A1 WO2010073711 A1 WO 2010073711A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- substrate

- power

- cathode

- sputtering

- magnetic field

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F41/00—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties

- H01F41/14—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties for applying magnetic films to substrates

- H01F41/18—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties for applying magnetic films to substrates by cathode sputtering

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C14/00—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material

- C23C14/22—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material characterised by the process of coating

- C23C14/34—Sputtering

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y25/00—Nanomagnetism, e.g. magnetoimpedance, anisotropic magnetoresistance, giant magnetoresistance or tunneling magnetoresistance

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C14/00—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material

- C23C14/22—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material characterised by the process of coating

- C23C14/34—Sputtering

- C23C14/3464—Sputtering using more than one target

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C14/00—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material

- C23C14/22—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material characterised by the process of coating

- C23C14/54—Controlling or regulating the coating process

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/34—Gas-filled discharge tubes operating with cathodic sputtering

- H01J37/3411—Constructional aspects of the reactor

- H01J37/3414—Targets

- H01J37/3417—Arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/34—Gas-filled discharge tubes operating with cathodic sputtering

- H01J37/3411—Constructional aspects of the reactor

- H01J37/3447—Collimators, shutters, apertures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/34—Gas-filled discharge tubes operating with cathodic sputtering

- H01J37/3411—Constructional aspects of the reactor

- H01J37/345—Magnet arrangements in particular for cathodic sputtering apparatus

- H01J37/3452—Magnet distribution

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/34—Gas-filled discharge tubes operating with cathodic sputtering

- H01J37/3411—Constructional aspects of the reactor

- H01J37/345—Magnet arrangements in particular for cathodic sputtering apparatus

- H01J37/3455—Movable magnets

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/34—Gas-filled discharge tubes operating with cathodic sputtering

- H01J37/3476—Testing and control

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N50/00—Galvanomagnetic devices

- H10N50/01—Manufacture or treatment

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N50/00—Galvanomagnetic devices

- H10N50/10—Magnetoresistive devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F10/00—Thin magnetic films, e.g. of one-domain structure

- H01F10/32—Spin-exchange-coupled multilayers, e.g. nanostructured superlattices

- H01F10/324—Exchange coupling of magnetic film pairs via a very thin non-magnetic spacer, e.g. by exchange with conduction electrons of the spacer

- H01F10/3254—Exchange coupling of magnetic film pairs via a very thin non-magnetic spacer, e.g. by exchange with conduction electrons of the spacer the spacer being semiconducting or insulating, e.g. for spin tunnel junction [STJ]

Abstract

Description

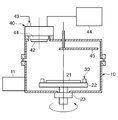

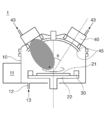

図1に示すように、本実施形態のスパッタリング装置は、処理空間を区画形成するチャンバ(反応容器)10を備えている。このチャンバ10には、その内部を所望の真空度まで真空排気可能な排気系として、ゲートバルブ等の不図示の主弁を介して排気ポンプ11が接続されている。

A=a・B・・・(2)

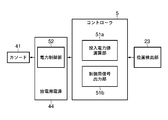

すなわち、コントローラ5は、上記式(1)に基づいて、基板21の回転角の正弦波関数として、カソード41へ投入する放電用電力を算出する。なお、θは0°≦θ≦360°である。また、Aは投入電力の振幅、αは位相角、Bは投入電力の振幅の中心値、aは投入電力の変動率である。

なお、式(3)中、Rsはシート抵抗値、Rs,maxはシート抵抗値の最大値である。

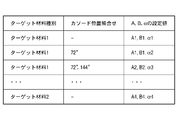

また、図7~図9に示すように、ターゲット材料に応じて制御パターンの変更を行ってもよい。これはターゲット材料によって、膜厚分布の偏りの傾向が異なってくるためである。

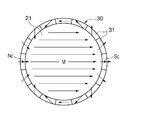

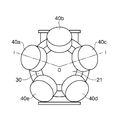

図10及び図11を参照して、第3の実施形態のスパッタリング装置について説明する。図10は本実施形態のスパッタリング装置を模式的に示す概略断面図であり、図11のi-i断面を示している。また、図11は基板ホルダとカソードユニットとの配置関係を模式的に示す平面図である。なお、以下では、第1の実施形態の図1と同じ構成には同一の符号を付して示している。

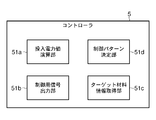

また、図13及び14に示すように、同時に放電させるカソード同士の位置関係に応じて制御パターンの変更を行ってもよい。これは他のカソードにより形成される電界、電磁界の干渉によって、膜厚分布の偏りの傾向が異なってくるためである。図13は、コントローラ5の構成を示したブロック図であり、他は第1の実施形態の図4の構成と同じである。ターゲット材料情報取得部51cは、成膜時に選択されるターゲット材料の情報をユーザの入力や予め記憶するデータなどとして取得する。カソード位置取得部51fは、同時に放電させる複数のカソード41の組合せに基づいて相互の位置関係を取得する。制御パターン決定部51dは、例えば図8に示すようなテーブルを保持しており、ターゲット材料情報取得部51cにより取得したターゲット材料情報、及び、カソード位置取得部51fにより取得したカソードの位置関係に基づき、例えば、図14に示すようなテーブルを用いて制御パターンを決定する。

高周波電源を用いた高周波スパッタリングにおいても本発明を適用できる。つまり、基板の回転位置に応じ、スパッタ率が増減するように高周波電力を制御することで、膜厚分布改善の効果を得ることができる。

なお、本発明は発明の要旨を逸脱しない範囲において種々の変更が可能である。

図17は、本発明に係るスパッタリング装置を用いたスパッタリング方法を適用して形成可能な電子部品の例として、TMR素子を示す説明図である。ここで、TMR素子とは、磁気効果素子(TMR(Tunneling Magneto resistance:トンネル磁気抵抗効果)素子)である。

Claims (19)

- 基板をその処理面の面方向に沿って回転可能に保持する基板ホルダと、

前記基板の周囲に配設され、前記基板の処理面に磁場を形成する基板磁場形成手段と、

前記基板の斜向かいの位置に配置され、放電用の電力が投入されるカソードと、

前記基板の回転位置を検出する位置検出手段と、

前記位置検出手段の検出した回転位置に応じて、前記カソードへ投入する電力を制御する電力制御手段と、を備えることを特徴とするスパッタリング装置。 - 前記基板磁場形成手段は、前記基板と同期して回転可能であって、前記基板の処理面に沿って方向性を有する磁場を形成することを特徴とする請求項1に記載のスパッタリング装置。

- 前記電力制御手段は、前記基板の特定の位置と、前記カソードとの位置関係に基づいて、電力を制御することを特徴とする請求項1に記載のスパッタリング装置。

- 前記電力制御手段は、前記基板における磁場の形成状態によりスパッタリング粒子の飛散量が多い第1の部分が前記カソードに近い位置にあるときに第1の電力を投入し、前記第1の部分よりもスパッタリング粒子の飛散量が少ない第2の部分が前記カソードに近い位置にあるときに前記第1の電力よりも高い第2の電力を投入することを特徴とする請求項3に記載のスパッタリング装置。

- 前記電力制御手段は、前記第1の部分が前記カソードに近づくに従って徐々に投入電力を減少させて前記第1の電力にすると共に、前記第2の部分が前記カソードに近づくに従って徐々に投入電力を増加させて前記第2の電力とすることを特徴とする請求項3に記載のスパッタリング装置。

- 前記電力制御手段は、電力値が前記基板の回転角の正弦波関数となるように、前記カソードに投入する電力を制御することを特徴とする請求項1に記載のスパッタリング装置

- 基板をその処理面の面方向に沿って回転させ、その処理面に磁場を形成させつつ、前記基板の斜向かいの位置に配置されるカソードに、位置検出手段の検出した前記基板の回転位置に応じて、調整した電力を投入することで、成膜を実行することを特徴とするスパッタリング方法。

- 磁性膜を成膜することを特徴とする請求項7に記載のスパッタリング方法。

- 基板をその処理面の面方向に沿って回転させ、その処理面に磁場を形成させつつ、前記基板の斜向かいの位置に配置されるカソードに、位置検出手段の検出した前記基板の回転位置に応じて、調整した電力を投入することで、スパッタリング法により成膜する成膜ステップを有することを特徴とする電子デバイスの製造方法。

- 前記基板の斜向かいに位置し、放電用の電力が夫々投入される複数の前記カソードと、

前記複数のカソードに対応して夫々設けられ、前記位置検出手段の検出した回転位置に応じて、前記対応するカソードに投入する電力を制御する複数の前記電力制御手段と、

前記複数の電力制御手段を介して、前記複数のカソードへ放電用の電力を投入し、前記基板ホルダに保持される基板に対して同時スパッタリングによる成膜を実行させる成膜制御手段と、を更に備えることを特徴とする請求項1に記載のスパッタリング装置。 - 前記電力制御手段は、前記基板の特定の位置と、前記対応するカソードとの位置関係に応じて、電力を制御することを特徴とする請求項10に記載のスパッタリング装置。

- 前記電力制御手段は、前記基板における磁場の形成状態によりスパッタリング粒子の飛散量が多い第1の部分が前記対応するカソードに近い位置にあるときに第1の電力を投入し、前記第1の部分よりもスパッタリング粒子の飛散量が少ない第2の部分が前記対応するカソードに近い位置にあるときに前記第1の電力よりも高い第2の電力を投入することを特徴とする請求項11に記載のスパッタリング装置。

- 前記電力制御手段は、前記第1の部分が前記対応するカソードに近づくに従って徐々に投入電力を減少させて前記第1の電力にすると共に、前記第2の部分が前記対応するカソードに近づくに従って徐々に投入電力を増加させて前記第2の電力とすることを特徴とする請求項11に記載のスパッタリング装置。

- 前記電力制御手段は、電力値が前記基板の回転角の正弦波関数となるように、前記対応するカソードに投入する電力を制御することを特徴とする請求項10に記載のスパッタリング装置。

- 前記電力制御手段は、スパッタリング対象となるターゲット材料に応じて設定される制御パターンで、前記対応するカソードに投入する電力を調整することを特徴とする請求項10に記載のスパッタリング装置。

- 前記電力制御手段は、前記対応するカソードと他の前記カソードとの位置関係に応じて設定される制御パターンで、前記対応するカソードに投入する電力を調整することを特徴とする請求項10に記載のスパッタリング装置。

- 基板をその処理面の面方向に沿って回転させ、その処理面に磁場を形成させつつ、前記基板の斜向かいに位置しかつ異種材料からなるターゲットが配置される複数のカソードに、位置検出手段の検出した前記基板の回転位置に応じて、調整した電力を夫々投入することで、同時スパッタリングによる成膜を実行することを特徴とするスパッタリング方法。

- 磁性膜を成膜することを特徴とする請求項17に記載のスパッタリング方法。

- 基板をその処理面の面方向に沿って回転させ、その処理面に磁場を形成させつつ、前記基板の斜向かいに位置しかつ異種材料からなるターゲットが配置される複数のカソードに、位置検出手段の検出した前記基板の回転位置に応じて、調整した電力を夫々投入することで、同時スパッタリングによる成膜を実行する成膜ステップを有することを特徴とする電子デバイスの製造方法。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020117014654A KR101272009B1 (ko) | 2008-12-26 | 2009-12-25 | 스퍼터링 장치, 스퍼터링 방법 및 전자 디바이스의 제조 방법 |

| KR1020137002927A KR101271843B1 (ko) | 2008-12-26 | 2009-12-25 | 스퍼터링 장치, 스퍼터링 방법 및 전자 디바이스의 제조 방법 |

| CN200980147190.7A CN102227514B (zh) | 2008-12-26 | 2009-12-25 | 溅射装置、溅射方法和电子器件制造方法 |

| EP09834517.6A EP2390380B1 (en) | 2008-12-26 | 2009-12-25 | Sputtering equipment, sputtering method and method for manufacturing an electronic device |

| JP2010522884A JP4739464B2 (ja) | 2008-12-26 | 2009-12-25 | スパッタリング装置、スパッタリング方法及び電子デバイスの製造方法 |

| US13/104,472 US8906208B2 (en) | 2008-12-26 | 2011-05-10 | Sputtering apparatus, sputtering method, and electronic device manufacturing method |

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008333066 | 2008-12-26 | ||

| JP2008-333066 | 2008-12-26 | ||

| JP2008333480 | 2008-12-26 | ||

| JP2008-333480 | 2008-12-26 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| US13/104,472 Continuation US8906208B2 (en) | 2008-12-26 | 2011-05-10 | Sputtering apparatus, sputtering method, and electronic device manufacturing method |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| WO2010073711A1 true WO2010073711A1 (ja) | 2010-07-01 |

Family

ID=42287344

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| PCT/JP2009/007278 WO2010073711A1 (ja) | 2008-12-26 | 2009-12-25 | スパッタリング装置、スパッタリング方法及び電子デバイスの製造方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US8906208B2 (ja) |

| EP (1) | EP2390380B1 (ja) |

| JP (2) | JP4739464B2 (ja) |

| KR (2) | KR101271843B1 (ja) |

| CN (1) | CN102227514B (ja) |

| WO (1) | WO2010073711A1 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2019111631A1 (ja) * | 2017-12-05 | 2019-06-13 | 昭和電工株式会社 | 磁気センサの製造方法及び磁気センサ集合体 |

| JP2019201193A (ja) * | 2018-05-10 | 2019-11-21 | 株式会社アルバック | 抵抗体膜の製造方法及び抵抗体膜 |

Families Citing this family (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103046008B (zh) * | 2008-09-30 | 2015-04-01 | 佳能安内华股份有限公司 | 溅射方法 |

| WO2010073711A1 (ja) * | 2008-12-26 | 2010-07-01 | キヤノンアネルバ株式会社 | スパッタリング装置、スパッタリング方法及び電子デバイスの製造方法 |

| WO2013094171A1 (ja) * | 2011-12-22 | 2013-06-27 | キヤノンアネルバ株式会社 | SrRuO3膜の成膜方法 |

| JP5806967B2 (ja) * | 2012-03-30 | 2015-11-10 | 株式会社クボタ | ディーゼルエンジンの排気処理装置 |

| CN103374705B (zh) * | 2012-04-11 | 2015-12-02 | 北京北方微电子基地设备工艺研究中心有限责任公司 | 一种磁控溅射装置 |

| US20130327634A1 (en) * | 2012-06-08 | 2013-12-12 | Chang-Beom Eom | Misaligned sputtering systems for the deposition of complex oxide thin films |

| CN104641016A (zh) * | 2012-06-18 | 2015-05-20 | 欧瑞康先进科技股份公司 | 用于定向材料沉积的pvd设备、方法和工件 |

| JP2014046231A (ja) * | 2012-08-29 | 2014-03-17 | Hitachi Chemical Co Ltd | カーボンナノチューブ合成用触媒の製造方法 |

| KR101375878B1 (ko) * | 2012-09-27 | 2014-03-17 | 한국생산기술연구원 | 미세패턴 형성 방법 |

| US10048157B2 (en) * | 2013-07-11 | 2018-08-14 | Android Industries Llc | Balancing device, uniformity device and methods for utilizing the same |

| CN103487311B (zh) * | 2013-09-11 | 2016-04-13 | 广东省东莞市质量监督检测中心 | 一种湿浆样品置放装置及其控制方法 |

| US10196734B2 (en) * | 2014-03-25 | 2019-02-05 | Iowa State University Research Foundation, Inc. | Nanotwinned silver alloy film with controlled architecture |

| CN105112864B (zh) * | 2015-08-13 | 2019-03-05 | 江苏时代全芯存储科技有限公司 | 镀膜装置 |

| WO2017098537A1 (ja) * | 2015-12-07 | 2017-06-15 | キヤノンアネルバ株式会社 | 磁気抵抗効果素子の製造方法および装置 |

| US10431440B2 (en) * | 2015-12-20 | 2019-10-01 | Applied Materials, Inc. | Methods and apparatus for processing a substrate |

| DE102019200761A1 (de) * | 2019-01-22 | 2020-07-23 | TRUMPF Hüttinger GmbH + Co. KG | Verfahren zur Kompensation von Prozessschwankungen eines Plasmaprozesses und Regler für einen Leistungsgenerator zur Versorgung eines Plasmaprozesses |

| TW202104628A (zh) | 2019-04-19 | 2021-02-01 | 美商應用材料股份有限公司 | 用於控制pvd沉積均勻性的系統及方法 |

| US11557473B2 (en) * | 2019-04-19 | 2023-01-17 | Applied Materials, Inc. | System and method to control PVD deposition uniformity |

| EP3987079A4 (en) | 2019-06-24 | 2023-03-01 | TRUMPF Huettinger Sp. Z o. o. | PROCEDURE FOR ADJUSTING THE POWER OUTPUT OF A POWER SUPPLY FOR A PLASMA, PLASMA DEVICE AND POWER SUPPLY |

| KR20210006725A (ko) * | 2019-07-09 | 2021-01-19 | 삼성전자주식회사 | 스퍼터링 장치 및 이를 이용한 반도체 장치의 제조 방법 |

| CN110344013A (zh) * | 2019-08-19 | 2019-10-18 | 北京北方华创微电子装备有限公司 | 溅射方法 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS61250163A (ja) * | 1985-04-26 | 1986-11-07 | Nippon Telegr & Teleph Corp <Ntt> | 多層薄膜の製造方法および装置 |

| JPH06207270A (ja) * | 1993-01-07 | 1994-07-26 | Hitachi Ltd | 磁性膜形成装置 |

| JPH0969460A (ja) * | 1995-09-01 | 1997-03-11 | Kao Corp | 磁気記録媒体の製造方法 |

| JP2000265263A (ja) | 1999-01-12 | 2000-09-26 | Anelva Corp | スパッタリング方法及び装置 |

| JP2002069631A (ja) * | 2000-08-24 | 2002-03-08 | Hitachi Ltd | スパッタ方法及びその装置 |

| JP2002167661A (ja) * | 2000-11-30 | 2002-06-11 | Anelva Corp | 磁性多層膜作製装置 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60207270A (ja) * | 1984-03-30 | 1985-10-18 | 日本航空電子工業株式会社 | コネクタ |

| US4607903A (en) | 1984-03-30 | 1986-08-26 | Japan Aviation Electronics Industry Limited | Connector assembly |

| US6290824B1 (en) | 1992-10-28 | 2001-09-18 | Hitachi, Ltd. | Magnetic film forming system |

| US6491802B2 (en) | 1992-10-28 | 2002-12-10 | Hitachi, Ltd. | Magnetic film forming system |

| JP4205294B2 (ja) * | 2000-08-01 | 2009-01-07 | キヤノンアネルバ株式会社 | 基板処理装置及び方法 |

| JP3505135B2 (ja) * | 2000-08-30 | 2004-03-08 | 株式会社日鉱マテリアルズ | 銅の表面処理方法 |

| US7381661B2 (en) * | 2002-10-15 | 2008-06-03 | Oc Oerlikon Balzers Ag | Method for the production of a substrate with a magnetron sputter coating and unit for the same |

| US20050103620A1 (en) * | 2003-11-19 | 2005-05-19 | Zond, Inc. | Plasma source with segmented magnetron cathode |

| JP4494047B2 (ja) * | 2004-03-12 | 2010-06-30 | キヤノンアネルバ株式会社 | 多元スパッタ成膜装置の二重シャッタ制御方法 |

| JP4473323B2 (ja) * | 2007-04-26 | 2010-06-02 | キヤノンアネルバ株式会社 | スパッタリング成膜方法、電子デバイスの製造方法及びスパッタリング装置 |

| JP5209717B2 (ja) | 2008-06-25 | 2013-06-12 | キヤノンアネルバ株式会社 | スパッタリング装置及びその制御用プログラムを記録した記録媒体 |

| CN103046008B (zh) | 2008-09-30 | 2015-04-01 | 佳能安内华股份有限公司 | 溅射方法 |

| WO2010073711A1 (ja) * | 2008-12-26 | 2010-07-01 | キヤノンアネルバ株式会社 | スパッタリング装置、スパッタリング方法及び電子デバイスの製造方法 |

-

2009

- 2009-12-25 WO PCT/JP2009/007278 patent/WO2010073711A1/ja active Application Filing

- 2009-12-25 CN CN200980147190.7A patent/CN102227514B/zh active Active

- 2009-12-25 EP EP09834517.6A patent/EP2390380B1/en active Active

- 2009-12-25 JP JP2010522884A patent/JP4739464B2/ja active Active

- 2009-12-25 KR KR1020137002927A patent/KR101271843B1/ko active IP Right Grant

- 2009-12-25 KR KR1020117014654A patent/KR101272009B1/ko active IP Right Grant

-

2011

- 2011-04-25 JP JP2011097548A patent/JP5587822B2/ja active Active

- 2011-05-10 US US13/104,472 patent/US8906208B2/en active Active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS61250163A (ja) * | 1985-04-26 | 1986-11-07 | Nippon Telegr & Teleph Corp <Ntt> | 多層薄膜の製造方法および装置 |

| JPH06207270A (ja) * | 1993-01-07 | 1994-07-26 | Hitachi Ltd | 磁性膜形成装置 |

| JPH0969460A (ja) * | 1995-09-01 | 1997-03-11 | Kao Corp | 磁気記録媒体の製造方法 |

| JP2000265263A (ja) | 1999-01-12 | 2000-09-26 | Anelva Corp | スパッタリング方法及び装置 |

| JP2002069631A (ja) * | 2000-08-24 | 2002-03-08 | Hitachi Ltd | スパッタ方法及びその装置 |

| JP2002167661A (ja) * | 2000-11-30 | 2002-06-11 | Anelva Corp | 磁性多層膜作製装置 |

Non-Patent Citations (1)

| Title |

|---|

| See also references of EP2390380A4 |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2019111631A1 (ja) * | 2017-12-05 | 2019-06-13 | 昭和電工株式会社 | 磁気センサの製造方法及び磁気センサ集合体 |

| JP2019102681A (ja) * | 2017-12-05 | 2019-06-24 | 昭和電工株式会社 | 磁気センサの製造方法及び磁気センサ集合体 |

| JP2019201193A (ja) * | 2018-05-10 | 2019-11-21 | 株式会社アルバック | 抵抗体膜の製造方法及び抵抗体膜 |

| JP7120857B2 (ja) | 2018-05-10 | 2022-08-17 | 株式会社アルバック | 抵抗体膜の製造方法及び抵抗体膜 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20110089878A (ko) | 2011-08-09 |

| US20110209986A1 (en) | 2011-09-01 |

| US8906208B2 (en) | 2014-12-09 |

| EP2390380B1 (en) | 2016-03-09 |

| KR101272009B1 (ko) | 2013-06-05 |

| KR101271843B1 (ko) | 2013-06-07 |

| CN102227514B (zh) | 2014-08-20 |

| CN102227514A (zh) | 2011-10-26 |

| JP2011149104A (ja) | 2011-08-04 |

| JPWO2010073711A1 (ja) | 2012-06-14 |

| JP5587822B2 (ja) | 2014-09-10 |

| EP2390380A1 (en) | 2011-11-30 |

| EP2390380A4 (en) | 2014-01-08 |

| KR20130019035A (ko) | 2013-02-25 |

| JP4739464B2 (ja) | 2011-08-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4739464B2 (ja) | スパッタリング装置、スパッタリング方法及び電子デバイスの製造方法 | |

| JP5192549B2 (ja) | スパッタリング装置及びスパッタリング方法 | |

| US10636634B2 (en) | Sputtering apparatus, film deposition method, and control device | |

| JP4727764B2 (ja) | プラズマ処理装置、磁気抵抗素子の製造装置、磁性薄膜の成膜方法及び成膜制御プログラム | |

| US7955480B2 (en) | Sputtering apparatus and film deposition method | |

| US20130048494A1 (en) | Sputtering device | |

| EP1994196A1 (en) | Sputter deposition system and methods of use | |

| CN110177898A (zh) | 溅射装置及成膜方法 | |

| JP2006233240A (ja) | スパッタ用カソード及びスパッタ装置 | |

| JP4974582B2 (ja) | 成膜装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| WWE | Wipo information: entry into national phase |

Ref document number: 200980147190.7 Country of ref document: CN |

|

| WWE | Wipo information: entry into national phase |

Ref document number: 2010522884 Country of ref document: JP |

|

| 121 | Ep: the epo has been informed by wipo that ep was designated in this application |

Ref document number: 09834517 Country of ref document: EP Kind code of ref document: A1 |

|

| WWE | Wipo information: entry into national phase |

Ref document number: 2009834517 Country of ref document: EP |

|

| ENP | Entry into the national phase |

Ref document number: 20117014654 Country of ref document: KR Kind code of ref document: A |

|

| NENP | Non-entry into the national phase |

Ref country code: DE |