KR900003875B1 - 소거가능 프로그래머블 판독전용 메모리장치 및 그의 제조방법 - Google Patents

소거가능 프로그래머블 판독전용 메모리장치 및 그의 제조방법 Download PDFInfo

- Publication number

- KR900003875B1 KR900003875B1 KR1019870000077A KR870000077A KR900003875B1 KR 900003875 B1 KR900003875 B1 KR 900003875B1 KR 1019870000077 A KR1019870000077 A KR 1019870000077A KR 870000077 A KR870000077 A KR 870000077A KR 900003875 B1 KR900003875 B1 KR 900003875B1

- Authority

- KR

- South Korea

- Prior art keywords

- gate

- substrate

- floating gate

- memory cell

- insulating film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

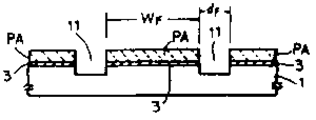

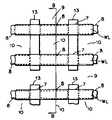

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/10—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the top-view layout

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/30—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B69/00—Erasable-and-programmable ROM [EPROM] devices not provided for in groups H10B41/00 - H10B63/00, e.g. ultraviolet erasable-and-programmable ROM [UVEPROM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/68—Floating-gate IGFETs

- H10D30/681—Floating-gate IGFETs having only two programming levels

- H10D30/684—Floating-gate IGFETs having only two programming levels programmed by hot carrier injection

- H10D30/685—Floating-gate IGFETs having only two programming levels programmed by hot carrier injection from the channel

Landscapes

- Non-Volatile Memory (AREA)

- Semiconductor Memories (AREA)

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP61-005310 | 1986-01-14 | ||

| JP61005310A JPS62163376A (ja) | 1986-01-14 | 1986-01-14 | 半導体記憶装置の製造方法 |

| JP61-5310 | 1986-01-14 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR870007571A KR870007571A (ko) | 1987-08-20 |

| KR900003875B1 true KR900003875B1 (ko) | 1990-06-02 |

Family

ID=11607698

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019870000077A Expired KR900003875B1 (ko) | 1986-01-14 | 1987-01-08 | 소거가능 프로그래머블 판독전용 메모리장치 및 그의 제조방법 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US4734887A (enExample) |

| EP (1) | EP0236676B1 (enExample) |

| JP (1) | JPS62163376A (enExample) |

| KR (1) | KR900003875B1 (enExample) |

| DE (1) | DE3780484T2 (enExample) |

Families Citing this family (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2616576B1 (fr) * | 1987-06-12 | 1992-09-18 | Commissariat Energie Atomique | Cellule de memoire eprom et son procede de fabrication |

| JP2618946B2 (ja) * | 1987-12-28 | 1997-06-11 | 株式会社東芝 | 不揮発性半導体メモリ装置の製造方法 |

| US5143860A (en) * | 1987-12-23 | 1992-09-01 | Texas Instruments Incorporated | High density EPROM fabricaiton method having sidewall floating gates |

| JP2780715B2 (ja) * | 1988-03-04 | 1998-07-30 | ソニー株式会社 | 半導体装置の製造方法 |

| US5268318A (en) * | 1988-06-08 | 1993-12-07 | Eliyahou Harari | Highly compact EPROM and flash EEPROM devices |

| FR2633455B1 (fr) * | 1988-06-24 | 1990-08-24 | Thomson Csf | Matrice photosensible a transfert de trame d.t.c., avec un systeme antieblouissement vertical, et procede de fabrication d'une telle matrice |

| JPH0265175A (ja) * | 1988-08-31 | 1990-03-05 | Toshiba Corp | 半導体不揮発性記憶装置及びその製造方法 |

| US5296396A (en) * | 1988-12-05 | 1994-03-22 | Sgs-Thomson Microelectronics S.R.L. | Matrix of EPROM memory cells with a tablecloth structure having an improved capacitative ratio and a process for its manufacture |

| IT1227989B (it) * | 1988-12-05 | 1991-05-20 | Sgs Thomson Microelectronics | Matrice di celle di memoria eprom con struttura a tovaglia con migliorato rapporto capacitivo e processo per la sua fabbricazione |

| JPH0821638B2 (ja) * | 1989-12-15 | 1996-03-04 | 株式会社東芝 | 不揮発性半導体記憶装置およびその製造方法 |

| JPH088316B2 (ja) * | 1990-01-31 | 1996-01-29 | 株式会社東芝 | 紫外線消去型不揮発性半導体メモリ装置 |

| JPH088317B2 (ja) * | 1990-04-24 | 1996-01-29 | 株式会社東芝 | 半導体記憶装置及びその製造方法 |

| US5057447A (en) * | 1990-07-09 | 1991-10-15 | Texas Instruments Incorporated | Silicide/metal floating gate process |

| KR970000533B1 (ko) * | 1990-12-20 | 1997-01-13 | 후지쓰 가부시끼가이샤 | Eprom 및 그 제조방법 |

| DE69226687T2 (de) * | 1991-10-16 | 1999-04-15 | Sony Corp., Tokio/Tokyo | Verfahren zur Herstellung einer SOI-Struktur mit einem DRAM |

| JP3160966B2 (ja) * | 1991-10-16 | 2001-04-25 | ソニー株式会社 | Soi基板の製造方法 |

| KR100215840B1 (ko) * | 1996-02-28 | 1999-08-16 | 구본준 | 반도체 메모리셀 구조 및 제조방법 |

| JP3583579B2 (ja) | 1997-06-06 | 2004-11-04 | 株式会社東芝 | 不揮発性半導体記憶装置およびその製造方法 |

| DE19926500C2 (de) * | 1999-06-10 | 2001-09-20 | Infineon Technologies Ag | Nichtflüchtige Halbleiter-Speicherzelle mit einer eine hohe relative Dielektrizitätskonstante aufweisenden dielektrischen Schicht und Verfahren zu deren Herstellung |

| US6744094B2 (en) | 2001-08-24 | 2004-06-01 | Micron Technology Inc. | Floating gate transistor with horizontal gate layers stacked next to vertical body |

| US7288821B2 (en) * | 2005-04-08 | 2007-10-30 | International Business Machines Corporation | Structure and method of three dimensional hybrid orientation technology |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4258466A (en) * | 1978-11-02 | 1981-03-31 | Texas Instruments Incorporated | High density electrically programmable ROM |

| JPS5929155B2 (ja) * | 1979-11-12 | 1984-07-18 | 富士通株式会社 | 半導体記憶装置 |

| US4493057A (en) * | 1980-01-07 | 1985-01-08 | Texas Instruments Incorporated | Method of making high density semiconductor device such as floating gate electrically programmable ROM or the like |

| JPS5742169A (en) * | 1980-08-26 | 1982-03-09 | Toshiba Corp | Production of semiconductor device |

| JPS59111370A (ja) * | 1982-12-16 | 1984-06-27 | Seiko Instr & Electronics Ltd | 不揮発性半導体メモリ |

| JPS59178773A (ja) * | 1983-03-30 | 1984-10-11 | Toshiba Corp | 半導体装置の製造方法 |

| US4618876A (en) * | 1984-07-23 | 1986-10-21 | Rca Corporation | Electrically alterable, nonvolatile floating gate memory device |

| JPH0722195B2 (ja) * | 1985-08-20 | 1995-03-08 | 日本電気株式会社 | 不揮発性半導体記憶装置の製造方法 |

-

1986

- 1986-01-14 JP JP61005310A patent/JPS62163376A/ja active Granted

- 1986-12-15 US US06/941,439 patent/US4734887A/en not_active Expired - Fee Related

-

1987

- 1987-01-08 KR KR1019870000077A patent/KR900003875B1/ko not_active Expired

- 1987-01-13 DE DE8787100310T patent/DE3780484T2/de not_active Expired - Fee Related

- 1987-01-13 EP EP87100310A patent/EP0236676B1/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| EP0236676B1 (en) | 1992-07-22 |

| DE3780484D1 (de) | 1992-08-27 |

| KR870007571A (ko) | 1987-08-20 |

| EP0236676A3 (en) | 1989-11-02 |

| EP0236676A2 (en) | 1987-09-16 |

| JPS62163376A (ja) | 1987-07-20 |

| JPH0560671B2 (enExample) | 1993-09-02 |

| US4734887A (en) | 1988-03-29 |

| DE3780484T2 (de) | 1993-01-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR900003875B1 (ko) | 소거가능 프로그래머블 판독전용 메모리장치 및 그의 제조방법 | |

| KR920002091B1 (ko) | 불휘발성 반도체기억장치 및 그 제조방법 | |

| US5168334A (en) | Non-volatile semiconductor memory | |

| US4103415A (en) | Insulated-gate field-effect transistor with self-aligned contact hole to source or drain | |

| US4750024A (en) | Offset floating gate EPROM memory cell | |

| US5017515A (en) | Process for minimizing lateral distance between elements in an integrated circuit by using sidewall spacers | |

| EP0190928A2 (en) | Integrated MOS transistor and method of manufacturing it | |

| KR100673673B1 (ko) | Dram 셀 장치 및 그 제조 방법 | |

| JPH10511511A (ja) | メモリアレーのための自己整列型分離及び平坦化方法 | |

| US4053349A (en) | Method for forming a narrow gap | |

| JPS6249750B2 (enExample) | ||

| KR0146401B1 (ko) | 스택 게이트 구조를 갖고 있는 반도체 집적 회로 장치의 제조 방법 | |

| US4169270A (en) | Insulated-gate field-effect transistor with self-aligned contact hole to source or drain | |

| US4455742A (en) | Method of making self-aligned memory MNOS-transistor | |

| KR100231962B1 (ko) | 비트라인 사이의 리치스루우 및 비트라인의 인터럽션에 대한 면역성을 제공하는 고밀도로 적층된 분할 게이트 eprom 셀 | |

| GB2080024A (en) | Semiconductor Device and Method for Fabricating the Same | |

| US5340768A (en) | Method of fabricating self-aligned field-plate isolation between control electrodes | |

| US4357747A (en) | Method for producing a semiconductor device having an insulated gate type field effect transistor | |

| KR980012468A (ko) | 버드 비크의 형태 없이 반도체 장치를 제조하기 위한 방법 | |

| US5227319A (en) | Method of manufacturing a semiconductor device | |

| JPH1012750A (ja) | 不揮発性半導体記憶装置の製造方法 | |

| JPS60113460A (ja) | ダイナミックメモリ素子の製造方法 | |

| JP2560517B2 (ja) | 浮遊ゲート型半導体記憶装置およびその製造方法 | |

| US5714787A (en) | Semiconductor device with a reduced element isolation region | |

| KR0135690B1 (ko) | 반도체소자의 콘택 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| PA0109 | Patent application |

St.27 status event code: A-0-1-A10-A12-nap-PA0109 |

|

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| R17-X000 | Change to representative recorded |

St.27 status event code: A-3-3-R10-R17-oth-X000 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| G160 | Decision to publish patent application | ||

| PG1605 | Publication of application before grant of patent |

St.27 status event code: A-2-2-Q10-Q13-nap-PG1605 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U11-oth-PR1002 Fee payment year number: 1 |

|

| FPAY | Annual fee payment |

Payment date: 19930512 Year of fee payment: 4 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 4 |

|

| LAPS | Lapse due to unpaid annual fee | ||

| PC1903 | Unpaid annual fee |

St.27 status event code: A-4-4-U10-U13-oth-PC1903 Not in force date: 19940603 Payment event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE |

|

| PC1903 | Unpaid annual fee |

St.27 status event code: N-4-6-H10-H13-oth-PC1903 Ip right cessation event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE Not in force date: 19940603 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R13-asn-PN2301 St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R13-asn-PN2301 St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R13-asn-PN2301 St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |