KR20180098442A - 화소 및 이를 가지는 유기전계발광 표시장치 - Google Patents

화소 및 이를 가지는 유기전계발광 표시장치 Download PDFInfo

- Publication number

- KR20180098442A KR20180098442A KR1020170024876A KR20170024876A KR20180098442A KR 20180098442 A KR20180098442 A KR 20180098442A KR 1020170024876 A KR1020170024876 A KR 1020170024876A KR 20170024876 A KR20170024876 A KR 20170024876A KR 20180098442 A KR20180098442 A KR 20180098442A

- Authority

- KR

- South Korea

- Prior art keywords

- transistor

- turned

- supplied

- auxiliary

- node

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

-

- H01L27/1225—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/121—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements

- H10K59/1213—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements the pixel elements being TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/121—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements

- H10K59/1216—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements the pixel elements being capacitors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/131—Interconnections, e.g. wiring lines or terminals

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2230/00—Details of flat display driving waveforms

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0404—Matrix technologies

- G09G2300/0417—Special arrangements specific to the use of low carrier mobility technology

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0421—Structural details of the set of electrodes

- G09G2300/0426—Layout of electrodes and connections

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0814—Several active elements per pixel in active matrix panels used for selection purposes, e.g. logical AND for partial update

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0819—Several active elements per pixel in active matrix panels used for counteracting undesired variations, e.g. feedback or autozeroing

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0861—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor with additional control of the display period without amending the charge stored in a pixel memory, e.g. by means of additional select electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0209—Crosstalk reduction, i.e. to reduce direct or indirect influences of signals directed to a certain pixel of the displayed image on other pixels of said image, inclusive of influences affecting pixels in different frames or fields or sub-images which constitute a same image, e.g. left and right images of a stereoscopic display

- G09G2320/0214—Crosstalk reduction, i.e. to reduce direct or indirect influences of signals directed to a certain pixel of the displayed image on other pixels of said image, inclusive of influences affecting pixels in different frames or fields or sub-images which constitute a same image, e.g. left and right images of a stereoscopic display with crosstalk due to leakage current of pixel switch in active matrix panels

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0219—Reducing feedthrough effects in active matrix panels, i.e. voltage changes on the scan electrode influencing the pixel voltage due to capacitive coupling

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0233—Improving the luminance or brightness uniformity across the screen

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/02—Details of power systems and of start or stop of display operation

- G09G2330/028—Generation of voltages supplied to electrode drivers in a matrix display other than LCD

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6741—Group IV materials, e.g. germanium or silicon carbide

- H10D30/6743—Silicon

- H10D30/6745—Polycrystalline or microcrystalline silicon

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6755—Oxide semiconductors, e.g. zinc oxide, copper aluminium oxide or cadmium stannate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/421—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer

- H10D86/423—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer comprising semiconductor materials not belonging to the Group IV, e.g. InGaZnO

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/441—Interconnections, e.g. scanning lines

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/481—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs integrated with passive devices, e.g. auxiliary capacitors

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Geometry (AREA)

- Electroluminescent Light Sources (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Control Of El Displays (AREA)

Abstract

본 발명의 실시예에 의한 화소는 유기 발광 다이오드와; 제 1노드의 전압에 대응하여 제 1구동전원으로부터 상기 유기 발광 다이오드를 경유하여 제 2구동전원으로 공급되는 전류량을 제어하기 위한 제 1트랜지스터와; 상기 제 1노드와 상기 제 1구동전원 사이에 접속되는 스토리지 커패시터와; 데이터선과 상기 제 1노드 사이에 접속되며, 제 1주사선으로 주사신호가 공급될 때 턴-온되는 제 2트랜지스터와; 상기 제 2트랜지스터와 상기 데이터선 사이에 접속되며, 제 2주사선으로 주사신호가 공급될 때 턴-온되는 보조 트랜지스터를 구비하며; 상기 제 2트랜지스터 및 상기 보조 트랜지스터는 턴-온기간이 중첩되며, 상기 제 2트랜지스터는 상기 보조 트랜지스터보다 먼저 턴-오프된다.

Description

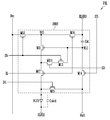

도 2는 누설전류를 최소화하기 위한 본 발명의 실시예에 의한 트랜지스터들의 접속관계를 나타내는 도면이다.

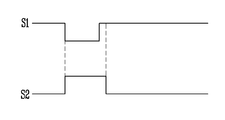

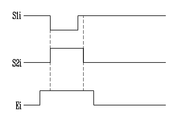

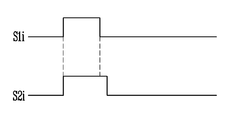

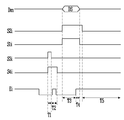

도 3은 도 2의 트랜지스터들의 구동방법 실시예를 나타내는 파형도이다.

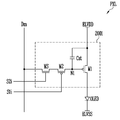

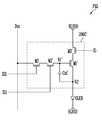

도 4는 본 발명의 실시예에 의한 화소를 나타내는 도면이다.

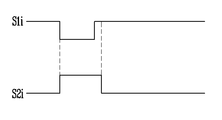

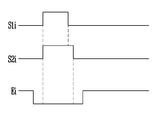

도 5는 도 4에 도시된 화소의 구동방법 실시예를 나타내는 파형도이다.

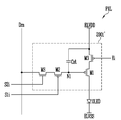

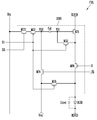

도 6a 및 도 6b는 본 발명의 다른 실시예에 의한 화소를 나타내는 도면이다.

도 7은 도 6a 및 도 6b에 도시된 화소의 구동방법 실시예를 나타내는 파형도이다.

도 8은 본 발명의 또 다른 실시예에 의한 화소를 나타내는 도면이다.

도 9는 도 8에 도시된 화소의 구동방법 실시예를 나타내는 파형도이다.

도 10은 본 발명의 또 다른 실시예에 의한 화소를 나타내는 도면이다.

도 11은 도 10에 도시된 화소의 구동방법 실시예를 나타내는 파형도이다.

도 12는 본 발명의 또 다른 실시예에 의한 화소를 나타내는 도면이다.

도 13은 도 12에 도시된 화소의 구동방법 실시예를 나타내는 파형도이다.

도 14는 본 발명의 또 다른 실시예에 의한 화소를 나타내는 도면이다.

도 15는 도 14에 도시된 화소의 구동방법 실시예를 나타내는 파형도이다.

도 16은 본 발명의 또 다른 실시예에 의한 화소를 나타내는 도면이다.

도 17은 도 16에 도시된 화소의 구동방법 실시예를 나타내는 파형도이다.

도 18은 본 발명의 또 다른 실시예에 의한 화소를 나타내는 도면이다.

도 19는 도 18에 도시된 화소의 구동방법 실시예를 나타내는 파형도이다.

120 : 데이터 구동부 130 : 발광 구동부

140 : 타이밍 제어부 150 : 호스트 시스템

2001,2002,2003,2004,2005 : 화소회로

Claims (53)

- 유기 발광 다이오드와;

제 1노드의 전압에 대응하여 제 1구동전원으로부터 상기 유기 발광 다이오드를 경유하여 제 2구동전원으로 공급되는 전류량을 제어하기 위한 제 1트랜지스터와;

상기 제 1노드와 상기 제 1구동전원 사이에 접속되는 스토리지 커패시터와;

데이터선과 상기 제 1노드 사이에 접속되며, 제 1주사선으로 주사신호가 공급될 때 턴-온되는 제 2트랜지스터와;

상기 제 2트랜지스터와 상기 데이터선 사이에 접속되며, 제 2주사선으로 주사신호가 공급될 때 턴-온되는 보조 트랜지스터를 구비하며;

상기 제 2트랜지스터 및 상기 보조 트랜지스터는 턴-온기간이 중첩되며, 상기 제 2트랜지스터는 상기 보조 트랜지스터보다 먼저 턴-오프되는 화소. - 제 1항에 있어서,

상기 보조 트랜지스터는 N타입 트랜지스터로 설정되는 화소. - 제 2항에 있어서,

상기 보조 트랜지스터는 산화물 반도체 트랜지스터로 설정되는 화소. - 제 1항에 있어서,

상기 제 1트랜지스터 및 상기 제 2트랜지스터는 P타입 트랜지스터로 설정되는 화소. - 제 4항에 있어서,

상기 제 1트랜지스터 및 상기 제 2트랜지스터는 폴리 실리콘 반도체 트랜지스터로 설정되는 화소. - 제 1항에 있어서,

상기 제 2트랜지스터 및 상기 보조 트랜지스터는 동시에 턴-온되는 화소. - 제 1항에 있어서,

상기 제 1구동전원과 상기 제 1트랜지스터의 사이 및 상기 제 1트랜지스터와 상기 유기 발광 다이오드의 애노드전극 사이 중 적어도 하나에 형성되며, 발광 제어선으로 발광 제어신호가 공급될 때 턴-오프되는 제 3트랜지스터를 더 구비하는 화소. - 제 7항에 있어서,

상기 제 3트랜지스터의 턴-온기간은 상기 제 2트랜지스터의 턴-온기간과 중첩되지 않는 화소. - 유기 발광 다이오드와;

제 1노드에 접속된 제 1구동전원과 상기 유기 발광 다이오드의 애노드전극 사이에 접속되며, 제 2노드의 전압에 대응하여 상기 제 1구동전원으로부터 상기 유기 발광 다이오드로 공급되는 전류량을 제어하기 위한 제 1트랜지스터와;

상기 제 2노드와 상기 제 1구동전원 사이에 접속되는 스토리지 커패시터와;

데이터선과 상기 제 1노드 사이에 접속되며, i(i는 자연수)번째 제 1주사선으로 제 1주사신호가 공급될 때 턴-온되는 제 2트랜지스터와;

상기 제 1트랜지스터의 제 2전극과 상기 제 2노드 사이에 접속되며, 상기 제 1주사신호가 공급될 때 턴-온되는 제 3트랜지스터와;

상기 제 3트랜지스터와 상기 제 1트랜지스터의 제 2전극 사이에 접속되며, i번째 제 2주사선으로 제 2주사신호가 공급될 때 턴-온되는 보조 트랜지스터를 구비하며;

상기 제 3트랜지스터 및 상기 보조 트랜지스터는 턴-온기간이 중첩되며, 상기 제 3트랜지스터는 상기 보조 트랜지스터보다 먼저 턴-오프되는 화소. - 제 9항에 있어서,

상기 보조 트랜지스터는 N타입 트랜지스터로 설정되는 화소. - 제 10항에 있어서,

상기 보조 트랜지스터는 산화물 반도체 트랜지스터로 설정되는 화소. - 제 9항에 있어서,

상기 제 1트랜지스터, 상기 제 2트랜지스터 및 상기 제 3트랜지스터는 P타입 트랜지스터로 설정되는 화소. - 제 12항에 있어서,

상기 제 1트랜지스터, 상기 제 2트랜지스터 및 상기 제 3트랜지스터는 폴리 실리콘 반도체 트랜지스터로 설정되는 화소. - 제 9항에 있어서,

상기 제 3트랜지스터 및 보조 트랜지스터는 동시에 턴-온되는 화소. - 제 9항에 있어서,

상기 제 2노드와 제 1전원 사이에 접속되며, i번째 제 3주사선으로 주사신호가 공급될 때 턴-온되는 제 4트랜지스터와,

상기 유기 발광 다이오드의 애노드전극과 상기 제 1전원 사이에 접속되며, i번째 제 4주사선으로 주사신호가 공급될 때 턴-온되는 제 5트랜지스터를 더 구비하는 화소. - 제 15항에 있어서,

상기 제 4트랜지스터 및 제 5트랜지스터는 P타입 트랜지스터로 설정되는 화소. - 제 16항에 있어서,

상기 제 4트랜지스터 및 제 5트랜지스터는 폴리 실리콘 반도체 트랜지스터로 설정되는 화소. - 제 16항에 있어서,

상기 i번째 제 3주사선은 i-1번째 제 1주사선으로 설정되고, 상기 i번째 제 4주사선은 i번째 제 1주사선으로 설정되는 화소. - 제 15항에 있어서,

상기 제 4트랜지스터 및 제 5트랜지스터는 N타입 트랜지스터로 설정되는 화소. - 제 19항에 있어서,

상기 제 4트랜지스터 및 제 5트랜지스터는 산화물 반도체 트랜지스터로 설정되는 화소. - 제 19항에 있어서,

상기 i번째 제 3주사선은 i-1번째 제 2주사선으로 설정되고, 상기 i번째 제 4주사선은 i번째 제 2주사선으로 설정되는 화소. - 제 9항에 있어서,

상기 제 1구동전원과 상기 제 1노드 사이에 접속되며, i번째 발광 제어선으로 발광 제어신호가 공급될 때 턴-오프되고 그 외의 경우에 턴-온되는 제 6트랜지스터와;

상기 제 1트랜지스터의 제 2전극과 상기 유기 발광 다이오드의 애노드전극 사이에 접속되며, 상기 제 6트랜지스터와 동시에 턴-온 및 턴-오프되는 제 7트랜지스터를 더 구비하는 화소. - 제 22항에 있어서,

상기 제 6트랜지스터의 턴-온기간은 상기 제 3트랜지스터의 턴-온기간과 중첩되지 않는 화소. - 유기 발광 다이오드와;

제 2노드에 접속된 상기 유기 발광 다이오드의 애노드전극과 제 1구동전원 사이에 접속되며, 제 1노드의 전압에 대응하여 상기 제 1구동전원으로부터 상기 유기 발광 다이오드로 공급되는 전류량을 제어하기 위한 제 1트랜지스터와;

상기 제 1노드와 상기 제 2노드 사이에 접속되는 스토리지 커패시터와;

데이터선과 상기 제 1노드 사이에 접속되며, 제 1주사선으로 주사신호가 공급될 때 턴-온되는 제 2트랜지스터와;

상기 제 2트랜지스터와 상기 데이터선 사이에 접속되며, 제 2주사선으로 주사신호가 공급될 때 턴-온되는 보조 트랜지스터를 구비하며;

상기 제 2트랜지스터는 상기 보조 트랜지스터와 턴-온기간이 중첩되며, 상기 제 2트랜지스터는 상기 보조 트랜지스터보다 먼저 턴-오프되는 화소. - 제 24항에 있어서,

상기 보조 트랜지스터는 N타입 트랜지스터로 설정되는 화소. - 제 25항에 있어서,

상기 보조 트랜지터는 산화물 반도체 트랜지스터로 설정되는 화소. - 제 24항에 있어서,

상기 제 1트랜지스터 및 상기 제 2트랜지스터는 N타입 트랜지스터로 설정되는 화소. - 제 27항에 있어서,

상기 제 1트랜지스터 및 상기 제 2트랜지스터는 폴리 실리콘 반도체 트랜지스터로 설정되는 화소. - 제 24항에 있어서,

상기 제 2트랜지스터 및 상기 보조 트랜지스터는 동시에 턴-온되는 화소. - 제 24항에 있어서,

상기 제 2노드와 제 1전원 사이에 접속되며, 제 3주사선으로 주사신호가 공급될 때 턴-온되는 제 3트랜지스터와;

상기 제 1구동전원과 상기 제 1트랜지스터의 제 1전극 사이에 접속되며, 발광 제어선으로 발광 제어신호가 공급될 때 턴-오프되는 제 4트랜지스터와;

기준전원과 상기 제 1노드 사이에 접속되며, 제 4주사선으로 주사신호가 공급될 때 턴-온되는 제 5트랜지스터를 더 구비하는 화소. - 제 30항에 있어서,

상기 제 3트랜지스터 및 상기 제 4트랜지스터는 N타입의 폴리 실리콘 반도체 트랜지스터로 설정되고, 상기 제 5트랜지스터는 N타입의 산화물 반도체 트랜지스터로 설정되는 화소. - 유기 발광 다이오드와;

제 1노드의 전압에 대응하여 제 1구동전원으로부터 상기 유기 발광 다이오드를 경유하여 제 2구동전원으로 흐르는 전류량을 제어하기 위한 제 1트랜지스터와;

상기 제 1노드와 상기 제 1트랜지스터의 제 2전극 사이에 접속되며, 제 1주사선으로 제 1주사신호가 공급될 때 턴-온되는 제 2트랜지스터와;

상기 제 1노드와 제 2노드 사이에 접속되는 스토리지 커패시터와;

데이터선과 상기 제 2노드 사이에 접속되며, 상기 제 1주사신호가 공급될 때 턴-온되는 제 3트랜지스터와;

상기 데이터선과 상기 제 3트랜지스터 사이에 접속되며, 제 2주사선으로 제 2주사신호가 공급될 때 턴-온되는 보조 트랜지스터를 구비하며;

상기 제 3트랜지스터는 상기 보조 트랜지스터와 턴-온기간이 중첩되며, 상기 제 3트랜지스터는 상기 보조 트랜지스터보다 먼저 턴-오프되는 화소. - 제 32항에 있어서,

상기 보조 트랜지스터는 N타입 트랜지스터로 설정되는 화소. - 제 33항에 있어서,

상기 보조 트랜지스터는 산화물 반도체 트랜지스터로 설정되는 화소. - 제 32항에 있어서,

상기 제 1트랜지스터, 제 2트랜지스터 및 제 3트랜지스터는 P타입 트랜지스터로 설정되는 화소. - 제 35항에 있어서,

상기 제 1트랜지스터, 제 2트랜지스터 및 제 3트랜지스터는 폴리 실리콘 반도체 트랜지스터로 설정되는 화소. - 제 32항에 있어서,

상기 제 3트랜지스터 및 상기 보조 트랜지스터는 동시에 턴-온되는 화소. - 제 32항에 있어서,

상기 제 2노드와 제 1전원 사이에 접속되며, 반전 발광 제어선으로 반전 발광 제어신호가 공급될 때 턴-오프되는 제 4트랜지스터와;

상기 제 1전원과 상기 유기 발광 다이오드의 애노드전극 사이에 접속되며, 상기 제 1주사신호가 공급될 때 턴-온되는 제 5트랜지스터와;

상기 제 1트랜지스터와 상기 유기 발광 다이오드의 애노드전극 사이에 접속되며, 발광 제어선으로 발광 제어신호가 공급될 때 턴-오프되는 제 6트랜지스터를 더 구비하는 화소. - 제 38항에 있어서,

상기 제 4트랜지스터 및 제 6트랜지스터의 턴-온기간은 중첩되는 화소. - 제 38항에 있어서,

상기 제 4트랜지스터의 턴-온기간은 상기 제 2트랜지스터의 턴-온기간과 적어도 일부 중첩되는 화소. - 제 38항에 있어서,

상기 제 4트랜지스터는 N타입 산화물 반도체 트랜지스터로 설정되고, 상기 5트랜지스터 및 제 6트랜지스터는 P타입 폴리 실리콘 반도체 트랜지스터로 설정되는 화소. - 제 1구동전원으로부터 유기 발광 다이오드를 경유하여 제 2구동전원으로 이어지는 전류 경로에 위치되는 제 1트랜지스터와;

상기 전류 경로 이외의 전류 누설경로에 직렬로 접속되는 제 2트랜지스터 및 보조 트랜지스터를 구비하며;

상기 제 2트랜지스터 및 상기 보조 트랜지스터는 턴-온기간이 중첩되며, 상기 제 2트랜지스터는 상기 보조 트랜지스터보다 먼저 턴-오프되는 화소. - 제 42항에 있어서,

상기 제 2트랜지스터는 상기 제 1트랜지스터의 게이트전극과 전기적으로 접속되는 화소. - 제 42항에 있어서,

상기 보조 트랜지스터는 N타입 트랜지스터로 설정되는 화소. - 제 44항에 있어서,

상기 보조 트랜지스터는 산화물 반도체 트랜지스터로 설정되는 화소. - 제 42항에 있어서,

상기 제 2트랜지스터는 폴리 실리콘 반도체 트랜지스터로 설정되는 화소. - 제 42항에 있어서,

상기 제 2트랜지스터 및 상기 보조 트랜지스터는 동시에 턴-온되는 화소. - 주사선들 및 데이터선들과 접속되는 화소들을 구비하며;

상기 화소들 각각은

제 1구동전원으로부터 유기 발광 다이오드를 경유하여 제 2구동전원으로 이어지는 전류 경로에 위치되는 제 1트랜지스터와;

상기 전류 경로 이외의 전류 누설경로에 직렬로 접속되는 제 2트랜지스터 및 보조 트랜지스터를 구비하며;

상기 제 2트랜지스터 및 상기 보조 트랜지스터는 턴-온기간이 중첩되며, 상기 제 2트랜지스터는 상기 보조 트랜지스터보다 먼저 턴-오프되는 유기전계발광 표시장치. - 제 48항에 있어서,

상기 제 2트랜지스터는 상기 제 1트랜지스터의 게이트전극과 전기적으로 접속되는 유기전계발광 표시장치. - 제 48항에 있어서,

상기 보조 트랜지스터는 N타입 트랜지스터로 설정되는 유기전계발광 표시장치. - 제 50항에 있어서,

상기 보조 트랜지스터는 산화물 반도체 트랜지스터로 설정되는 유기전계발광 표시장치. - 제 48항에 있어서,

상기 제 2트랜지스터는 폴리 실리콘 반도체 트랜지스터로 설정되는 유기전계발광 표시장치. - 제 48항에 있어서,

상기 제 2트랜지스터 및 상기 보조 트랜지스터는 동시에 턴-온되는 유기전계발광 표시장치.

Priority Applications (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020170024876A KR102775758B1 (ko) | 2017-02-24 | 2017-02-24 | 화소 및 이를 가지는 유기전계발광 표시장치 |

| US15/887,027 US10614758B2 (en) | 2017-02-24 | 2018-02-02 | Pixel and organic light emitting display device having the pixel |

| CN201810156832.0A CN108510944B (zh) | 2017-02-24 | 2018-02-24 | 像素以及具有该像素的有机发光显示装置 |

| CN202210505668.6A CN114743503B (zh) | 2017-02-24 | 2018-02-24 | 像素 |

| EP18158700.7A EP3367373B1 (en) | 2017-02-24 | 2018-02-26 | Pixel and organic light emitting display device having the pixel |

| US16/841,582 US11217165B2 (en) | 2017-02-24 | 2020-04-06 | Pixel and organic light emitting display device having the pixel |

| US17/567,767 US11688342B2 (en) | 2017-02-24 | 2022-01-03 | Pixel and organic light emitting display device having the pixel |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020170024876A KR102775758B1 (ko) | 2017-02-24 | 2017-02-24 | 화소 및 이를 가지는 유기전계발광 표시장치 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20180098442A true KR20180098442A (ko) | 2018-09-04 |

| KR102775758B1 KR102775758B1 (ko) | 2025-03-07 |

Family

ID=61283112

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020170024876A Active KR102775758B1 (ko) | 2017-02-24 | 2017-02-24 | 화소 및 이를 가지는 유기전계발광 표시장치 |

Country Status (4)

| Country | Link |

|---|---|

| US (3) | US10614758B2 (ko) |

| EP (1) | EP3367373B1 (ko) |

| KR (1) | KR102775758B1 (ko) |

| CN (2) | CN108510944B (ko) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2020226246A1 (ko) * | 2019-05-08 | 2020-11-12 | 삼성디스플레이 주식회사 | 화소, 화소를 포함하는 표시 장치 및 그의 구동 방법 |

| KR20220133755A (ko) * | 2020-01-28 | 2022-10-05 | 오엘이디워크스 엘엘씨 | 보호 회로를 갖춘 oled 디스플레이 |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI708233B (zh) * | 2019-09-20 | 2020-10-21 | 友達光電股份有限公司 | 適用於低更新頻率的畫素電路與相關的顯示裝置 |

| CN110728952B (zh) * | 2019-10-31 | 2021-04-30 | 厦门天马微电子有限公司 | 像素驱动电路及其驱动方法、显示装置 |

| TWI853179B (zh) * | 2020-07-21 | 2024-08-21 | 美商Oled沃克斯有限責任公司 | 具有低電壓矽背板之堆疊式有機發光二極體微顯示器 |

| KR102791842B1 (ko) * | 2020-07-23 | 2025-04-09 | 삼성디스플레이 주식회사 | 화소 및 이를 포함하는 표시 장치 |

| KR102805323B1 (ko) * | 2020-10-16 | 2025-05-13 | 삼성디스플레이 주식회사 | 표시 장치 및 이의 구동 방법 |

| CN112419982A (zh) * | 2020-11-11 | 2021-02-26 | Oppo广东移动通信有限公司 | 一种像素补偿电路、显示面板及电子设备 |

| KR102765756B1 (ko) * | 2020-11-17 | 2025-02-13 | 삼성디스플레이 주식회사 | 표시 장치 |

| CN112397025A (zh) * | 2020-11-24 | 2021-02-23 | 合肥维信诺科技有限公司 | 像素电路及其驱动方法、显示面板 |

| KR102812137B1 (ko) * | 2020-12-28 | 2025-05-26 | 엘지디스플레이 주식회사 | 표시장치 |

| CN112992071A (zh) * | 2021-04-22 | 2021-06-18 | 京东方科技集团股份有限公司 | 像素电路及其驱动方法、显示装置 |

| GB2615719A (en) * | 2021-04-26 | 2023-08-16 | Boe Technology Group Co Ltd | Pixel circuit, pixel driving method and display device |

| WO2022226727A1 (zh) * | 2021-04-26 | 2022-11-03 | 京东方科技集团股份有限公司 | 像素电路、像素驱动方法和显示装置 |

| CN113870780A (zh) * | 2021-09-18 | 2021-12-31 | 合肥维信诺科技有限公司 | 像素电路及显示面板 |

| US12340751B2 (en) * | 2022-06-24 | 2025-06-24 | Chengdu Boe Optoelectronics Technology Co., Ltd. | Pixel driving circuit and driving method thereof, display panel and display device |

| CN115171611A (zh) * | 2022-07-29 | 2022-10-11 | 武汉天马微电子有限公司 | 像素电路、其驱动方法、显示面板及显示装置 |

| KR20240046384A (ko) * | 2022-09-30 | 2024-04-09 | 삼성디스플레이 주식회사 | 화소, 표시 장치 및 화소의 구동 방법 |

| CN115862546A (zh) * | 2022-12-15 | 2023-03-28 | 合肥维信诺科技有限公司 | 像素电路及其驱动方法、显示面板 |

| WO2024152289A1 (en) * | 2023-01-19 | 2024-07-25 | Boe Technology Group Co., Ltd. | Pixel driving circuit and display apparatus |

| CN119811307B (zh) * | 2024-12-31 | 2025-12-26 | 惠科股份有限公司 | 显示面板与显示装置 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20050100624A (ko) * | 2003-01-22 | 2005-10-19 | 도시바 마쯔시따 디스플레이 테크놀로지 컴퍼니, 리미티드 | 유기 el 디스플레이 및 액티브 매트릭스 기판 |

| KR20060024347A (ko) * | 2003-11-07 | 2006-03-16 | 산요덴키가부시키가이샤 | 화소 회로 및 표시 장치 |

| KR20110078396A (ko) * | 2009-12-31 | 2011-07-07 | 삼성모바일디스플레이주식회사 | 화소 및 이를 이용한 유기전계발광 표시장치 |

| KR20130135506A (ko) * | 2012-06-01 | 2013-12-11 | 삼성디스플레이 주식회사 | 화소 및 이를 이용한 유기전계발광 표시장치 |

| KR20150100515A (ko) * | 2014-02-25 | 2015-09-02 | 엘지디스플레이 주식회사 | 조절가능한 리프레시 레이트로 구동되는 선택적인 부분들을 포함하는 디스플레이 및 이를 구동하는 방법 |

Family Cites Families (30)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6636191B2 (en) * | 2000-02-22 | 2003-10-21 | Eastman Kodak Company | Emissive display with improved persistence |

| KR100496884B1 (ko) | 2003-02-10 | 2005-06-23 | 삼성전자주식회사 | 유기 발광 소자의 픽셀 회로 |

| US7612749B2 (en) * | 2003-03-04 | 2009-11-03 | Chi Mei Optoelectronics Corporation | Driving circuits for displays |

| KR100592646B1 (ko) * | 2004-11-08 | 2006-06-26 | 삼성에스디아이 주식회사 | 발광 표시장치 및 그의 구동방법 |

| KR100707623B1 (ko) * | 2005-03-19 | 2007-04-13 | 한양대학교 산학협력단 | 화소 및 이를 이용한 발광 표시장치 |

| KR100703429B1 (ko) * | 2005-08-01 | 2007-04-03 | 삼성에스디아이 주식회사 | 화소 및 이를 이용한 유기 발광 표시장치 |

| JP4600780B2 (ja) | 2007-01-15 | 2010-12-15 | ソニー株式会社 | 表示装置及びその駆動方法 |

| KR100902221B1 (ko) * | 2008-01-28 | 2009-06-11 | 삼성모바일디스플레이주식회사 | 화소 및 이를 이용한 유기전계발광 표시장치 |

| JP5439782B2 (ja) | 2008-09-29 | 2014-03-12 | セイコーエプソン株式会社 | 画素回路の駆動方法、発光装置および電子機器 |

| KR101056317B1 (ko) * | 2009-04-02 | 2011-08-11 | 삼성모바일디스플레이주식회사 | 화소 및 이를 이용한 유기전계발광 표시장치 |

| KR101719567B1 (ko) | 2010-10-28 | 2017-03-27 | 삼성디스플레이 주식회사 | 유기전계발광 표시장치 |

| CN101986378A (zh) * | 2010-11-09 | 2011-03-16 | 华南理工大学 | 有源有机发光二极管显示器像素驱动电路及其驱动方法 |

| KR101869056B1 (ko) * | 2012-02-07 | 2018-06-20 | 삼성디스플레이 주식회사 | 화소 및 이를 이용한 유기 발광 표시 장치 |

| KR20140028921A (ko) * | 2012-08-31 | 2014-03-10 | 삼성디스플레이 주식회사 | 화소 및 이를 이용한 유기전계발광 표시장치 |

| JP2014109707A (ja) | 2012-12-03 | 2014-06-12 | Samsung Display Co Ltd | 電気光学装置の駆動方法および電気光学装置 |

| KR20140081262A (ko) * | 2012-12-21 | 2014-07-01 | 삼성디스플레이 주식회사 | 화소 및 이를 이용한 유기전계발광 표시장치 |

| CN103680406B (zh) * | 2013-12-12 | 2015-09-09 | 京东方科技集团股份有限公司 | 一种像素电路及显示装置 |

| CN104751777B (zh) * | 2013-12-31 | 2017-10-17 | 昆山工研院新型平板显示技术中心有限公司 | 像素电路、像素及包括该像素的amoled显示装置及其驱动方法 |

| US9276050B2 (en) | 2014-02-25 | 2016-03-01 | Lg Display Co., Ltd. | Organic light emitting display device |

| KR101672091B1 (ko) | 2014-02-25 | 2016-11-02 | 엘지디스플레이 주식회사 | 복합형 박막 트랜지스터를 갖는 유기 전계 발광 표시 장치 |

| KR102298336B1 (ko) | 2014-06-20 | 2021-09-08 | 엘지디스플레이 주식회사 | 유기발광다이오드 표시장치 |

| CN105719595B (zh) * | 2014-12-05 | 2018-08-24 | 昆山工研院新型平板显示技术中心有限公司 | 像素驱动电路、有机发光显示器及其驱动方法 |

| CN105789250B (zh) * | 2014-12-26 | 2018-11-09 | 昆山工研院新型平板显示技术中心有限公司 | 像素电路及其驱动方法和有机发光显示器 |

| EP3098804A3 (en) | 2015-05-28 | 2016-12-21 | LG Display Co., Ltd. | Organic light emitting display |

| CN104992663B (zh) * | 2015-08-05 | 2017-09-22 | 京东方科技集团股份有限公司 | 一种移位寄存器单元及栅极驱动电路、显示面板 |

| US10121430B2 (en) | 2015-11-16 | 2018-11-06 | Apple Inc. | Displays with series-connected switching transistors |

| KR102477982B1 (ko) * | 2016-06-08 | 2022-12-15 | 삼성디스플레이 주식회사 | 표시 장치 |

| KR102561294B1 (ko) | 2016-07-01 | 2023-08-01 | 삼성디스플레이 주식회사 | 화소 및 스테이지 회로와 이를 가지는 유기전계발광 표시장치 |

| KR102573334B1 (ko) * | 2016-12-28 | 2023-09-01 | 엘지디스플레이 주식회사 | 유기발광표시장치 및 그의 구동방법 |

| KR102583838B1 (ko) | 2017-01-17 | 2023-10-05 | 삼성디스플레이 주식회사 | 화소 및 이를 이용한 유기전계발광 표시장치 |

-

2017

- 2017-02-24 KR KR1020170024876A patent/KR102775758B1/ko active Active

-

2018

- 2018-02-02 US US15/887,027 patent/US10614758B2/en active Active

- 2018-02-24 CN CN201810156832.0A patent/CN108510944B/zh active Active

- 2018-02-24 CN CN202210505668.6A patent/CN114743503B/zh active Active

- 2018-02-26 EP EP18158700.7A patent/EP3367373B1/en active Active

-

2020

- 2020-04-06 US US16/841,582 patent/US11217165B2/en active Active

-

2022

- 2022-01-03 US US17/567,767 patent/US11688342B2/en active Active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20050100624A (ko) * | 2003-01-22 | 2005-10-19 | 도시바 마쯔시따 디스플레이 테크놀로지 컴퍼니, 리미티드 | 유기 el 디스플레이 및 액티브 매트릭스 기판 |

| US20050269961A1 (en) * | 2003-01-22 | 2005-12-08 | Makoto Shibusawa | Organic EL display and active matrix substrate |

| KR20060024347A (ko) * | 2003-11-07 | 2006-03-16 | 산요덴키가부시키가이샤 | 화소 회로 및 표시 장치 |

| KR20110078396A (ko) * | 2009-12-31 | 2011-07-07 | 삼성모바일디스플레이주식회사 | 화소 및 이를 이용한 유기전계발광 표시장치 |

| KR20130135506A (ko) * | 2012-06-01 | 2013-12-11 | 삼성디스플레이 주식회사 | 화소 및 이를 이용한 유기전계발광 표시장치 |

| KR20150100515A (ko) * | 2014-02-25 | 2015-09-02 | 엘지디스플레이 주식회사 | 조절가능한 리프레시 레이트로 구동되는 선택적인 부분들을 포함하는 디스플레이 및 이를 구동하는 방법 |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2020226246A1 (ko) * | 2019-05-08 | 2020-11-12 | 삼성디스플레이 주식회사 | 화소, 화소를 포함하는 표시 장치 및 그의 구동 방법 |

| US11922872B2 (en) | 2019-05-08 | 2024-03-05 | Samsung Display Co., Ltd. | Pixels, display device comprising pixels, and driving method therefor |

| US12223902B2 (en) | 2019-05-08 | 2025-02-11 | Samsung Display Co., Ltd. | Pixels, display device comprising pixels, and driving method therefor |

| KR20220133755A (ko) * | 2020-01-28 | 2022-10-05 | 오엘이디워크스 엘엘씨 | 보호 회로를 갖춘 oled 디스플레이 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP3367373A1 (en) | 2018-08-29 |

| US10614758B2 (en) | 2020-04-07 |

| US11688342B2 (en) | 2023-06-27 |

| US20200234642A1 (en) | 2020-07-23 |

| CN114743503A (zh) | 2022-07-12 |

| EP3367373B1 (en) | 2021-04-21 |

| US20220122537A1 (en) | 2022-04-21 |

| CN108510944A (zh) | 2018-09-07 |

| KR102775758B1 (ko) | 2025-03-07 |

| CN114743503B (zh) | 2025-07-22 |

| CN108510944B (zh) | 2022-05-27 |

| US20180247591A1 (en) | 2018-08-30 |

| US11217165B2 (en) | 2022-01-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20180098442A (ko) | 화소 및 이를 가지는 유기전계발광 표시장치 | |

| KR102729321B1 (ko) | 화소 및 스테이지 회로와 이를 가지는 유기전계발광 표시장치 | |

| KR102547871B1 (ko) | 화소 및 이를 가지는 유기전계발광 표시장치 | |

| KR101056302B1 (ko) | 유기전계발광 표시장치 | |

| KR102730406B1 (ko) | 화소 및 이를 가지는 유기전계발광 표시장치 | |

| KR101056241B1 (ko) | 유기전계발광 표시장치 | |

| KR100907391B1 (ko) | 화소 및 이를 이용한 유기전계발광 표시장치 | |

| US8345039B2 (en) | Organic light emitting display device and method of driving the same | |

| KR101765778B1 (ko) | 유기전계발광 표시장치 | |

| US20090295772A1 (en) | Pixel and organic light emitting display using the same | |

| KR20180004369A (ko) | 화소 및 스테이지 회로와 이를 가지는 유기전계발광 표시장치 | |

| KR20180003390A (ko) | 유기발광 표시장치 및 그의 구동 방법 | |

| KR101142660B1 (ko) | 화소 및 이를 이용한 유기전계발광 표시장치 | |

| KR20170132016A (ko) | Oled 표시 장치 및 그의 구동 방법 | |

| JP2009301005A (ja) | 画素およびこれを用いた有機電界発光表示装置 | |

| WO2015029422A1 (ja) | 駆動方法および表示装置 | |

| KR101901757B1 (ko) | 유기발광 다이오드 표시장치 및 그 구동방법 | |

| KR20180085121A (ko) | 화소 및 이를 이용한 유기전계발광 표시장치 | |

| US11211003B2 (en) | Display device having at least two emission enable periods per image frame and method of driving the same | |

| KR100858613B1 (ko) | 유기전계발광 표시장치 | |

| KR101056318B1 (ko) | 화소 및 이를 이용한 유기전계발광 표시장치 | |

| KR20100039066A (ko) | 유기전계 발광 디스플레이 장치 | |

| KR101048951B1 (ko) | 유기전계발광 표시장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0109 | Patent application |

St.27 status event code: A-0-1-A10-A12-nap-PA0109 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-3-3-R10-R18-oth-X000 |

|

| R17-X000 | Change to representative recorded |

St.27 status event code: A-3-3-R10-R17-oth-X000 |

|

| R17-X000 | Change to representative recorded |

St.27 status event code: A-3-3-R10-R17-oth-X000 |

|

| A201 | Request for examination | ||

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |

|

| E13-X000 | Pre-grant limitation requested |

St.27 status event code: A-2-3-E10-E13-lim-X000 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |

|

| E13-X000 | Pre-grant limitation requested |

St.27 status event code: A-2-3-E10-E13-lim-X000 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-2-2-P10-P22-nap-X000 |

|

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U11-oth-PR1002 |

|

| PG1601 | Publication of registration |

St.27 status event code: A-4-4-Q10-Q13-nap-PG1601 |