KR20150131361A - 재구성 가능한 스위치드 커패시터 전력 컨버터 기술들 - Google Patents

재구성 가능한 스위치드 커패시터 전력 컨버터 기술들 Download PDFInfo

- Publication number

- KR20150131361A KR20150131361A KR1020157029889A KR20157029889A KR20150131361A KR 20150131361 A KR20150131361 A KR 20150131361A KR 1020157029889 A KR1020157029889 A KR 1020157029889A KR 20157029889 A KR20157029889 A KR 20157029889A KR 20150131361 A KR20150131361 A KR 20150131361A

- Authority

- KR

- South Korea

- Prior art keywords

- voltage

- capacitor

- capacitors

- mode

- switched

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of dc power input into dc power output

- H02M3/02—Conversion of dc power input into dc power output without intermediate conversion into ac

- H02M3/04—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters

- H02M3/06—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using resistors or capacitors, e.g. potential divider

- H02M3/07—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using resistors or capacitors, e.g. potential divider using capacitors charged and discharged alternately by semiconductor devices with control electrode, e.g. charge pumps

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/0048—Circuits or arrangements for reducing losses

- H02M1/0054—Transistor switching losses

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/0095—Hybrid converter topologies, e.g. NPC mixed with flying capacitor, thyristor converter mixed with MMC or charge pump mixed with buck

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/32—Means for protecting converters other than automatic disconnection

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of dc power input into dc power output

- H02M3/02—Conversion of dc power input into dc power output without intermediate conversion into ac

- H02M3/04—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters

- H02M3/06—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using resistors or capacitors, e.g. potential divider

- H02M3/07—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using resistors or capacitors, e.g. potential divider using capacitors charged and discharged alternately by semiconductor devices with control electrode, e.g. charge pumps

- H02M3/073—Charge pumps of the Schenkel-type

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of dc power input into dc power output

- H02M3/02—Conversion of dc power input into dc power output without intermediate conversion into ac

- H02M3/04—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters

- H02M3/10—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M3/145—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal

- H02M3/155—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only

- H02M3/156—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only with automatic control of output voltage or current, e.g. switching regulators

- H02M3/158—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only with automatic control of output voltage or current, e.g. switching regulators including plural semiconductor devices as final control devices for a single load

- H02M3/1584—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only with automatic control of output voltage or current, e.g. switching regulators including plural semiconductor devices as final control devices for a single load with a plurality of power processing stages connected in parallel

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/0003—Details of control, feedback or regulation circuits

-

- H02M2001/0003—

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of dc power input into dc power output

- H02M3/02—Conversion of dc power input into dc power output without intermediate conversion into ac

- H02M3/04—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters

- H02M3/06—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using resistors or capacitors, e.g. potential divider

- H02M3/07—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using resistors or capacitors, e.g. potential divider using capacitors charged and discharged alternately by semiconductor devices with control electrode, e.g. charge pumps

- H02M3/073—Charge pumps of the Schenkel-type

- H02M3/075—Charge pumps of the Schenkel-type including a plurality of stages and two sets of clock signals, one set for the odd and one set for the even numbered stages

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02B—CLIMATE CHANGE MITIGATION TECHNOLOGIES RELATED TO BUILDINGS, e.g. HOUSING, HOUSE APPLIANCES OR RELATED END-USER APPLICATIONS

- Y02B70/00—Technologies for an efficient end-user side electric power management and consumption

- Y02B70/10—Technologies improving the efficiency by using switched-mode power supplies [SMPS], i.e. efficient power electronics conversion e.g. power factor correction or reduction of losses in power supplies or efficient standby modes

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Dc-Dc Converters (AREA)

- Amplifiers (AREA)

Abstract

제 1 전압을 제 2 전압으로 변환하는 장치는 선택 가능한 변환이득을 갖는 재구성 가능한 스위치드 커패시터 전력 컨버터를 포함한다. 컨버터는 스택 노드와 위상 노드에 전기적으로 각각 결합된 커패시터를 갖는 캐스케이드 멀티플라이어 스위치드 커패시터 네트워크를 포함한다. 제어기는 상기 네트워크가 제 1 및 제 2 동작모드사이의 전이를 일으킨다. 제 1모드에서 적어도 한 개의 커패시터는 상기 재구성 가능한 스위치드 커패시터 전력 컨버터의 전하 이동 경로에서 분리된다. 결과적으로, 상기 제 1 동작 모드에서, 상기 전력 컨버터는 제 1이득으로 동작한다. 상기 제 2 모드에서는, 상기 전력 컨버터는 제 2 변환이득으로 동작한다. 반면에, 상기 적어도 하나의 커패시터에 걸리는 제 3 전압은 어떠한 값도 자유롭게 가질 수 있다.

Description

본 출원은 2013년 3월 15일 출원된 미국 출원 번호 13/839,315에 대해 우선권을 주장하여, 상기 문헌은 본원에 참조로 원용된다.

본 발명은 스위치드 커패시터 전력 컨버터를 재구성하기 위한 기술과 관련된다.

스위치-모드 전력 컨버터는 스위치 네트워크를 사용하여 에너지 저장 소자들 (예, 인덕터들 및 커패시터들)을 상이한 전기적 구성이 되도록 스위칭함으로써 출력전압을 생산하는 특정 유형의 전력 컨버터이다. 스위치도 커패시터 전력 컨버터는 에너지를 전달하기 위해 주로 커패시터들을 이용하는 스위치-모드 전력 컨버터의 유형이다. 이러한 컨버터들에서, 또한 스위치드 커패시터 회로들로 알려진 것은, 변환율(transformation ratio) 혹은 변환-이득(conversion-gain)이 증가함에 따라 커패시터들 및 스위치들의 수가 증가한다. 하나 이상의 변환-이득(예, 모드)을 갖는 스위치드 커패시터 회로는 종종 다중-모드(multi-mode) 스위치드 커패시터 회로로 나타낸다.

캐스케이드 멀티플라이어들은 낮은 전압(low-voltage)의 트랜지스터들을 이용하여 높은 변환 이득을 공급할 수 있는 다단계(multi-stage) 스위치드 커패시터 전력컨버터 토폴로지(topology)들 중의 하나의 가족이다. 본원에서 사용된 변환-이득은 스위치드 커패시터 회로가 입력전압보다 큰 출력전압을 생산하는 경우의 전압 이득, 또는 스위치드 커패시터 회로가 입력전압보다 작은 출력전압(VO)을 생산하는 경우의 전류 이득을 나타낸다. 에너지는 캐스케이드 멀티플라이어 네트워크들을 상이한 토폴로지(topology) 상태들로 순환시킴으로써 입력에서 출력으로 이동된다. 전하는 입력전압(VI)에서 전하 이동 경로를 거쳐 출력전압으로 이동된다. 각각의 토폴로지(topology) 상태에서 커패시터들의 수와 구성은 변환이득을 설정한다. 그러므로, 캐스케이드 멀티플라이어 네트워크의 형식을 재구성함으로써, 상기 변환이득이 수정될 수 있다.

도 1A-1B는 전압 소스(source)(26)로부터 입력전압(VI)을 수신하고 부하(RL)로 출력전압(VO)을 공급하는 두 가지의 알려진 재구성 가능한 캐스케이드 멀티플라이어들(20A, 20B)을 도시한다. 상기 캐스케이드 멀티플라이어(20A)는 위상 전압(P1), 다이오드들(D1-D6), 펌프 커패시터들(C1-C3), 및 dc 커패시터들(C4-C6)를 포함하는 단-위상(single-phase) 비대칭 멀티플라이 어이다. 반대로, 상기 캐스케이드 멀티플라이어(20B)는 위상 전압들 (P1-P2), 다이오드들(D11-D14), 및 펌프 커패시터들(C1-C3)을 포함하는 대칭 캐스케이드 멀티플라이어이다.

상기 캐스케이드 멀티플라이어들(20A, 20B) 모두는 입력전압 (VI)의 4배인 최대 출력전압(VO)을 생산할 수 있다. 상기변환이득은 제 1, 제 2,및 제 3의 인에이블 신호들(EN1, EN2, EN3)에 근거하여 선택될 수 있다. 제 1 인에이블 신호(EN1)가 높을 때 출력전압 (VO)은 입력전압(VI)의 3 배이고; 제 1 및 제 2 인에이블 신호들(EN1, EN2)이 높을 때 출력전압은 입력전압(VI)의 2 배이다; 기타 등등.

불행하게도, 각각의 상기 캐스케이드 멀티플라이어들(20A, 20B)은 네트워크 재구성을 위한 각각의 상기 펌프 커패시터들(C1-C3)의 양극 단자에 결합된 회로와 상기 펌프 커패시터들(C1-C3) 각각의 음극 단자에 결합된 회로가 있어야 한다. 추가적인 회로망은 캐스케이드 멀티플라이어(20A, 20B)의 효율을 감소시키거나, 또는 대용량의 바이패스 트랜지스터들(bypass transistors)을 필요로 한다. 더구나, 바이패스된 상기 펌프 커패시터들(C1-C3)은 입력전압(VI)에서 다이오드 전압 강하를 뺀 것과 동일한 전압으로 충전된다. 예를 들면, 제 1 인에이블 신호(EN1)가 높을 때 상기 펌프 커패시터(C1)의 양극 단자는 상기 입력전압 (VI)에서 한 개의 다이오드 강하만큼의 아래 전압으로 바이어스되며 상기 펌프 커패시터(C1)의 상기 음극단자는 접지로 바이어스 된다.

상기 전하 이동 경로에서 상기 커패시터들의 수가 바뀔 때, 재구성 이벤트(a reconfiguration event) 이전의 총 전하량은 전하 보전에 의해 재구성 이벤트(a reconfiguration event) 이후의 총 전하량과 동일하다. 이것은 상기 재구성 이벤트(a reconfiguration event) 이전의 각각의 커패시터들 내의 상기 전하가 재구성 이벤트(a reconfiguration event) 발생 시 상기 잔여 커패시터들 사이로 재분배하는 것을 의미한다. 더구나, 상기 재구성 이벤트(a reconfiguration event )의 전과 후 각각의 커패시터들에 걸리는 상기 전압은 변환 이득과 입력전압 (VI)에 비례하여 또한 변경된다. 각각의 커패시터 전압의 극성 변화는 상기 스위치드 커패시터 회로의 상기 변환이득의 증가 또는 감소에 의존한다.

재구성 가능한 캐스케이드 멀티플라이어들에 대한 시도는 높은 입력전압 범위 혹은 높은 출력전압 범위를 가지는 낮은 전압 트랜지스터들을 내구성있게 동작시키는 디자인의 복잡성에 있다. 더구나, 각각의 변환 이득 변경에서 발생되는 과도 전류 및/혹은 전압은 입력 전자기 간섭, 트랜지스터 동작, 및 내구성의 관점에서 중요한 영향을 미칠 수 있다.

본 발명은 스위치드 커패시터 전력 컨버터의 변환이득을 변경하기 위한 커패시터 네트워크의 신규한 구성을 제공하는 데 목적이 있다.

일 측면에서, 본 발명은 제 1 전압을 제 2 전압으로 변환하기 위한 장치를 그 특징으로 한다. 이러한 장치는 선택 가능한 변환 이득을 지닌 재구성 가능한 스위치드 커패시터 전력 컨버터를 포함한다. 이 재구성 가능한 스위치드 커패시터 전력 컨버터는 복수의 커패시터들을 구비한 제 1 캐스케이드 멀티플라이어 스위치드 커패시터 네트워크를 포함하며, 각각의 커패시터는 그것의 제 1 단자에서 상기 커패시터와 관련된 스택 노드에 전기적으로 연결되어지고 그것의 제 2차 단자에서 상기 커패시터와 관련된 위상 노드에 연결된다. 이 복수의 커패시터들은 제 1 외부 커패시터, 제 2 외부 커패시터, 및 제1 외부 커패시터와 제 2 외부 커패시터 사이에 적어도 하나의 내부 커패시터를 포함한다. 복수의 스택 스위치들은 복수의 커패시터들로부터 인접한 커패시터들의 노드들 사이에 있다. 제어기는 제 1 캐스케이드 멀티 플라이어 스위치드 커패시터 네트워크가 제 1 동작 모드와 제 2 동작 모드사이에서 전이되도록 한다. 제 1 동작 모드에서 적어도 하나의 커패시터는 재구성 가능한 스위치드 커패시터 전력 컨버터의 전하이동 경로에서 분리되어 지며, 전하 이동 경로는 제 1 전압과 제 2 전압 사이에서 확장된다. 따라서, 제 1 동작 모드에서, 재구성 가능한 스위치드 커패시터 전력 컨버터는 제 1 변환이득에서 동작하고, 제 2 동작 모드에서, 재구성 가능한 스위치드 커패시터 전력 컨버터는 제 2 변환이득에서 동작하고, 및 상기 적어도 하나의 커패시터에 걸리는 제 3 전압은 어떠한 값도 가정하는 것이 자유롭다.

일부 실시 예에서, 동작 중에, 상기 제 3 전압은 상기 제 1전압과 상기 제 2전압 사이에 있다.

상기 장치들의 실시 예들 중에서 프리-차지(pre-charge) 회로를 포함하는 것들도 있다. 이 프리-차지 회로는 상기 적어도 하나의 커패시터가 특정전압에 충전하도록 구성된다.

일부 실시 예들에서, 상기 적어도 하나의 커패시터는 외부 커패시터이다. 하지만 다른 실시 예에서 상기 적어도 하나의 커패시터는 내부 커패시터이다.

또한 본 발명에 포함된 실시 예들은 상기 적어도 하나의 커패시터를 선택적으로 바이패싱하기 위한 스위치들을 구비하는 스위칭 네트워크를 포함하고 있다.

일부 실시 예에서, 상기 제 1 단자는 양극 단자이다.

실시 예들에서, 제어기(controller)는 제 1 단자 및 제 2 단자로 구성된 그룹에서 선택된 하나의 단자를 연결 해제함으로써 상기 적어도 하나의 커패시터를 분리하도록 구성되어진다. 이들 실시 예들 중에는 상기 전하 이동 경로로부터 상기 커패시터들의 서브세트의 연결 해제를 허용하도록 노출된 스택 스위치들의 집합을 포함하며, 여기서 상기 제어기는 커패시터들의 상기 서브세트가 상기 전하 이동 경로로부터 연결 해제가 되도록 상기 스택 스위치들의 서브세트를 선택적으로 개방하도록 구성되며, 이를 통해 상기 전하 이동 경로를 재구성한다.

추가의 실시 예들은 상기 전하 이동 경로로부터 상기 커패시터들의 서브세트의 연결 해제를 허용하도록 노출된 위상 스위치들의 집합을 포함하며, 여기서 상기 제어기는 커패시터들의 상기 서브세트가 상기 전하 이동 경로로부터 연결 해제가 되도록 상기 위상 스위치들의 서브세트를 선택적으로 개방하도록 구성되며, 이를 통해 상기 전하 이동 경로를 재구성한다.

일부 실시 예들에서, 상기 복수의 커패시터들 내부의 각각의 커패시터는, 그것의 제 2 단자에서, 복수의 위상노드들 중 대응하는 하나에 접속된다. 다른 실시 예에서는, 상기 커패시터들의 적어도 두 개는 공통의 위상노드에 접속된다.

다른 실시 예들은 복수의 커패시터들을 구비하는 제 2 캐스케이드 멀티플라이어 스위치드 커패시터 네트워크도 또한 포함하며, 각각의 커패시터들은 상기 제 1 캐스케이드 멀티플라이어 스위치드 커패시터 네트워크 내부의 하나의 커패시터에 대응하며, 그 결과로 제 1 및 제2 캐스케이드 멀티플라이어 스위치드 커패시터 네트워크들은 전기적으로 병렬이다. 이러한 실시 예들에서 제 1 및 제2 캐스케이드 멀티플라이어 스위치드 커패시터 네트워크들 내부에서 대응하는 커패시터들은 캐스코드(cascoded) 스택 스위치들 사이의 공통 노드들에게 접속된다.

일부 실시 예들은 인접하는 커패시터들 사이에 캐스코드 스택 스위치들을 포함한다. 이들 중에는 인접한 커패시터들 사이의 노드에서 전압을 제어하기 위해서 전압 클램프를 포함하고 있는 실시 예들도 있으며, 인접한 커패시터들 사이의 하나의 노드에서 전압 제어를 위한 전압 조정기(voltage regulator)를 포함한 실시 예들도 있다.

추가 실시 예들은 상기 앞서 말한 특징들의 임의의 조합을 포함한다.

다른 측면에서, 본 발명은 제 1 전압을 제 2 전압으로 변환하기 위한 장치를 특징으로 한다. 이러한 장치는 선택 가능한 변환 이득을 구비하는 재구성 가능한 스위치드 커패시터 파워 컨버터를 포함한다. 복수의 스위치 소자들을 포함하는 상기 재구성 가능한 스위치드 커패시터 전력 컨버터는 커패시터들을 서로 및/또는 연속적인 상태들에 있는 상기 제 1 또는 제 2 전압에 전기적으로 상호연결(interconnect) 하도록 구성하였다. 이러한 스위치 소자들은 상기 스위치 소자들을 통해 서로에게 적어도 일부 커패시터들을 상호 연결하도록(interconnect) 구성된다. 상기 장치는 스위치드 커패시터 전력 컨버터가 제 1동작 모드와 제 2동작 모드 사이에서 전이되도록 하는 제어기도 포함한다. 상기 제어기는 제 1모드에서 제 2모드로 전이할 때 나타나는 전기적 과도현상(transient)을 최소화하도록 구성된다. 결과적으로, 제 1 동작 모드에서, 상기 재구성 가능한 스위치드 커패시터 전력 컨버터는 제 1 변환이득으로 동작하며, 제 2 동작 모드에서, 상기 재구성 가능한 스위치드 커패시터 전력 컨버터는 제 2 변환이득으로 동작한다.

일부 실시 예들에서 상기제어기는 재구성 가능한 스위치드 커패시터 전력 컨버터의 스위칭주파수를 상승시킴으로써 제 1 모드에서 제 2 모드로의 전이 시간동안의 전기적 과도현상을 최소화하도록 구성된다. 이들 중 실시 예들은 프리-차지(pre-charged)된 바이패스 커패시터와, 프리-차지된 바이패스 커패시터 내부에서 변환되도록 구성된 상기 제어기를 포함한다. 또한 이런 실시 예에서 상기 제어기는 양방향(bidirectional) 전류 리미터(current limiter)를 사용하여 입력전류를 억압하도록 구성되어 있을 뿐만 아니라 상기 제어기는 온-저항(on-resistance)을 변조(modulating)함으로써 입력전류를 억압하도록 구성된다.

또 다른 실시 예에서 상기 제어기는 제 1 모드에서 동작중지 다음의 과도시간 및 제 2 모드에서 동작시작 이전의 전이 시간 동안 제 2 모드동안 상기 커패시터들이 도달하는 값들의 방향으로 적어도 하나 이상의 커패시터들에 걸리는 전압을 슬루잉(slewing)함으로써 전기적 과도현상을 최소화하도록 구성된다. 이들 실시 예들 중에는 상기 제어기가 전압 레귤레이터(regulator)를 이용하여 상기 전압을 슬루(slew) 하도록 구성되며, 상기 제어기가 전류 레귤레이터(regulator)를 사용하여 상기 전압을 슬루(slew)하도록 구성되고, 상기 제어기가 출력전류를 이용하여 상기 전압을 슬루(slew)하도록 구성된다.

다른 실시 예들에서, 상기 제어기는 제 1 모드에서 동작을 중지하고 이전의 제 2 모드에서의 동작을 시작하는 전이 시간 동안에 과도현상을 최소화하도록 구성된다.

다른 실시 예들은 앞서 말한 특징들의 조합을 포함한다.

다른 측면에서 본 발명은 제1전압을 제2전압으로 변환하기 위한 장치를 특징으로 한다. 이러한 장치는 선택 가능한 변환이득을 구비하는 재구성 가능한 스위치드 커패시터 전력 컨버터를 포함한다. 이 재구성 가능한 스위치드 커패시터 전력컨버터는 커패시터들을 서로 및/또는 상기 연속적인 상태들에 있는 제 1 또는 제 2 전압에 전기적으로 상호 연결하도록 구성된 스위치 소자들을 포함한다. 상기 스위치 소자들은 상기 스위치 소자들을 통해 적어도 일부의 커패시터들을 서로 상호 연결하도록 구성된다. 또한 상기 장치는 재구성 가능한 스위치드 커패시터 전력 컨버터가 제 1 동작모드와 제 2 동작모드사이에서 전이되도록 하는 제어기를 포함한다. 이 제어기는 상기 제 1 동작모드에서 상기 제 2 모드로 전이하는 시간 동안의 전기적 과도현상을 최소화하도록 구성된다. 상기 재구성 가능한 스위치드 커패시터 전력 컨버터는 제 1 변환이득으로 동작하며 제 2 모드에서는 제 2 변환이득으로 동작한다. 본 발명의 이러한 양상에서 상기 제어기는 상기 재구성 가능한 스위치드 커패시터 전력 컨버터의 스위칭주파수를 상승시킴으로써 제 1 모드에서 제 2 모드로 전이하는 시간 동안의 전기적 과도현상을 최소화하거나, 프리-차지된 바이패스 커패시터 내부에서 스위치하기 위해, 또는 양방향 전류 리미터(limiter)와 변조된 온-저항(on-resistance)중 하나를 사용함으로써 입력전류를 억제하도록 구성되어 있다.

본 발명은 스위치드 커패시터 전력 컨버터의 변환이득을 변경하기 위한 커패시터 네트워크의 신규한 구성을 제공하는 장점이 있다.

또한, 본 발명은 스위치드 커패시터 전력 컨버터가 동작 중 변환이득 변경에서 발생하는 과도 전류 및 전압을 최소화하는 장점이 있다.

도 1A-1B는 알려진 재구성 가능한 스위치드 커패시터 회로들을 도시한다;

도 2는 공유된 위상 노드들을 구비하는 단-위상(single-phase)캐스케이드 멀티플라이어와 결합된 재구성 블록을 도시한다;

도 3A는 도 2에서 재구성 블록의 특정 구현을 도시한다;

도 3B는 캐스코드 스위치들을 사용하고 있는 도 2에서 재구성 블럭의 특정 구현을 도시한다;

도 4는 분리된 위상 노드들을 구비하는 단-위상(single-phase) 캐스케이드 멀티플라이어를 도시한다.;

도 5는 공유의 위상 노드들(phase nodes)을 구비하는 듀얼-위상(dual-phase) 캐스케이드 멀티플라이어와 결합된 재구성 블럭을 도시한다.;

도 6은 분리된 위상 노드들을 구비하는 듀얼-위상(dual-phase) 멀티플라이어를 도시한다.

도 7A-7B는 과도 입력 전류를 억제하기 위해 소용량의 프리-차지(pre-charged)된 커패시터를 이용하는 특정 구현을 도시한다.;

도 8 은 양방향 입력 전류 제한 스위치(current-limited switch)의 특정한 구현을 도시한다.

도 9A-9C는 MOSFET의 상기 온-저항(on-resistance)을 변조하는 세 가지 서로 다른 방법을 도시한다.;

도 10A는 도 5에서 듀얼-위상(dual-phase) 캐스케이드 멀티플라이어와 결합된 dc노드 제어기를 도시한다.;

도 10B는 전압 클램프들을 이용한 dc 노드 제어기의 특정한 구현을 도시한다.;

도 10C는 전압 레귤레이터들을 이용한 dc 노드 제어기의 특정 구현을 도시한다.;

도 11은 도 2에서 단-위상(single-phase) 캐스케이드 멀티플라이어와 결합된 커패시터 프리-차지(pre-charge) 회로를 도시한다.;

도 12는 상기 구 변환이득과 상기 새로운 변환이득 사이의 고주파 동작 주기를 도시한다.;

도 13은 상기 구 변환이득과 상기 신 변환이득 사이의 전이 구간을 도시한다.;

도 14A-14B는 전압 레귤레이터들을 이용하여 전이 구간 동안 상기 커패시터 전압을 슬루잉(slewing)하는 다양한 방법들을 도시한다.’

도 15A- 15C는 전류 레귤레이터를 이용하여 전이 구간 동안 상기 커패시터 전압을 슬루잉(slewing)하는 다양한 방법들을 도시한다.;

도 16은 전이 구간 동안의 특정 스위칭 방법을 도시한다.

도 2는 공유된 위상 노드들을 구비하는 단-위상(single-phase)캐스케이드 멀티플라이어와 결합된 재구성 블록을 도시한다;

도 3A는 도 2에서 재구성 블록의 특정 구현을 도시한다;

도 3B는 캐스코드 스위치들을 사용하고 있는 도 2에서 재구성 블럭의 특정 구현을 도시한다;

도 4는 분리된 위상 노드들을 구비하는 단-위상(single-phase) 캐스케이드 멀티플라이어를 도시한다.;

도 5는 공유의 위상 노드들(phase nodes)을 구비하는 듀얼-위상(dual-phase) 캐스케이드 멀티플라이어와 결합된 재구성 블럭을 도시한다.;

도 6은 분리된 위상 노드들을 구비하는 듀얼-위상(dual-phase) 멀티플라이어를 도시한다.

도 7A-7B는 과도 입력 전류를 억제하기 위해 소용량의 프리-차지(pre-charged)된 커패시터를 이용하는 특정 구현을 도시한다.;

도 8 은 양방향 입력 전류 제한 스위치(current-limited switch)의 특정한 구현을 도시한다.

도 9A-9C는 MOSFET의 상기 온-저항(on-resistance)을 변조하는 세 가지 서로 다른 방법을 도시한다.;

도 10A는 도 5에서 듀얼-위상(dual-phase) 캐스케이드 멀티플라이어와 결합된 dc노드 제어기를 도시한다.;

도 10B는 전압 클램프들을 이용한 dc 노드 제어기의 특정한 구현을 도시한다.;

도 10C는 전압 레귤레이터들을 이용한 dc 노드 제어기의 특정 구현을 도시한다.;

도 11은 도 2에서 단-위상(single-phase) 캐스케이드 멀티플라이어와 결합된 커패시터 프리-차지(pre-charge) 회로를 도시한다.;

도 12는 상기 구 변환이득과 상기 새로운 변환이득 사이의 고주파 동작 주기를 도시한다.;

도 13은 상기 구 변환이득과 상기 신 변환이득 사이의 전이 구간을 도시한다.;

도 14A-14B는 전압 레귤레이터들을 이용하여 전이 구간 동안 상기 커패시터 전압을 슬루잉(slewing)하는 다양한 방법들을 도시한다.’

도 15A- 15C는 전류 레귤레이터를 이용하여 전이 구간 동안 상기 커패시터 전압을 슬루잉(slewing)하는 다양한 방법들을 도시한다.;

도 16은 전이 구간 동안의 특정 스위칭 방법을 도시한다.

캐스케이드 멀티플라이어의 여러 실시 예들을 설명하기 전에, 개념 설명에서의 명확성을 높이기 위한 노력으로, 본 발명에서는 때때로 특정 캐스케이드 멀티플라이어들 혹은 스위치드 커패시터 회로에 대한 참조가 이루어진다. 이러한 참조는 단지 예시적인 것에 지나지 않으며 제한하는 것으로 해석되어서는 안 된다는 것을 이해해야 한다. 여기에서 제공된 설명을 읽은 후에, 당해 기술분야의 통상의 지식을 가진 자는 여기에 기술된 특정한 캐스케이드 멀티플라이어들과 스위치드 커패시터 회로들에 대한 개념들을 어떻게 적용할 것인지를 이해할 것이다.

본 발명에서 때때로 참조되는 것은 특정 변환 이득뿐만 아니라 특정 입력전압들과 출력전압들에 관한 것이라는 것을 이해해야 한다. 이러한 참조들은 단지 예시적인 것이며 제한하는 것으로 해석되어서는 안 된다는 것을 이해해야 한다.

참조는 또한 때때로 본 발명에서 특정 적용들을 구성할 수 있다. 이러한 참조들은 단지 예시적인 것이며 본 발명에서 특정 적용으로 설명된 개념을 제한하는 것으로 간주되지 않아야 한다.

따라서, 비록 여기에서 특정 회로들 또는 특정 적용 또는 특정 전압의 맥락으로 본 발명의 개념을 설명한다 하더라도, 당해 기술 분야의 통상의 지식을 가진 자들은 상기 개념들이 다른 회로들 또는 적용들 또는 전압들에 동일하게 적용된다는 것을 이해할 것이다.

본 발명에서 설명된 장치는 스위치드 커패시터 전력 컨버터가 상기 컨버터 노드들에서 과도 전류 및/또는 전압을 최소화하는 방법으로 동작 중에 상기 변환 이득을 변경하기 위한 하나의 방법을 제공한다. 이것은 넓은 입력 및/혹은 출력전압범위를 지원하고, 및 상기 컨버터에서 저-전압 트랜지스터를 사용하는 높은 변환-이득의 스위치드 커패시터 전력 변환기에 필요하다. 상기 장치는 구현의 유연성 및 용이성을 위해 변환 이득에서의 상기 변경이 상이한 스위치드 커패시터 스테이지들과 스테이지들의 조합들을 포함하는 것을 허용한다. 뿐만 아니라. 본 발명에서 제안된 방법은 스텝-업(step-up) 구성에도 적용할 수 있다는 것을 이해해야 한다.

도 2는 캐스케이드 멀티플라이어(30)가 소스(26)로부터 입력전압(VI)을 받아서 출력전압(VO)을 부하(RL)로 전달하는 것을 도시한다. 소스(26)와 부하(RL)는 캐스케이드 멀티플라이어(30)의 일부가 아니므로 그들은 점선으로 도시된다. 캐스케이드 멀티플라이어(30)는 단-위상(single-phase)의 대칭적인 캐스케이드 멀티플라이어이며 커피시터들(C1-C6), 스택스위치들(S1-S7), 그리고 위상 스위치들(S1P-S4P)을 포함한다. 캐스케이드 멀티플라이어(30)에는 6개의 스테이지가 있으며 각 스테이지들은 커패시터와 스위치를 포함한다. 상기 제 1 스테이지는 상기 스택스위치(S1)와 상기 커패시터 (C1); 상기 제 2 스테이지는 상기 스택스위치(S2)와 상기 커패시터(C2)를 포함한다; 기타 등등. 상기 스택스위치(S7)는 커패시터와 연관되지 않는다. 이 실시 예에서는, 6개의 스테이지들이 있기 때문에 최대 변환이득은 7이다.

캐스케이드 멀티플라이어(30)에서, 상기 위상 스위치들(SP1-SP4)은 제 1 및 제 2 위상노드들(P1, P2)에서 상기 전압들을 발생시킨다. 제 1 위상 노드(P1)는 커패시터들(C1, C3, C5)의 음극단자와 결합하고 동시에 제 2 위상 노드는 커패시터들(C2, C4, C6)의 음극단자들과 결합한다. 본원에서 사용된 바와 같이, 입력전압(VI ) 및 출력전압(VO)에 가장 가까운 커패시터들은 외부 커패시터들(outer capacitors)로 기술되는 반면 상기 잔여 커패시터들은 내부 커패시터들(inner capacitor)로 기술된다. 결과적으로, 캐스케이드 멀티플라이어(30)에서 커패시터들(C1,C6)은 외부 커패시터들이고 반면에 커패시터들(C2-C5)은 내부 커패시터들이다.

제어기(24)는 변환 이득 신호(M)을 수신하고 경로(28) 상의 상기 캐스케이드 멀티플라이어(30)에 제어신호들을 공급한다. 상기 제어 신호는 상기 스택 스위치들(S1-S7)과 위상 스위치들(SP1-SP4)을 특정한 순서로 활성화 및 비활성화시켜, 상기 캐스케이드 멀티플라이어(30)는 특정한 주파수로 반복되는 두 가지의 동작 상태들로 특징을 이룬다. 예를 들면, 제 1 상태 혹은 상태 1 동안에, 상기 홀수 스택 스위치들(S1, S3, S5, S7)과 홀수 위상 스위치들(S1P, S3P)은 폐쇄되고 반면에 짝수 스택 스위치들(S2, S4, S6)과 짝수 위상 스위치들(S2P, S4P)은 개방된다. 이와 반대로 제 2 상태 혹은 상태 2 동안 홀수 스택 스위치들(S1, S3, S5, S7)과 홀수 위상스위치들(S1P, S3P)은 개방되며 반면에 짝수 스택 스위치들(S2, S4, S6)과 짝수 위상 스위치들(S2P, S4P)은 폐쇄된다. 그 결과로, 상기 캐스케이드 멀티플라이어(30)는 상기 입력전압(VI)보다 7배 낮은 출력전압 (VO)을 발생시킨다. 변환 이득을 변경하기 위해, 제어기(24)와 연동하는 재구성 블럭(22)은 단자들(A1-A3)을 통하여 상기 제 1 및 제 2 상태에 있는 커패시터(C1-C6)사이의 상기 결합들을 변경한다. 또한, 상기 제어기(24)는 단자(B1)를 통하여 상기 재구성 블록(22) 내부에 있는 상기 스위치들을 제어한다.

일반적으로, 상기 변환이득을 감소시키는 것은 상기 단계들 중 적어도 하나의 단계의 제거와 더 나아가, 상기 커패시터들(C1-C6)중 적어도 하나의 커패시터를 제거하는 것을 필요로 한다. 대조적으로, 상기 변환이득을 증가시키는 것은 적어도 하나의 단계의 추가와 더 나아가, 상기 커패시터들(C1-C6) 중 적어도 하나의 커패시터를 추가하는 것을 필요로 한다. 불행하게도, 상기 캐스케이드 멀티플라이어(30)에서, 상기 커패시터들(C1-C6)은 상기 제1 위상 노드(P1)와 상기 제 2 위상 노드(P2) 중 하나와 공유하고 있기 때문에 그 중에서 어떠한 것도 완벽히 제거하거나 분리하는 것은 불가능하다. 하지만 상기 커패시터들(C1-C6) 중 그 어떤 것 혹은 그들 전부는 상기 전류 흐름 경로(current flow path)의 연결을 해제함으로써 상기 전류 흐름 경로(current flow path)에서 제거될 수 있다. 예를 들면, 상기 스택 스위치들(S1,S2)을 개방함으로써, 상기 커패시터(C1)는 전하 이동 경로에서 제거된다. 주어진 상기 스택 스위치들(S1-S7)의 직렬 연결 특성(nature)으로, 전하이동 경로는 상기 스택 스위치들 (S1,S2)을 단순히 활성화함으로써 끊어진다. 그러므로 상기 재구성 블록(22)은 상기 적당한 전하 이동 경로를 유지하면서 상기 분리된 커패시터(C1) 주위에 바이패스 경로를 형성하는 스위치들을 포함한다.

변환이득을 증가시키기 위해서는, 이전에 제거된 커패시터(예, C1)가 전하 이동 경로에 다시 추가될 수 있다. 이것을 수행하기 위해, 상기 이전에 제거된 커패시터(예, C1)의 양극 단자에 있는 상기 한 쌍의 스택스위치들(예, S1, S2)은 상기 대응하는 바이패스 스위치가 비활성화될 때 다시 활성화된다. 일반적으로 바이패스 스위치들의 수와 상기 캐스케이드 멀티플라이어(30)와 상기 재구성블록(22) 사이의 연결 수는 상기 변환이득의 범위에 의존한다.

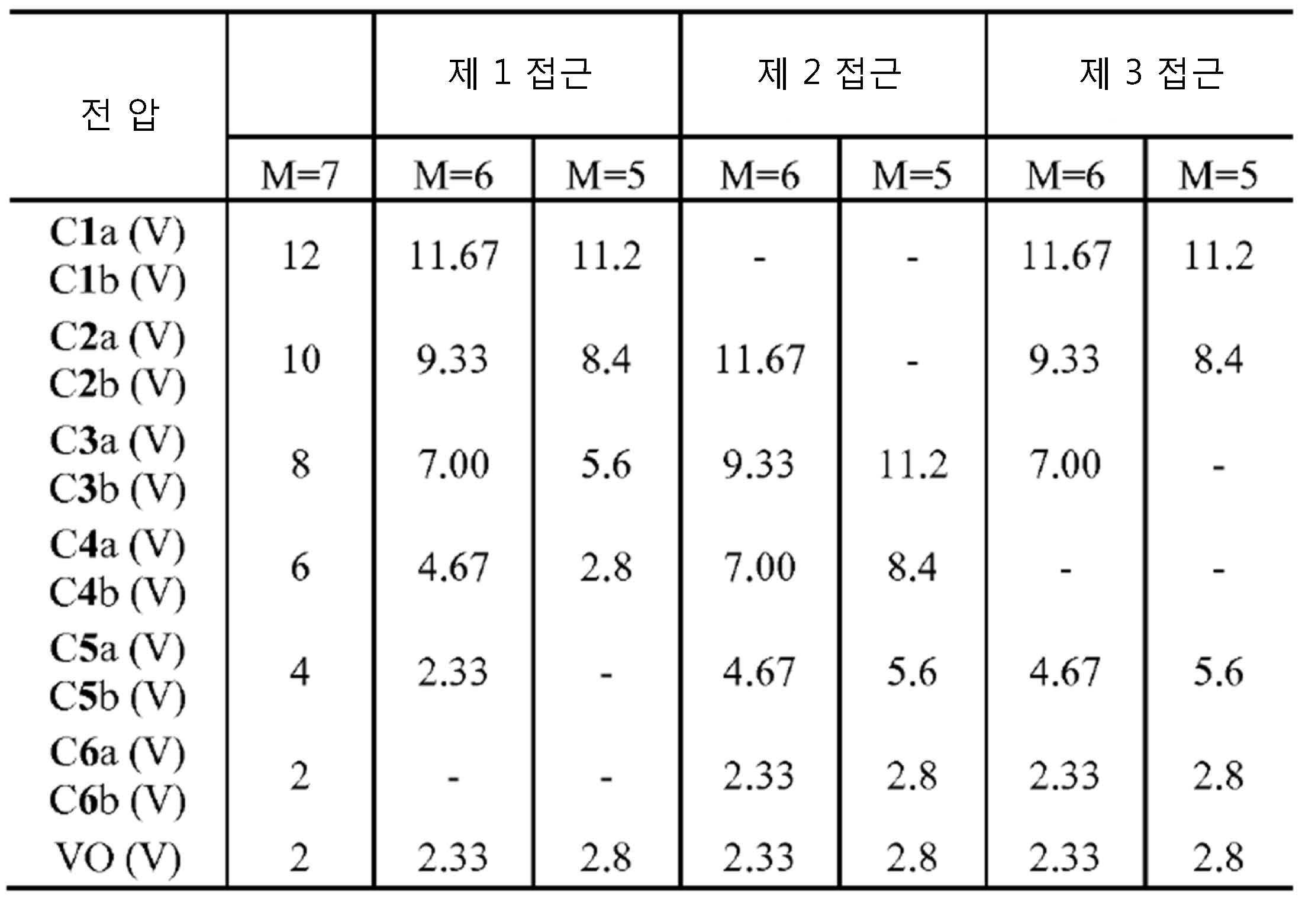

표 1 은 상기 다양한 캐스케이드 멀티플라이어(30) 노드들과 상기 5, 6, 7의 변환이득을 지원하는 상기 재구성 가능한 블록(22)의 단자(A1,A2,A3) 사이의 세 가지 가능한 연결들의 구성을 요약하여 보여준다. 표1에 나타난 세 가지의 조합과 변형으로 이루어진 더 많은 구성은 더 많은 단자들, 더 많은 결합들, 및 더 많은 복잡성의 댓가로 가능하다. 예를 들어, 상기 제 1 접근 방식과 상기 제 2 접근 방식은 동시에 혹은 교대 방식으로 사용될 수 있다.

제 1 재구성 접근 방식에서는, 상기 마지막 단계에서 시작하는 상기 커패시터들(C1-C6)은 추가되거나 제거된다(예, C5). 제 2 재구성 접근 방식에서는, 상기 제 1 스테이지에서 시작하는 상기 커패시터들(C1-C6)들이 추가되거나 제거된다(예, C1). 마지막으로, 제 3 재구성 접근 방식에서는, 내부 단계에서 시작하는 상기 커패시터들(C1-C6)이 추가되거나 제거된다.(예, C3 및/또는 C4) 표 1에서, 상기 제 3 재구성 접근 동안, 상기 커패시터들(C3, C4)은 인접한 스테이지들에 놓이게 된다. 이러한 특성이 필요조건은 아니지만, 짝의 정수 번호의 커패시터들을 제거하는데 필요한 바이패스 스위치들의 수를 줄이는 장점을 가지고 있다.

도 3A는 단자(A1)에 공통으로 연결되어있고 단자들(A2, A3)에서의 연결을 각각 분리시키는 두 개의 바이패스 스위치들(SA, SB)을 포함하는 상기 재구성 블록 22의 특정한 구현을 도시한다. 상기 재구성 블록(22)과 상기 재구성 블록(22)에 연결된 상기 스택 스위치들(S1-S7)에서의 상기 스위치들은 상기 스위치 단자들에 걸리는 전압의 극성과 크기에 상관없이 개방하거나 폐쇄하는 능력을 가지고 있어야 한다. 이것은 스위치로서 표준 다이오드의 사용을 배제하고, 그 대신에, 릴레이들 또는 트랜지스터들의 사용을 요구한다.

표 2는 상기 세 가지 다른 재구성 접근 방식들을 위한 도 (2-3A)에서의 상기 바이패스 스위치들(SA, SB)과 상기 상부 스위치들(top switches)(S1-S7) 모두의 동작 상태를 도시하며, 여기서 M은 변환이득과 동일하다. 예를 들면, 상태 1 에서, “A”라고 명시된 상기 스위치들은 “B”라고 명시된 상기 스위치들이 폐쇄되어 있는 동안에 개방된다. 상태 2 에서, “A”라고 지정된 상기 스위치들은 “B”로 지정된 상기 스위치들이 폐쇄되어 있는 동안에 개방된다. “O”로 지정된 상기 스위치들은 두 가지 동작 상태 모두에서 개방된다. 표 2 에서 다음과 같은 예를 도시 한다: 즉, 변환이득 6에서는, 상기 커패시터(C1)가 상기 제 2 접근 방식에서 제거되는 동안에 상기 커패시터(C6)가 상기 제 1 접근방식에서 제거된다. 변환이득 5에서는, 상기 커패시터들(C1-C2)이 상기 제 2 접근 방식에서 제거되는 동안에 상기 커패시터들(C5-C6)은 상기 제 1 접근방식에서 제거된다. 변환이득 5의 상기 제 3 접근방식에서 상기 커패시터들(C3-C4)은 제거 된다

트랜지스터들을 스위치들로서 사용하는 것은 상기 트랜지스터의 드레인-소스(drain-to-source) 전압 정격 및 그것의 백 게이트(back-gate) 전압 바이어스와 같은 추가적인 고려사항을 도입한다. 상기 캐스케이드 멀티플라이어(30)에서, 개방시 상기 위상 스위치들(S1P-S4P)은 최대 드레인-소스(drain-to-source)전압을 상기 출력전압(VO)과 동일한 것으로 본다. 대조적으로, 상기 스택스위치들(S1-S7)은 개방 시 최대 드레인-소스(drain-to-source) 전압을 상기 출력전압(VO)의 2배와 동일한 것으로 본다.

상기 바이패스 스위치들(SA, SB)에 관해서 본다면, 상기 제 1 및 제 2 재구성 접근방식들에서, 상기 바이패스 스위치들(SA, SB)은 개방 시 최대 드레인-소스(drain-to-source) 전압을 각각 출력전압(VO)의 2배 및 출력전압(VO)의 3 배와 동일하게 본다. 그러나 상기 제 3 구성에서는, 상기 바이패스 스위치들(SA, SB)은 최대 드레인-소스(drain-to-source) 전압을 상기 커패시터들(C1-C6) 중의 어떤 것이 제거되는지에 크게 좌우된다고 본다.

예를 들어, 상기 제 3 접근 방식에서, 표 2에 도시된 바와 같이, 상기 바이패스 스위치(SA)는 노드들(N2, N5)에 걸쳐 연결된다. 상기 바이패스 스위치(SA)는 변환이득이 7일때, 상기 출력전압(VO)의 4배와 동일한 최대 드레인-소스(drain-to-source)전압에 노출된다. 다시 말해서, 상기 바이패스 스위치들(SA, SB)을 구현하는 상기 트랜지스터들은 상기 위상 스위치들(S1P-S4P)과 스택 스위치들(S1-S7)을 구현하는 것보다 더 높은 드레인-소스(drain-to-source) 전압 정격(rating)을 가져야 한다.

도 3B는 상기 재구성 블록(22)의 또 다른 구현을 도시하며, 각각의 바이패스 스위치(예, SA)는 각각의 트랜지스터들에서 보여지는 상기 최대 드레인-소스(drain-to-source) 전압을 본질적으로 이등분하는 두 개의 캐스코드 트랜지스터들(예, SA1, SA2)로 구성된다. 상호절충(Tradeoff)은 더 높은 복잡성과 더 많은 수의 트랜지스터들로 인한 더 낮은 효율이다. 또 다른 고려사항은, 상기 드레인 또는 소스 전압과 관련된 상기 트랜지스터의 백-게이트(back-gate) 전압이다.

상기 스택 스위치들(S1-S7)의 공통-모드 전압은 상기 스택 스위치(S7)에서 상기 스택 스위치(S1)로 이동시킬 때 상기 출력전압(VO)의 정수 배로 증가한다. 상기 스택 스위치들(S1-S7) 각각의 상기 백-게이트 전압을 그들의 대응하는 소스 전압으로 바이어싱(biasing)하는 것은 상기 백-게이트 전압을 접지(NMOS 트랜지스터들 용) 또는 입력전압(PMOS 트랜지스터용)에 바이어싱(biasing)하는 것과 비교하여, 주어진 온-저항을 위한 그것들의 크기를 줄인다. 상기 백-게이트 전압을 접지(NMOS 트랜지스터들 용) 또는 입력전압(PMOS 트랜지스터용)에 바이어싱(biasing)하는 것과 비교된다. 후자의 바이어싱(biasing) 방식은 상기 트랜지스터 임계 전압에 중요한 백-게이트 효과로 인해 주어진 트랜지스터 크기와 게이트-드라이브 전압 레벨을 위한 유효 온-저항을 감소시킨다. 하지만 다이 영역(die area)또는 효율성이 크게 중요하지 않다면, 이 바이어싱(biasing) 방식은 상기 백-게이트 효과를 제거하거나 최소화하는 시도보다 덜 복잡하다.

변환이득이 감소할 때 상기 스택 스위치들(예, 제 1 접근 방식에서의 S6, S7)의 일부는 표2에서처럼 두 가지 동작 상태 모두에서 개방된다. 만약 상기 백-게이트 연결이 더 낮은 드레인 및 소스 전압들로 스위치(switch) 되지 않는 한 이런 개방된 스택 스위치들(예, 제 1 접근 방식에서의 S6, S7)에 걸리는 전압 극성은 반전될 것이며 이로 인해 트랜지스터 바디 다이오드는 도통될 것이다. 이것은 상기 재구성 동안 제거된 상기 트랜지스터들(예, C6)이 그들의 전압을 유지하거나 누설로 인해 시간이 경과함에 따라 방전하는 것에 상관없이 사실이다. 스위치가 개방되어 있어야 할 때 상기 트랜지스터의 바디 다이오드를 도통하게 하는 것은 필연적으로 잘못된 동작을 초래한다.

예를 들어, 상기 캐스케이드 멀티플라이어(30)가 상기 제 1 재구성 접근 방식과 상기 스택 스위치들(S1-S7)을 사용하여 변환이득 7에서 6으로 변하는 방향으로 재구성한다고 가정하는 것은 NMOS 트랜지스터들을 사용하는 것으로 구현된다. 상기 스택 스위치(S6)는 그것의 백-게이트 연결을 상태 2 동안 상기 노드(N6)로부터 노드(N5)로 이동시켜야 하며 동시에 상기 커패시터(C6)는 상기 출력전압(VO)과 동일한 그것의 이전 전압을 유지한다. 만약 상기 커패시터(C6)가 천천히 시간이 경과함에 따라 제로 볼트까지 방전한다면, 그때 상기 스택 스위치(S6)는 상기 노드(N6)에 연결된 백-게이트를 유지해야 하며 동시에 상기 스택 스위치(S7)는 그것의 백-게이트 연결을 상기 출력전압(VO)에서 상기 노드(N6)로 이동시켜야 한다.

상기 캐스케이드 멀티플라이어(30)을 위한 상기 제 3 재구성 접근 방식을 구현하는 것은 상기 변환이득이 홀수의 정수로 변경될 때 매우 복잡할 수 있다. 이것은 상기 커패시터들(C1-C6) 각각의 음의 단자가 공유 위상 노드(shared phase node)에 항상 연결되어 있기 때문이며, 및 대칭 캐스케이드 멀티플라이어에서는, 인접한 스테이지들에서의 커패시터들은 반대 위상에서 동작하거나 혹은 반대 위상 노드들과 결합한다. 1씩 변환-이득을 감소시키기 위해 내부 커패시터를 제거하는 것은 인접 스테이지 커패시터들이 상기 동일 위상 노드를 공유하는 결과를 초래한다. 비록 이것이 상기 잔여 커패시터들의 스테이지 순서를 플립핑(flipping) 함으로써 해결될 수 있지만, 그 결과는 고-전압 바이패스 스위치들뿐만 아니라 고도의 스위치 제어 및 트랜지스터 백-게이트-스위칭(back-gate-switching)의 복잡성을 초래한다.

예를 들어, 상기 커패시터(C4)를 제거함으로써 상기 변환-이득이 7에서 6으로 변경되면, 상기 캐스케이드 멀티플라이어(30)의 토폴로지(topology)는 수많은 변경들을 함으로써 유지될 수도 있다. 상기 캐스케이드 멀티플라이어(30)에 적합한 변경들은 다음과 같다: (1) 상기 스택 스위치들(S4, S5, S7)의 개방; (2) 상기 스택 스위치(S6)를 “B”에서 “A”로 지정하고 플립핑(flipping) 하는 것; (3) 상기 노드(N5) 및 상기 출력전압(VO) 사이에 제 1 바이패스 스위치를 연결하는 것; (4) 상기 노드들(N3, N6) 사이에 제 2 바이패스 스위치를 연결하는 것; 및 (5) 상기 제 1 및 제 2 바이패스 스위치들을 “B”로 지정하고 할당하는 것. 반면에, 인접한 스테이지의 여러 쌍으로 구성된 내부 커패시터들의 제거가 상기 토폴로지(topology)를 유지하기 때문에 상기 변환이득을 짝수-정수로 증가하는 것으로 변경하는 것이 구현에 훨씬 용이하다.

도 4의 캐스케이드 멀티플라이어(32)는 상기 캐스케이드 멀티플라이어(30)의 다양성을 도시한다. 결과적으로, 상기 캐스케이드 멀티플라이어(32)는 커패시터들(C1-C6)과 스택 스위치들(S1-S7)을 포함하는 단-위상(single-phase) 대칭 캐스케이드 멀티플라이어이다. 그러나, 상기 캐스케이드 멀티플라이어(30)와는 다르게, 분리된 위상 노드들(P1-P6)이 상기 대응하는 커패시터들(C1-C6)의 음극 단자에 연결된다.

제어기(24)는 변환이득 신호(M)을 수신하고 경로(28)에 있는 상기 캐스케이드 멀티플라이어 (32)에 제어 신호들을 제공한다. 상기 제어 신호들은 상기 스택 스위치들(S1-S7)과 상기 위상 스위치들(SP1-SP12)을 특정한 순서로 활성화시키고 비활성화시킴으로써, 상기 캐스케이드 멀티플라이어(32)가 특정한 주파수로 반복되는 두 가지의 동작 상태들로 특징을 이룬다. 제 1 상태 또는 상태 1 동안에, 상기 홀수 스택 스위치들( S1, S3, S5, S7) 및 상기 홀수 위상 스위치들( S1P . . . S11P)은 폐쇄되어 있고 동시에 상기 짝수 스택 스위치들(S2, S4, S6) 및 상기 짝수 위상 스위치들(S2P . . . S12P)은 개방되어 있다. 대조적으로, 제 2 상태 혹은 상태 2에서는, 상기 홀수 스택 스위치들(S1, S3, S5, S7)과 상기 홀수 위상 스위치들( S1P . . . S11P)은 개방되어 있고 동시에 상기 짝수 스택 스위치들(S2, S4, S6)과 상기 짝수 위상스위치들(S2P . . . S12P)은 폐쇄되어 있다. 결과적으로, 상기 캐스케이드 멀티플라이(32)는 상기 입력전압(VI)보다 7배 더 낮은 출력전압 (VO)를 발생시킨다.

상기 위상 노드들(P1-P6)이 분리되어있기 때문에, 상기 제어기(24)는 상기 캐스케이드 멀티플라이어(32)를 재구성할 수 있고, 이렇게 경로(28) 상의 상기 제어 신호들을 수정하여 상기 변환이득을 변경할 수 있다. 표 3은 상기 스택 스위치들(S1-S7)의 동작 상태를 도시하고 세 개의 다른 재구성 접근 방식을 위한 상기 캐스케이드 멀티플라이어(32)에서 상기 위상스위치들(S1P-S12P)을 도시한다. 표 2와 같이, 다음의 예는 표 3으로 도시된다: 변환이득 6에서, 상기커패시터(C6)는 상기 제 1 접근방식에서 제거되고, 상기 커패시터(C1)는 상기 제 2 접근방식에서 제거되며, 상기 커패시터(C4)는 상기 제 3 접근방식에서 제거된다. 변환이득 5에서, 상기 커패시터들(C5, C6)은 상기 제 1 접근방식에서 제거되고, 상기 커패시터들(C1, C2)은 상기 제 2 접근방식에서 제거되며, 상기 커패시터들(C3, C4)은 상기 제 3 접근 방식에서 제거된다.

상기 커패시터들(C1-C6) 사이에 상기 위상 노드들(P1-P6)을 공유하지 않는 주된 장점은, 고-전압 바이패스 스위치들을 포함하고 있는 분리된 재구성 블록(22)이 도 2의 경우와 같이, 더 이상 필요하지 않다는 것이다. 상기 제거된 커패시터들의 상기 음극 단자들은 상기 캐스케이드 멀티플라이어(30)에서와 같이 상기 양극 단자 대신에 연결 해제된다. 상기 위상 스위치들(SP1-SP12)은 상기 커패시터들의 연결을 해제하는 수단으로 제공되며 동시에 상기 스택 스위치들(S1-S7)은 바이패스 경로를 제공한다.

상태 1에서는, “A”로 지정된 상기 스위치들은 폐쇄되며 동시에 “B”로 지정된 상기 스위치들은 개방된다. 상태 2에서는, “A”로 지정된 스위치들은 개방되며 동시에 “B”로 지정된 스위치들은 폐쇄된다. “O”로 지정된 상기 스위치들은 두 동작 모두에서 개방된다. 별표 “*”로 지정된 상기 항목들은 상기 변환 이득이 7일 때로부터 반전되는 극성 상태를 나타낸다.

예를 들어, 상기 커패시터들(C1, C2)이 제거되었을 때, 상기 변환이득은 5(제 2 재구성 접근방식)와 동일하다. 상기 위상 스위치들(S1P-S4P)은 두 가지 동작 모두에서 개방된 상태로 있으며 반면에 상기 스택 스위치들(S1, S2)은 상기 스택 스위치(S3)와 동일한 상태를 따른다. 이것은 상태 1 동안, 상기 커패시터(C3)의 상기 양극 단자는 상기 세 개의 직렬 연결된 스위치들 (S1-S3)을 통해서 입력전압(VI)에 단락되고, 동시에 스택스위치들(S1-S3)의 동일한 집합은 상태 2동안 개방된다. 이러한 예에서 설명하듯이, 상기 스택 스위치들(S1, S2)을 리퍼포징(repurposing) 하는 것은, 분리된 바이패스 스위치를 사용하는 것보다 더 높은 전도 손실이 발생할 수 있다.

추가로, 상기 제 1 및 제 2 재구성 접근 방식은 제거된 커패시터들이 상기 출력전압(VO) 혹은 상기 입력전압(VI) 사이에서 접지되는 바이패스 커패시터로 쉽게 재사용 되도록 한다. 예를 들어, 상기 제 1 재구성 접근 방식에서, 변환이득이 5와 동일할 때, 상기 커패시터들(C5, C6)은 출력전압(VO)과 접지 사이에서 추가의 바이패스 커패시터들로 역할을 할 수 있다. 이것은 두 가지 상태(즉, 상태 1과 상태 2) 모두에서 상기 스위치들(S6, S7, S10P, S11P)을 폐쇄하고 및 상기 스위치들(S9P, S12P)을 개방함으로써 상기 캐스케이드 멀티플라이어(32)의 정상적인 동작을 간섭하지 않고 행해진다. 이 자유로운 측면의 접근방식의 이점은, 상기 커패시터들(C5, C6)이 추가 회로 없이 알려진 전압으로 프리차지(pre-charged) 되는 것이다.

비슷하게, 상기 제 2 접근방식에서, 변환이득이 5와 동일할 때, 상기 커패시터들(C1,C2)은 상기 입력전압(VI)과 접지 사이에서 추가적인 바이패스 커패시터들로서 역할을 할 수 있다. 이것은 또한 상태 1과 상태 2 모두에서 상기 스위치들(S1, S2, S2P, S3P)을 폐쇄하고 및 상기 스위치들(S1P, S4P)을 개방함으로써 상기 캐스케이드 멀티플라이어(32)의 정상적인 동작을 간섭하지 않고 행해진다. 비록 프리-차지 회로 요건의 결여가 매력적이긴 하지만, 상기 커패시터들(C1, C2)이 상기 변환이득이 증가하는 경우에 상기 캐스케이드 멀티플라이어(32)에 재연결될 때 그들의 정상 상태 전압 레벨을 초과되어 바이어스되는 불리한 면이 있다. 상기 재구성이 발생할 때, 상기 캐스케이드 멀티플라이어(32)의 노드들에서 더 큰 과도 전류 및 전압이 있을 수 있다.

상기 위상 노드들(P1-P2)을 분리시키는 것의 또 다른 이점은 상기 스택 스위치들(S1-S7)의 상기 바디 다이오드들(body diodes)이 상기 커패시터들(C1-C6) 중 적어도 하나가 캐스케이드 멀티플라이어(32)에서 제거될 때의 터닝-온에 더 이상 민감하지 않다는 것이다. 이것은 상기 커패시터들(C1-C6) 각각의 양극 단자들은 하나의 상태에서 다음 상태로 변할 때 항상 정확한 상대 전압 레벨과 극성으로 바이어스되기 때문이다. 상기 변환이득은 한 번에 한 단계이상 변하지 않는다는 기본 전제가 있고 및 그 다음의 재구성 단계 전에 상기 전하 이동 경로에 있는 상기 모든 잔여 커패시터들이 그것들의 새로운 정상 상태 전압에 도달하는 것을 허용하는 충분한 정착시간(settling time)이 있다. 이것은 비록 상기 위상스위치들의 상기 백-게이트를 적절히 변경함으로써 극복될 수 있지만, 상기 제거된 커패시터들에서의 상기 위상 노드들이 접지 아래로 구동되는 것과 상기 대응하는 위상 스위치들을 스트레싱하는 것을 방지한다.

상기 분리된 위상 노드들(P1-P6)은 상기 커패시터 스테이지의 순서가 적절한 동작을 유지하기 위해서 플립 될(be flipped) 필요가 없기 때문에 상기 변환이득에서 홀수 정수의 변화를 처리할 수 있는 상기 제 3 재구성 접근방식의 더 간단한 구현을 또한 허용한다. 또한, 특정한 재구성 접근방식이 한번 선택되면, 그 접근방식에 따라 제거되거나 추가되어질 상기 커패시터들만이 분리된 위상 노드들을 필요로 하며 동시에 상기 잔여 커패시터들이 그들의 위상 노드들을 공유하며, 그렇게 함으로써 특히 모든 커패시터들이 상기 스위치드 커패

시터 전력 컨버터 패키지의 외부에 있는 경우 핀 절감 결과가 발생한다.

상기 제거된 커패시터들이 다수의 스위칭 주기(cycles)가 경과하면서 방전되어 제로 전압으로 되는 경우, 제거된 커패시터들의 양극 및 음극 단자들은 상기 출력전압(VO)의 정수 배에 가깝게 바이어스된다. 이러한 이벤트가 발생하면, 상기 위상 노드들(P1-P6)에서의 상기 전압 스트레스들은 상당히 클 수 있다. 상기 전압 스트레스의 크기는 재구성 접근방식에 달렸다. 상기 제 1 재구성 접근 방식의 경우에서, 최대 위상 노드 전압은 심지어 상기 제거된 커패시터가 완전히 방전된 후에도 상기 출력 전압(VO)과 동일하다. 하지만, 이것은 상기 제 2 및 제 3 재구성 접근 방식에서의 사례는 아니다.

상기 제 2 재구성 접근방식에서, 만약 상기 커패시터(C1)가 제거되고 방전된다면, 상기 제 1 위상 노드(P1)에서의 상기 전압은 상기 입력전압(VI)에 근접할 것이다. 상기 위상 스위치 (S1P)가 상기 입력전압(VI)의 5/6과 동일한 최대 드레인-소스 전압으로 노출되며 동시에 상기 위상 스위치(S2P)는 상기 입력전압(VI)과 동일한 최대 드레인-소스 전압으로 노출된다. 그러므로 상기 위상 스위치들(S1P, S2P)을 구현하는 상기 트랜지스터들은 상기 스택 스위치들(S1-S7)을 구현하는 트랜지스터들보다 더 높은 드레인-소스 전압 정격(rating)을 가져야 한다. 추가로, 상기 위상 스위치(S1P)(예, NMOS)의 상기 바디-다이오드가 도통하는 것을 막기 위해서, 그것의 백-게이트는 상기 제 1 위상 노드(P1)에서 상기 출력전압(VO)까지 변경되어야 한다.

비슷한 문제점은 상기 제 3 재구성 접근 방식에 적용된다는 점에서, 상기 커패시터(C3) 혹은 상기 커패시터(C4) 모두 제거되거나 방전된다. 다행히도, 상기 개방된 위상 스위치들(예, C3 사례에서 S5P, S6P)은 상기 제 2 재구성 접근방식과 비교했을 때 더 작은 크기의 전압 스트레스들에게 노출된다.

한 가지 가능한 해결책은 전압 레귤레이터들을 사용하여 상기 제거된 위상 노드들을 상기 출력전압(VO)으로 혹은 근접하게 바이어스를 유지하는 것이 될 수 있다. 이를 달성하기 위해, 상기 위상 노드 전압들(P1-P6)은 몇 개의 스위칭 주기에 걸쳐 감시될 수 있고, 각각의 상기 위상 노드들(P1-P6)에서의 전압 레귤레이터는 상기 출력전압(VO)을 초과하는 전압 편차가 검출이 될 때 인에이블 될 수 있다. 상기 전압 레귤레이터의 태스크는 전압을 유지하는 것이며 선형 레귤레이터들 및 전압 폴로어(followers)들과 같은 회로들을 사용하여 구현될 수 있다.

대안적인 해결책의 일례로는 상기 제거된 커패시터들을 상기 입력전압(VI)과 접지 사이에서 바이패스 커패시터로 재사용하는 기존의 제안을 사용하는 것이다. 하지만, 이 방법은 상기 제 2 재구성 접근방식에 좀 더 적합하다. 두 해결책은 상기 제거된 커패시터들을 제로(0) 볼트보다 다른 전압으로 바이어스하는 수단을 제공한다.

일반적으로, 단-위상(single-phase) 캐스케이드 멀티플라이어는 시간에 맞추어 시프트되는 다수의(multiple) 전하 이동 경로의 특징을 나타내는 다-위상(multi-phase) 구조로 변환될 수 있다. 도 5에서 도시된 바와 같이, 듀얼-위상(dual-phase) 캐스케이드 멀티플라이어 회로(34)는 상기 두 개의 단-위상(single-phase) 캐스케이드 멀티플라이어 회로(30)의 복사본을 병렬로 배치함으로써 구성될 수 있다.

상기 캐스케이드 멀티플라이어(34)는 커패시터들(C1 a - C6 b), 스택 스위치들(S10-S63), 및 위상 스위치들(SP1-SP4)을 포함한다. 일반적으로, 듀얼-위상(dual-phase) 구조에는 2배의 많은 스택 스위치들이 있어야 하지만, 상기 캐스케이드 멀티플라이어(34)에서의 상기 스택 스위치들(S10-S63)은 또한 캐스코드 된다. 캐스코딩으로 인해, 상기 스택 스위치들(S10-S63)의 각각에서 보이는 상기 최대 드레인-소스 전압은 상기 출력전압 (VO)과 동일하다. 상기 스택 스위치들(S10-S63) 및 위상 스위치들(SP1-SP4)은 이제 동일한 트랜지스터들을 사용하여 구현될 수 있다.

추가로, 상기 캐스케이드 멀티플라이어(34)는 상기 캐스케이드 멀티플라이어(30)와 비교하여 두 배 많은 커패시터들을 필요로 한다. 제 1 위상 노드(Pb)는 상기 커패시터들(C1 a-C6 a)의 음극 단자들과 결합하고 동시에 제 2 위상 노드(P2)는 커패시터들(C1 b-C6 b)의 상기 음극 단자들과 결합한다. 상기 위상 스위치들(SP1-SP4)은 상기 제 1 및 제 2 위상 노드들(P1, P2)에 상기 전압들을 발생시킨다. 상기 캐스케이드 멀티플라이어(34)에서 상기 커패시터들(C1 a, C1 b, C6 a, C6 b)은 외부 커패시터들이고, 반면에 상기 잔여 커패시터들은 내부 커패시터들이다.

제어기(24)는 변환이득 신호(M)를 수신하고 경로(28) 상의 상기 캐스케이드 멀티플라이어(34)에 상기 제어 신호들을 공급한다. 상기 제어 신호들은 상기 스택 스위치들(S10-S62) 및 위상 스위치들(SP1-SP4)을 특정 순서로 활성화 및 비활성화시킴으로써, 상기 캐스케이드 멀티플라이어(34)는 특정 주파수에서 반복되는 두 가지 동작의 특징을 나타낸다. 예를 들면, 상태 1 동안에, 상기 홀수 스택 스위치들(S11, S13 . . . S61, S63) 및 홀수 위상 스위치들(SIP, S3P)은 폐쇄되며 그 동안에 상기 짝수 스택 스위치들(S10, S12 . . . S60, S62) 및 짝수 위상 스위치들(S2P, S4P)은 개방된다. 이와 반대로, 상태 2 동안에는, 상기 홀수 스위치들(S11, S13, . . . S61, S63) 및 홀수 위상 스위치들(SIP, S3P)은 개방되고 그 동안에 상기 짝수 스위치들(S10, S12, . . . S60, S62) 및 짝수 위상 스위치들(S2P, S4P)은 폐쇄된다. 그 결과, 상기 캐스케이드 멀티플라이어(34)는 상기 입력전압(VI)보다 7배 더 낮은 출력 전압(VO)을 발생시킨다. 상기 변환이득을 변경하기 위해서는, 상기 제어기(24)와 협력하는 재구성 블록(22)은 단자들 A1-A3를 통해 상기 제 1 및 제 2 상태에 있는 상기 커패시터들(C1 a-C6 b) 사이의 결합을 변경한다. 상기 제어기(24)는 단자 B1을 통해 상기 재구성 블록(22)의 구성을 제어한다.

상기 재구성 블록(22)은 도 3A에서처럼 바이패스 스위치들(SA, SB)을 포함하거나 도 3B에서처럼 캐스코드 바이패스 스위치들(SA1-SB2)을 포함한다. 표 4는 상기 다양한 캐스케이드 멀티플라이어(34) 노드들 및 상기 재구성 블록(22)의 단자들(A1, A2, A3) 사이에서 세 가지 가능한 연결 구성을 요약한다. 상기 지원되는 변환이득은 5, 6 및 7이다. 표 4에 도시된 상기 세 가지 다양성 또는 조합을 포함하는 더 많은 연결 구성들은 더 많은 단자들, 연결들, 및 복잡성을 희생으로 하여 가능하다.

제 1 재구성 접근방식에서, 마지막 단계로부터의 시작은, 상기 커패시터들(C1 a-C6 b)의 일부가 추가되거나 제거된다.(예, C5 a, C5 b, C6 a, C6 b) 제 2 재구성 접근 방식에서, 제 1 단계로부터의 시작은, 상기 커패시터들(C1 a-C6 b)의 일부가 추가되거나 제거된다.(예, C1 a, C1 b, C2 a, C2 b) 마지막으로, 제 3 재구성 접근방식에서, 내부 스테이지로부터의 시작은, 상기 커패시터들(C1 a-C6 b)의 일부가 추가되거나 제거된다.(예, C3 a, C3 b, C4 a, C4 b) 표 4에서, 상기 제 3 재구성 접근방식에서, 상기 커패시터들(C3 a, C3 b, C4 a, C4 b)은 인접한 스테이지들에 놓이게 된다. 이 특성은 필요조건은 아니지만, 짝수 정수 번호의 커패시터들을 제거하는데 사용되는 바이패스 스위치의 수를 줄이는 장점을 가지고 있다.

단-위상(single-phase) 구조에 비해 듀얼-위상(dual-phase) 구조의 한 가지 이점은 상기 바이패스 스위치들(SA, SB)이 개방되면, 그들은 더 낮은 최대 드레인-소스 전압을 경험하며 그것은 상기 출력 전압(VO) 및 두 배의 상기 출력전압(VO)과 각각 동일하다.

표 5는 상기 스택 스위치들(S10-S63)의 동작 상태 및 상기 세 가지 재구성 접근방식들을 위한 상기 바이패스 스위치들(SA, SB)의 동작 상태를 도시한다. 상기 “O”로 지정된 스위치들은 두 동작 모두에서 개방되고, 상기 “C”로 지정된 스위치들은 두 동작 모두에서 폐쇄되며, 상기 “N”으로 지정된 스위치들은 상기 변환이득 신호(M)이 7과 동일할 때 상기 두 상태 각각에서 동일한 동작을 따른다.

사용될 때, 상기 바이패스 스위치는 두 가지 상태 모두에서 폐쇄된다. 상기 변환이득 신호(M)가 5와 동일할 때, 두 상태 모두에서 개방 혹은 폐쇄가 유지될 수 있기 때문에 상기 바이패스 스위치(SA)는 “O+” 로 지정된다. 하지만, 상기 바이패스 스위치(SA)가 상기 바이패스 스위치(SB)와 동기화되어, 상기 개방된 스택 스위치들에 걸리는 상기 최대 드레인-소스 전압은 최소화 된다.

표 5에서, 상기 듀얼-위상(dual-phase) 캐스케이드 멀티플라이어(34)는 단-위상(single-phase) 캐스케이드 멀티플라이어와 연관된 복잡성 없이 상기 제 3 재구성 접근방식으로 상기 변환이득이 홀수-정수로 변경하는 것을 지원할 수 있는 것은 자명하다. 예를 들어, 상기 커패시터들(C1 a-C6 a)은 상기 제 1 위상 노드(P1)를 공유하는 병렬의 6 스테이지들을 포함하는 동시에 상기 커패시터들(C1 b-C6 b)은 상기 제 2 위상 노드(P2)를 공유하는 병렬의 6 스테이지를 포함한다. 이것은 상기 6 스테이지들 각각은 상기 제 1 및 제 2 위상 노드들(P1, P2)과 교대 방식으로 연결된다는 점에서, 상기 단-위상(single-phase) 캐스케이드 멀티플라이어와는 다르다.

정상 동작에서, 상기 커패시터들(C1 a-C6 b) 중 적어도 하나가 제거되면 상기 스택 스위치들(S10-S63) 중 몇 개에 걸리는 상기 전압 극성을 적어도 하나의 동작 상태에서 반전시키는 것은 가능하다. 상기 단-위상(single-phase) 캐스케이드 멀티플라이어(30)에서와 같이, 요구되지 않는 바디 다이오드의 도통을 막기 위해서 상기 스택 스위치들의 백-게이트 전압 스위칭(switching)은 상기 듀얼-위상 캐스케이드 멀티플라이어(34)에서 사용된다. 또한, 다이 영역(die area) 및 전력 손실(power loss)의 댓가로, 상기 스택 스위치들(S10-S63)의 상기 백-게이트는 상기 커패시터들(C1 a-C6 b) 중 적어도 하나가 제거되는 경우마다 접지(NMOS 트랜지스터들을 위한) 혹은 입력전압(PMOS 트랜지스터들을 위한)으로 바이어스 될 수 있다.

도 6은 커패시터들(C5 a, C5 b, C6 a, C6 b)이 분리된 위상 노드들(P5 a, P5 b, P6 a, P6 b)과 결합되는 반면, 상기 잔존 커패시터들(C1 a-C4 a)은 위상 노드(P1)와 공유하고 및 커패시터들(C1 b-C4 b)은 위상 노드(P2)와 공유하는 상기 캐스케이드 멀티플라이어(34)의 다양성을 도시한다.

상기 듀얼-위상 구조는 본질적으로 외부 커패시터들이 사용되는 경우 동등한 변환이득을 가지는 단-위상(single-phase)보다 패키지 핀 수가 더 많기 때문에, 변환 이득 재구성 동안 제거되는 상기 커패시터들을 위해서만 분리된 위상 노드들을 가지는 것은 핀 효율이 향상되는 반면, 위상 노드들을 공유하는 상기 잔여 커패시터들을 갖게 된다.

도 6은 재구성 블록 (22)과 상기 위상 노드들을 분리하는 것을 모두 사용하는 듀얼-위상 캐스케이드 멀티플라이어(36)을 도시한다. 상기 캐스케이드 멀티플라이어(34) 사이의 유사성 때문에, 상기 캐스케이드 멀티플라이어(36)은 도 5의 연결에서 기술한 바와 같이 작동한다. 유일한 차이점은 네 개의 위상 노드들(P5 a-P6 b)을 추가하는 것이다. 상기 변환이득이 5, 6, 혹은 7과 동일할 때, 상기 캐스케이드 멀티플라이어(32)와 관련된 많은 특성들은 유효하다. 예를 들어, 분리된 위상 노드들은 상기 스택 스위치들의 상기 트랜지스터 구현 방법들에서 백-게이트 스위칭의 중요성을 제거한다. 또한, 상기 캐스케이드 멀티플라이어(32)를 위한 상기 제 2 및 제 3 재구성 접근방식에 관해 앞서 논의된 상기 제 1 재구성 접근방식의 장점은 여기에도 적용된다.

일반적으로, 스위치드 커패시터 전력 컨버터의 변환 이득 변경에는 상기 전하 이동 경로에 커패시터들을 제거하거나 추가하는 것을 포함한다. 만약 변환 이득 변경이 컨버터 동작 중에 일어난다면, 이러한 중단(disruptive) 이벤트는 상기 입력전압(VI) 단자 및 상기 출력 전압(VO) 단자를 포함하는 다양한 상기 컨버터 노드들에서 큰 과도 전압 및 전류를 일으키게 된다. 이런 과도 전압 및 전류의 크기와 심각성은 다양한 방법으로 감소시킬 수 있다. 상기 제안된 모든 방법들은 독립적으로 또는 그것의 다양한 조합으로 이용될 수 있다.

도 5에 따르면, 표 6은 각각의 상기 캐스케이드 멀티플라이어(36) 커패시터들(C1 a-C6 b)에 걸리는 평균 정상 전압 및 상기 출력전압(VO) 값을 요약하고 있으며, 상기 입력전압(VI)은 14V와 동일하다는 것을 가정하고 있다. 또한, 표 6은 다음의 예시를 설명하고 있다. 즉, 변환 이득이 6일 때 상기 커패시터들(C6 a, C6 b)은 제 1 접근방식에서 제거되어 지며, 상기 커패시터들(C1 a, C1 b )은 제 2 접근방식에서 제거되어 지며, 및 상기 커패시터들(C4 a, C4 b)은 제 3 접근방식에서 제거되어 진다. 변환 이득이 5일 때는, 상기 커패시터들(C5 a, C6 b)은 제 1 접근방식에서 제거되어 지고, 상기 커패시터들(C1 a, C2 b)은 제 2 접근방식에서 제거되어 지며, 상기 커패시터들(C3 a, C5 b)은 제 3 접근방식에서 제거되어 진다.

각 커패시터 전압은 상기 출력전압(VO)의 정수 배이며 인접한 스테이지들의 두 커패시터들 사이의 전압 차이는 출력전압(VO)과 동일하다. 예를 들면, 만약 상기 변환 이득이 7과 동일하다면, 상기 제 1 스테이지 커패시터들은 상기 출력전압(VO)의 6배와 동일한 전압을 가지는 상기 커패시터들(C1 a, C1 b)이다. 상기 제 2 스테이지 커패시터들은 출력전압(VO)의 5배와 동일한 전압을 가지는 커패시터들(C2 a, C2 b)이다. 상기 제 3 스테이지 커패시터들은 출력전압(VO)의 4배와 동일한 전압을 가지는 커패시터들(C3 a, C3 b) 이다. 등등.

상기 커패시터들(C1 a- C6 b)에 걸리는 전압들 및 상기 출력전압(VO) 값은 상기 캐스케이드 멀티플라이어(34)의 변환 이득이 바뀔 때 변한다. 예를 들어, 상기 제 1 재구성 접근방식 및 상기 입력전압이 재구성 시 변하지 않는다는 가정 하에, 상기 변환 이득이 7에서 5로 변한다면 상기 커패시터들(C1 a C1 b, C2 a-C2 b, C3 a-C3 b, C4 a-C4 b)에 걸리는 전압은 각각 상기 출력전압(VO)의 4배, 3배, 2배, 및 1배가 된다. 또한, 각각의 상기 커패시터들(C1 a-C4 b)에 걸리는 전압은 상기 출력전압(VO)이 증가하는 동한 감소한다.

상기 제 1 재구성 접근방식에서, 상기 잔여 커패시터들(C1 a-C4 a)에 걸리는 전압은 변환 이득이 줄어들 때 감소하여, 상기 캐스케이드 멀티플라이어(34)에서 상기 소스(26)로 역방향 극성의 큰 과도 전류가 흐르게 된다. 반면에, 상기 제 2 재구성 접근방식을 사용할 때는, 상기 잔여 커패시터들에 걸리는 전압은 상기 변환 이득이 줄어들 때 증가하게 되어, 상기 소스(26)로부터 상기 캐스케이드 멀티플라이어(34)로 순방향 극성의 큰 과도 전류가 흐르게 된다.

큰 입력 과도 전류는 스위치드 커패시터 전력 컨버터의 변환 이득이 동작 중에 변할 때 발생하는 상기 중단의 한 표현이다. 그런 과도현상은 원하지 않는 전자파 간섭을 일으키거나 상기 입력전압(VI)을 공급하는 외부 시스템을 교란시킨다. 또한, 상기 커패시터 전압들은 재구성 시 발생하는 상기 전하 재 분포(redistribution)에 의해 여러 스위칭 주기들(cycles) 이후에 새로운 정상 상태 레벨들로 정착(settling)하기 전에, 요구되는 목표 전압으로부터 높게 또는 낮게 벗어날 수도 있다. 상기 스위치드 커패시터 회로의 노드들에서의 일부 전압들이 회로에 전력 지원이 하지 않는 한 이것은 정상적인 것으로 문제가 아니다.

본 발명에 사용된 바와 같이, 레일 노드(rail node)는 캐스케이드 멀티플라이어에서의 커패시터들(예, 도 2에서의 노드들 N1-N6)의 양극 단자이거나, 혹은 듀얼-위상 캐스케이드 멀티플라이어 내에서의 dc 노드(예, 도 5에서 노드들 N1 c-N5 c ), 혹은 상기 입력전압(VI) 노드, 혹은 상기 출력전압 (VO) 노드이다. 본 발명에 사용된 바와 같이, 인접한 레일 노드들은 여러 쌍의 레일 노드들을 참조하며, 그곳의 차등 전압(differential voltage)은 적어도 상기 출력전압(VO)의 정수 배이고 및 두 동작 상태 모두에서 정상-상태로 일정하다. 도 2를 참고하면, 상기 노드들(N1, N3) (혹은, 상기 노드들 VI, N2)은 레일 노드들에 인접하며 동시에 도 5를 참고하면, 상기 노드들(N1 c, N2 c) 및 노드들(N1 a, N2 a)은 레일 노드들에 인접한다.

이러한 특성으로 인해 인접 레일(rail) 노드들 사이의 저-전압 트랜지스터 회로들에 전력을 공급하는 것이 편리하다. 예를 들어, 상기 캐스케이드 멀티플라이어(34)에서 각각의 스택 스위치들 (예, S10-S11)을 위한 상기 게이트 드라이버 및 제어 회로는 인접한 레일 노드들(예, VI, N1 c) 사이에서 전원을 공급받을 수 있다. 인접한 레일 노드들의 집합(set)에 걸리는 차등 전압이 정적상태(static) 혹은 충분히 긴 과도현상 이벤트 동안 상기 트랜지스터들의 상기 최대 드레인-소스 전압 혹은 게이트-소스 전압 정격(rating)을 초과할 경우, 영구적인 장치 손상이 일어날 수 있다. 반대로, 이 차등 전압이 상기 트랜지스터 임계전압에 너무 가까이 근접하게 되면, 기본적인 트랜지스터 기능이 고장 나거나, 혹은 상기 스위치드 커패시터 회로의 상기 성능에 나쁜 영향을 미치는 지점까지 저하될 수 있다.

예를 들면, 상기 게이트 드라이버 출력은 그것의 입력에 따라 전이하는데 실패할 수도 있거나, 혹은 상기 게이트 드라이버의 전파 지연이 상기 스위치드 커패시터 회로 내 다른 곳에서 오작동을 일으킬 정도로 증가하거나, 혹은 상기 트랜지스터 스위치가 적당한 전력을 흐르게 하기 위해 폐쇄되는 경우 과도한 저항이 남아있을 수도 있다. 다시 말해서, 인접 레일 노드들에서 저-전압(under-voltage) 혹은 초과-전압(over-voltage)은 원하지 않는 이벤트가 될 수 있으며 및 재구성으로 인한 이런 이벤트들의 크기 및/혹은 지속시간을 최소화 하는 것이 필요하게 된다.

전형적인 스위치 커패시터 회로에서, 입력 과도현상들은 입력전압(VI)과 접지 사이에 대용량의 바이패스 커패시터를 위치함으로써 억압된다. 불행하게도, 이 기술이 효과적이기 위해서는, 물리적으로 큰 커패시터가 필요하다. 도 2-6에서 도시된 상기 스위치드 커패시터 회로들에 약간의 수정 및/혹은 추가를 하면, 재구성 시에 발생하지 않을 입력 과도현상을 억제하는 것은 가능하다. 도 7A-9C는 스위치드 커패시터 회로의 입력 과도현상을 억압하는 세 가지 보편적인 방법들을 도시한다.

상기 첫 번째 방법에서, 부피 및 용량이 모두 작은 소형 바이패스 커패시터(CB1)는, 전형적으로 상기 응용에 적합한 크기를 갖는 제 2 바이패스 커패시터(CB2)와 병렬로 사용될 때 큰 입력 과도 전류를 억압할 수 있다. 도 7A에서 도시된 바와 같이, 인에이블 시그널(EN1)이 낮게 설정될 때, 상기 소형 바이패스 커패시터(CB1)는 프리-차지 전압(VC)으로 충전된다. 상기 스위치드 커패시터 회로의 변환 이득의 재구성이 일어나는 것처럼, 상기 인에이블 신호(EN1)는 높게 설정되며 및 상기 소형 바이패스 커패시터(CB1)은 상기 입력전압(VI)과 접지 사이에 연결된다. 상기 소형 바이패스 커패시터(CB1)는 상기 입력전압(VI)과 비교되는 상기 프리 차지 전압(VC)의 극성에 따라서, 전류를 싱크하거나 공급함으로써, 상기 스위치드 커패시터 회로의 소스(26)에서 추출되는 혹은 소스(26)로 재공급되는 전하의 양을 줄인다. 도 7B에서 도시된 바와 같이, 상기 재구성의 시작과 동시에 상기 소형 바이패스 커패시터(CB1)는 입력전압(VI)에 연결되어야 하고, 및 상기 재구성의 여러 스위칭 주기들 이후에 연결 해제될 수 있다. 선택 신호(SEL)은 상기 프리-차지 전압(VC)을 설정한다. 상기 선택 신호(SEL)가 높으면, 상기 프리-차지 전압(VC)은 상기 입력전압(VI)보다 높은 제 1 목표 전압(V1)으로 설정된다. 반대로 상기 선택 신호(SEL)가 낮으면, 상기 프리-차지 전압(VC)은 입력전압(VI) 보다 낮은 제 2 목표 전압(V2)으로 설정된다.

상기 재구성 접근방식 및 변환이득 극성 변경에 따라서, 최적의 프리-차지 전압(VC)이 있다. 상기 제 1 재구성 접근방식에서, 만약 상기 변환이득이 감소하면, 상기 프리-차지 전압(VC)은 상기 입력전압(VI) 보다 낮아야 한다. (즉. 선택 신호(SEL)가 낮다) 이것은 재구성 시 상기 제 2 목표 전압까지 충전된 상기 소형 바이패스 커패시터(CB1)가 상기 스위치드 커패시터 회로에서 유발되는 상기 역방향 극성의 과도 전류의 일부를 흡수하게 함으로써, 상기 소스(26)에서 보이는 상기 입력 과도 전류의 크기를 줄인다.

반대로, 만약 상기 제 1 재구성 접근방식으로 상기 변환이득이 증가하면, 프리-차지 전압(VC)은 상기 입력전압( VI) 보다 높아야 한다. (즉. 선택 신호(SEL)는 높다) 이것은 재구성 시 상기 제 1 목표 전압까지 충전된 상기 소형 바이패스 커패시터(CB1)가 상기 스위치드 커패시터 회로에 의해 요구되어지는 순방향 극성의 과도 전류의 일부를 공급하게 함으로써, 상기 소스(26)에서 보이는 상기 과도 입력 전류의 크기를 줄인다. 좀 더 정확성을 위해, 상기 목표 전압들(V1, V2)은 상기 입력전압(VI), 상기 변환-이득, 상기 커패시터 값들, 및 상기 출력 부하 전류 레벨을 고려할 수 있다.

도 8 에서는 재구성 시 과도 입력을 억압하는 다른 방법을 도시한다. 이 방법은 소스 (26)와 스위치드 커패시터 회로의 입력 사이에 연결된 양방향 전류-제한(bidirectional current-limited) 스위치(MP1) (즉. PMOS 트랜지스터)를 포함한다. 도 8에 도시된 상기 제어 방법에서, 상기 전류-제한 스위치(MP1)는 오믹 영역(ohmic region)에서 제 1 혹은 제 2 전류-감지(current-sense) 증폭기(AV1 or AV2)가 특정 전류 제한 레벨을 초과하는 순방향 혹은 역방향 극성의 입력 전류를 검출할 때까지 정상적으로 동작한다. 저항(R1) 및 전류 소스(42)는 오믹 영역에서 상기 전류-제한 스위치(MP1)를 바이어스 하는 정상-상태 게이트 전압(VG)을 설정한다. 상기 전류 제한을 초과하는 이벤트가 검출되면, 상기 제 1 전류 감지 증폭기(AV1) 혹은 상기 제 2 전류-감지 증폭기(AV2) 중 하나는 상기 게이트 전압(VG)을 높게 구동한다. 이것은 상기 전류-제한 스위치(MP1)의 구동 강도를 감소시킴으로써, 상기 과도현상이 진정될 때까지 상기 입력 전류 크기를 제한한다. 상기 다이오드들(D1, D2)은 상기 전류 감지 증폭기들(AV1, AV2)의 출력에 각각 OR 동작을 제공한다.

또 다른 제어 방법은 상기 재구성 시 짧은 시간 동안 혹은 입력 전류 제한이 검출될 때 상기 전류-제한 스위치(MP1)를 개방하는 것이다. 불행하게도, 이 제어 방법을 사용하는 경우, 상기 스위치드 커패시터 회로의 입력에 더 큰 과도 전압이 있으며, 이것은 상기 스위치드 커패시터 회로의 입력(즉. 상기 PMOS 회로-제한 스위치(MP1)의 드레인 단자)과 접지 사이에 바이패스 커패시터를 추가함으로써 어느 정도까지 완화될 수 있다.

입력 과도현상을 억압하는 또 다른 하나의 방법은 재구성 시작 직전부터 여러 스위칭 주기까지 스위치드 커패시터 회로 내의 스위치들의 상기 온-저항(on-resistance)을 변조하는 것을 포함한다. 상기 스위치들의 상기 온-저항을 증가시키는 것은 재구성 시 발생하는 상기 전하 재분포(redistribution)를 막지는 않지만, 상기 스위칭 주기의 더 오랜 부분 동안 상기 에너지를 확산함으로써 상기 관련된 피크 과도 전류를 최소화한다. 비록 상기 스위치드 커패시터 회로의 효율이 더 큰 전도 전력 손실(conduction power loss)로 나빠지더라도, 이는 일시적인 효과이다. 상기 스위치들의 상기 온-저항은 상기 스위치드 커패시터 회로의 상기 효율을 최대화하기 위해서 상기 재구성 이후 그들의 최저 레벨로 다시 변조 될 수 있다.

도 9A-9C는 제어 전압(VON)이 높은 경우 양극 단자(TP) 와 음극 단자(TN) 사이에 있는 MOSFET의 상기 온 저항을 변조하는 세 가지 방법들을 도시한다. 상기 온-저항은 인에이블 신호(EN2)를 사용하여 제 1 저항값 혹은 제 2 저항값 중 하나와 동일하다. 도 9A에서, 상기 단자들(TP, TN) 사이의 상기 온 저항은 하부 트랜지스터(bottom transistor)(M72)를 디스에이블링하거나 인에이블링하여 두 값 사이에서 변조한다. 전압 소스(52)에 의해 전력을 공급받는 이에 대응하는 게이트 드라이버는 구동 전압(VDRV)으로 하부 트랜지스터(M72)를 구동한다. 상기 하부 트랜지스터(M72)는 인에이블 신호(En2)가 높을 때 인에이블 되고 인에이블 신호(EN2)가 낮을 때에는 디스에이블 된다. 그러므로 상기 단자들(TP, TN) 사이의 상기 온-저항은, 상기 인에이블 신호(EN2)가 낮은 경우와 비교해보면, 상기 인에이블 신호(EN2)가 높은 경우 더 낮다.

또한, 도 9B에서는 상기 단자들(TP, TN) 사이의 상기 온-저항이 트랜지스터(M74)의 구동 전압(VDRV)을 변경함으로써 두 값 사이에 변조하는 기술을 도시한다. 상기 구동 전압(VDRV)은 상기 인에이블 신호(EN2)가 높은 경우 제 1 전압 소스(52)에 의해 공급받으며 상기 인에이블 신호(EN2)가 낮을 때는 제 2 전압 소스(54)에 의해 공급받는다. 상기 제 1 전압 소스(52)가 상기 제 2 전압 소스(54)보다 더 큰 전기적 전위(electric potential)를 생산한다고 가정하면; 즉, 상기 단자들( TP, TN) 사이의 상기 온-저항은 상기 인에이블 신호(EN2)가 낮은 경우와 비교해보면, 상기 인에이블 신호( EN2)가 높은 경우 더 낮다.

마지막으로, 도 9C는 NMOS 트랜지스터(M76)의 백-게이트 전압(VB)를 변경함으로써 상기 단자들(TP, TN) 사이의 상기 온-저항이 두 값 사이에서 변조하는 기술을 도시한다. 전압 소스(52)에 의해 전력을 공급받는 이에 대응하는 게이트 드라이버는 구동 전압(VDRV)으로 상기 트랜지스터(M76)을 구동한다. 상기 NMOS 트랜지스터(M76)의 상기 백-게이트 단자는 상기 인에이블 신호(EN2)가 높은 경우 그것의 소스(즉. 단자 TN)에 연결되고 및 상기 인에이블 신호가 낮은 경우에는 전압 소스(56)에 연결된다. 상기 소스-투-백-게이트(source-to-back-gate) 전압이 증가하면 상기 NMOS 트랜지스터(M76)의 임계 전압이 증가하기 때문에, 상기 인에이블 신호(EN2)가 낮은 경우와 비교해보면, 상기 인에이블 신호(EN2)가 높은 경우 상기 단자들(TP, TN) 사이의 상기 온-저항은 더 낮다.

상기 온-저항 변조 기법은 상기 스위치드 커패시터 회로 내 모든 또는 서브셋 스위치들에 적용될 수 있다. 상기 스택 스위치들의 상기 직렬 연결된 특성에 의해, 상기 제어 회로부는 상기 위상 스위치들의 경우와 같은 하나의 전압 영역에 비하여 복수 전압들 영역 간에서 동작해야 할 것이다. 복잡성과 다이 영역(die area) 관점으로, 상기 위상 스위치들만의 상기 온-저항 변조는 좀 더 매력적인 해결책일지도 모른다.

캐스코드 스택 스위치들을 포함하는 스위치드 커패시터 회로에는 특별한 주의가 이루어져야 한다. 스위치도 커패시터 회로 재구성 시, 상기 dc 노드들에서 중대한 전압 편차들이 발생하여 상기 캐스코드 스택 스위치들을 오버-스트레스(over-stress) 할 수 있다. dc 노드들을 능동적으로 감지하고 제어함으로써, 상기 캐스코드 스택 스위치들은 보호될 수 있다. 예를 들어, 도 10A는 상기 캐스케이드 멀티플라이어(34)의 dc 노드들(N1 c-N5 c), 입력전압(VI), 및 출력전압(VO)과 결합된 제어기 (62)를 도시한다. 상기 제어기(62)의 두 가지 구현들이 도 10B-10C에 도시된다. 또한, dc 노드(예, N1 c)는 어떠한 동작 상태에서라도 스위치드 커패시터 회로 내에 있는 두 커패시터들(예, C1 a, C2 b)의 양극 단자들과 결합하기 때문에 상기 dc노드의 전압을 제어하고 또한 각 동작 상태에 있는 상기 dc 노드에 연결된 상기 두 커패시터들의 상기 전압을 제어한다.

도 10B는 인접한 레일 노드들의 각각의 집합에 걸친 서브-블럭(64)를 포함하는 제어기(62)의 구현을 도시하며, 여기서 인접한 레일 노드들 각각의 세트에 걸리는 상기 차등 전압은 출력전압(VO)와 동일하다. 각 서브-블럭(64) 내에서, 제 1 및 제 2 전압 증폭기들(AV1, AV2)은 인접한 노드들의 각각의 세트에 걸리는 상기 차등 전압을 과전압(over-voltage) 임계(VOV) 및 저-전압(under-voltage) 임계 (VUV)에 대해 비교한다. 만약 상기 차등 전압(예, N5 c-VO)이 상기 과전압(over-voltage) 임계 전압(VOV) 혹은 저-전압(under-voltage) 임계 전압(VUV) 위로 상승하거나 혹은 아래로 하강할 경우 상기 서브-블록(64)은 이에 대응하는 레일노드(예, N5 c)의 상기 전압을 클램프(clamp) 한다.

상기 제어기(62)에서 각각의 서브-블록(64)의 상기 동작을 이해하는 것은 그렇게 어렵지 않다. 예를 들면, 만약 상기 dc 노드(N5) 및 상기 출력전압(VO)에 걸리는 상기 차등 전압이 상기 과-전압 임계 전압(over-voltage threshold voltage)(VOV)을 초과하면, 상기 제 1 전압 증폭기(AV1)는 상기 NMOS 트랜지스터(MN1)의 게이트를 높게 구동시킨다. 이로 인해 상기 NMOS 트랜지스터(MN1)가 상기 dc 노드 (N5 c)로부터 전류를 싱크(sink)함으로써, 상기 dc 노드(N5 c) 및 상기 출력전압(VO)에 걸리는 차등 전압을 과전압 임계 전압(over-voltage threshold voltage)(VOV)에 클램핑(clamping)한다. 반대로, 만약 dc 노드(N5 c) 및 상기 출력전압(VO)에 걸리는 차등 전압이 상기 저-전압 임계(under-voltage threshold)(VOV) 이하로 내려가면, 상기 제 2 전압 증폭기(AV2)는 상기 PMOS 트랜지스터의 게이트를 낮게 구동한다. 이로 인해, 상기 PMOS 트랜지스터(MP1)가 상기 dc 노드(N5 c)로터 전류를 소스(source)함으로써, 상기 dc 노드(N5 c) 및 상기 출력전압(VO)에 걸리는 차등전압을 상기 저-전압 임계 전압(under-voltage threshold voltage)(VUV)에 클램핑(clamping)한다.

클램핑(clamping)동안, 전력 손실을 최소화하기 위해, 상기 소싱(sourcing) 및 싱킹(sinking) 전류들은 상기 입력전압(VI), 상기 접지, 및/혹은 다른 서브-블록(64) 단자들 사이로 다이렉트(direct)될 수 있다. 예를 들어, 상기 dc 노드들(N2 c, N3 c)에 걸친 서브 블록(64) 내에서 노드(N2 c)로부터 상기 NMOS 트랜지스터(MN1)로 흐르는 클램프(clamp) 전류는 하부 쌍(lower pair)의 레일 노드들(예, N4 c, N5 c)에 걸친 다른 서브 블록(64)으로 리다이렉트(redirect) 될 수 있으며 상기 PMOS 트랜지스터(MP1)를 통해 동시에 전류를 소싱(sourcing)하는 클램프(clamp)를 가지게 된다. 인접한 레일 노드들에 걸리는 상기 차등 전압을 제한하기 전에 능동 클램프들(active clamps)이 제안되고 있지만, 이 방법들은 오직 스위치드 커패시터 회로가 셧다운 모드(shutdown mode)에 있을 때만 사용된다.

도 10C에서는 상기 dc 노드들(N1 c-N5 c) 각각의 서브-블록(66)을 포함하는 제어기(62)에 대한 또 다른 구현을 도시한다. 여기서의 아이디어는 상기 dc 노드들(N1 c-N5 c)의 전압들 및 확장하여, 상기 이전의 정상 상태 전압들에서 상기 새로운 변환 이득과 관련된 레벨들로의 재구성 시 일어나는 근접한 스위칭 주기 내에서 상기 커패시터들 (C1 a-C6 b)의 전압을 조절(regulate)하는 것이다. 서브-블록(66) 각각은 상기 전압 레귤레이터 출력에서 전류 싱킹(sinking) 및 소싱(soucing) 능력을 가지기 위한 푸쉬-풀 버퍼(push-pull buffer) 트랜지스터 주위에서 단위-이득 폴로어(unity-gain follower)의 역할을 하게끔 연결된 전압 증폭기(AV3)로 구성된 전압 레귤레이터를 포함한다.

각각의 서브-블록(66)을 위한 목표 전압들(V51-V55)은 상기 조절(regulation) 전압 레벨들을 결정한다. 필요 시, 상기 dc노드들(N1 c-N5 c) 각각은 스위치들(SW1-SW5)을 폐쇄하여 그것에 대응하는 서브-블록(66)에 연결하거나, 스위치들(SW1-SW5)을 개방하여 정상적인 스위치드 커패시터 회로부터 격리될 수 있다. 상기 dc 노드들(N1 c-N5 c ) 각각의 상기 전압은 일반적으로 표 6에 나열된 바와 같이 상기 커패시터들(C1 a-C5 b )에 걸리는 전압들과 관련된 값들을 따른다.

도 10C에서 상기 제어기(62)의 동작은 복잡하지 않다. 상기 제 2 재구성 접근방식을 사용하여 상기 변환-이득이 7에서 6으로 감소하는 경우, 각각의 서브-블록(66)은 스위치들(SW2-SW5)을 폐쇄함으로써 그들의 대응하는 dc 노드들(N2 c-N5 c)에 연결된다. 가령, 상기 입력전압(VI)이 14V와 동일하다고 가정하면, 상기 타깃 전압들(V52, V53, V54, V55 )은 각각 10V, 8V, 6V, 4V에서 11.67V, 9.33V, 7V, 4.67V로 변한다. 상기 dc 노드 (N1 c)의 상기 서브-블록(66)은 불필요하며 및 상기 스위치(SW1)은 상기 커패시터들(C1 a, C1 b )이 제거되기 때문에 개방 상태로 남을 수 있다. 하나의 전압 레벨에서 다음 레벨으로 스테핑(stepping)하는 것과 반대로, 특정 슬루율(slew rate)로 하나의 레벨에서 다음 레벨로 목표 전압들(V52-V55)을 램핑하는 것은, 상기 스위치드 커패시터 회로(34)의 노드들에서 상기 과도현상들을 추가로 최소화할 수 있다. 또한, 각각의 서브-블록(66)은 상기 전체 출력 전류 범위에 걸쳐 유효한 충분한 전류 소싱(sourcing) 혹은 싱킹(sinking) 능력을 가져야 한다.

도 10B와 같이, 전력 손실을 최소화하기 위하여 상이한 서브-블록들(66) 사이의 상기 dc 노드들(N1 c-N5 c )을 조절하는 동안 사용된 상기 전류의 일부를 리다이렉트하는 것이 가능하다. 만약 변환-이득의 변경 시 반대 극성 전압의 변화가 요구되는 dc 노드들(N1 c-N5 c)의 조합이 있다면, 이것은 달성될 수 있다. 표 6에서 도시하듯이, 이 시나리오는 상기 제 3 재구성 접근방식에 적용된다. 예를 들어, 만일 상기 변환이득이 감소하면, 상기 제거된 내부 커패시터의 상위 스테이지의 상기 커패시터들은 자신의 전압을 감소시키길 원하고, 반면에 하위 스테이지의 커패시터들은 자신의 전압을 증가시키길 원한다.

이에 비해, 상기 변환 이득이 감소할 때 상기 제 1 재구성 접근방식에서의 모든 상기 잔여 커패시터들 상기 전압은 감소한다. 반면, 상기 제 2 재구성 접근방식에서의 상기 변환 이득이 감소할 때 모든 상기 잔여 커패시터들의 상기 전압은 증가한다. 그러므로 상기 제 1 및 제 2 재구성 접근방식 모두에서 각각의 서브-블록 내에서는 단방향(unidirectional) 전류가 흐른다. 모든 것을 잃어버린 것은 아니다; 하지만, 즉, 제 3 재구성 접근 방식에서 보다 상기 제 1 및 제 2 재구성 접근방식들에서 필요한 이런 전류의 일부를 리캡처링(recapturing)할 수 있는 가능성들이 비록 더 좁은 조건의 범위 아래일지라도 남아있다.

각각의 서브 블록이 자신의 전압을 감소시키기 위해 dc 노드로부터 전류를 싱크(sink) 할 때 이 더 좁은 범위가 존재한다. 이것은 상기 변환-이득이 감소할 때의 제 1 재구성 접근 방식 및 상기 변환-이득이 증가할 때의 제 2 접근 방식에 적용된다. 이러한 조건들 하에서, 각각의 서브-블록 전류는 상기 출력전압(VO)으로 리다이렉트(redirect)됨으로써, 상기 출력 부하 전류의 일부를 직접적으로 공급한다.

일반적으로, 재구성 시 발생하는 상기 전류 및 전압 과도현상은 상기 재구성이 일어나기 전에 상기 개별 커패시터 전압들을 새로운 변환 이득과 관련된 상기 새로운 정상 상태 레벨로 가능한 가깝게 가져간다면 최소화될 수 있다. 결국, 전하 재분포(charge redistribution)는 상기 재구성 이벤트 이전 및 이후의 상기 커패시터 전압 차이의 크기에 직접적으로 비례한다. 만일 이 전압 차이를 재구성 이전에 감소 될 수 있다면, 상기 결과로 초래된 전하 재분포(charge redistribution)는 더 작아지게 되며 결과적으로 상기 스위치드 커패시터 회로 내 노드들에서의 전류 및 전압 과도현상을 최소화한다.

이를 염두에 두고, 상기 변환-이득이 증가하고 및 이전에 제거된 커패시터가 상기 전하 이동 경로로 재도입(reintroduce)되는 이벤트에 주의를 기울여야 한다. 전술한 바와 같이, 저-전압 트랜지스터들(low voltage transistors)이 사용될 때 특정 스위치드 커패시터 회로 노드들 사이의 최대 전압 차이를 제한하기 위해서, 상기 제거된 커패시터들 전부가 프리 차지되지 않고 일부만 유지하는 것에도 이득이 있다. 선택된 상기 재구성 접근방식에 따라, 상기 전하 이동 경로의 상기 잔여 커패시터들과 비교하여 이 제거된 커패시터들의 프리-차지 전압은 발생되는 과도 전류의 크기에 영향을 미칠 수 있다. 또한, 상기 프리-차징(the pre-charging)은 상기 정상 전하 이동 경로를 간섭해서는 안 된다.

도 11은 상기 단-위상(single-phase)의 캐스케이드 멀티플라이어(30)에서의 상기 커패시터들 (C1-C6 )과 결합된 커패시터 프리-차지 회로(68)을 도시한다. 상기 제거된 커패시터는 제거된 커패시터의 상기 스택 스위치들이 항상 개방되기 있기 때문에 상기 제 1 상태 혹은 상기 제 2 동작 상태에서 프리-차지될 수 있다. 그러나 만일 상기 제거된 커패시터들이 자신에 대응하는 위상 노드가 접지되어 있는 상태 동안 프리-차지된다면 구현이 더 쉬울 수도 있다.

다음 예는 상기 입력전압(VI)이 14V로, 상기 변환이득이 5, 및 상기 제거된 커패시터들(C5, C6)(제1 재구성 접근방식)이 출력전압(VO)(즉. 2.8V )으로 프리-차지된다고 가정한다. 상기 변환-이득이 6으로 변경하는 재구성 이벤트에서, 상기 커패시터(C5)의 전압을 2.8V에서 2.33V로 전압을 전이하는 동안 상기 커패시터(C5)의 초과 전하는 상기 커패시터들 (C1-C4)의 전압들을 증가시키기 위해 사용함으로써, 순방향 극성(the forward polarity)의 과도 입력 전류의 크기를 줄인다.

유사하게, 5의 변환 이득 및 14V의 입력전압(VI)에서의 상기 제 2 재구성 접근방식의 경우, 상기 제거된 커패시터들(C1, C2)은 11.2V(출력전압(VO)의 4배)로 프리-차지된다. 상기 변환-이득이 6으로 변경하는 재구성 이벤트에서, 커패시터들(C3-C6)의 초과 전하는 상기 커패시터(C2) 전압을 11.2V에서 11.6V로 증가시키는 것을 돕는데 사용됨으로써, 역극성(the reverse polarity) 과도 입력 전류의 크기를 감소시킨다.

만일 상기 제 1 재구성 접근방식에서 상기 제거된 커패시터들이 출력전압(VO)보다 높게 프리-차지되거나, 혹은 상기 제 2 재구성 접근방식에서 상기 제거된 커패시터들이 출력전압 (VO)의 4배보다 작게 프리-차지된다면, 상기 과도 입력 전류의 크기보다 더 큰 크기의 축소가 달성된다고 주장할 수도 있다. 이 논쟁의 장점도 있지만, 상기 스위치드 커패시터 회로에서 저-전압 MOS 트랜지스터들을 사용하는 것은 개방 상태에 있는 상기 스위치들에서 보이는 상기 최대 드레인-소스 전압에 제한(limit)을 부여하고, 및 이 제한은 또한 상기 프리-차지 전압을 억제한다.

5의 변환이득 및 14V의 입력전압(VI)을 가지는 상기 제 3 재구성 접근방식에 관해서는, 상기 제거된 커패시터들(C3, C4)은 상기 커패시터들처럼(C2, C5 ) 각각 동일한 전압들(즉. 8.4V, 5.6V )로 프리-차지된다. 상기 스위치드 커패시터 회로의 중간 단계를 포함하거나 그에 가까운 재구성을 위한 내부 커패시터들을 선택하는 것은 변환이득의 변경 시 자신의 전압들을 증가시키거나 감소시켜야 하는 커패시터들의 수와 거의 동일하다. 이러한 동작 때문에, 상기 제 3 재구성 접근방식은 다른 모든 조건이 동일하다면 상기 제 1 혹은 제 2 재구성 접근 방식보다 더 낮은 과도 입력 전류를 발생시킬 것이다.

전이 구간의(transition interval)에 대한 이런 일반적인 개념은 단-위상(single-phase ) 스위치드 커패시터 전력 컨버터(예, 도 2) 혹은 다-위상(multi-phase) 스위치드 커패시터 전력 컨버터들(예, 도 5)에 적용될 수 있다고 이해되어야 한다. 상기 전이 시간 내에서, 과도 전류 및/또는 전압을 최소화하는데 사용될 수 있는 수많은 옵션 또는 기술들이 있으며 이는 상기 변환-이득 변경의 극성과 선택된 상기 재구성 접근 방식에 따라 다를 수 있다.

도 14A-16는 상기 전이 구간 동안 듀얼-위상 캐스케이드 멀티플라이어(34) 작동의 몇 가지 다른 방법을 도시한다. 이 방법들의 다양한 조합 또한 가능하다. 도 14A-14B에서, 전압 소스들이 사용되며, 실제로, 이상적인 전압 소스들은 자신들의 동작을 에뮬레이트하는(emulate) 회로들을 사용하여 전압 레귤레이터 혹은 스위치드 커패시터 회로처럼 구현될 수 있다.

도 14A 는 상기 전이 구간 동안 전압 소스의 구현을 도시한다. 상기 재구성의 시작 시, 그러나 커패시터들의 제거 혹은 추가에 우선하여, dc 노드들(N1 c-N5 c)의 전압들은 상기 전이 시간에 걸쳐 상기 새로운 변환이득의 새로운 정상-상태 전압으로 제어된 방식으로 슬루(slew) 된다. 상기 전이 시간 동안에, 모든 위상 노드들은 접지로 연결되며 동시에 각각의 공통 스테이지의 한 쌍의 커패시터들(pair of capacitors)의 상기 스택 스위치들은 각각의 공통 스테이지의 한 쌍의 커패시터들의 상기 양극 단자들을 상기 대응하는 dc 노드들(N1 c-N5 c ) 및 상기 출력전압(VO)에 함께 연결하는 방식으로 폐쇄된다.

도 5에 따르면, 이는 상기 제 1 스테이지 커패시터들(C1 a, C1 b)을 위한 상기 스택 스위치들 (S10, S10)을 개방하는 동안 스택 스위치들 (S12, S13 )을 폐쇄하는 것을 의미한다; 즉, 상기 제 2 스테이지 커패시터들(C2 a, C2 b)을 위한 스택 스위치들(S20, S21)을 개방하는 동안 스택 스위치들(S22, S23)을 폐쇄하는 것; 기타 등등을 의미한다. 상기 dc 노드들(N1 c-N5 c) 각각에 연결된 전압 소스들(81-85)은 커패시터들(C1 a-C5 b )의 전압을 새로운 변환-이득에 연관된 값의 방향으로 제어된 방식으로 슬루(slew)한다. 상기 커패시터들이 상기 목표 값들에 도달하면, 전하 이동 경로에 커패시터들을 제거 혹은 추가함으로써 스위치드 커패시터 회로의 재구성은 시작될 수 있다. 상기 마지막 스테이지 커패시터들(C6 a-C6 b)은 상기 출력 부하 전류(IL)를 공급하기 위해 상기 출력전압(VO)과 접지 사이의 연결을 유지하고 및 상기 출력전압(VO)이 과도하게 드루핑 (drooping)되는 것을 막는다.

불행하게도, 도 14A에는 상기 입력전압(VI)에서 출력전압(VO)으로의 직접적인 전력 경로가 없다. 그러나 만일 상기 커패시터들(C1 a, C1 b)에 대응하는 상기 위상 노드들이 상기 잔여 위상 노드들로부터 분리되는 경우에 도 14B에 도시된 바와 같은 상기 구성을 형성하는 것은 가능하다. 상기 커패시터들(C1 a, C1 b)을 입력전압(VI)과 출력전압(VO) 사이에 위치시킴으로써, 전력 흐름은 상기 전이 구간 동안 유지될 수 있음에 따라, 도 14A에 도시된 바와 비교해 볼 때 상기 출력전압(VO)의 피크-투-피크 리플(peak-to-peak ripple)을 감소시킬 수 있다.

그 대신에, 상기 전이 구간 동안 제어된 방식으로 각각의 커패시터 전압을 슬루(slew)하는 전류 소스를 사용하는 것은 가능하다. 도 15A-15C는 이상적인 전류 소스를 사용하는 세 가지 다른 재구성 방법 각각의 특정한 구현 예를 나타낸다. 실제로, 자신의 동작을 에뮬레이트(emulate) 하는 회로를 사용하여 전류 레귤레이터 혹은 전류 미러와 같은 상기 이상적인 전류 소스를 구현할 수 있다. 도 14A-14B에서와 같이, 상기 듀얼-위상(dual-phase) 캐스케이드 멀티플라이어(34)는 기술을 설명하기 위해 사용된다. 하지만 이 기술은 스위치드 커패시터 회로들의 다른 유형에 적용될 수 있다. (예, 단-위상(single-phase) 캐스케이드 멀티플라이어들)

도 15A는 상기 제 1 재구성 접근방식에서 전이 구간 동안 전류 소스가 상기 커패시터들(C1 a-C6 b )의 전압들을 슬루(slew)하는데 사용되는 특별한 구현 예를 도시한다. 만일 상기 변환 이득이 7에서 6으로 감소하면, 상기 커패시터들(C1 a-C6 b)의 전압은 감소할 것이다. 그러므로 전이 시간, 상기 위상 노드들(P1, P2)은 접지에 연결되고 그동안 상기 스택 스위치들은 각각의 공통 스테이지의 한 쌍의 커패시터들(pair of capacitors)의 상기 양극 단자들을 자신의 대응하는 dc 노드들(N1 c-N5 c)에 연결하는 방식으로 동작한다. 도 5를 참조하면, 이것은 상기 제 1 스테이지 커패시터들(C1 a, C1 b )을 위한 상기 스택 스위치들(S10, S11)이 개방되어있는 동안 상기 스택 스위치들 (S12, S13 )을 폐쇄하는 것을 의미한다; 상기 제 2 스테이지 커패시터(C2 a, C2 b )를 위한 상기 스택 스위치들 (S20, S21)이 개방되어 있는 동안 상기 스택 스위치들(S22, S23)을 폐쇄한다; 기타 등등을 의미한다. 각각의 상기 dc 노드들(N1 c-N5 c)로부터 상기 출력전압(VO)까지 연결된 전류 소스들(91-95)은 상기 커패시터들을 선형 방식으로 방전시킨다.

상기 제 1 스테이지 커패시터들(즉. C1 a, C1 b)에서 시작하여 상기 포스트- 재구성(post-reconfiguration)의 마지막 스테이지 커패시터들(변환이득 6에서의 C5 a, C5 b)에 이르기까지, 커패시터 전압 감소량은 VI/[M×(M+1)]의 증가하는 정수배 형태로 순차적으로 증가한다. 여기서 M은 재구성 이후 새로운 변환이득과 동일하다. 모든 커패시터들에 공통으로 주어진 전이 구간 동안, 상기 전류들의 크기는 상기 전류 소스(91)부터 상기 전류 소스(95)까지 정수배 형태로 연속적으로 증가해야 한다. 키르히호프의 전류 법칙(Kirchhoff's current law)에 의하여, 상기 부하 전류(IL)는 상기 전류 소스들(91-95)과 상기 커패시터들(C6 a, C6 b)에 흐르는 전류의 합과 동일하다.

도 15B는 상기 전이 구간 동안 특별한 구현 예를 도시하고 있으며 여기서 전류 소스들은 상기 제 2 재구성 접근방식을 위한 커패시터들(C1 a-C6 b)의 상기 전압들을 슬루(slew)하기 위해 사용된다. 만일 상기 변환 이득이 7에서 6으로 감소하면, 상기 커패시터들(C1 a-C6 b)의 상기 전압들은 증가해야 한다. 그러므로, 전이 시간 동안, 상기 위상 노드들(P1, P2)은 상기 출력전압(VOD)에 연결되고 그동안 상기 스택 스위치들은 각각의 공통 스테이지의 한 쌍의 커패시터들의 상기 양극 단자들을 자신의 대응하는 dc 노드들(N1 c-N5 c)에 연결하는 방식으로 동작한다. 도 5에 참조하여, 이것은 상기 제 1 스테이지 커패시터들(C1 a, C1 b)을 위한 상기 스택 스위치들(S12, S13 )을 개방하는 동안 상기 스택 스위치들(S10, S11)을 폐쇄한다; 즉, 상기 제 2 스테이지 커패시터들(C2 a, C2 b)을 위한 상기 스택 스위치들(S22, S23)을 개방하는 동안 상기 스택 스위치들(S20, S21 )을 폐쇄한다.; 기타 등등 을 의미한다. 상기 입력전압(VI)으로부터 각각의 상기 dc 노드들(N1 c-N5 c)까지 연결된 전류 소스들(91-95)은 커패시터들을 선형방식으로 충전한다.

상기 포스트-재구성의 제 1 스테이지 커패시터들(변환이득 6에서의 C2 a, C2 b)에서 시작하여 상기 마지막 스테이지 커패시터들(즉. C6 a, C6 b)에 이르기까지, 커패시터 전압 증가는 VI/[M×(M+1)]의 감소하는 정수배 형태로 순차적으로 감소한다. 여기서 M은 재구성 이후 상기 새로운 변환이득과 동일하다. 모든 커패시터들에 공통으로 주어진 전이 구간 동안, 상기 전류들의 크기는 상기 전류 소스(91)부터 상기 전류 소스(95)까지 정수배 형태로 연속적으로 감소해야 한다. 키르히호프의 전류 법칙(Kirchhoff's current law)에 의하여, 상기 부하 전류(IL)는 상기 전류 소스들(91-95)과 상기 커패시터들(C1 a, C1 b)에 흐르는 전류의 합과 동일하다.

도 15C는 변환이득이 6에서 5로 감소 시 제 3 재구성 접근방식(C3 a, C3 b, C4 a, C4 b와 관련됨)에서 상기 전이 구간 동안의 전류 소스의 구현 예를 도시한다. 상기 커패시터들(C4 a, C4 b)은 이전 재구성에서 이미 제거된 것으로 간주되고, 여기서 상기 변환이득이 7에서 6으로 변경된다. 상기 전이 시간 동안, 상기 커패시터들(C1 a, C1 b, C2 a, C2 b) 각각 전압은 감소해야 하며, 그 반대로, 상기 커패시터들(C5 a, C5 b, C6 a, C6 b) 각각의 전압은 증가해야 한다.

이 특별한 예는 낮은 전력 손실 전이 구간을 얻기 위해 분리된 위상 노드들을 가지는 듀얼-위상 캐스케이드 멀티플라이어로 가정하고 여기서 전류 소스들(91-93)은 상기 커패시터들(C1 a-C6 b)을 충전 및 방전하는데 사용된다. 상기 전류 소스들(91-93)은 부하 전류(IL)를 공급하도록 입력전압(VO)에서 합쳐진다. 공유된 위상 노드들과, 이 전이 시간은 상기 전류 소스들(91, 92)이 쉽게 재순환되지 않을 수 있기 때문에 더 많은 전력을 소비할 것이다.

상기 전이 구간(transition interval) 동안, 상기 대응하는 커패시터들(C5 a, C5 b, C6 a, C6 b)의 상기 위상 노드들은 상기 출력전압(VO)에 연결되고 그 동안 상기 잔여 커패시터들의 상기 위상 노드들은 접지에 연결된다. 또한, 상기 전류 소스(91)는 동시에 상시 커패시터들(C1 a, C1 b )을 방전하고 상기 커패시터들 (C6 a, C6 b )을 충전하며 그동안 상기 전류 소스(92)는 동시에 상기 커패시터들(C2 a, C2 b)을 방전하고 상기 커패시터들(C5 a, C5 b )을 충전한다. 이 작업을 위해, 상기 전류 소스(92)의 크기는 상기 전류 소스(91)의 크기보다 정수 배로 더 커야한다.

상기 전이 구간 동안 상기 커패시터 전압들을 슬루(slew)하기 위해 전압 혹은 전류 소스를 추가적으로 사용하는 대신에, 이와 같은 목적으로 부하 전류 (IL)을 직접적으로 사용하는 것은 가능하다. 선택된 커패시터들에게 시간-기반 스큐(time-based skew)를 적용함으로써, 정상 상태를 넘어서 원하는 방향으로 자신의 전압을 변경하는 것은 가능하다. 예를 들어, 도 16은 상기 듀얼-위상 캐스케이드 멀티플라이어(34)에서 시간 t1에서 시간 t2 동안의 전이 시간 동안에서의 샘플 타이밍-다이아그램(timing-diagram)을 도시하며, 여기서 상기 제 3 재구성 접근 방식을 이용하여 상기 변환 이득이 7에서 6으로 변경된다. 상기 제 1 위상을 위한 상기 대응하는 신호들만이 도 16에서 설명하고 있다는 것을 주의해야 한다.

정상 동작에서의 전이 구간 동안, 특정한 주파수로 반복되는 제 1 상태 및 제 2 상태가 있다. 또한, 상기 스택 스위치들(S10, S11, S63, S62 )은 전이 구간(transition interval)의 전체 시간 동안 개방된다. 결과적으로, 상기 커패시터들(C1 a, C1 b)은 상기 커패시터들(C2 b, C2 a)과 직렬로 연결될 때에만 방전되지만, 상기 입력전압(VI)으로부터는 충전되지 않아서, 그 결과로 전하의 순 유출 및 커패시터 전압의 감소가 일어난다. 반대로, 상기 커패시터들 (C6 a, C6 b )은 상기 커패시터들(C5 b, C5 a )과 직렬로 연결될 때에만 충전되지만, 상기 출력전압(VO)으로 방전은 되지 않아, 그 결과로 전하의 순 유입 및 커패시터 전압의 증가가 일어난다.

다행스럽게도, 상기 제 3 재구성 접근 방식에서, 변환이득의 감소는 상기 커패시터들(C1 a, C1 b)에 걸리는 전압이 더 낮게 되지만, 상기 커패시터들(C6 a, C6 b)에 걸리는 전압은 더 높아진다. 그러므로 상기 재구성이 일어날 때, 그 결과인 전하의 재분포(redistribution)는 상기 전이 구간 및 상기 외부 커패시터들(C1 a, C1 b, C6 a, C6 b)에서의 시간 기반 스큐(time-based skew)없이 일어나는 것보다 더 작다

상기 전이 구간의 듀레이션(duration)은 하나의 스위칭 주기 혹은 스위칭 주기의 몇 배의 정수 배만큼 짧을 수 있다. (예, 시간 t1 에서 시간 t2 까지의 듀레이션(duration)의 2배) 비록 상기 전이 시간의 상기 듀레이션(duration)이 상기 스위치드 커패시터 전력 컨버터의 스위칭 주기의 정수배가 될 필요는 없지만, 타이밍 동기화 및 동작 대칭성의 관점에서 이점이 될 수 있다

또한, 상기 시간-기반 스큐 기술은 상기 다른 재구성 접근방식에도 물론 적합하다. 예를 들어 제 1 접근 방식을 사용하여 변환이득을 7에서 6으로 변경할 때, 상기 커패시터들(C6 a, C6 b)은 제거되고 및 상기 잔여 커패시터들에 걸리는 전압들을 감소한다. 상기 커패시터들(C1 a, C1 b)에 걸리는 상기 전압들은 상기 전이 구간 동안에 감소하기 때문에, 그 결과인 재구성 시의 전하 재분포(redistribution)는 더 작아짐으로써, 상기 대응하는 과도 전류 및 전압의 크기는 줄어든다.

불행히도, 시간-기반 스큐(time-based skew) 기술을 사용하여 전하 재분배를 감소시키는 것은 상기 외부 커패시터의 전압들만이 상기 전이 구간 동안 변경되기 때문에 본질적으로 제한된다. 또한, 출력전압(VO) 에서의 상기 최대 혹은 최소 허용되는 리플 크기는 상기 전이 시간 동안 외부 커패시터 전압 변경의 크기를 제한할 수 있다. 어떤 경우에서도, 이 방법의 이점을 최대화하기 위해 상기 출력 전류의 크기 및 상기 스위치드 커패시터 회로 주파수의 기능으로 전이 시간의 듀레이션을 커스터마이즈(customize)하는 것은 가능할 것이다.

다양한 특징들, 양상들, 및 스위치드 커패시터 전력 컨버터들의 실시 예들이 본 발명에 기술되어 있다. 본 발명에 설명된 다양한 특징들, 양상들, 및 수많은 실시 예들은 변형과 수정뿐만 아니라 서로 조합하기 쉬우며, 당해 기술 분야에서 통상 지식을 가진 자들에 의해 이해될 것이다. 본 발명은, 따라서, 그러한 조합들, 변형들, 및 수정들을 포함하는 것으로 간주되어야 한다. 또한, 본 명세서에 사용된 용어들과 표현들은 제한의 용어가 아닌 설명을 위한 용어로 사용된다. 그러한 용어들과 표현들을 사용하는 데에, 도시되고 기재된 임의의 등가물들을 제외할 의도는 없으며, 다양한 변경들은 청구 범위 내에서 가능하다고 인식된다. 다른 수정들, 변형들, 및 대안들은 또한 가능하다. 따라서, 청구 범위들은 이러한 모든 등가물들을 포함하도록 의도된다.

Claims (29)

- 제 1 전압을 제 2 전압으로 변환하기 위한 장치에 있어서, 상기 장치는 선택 가능한 변환이득을 가지는 재구성 가능한 스위치드 커패시터 전력 컨버터를 포함하고,

상기 재구성 가능한 스위치드 커패시터 전력 컨버터는 제 1 캐스케이드 멀티플라이어 스위치드 커패시터 네트워크를 포함하며, 상기 제 1 캐스케이드 멀티플라이어 스위치드 커패시터 네트워크느 복수의 커패시터들 - 상기 복수의 커패시터들 각각은 상기 복수의 커패시터들의 제 1 단자에서 상기 커패시터와 관련된 스택 노드 및 상기 복수의 커패시터들의 제 2 단자에서 상기 커패시터와 관련된 위상 노드에 전기적으로 연결되고, 상기 복수의 커패시터들은 제 1 외부 커패시터, 제 2 외부 커패시터, 및 상기 제 1 외부 커패시터와 상기 제 2 외부 커패시터 사이의 적어도 하나의 내부 커패시터를 포함함 -, 복수의 커패시터들로부터 인접한 커패시터들의 노드들 사이의 복수의 스택 스위치들, 및 상기 제 1 캐스케이드 멀티플라이어 스위치드 커패시터 네트워크를 제 1 동작 모드와 제 2 동작 모드사이의 전이를 일으키기 위한 제어기를 포함하되,

상기 제 1 동작모드에서 적어도 하나의 커패시터가 상기 재구성 가능한 스위치드 커패시터 전력 컨버터의 전하 이동 경로 - 상기 전하 이동 경로는 상기 제 1 전압과 상기 제 2 전압 사이에 확장됨 - 에서 고립되고, 상기 제 1 동작모드에서 상기 재구성 가능한 스위치드 커패시터 전력 컨버터는 제 1 변환 이득으로 동작하고 및 상기 제 2 동작 모드에서 상기 재구성 가능한 스위치드 커패시터 전력 컨버터는 제 2 변환 이득으로 동작하며, 및 이에 의해 상기 적어도 하나의 커패시터에 걸리는 제 3 전압은 어떤 값이라도 가지는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치. - 제 1 항에 있어서, 동작 시, 상기 제 3 전압은 상기 제 1 전압과 상기 제 2 전압 사이에 있는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 1항에 있어서, 상기 전압 변환을 위한 장치는 프리-차지 회로 - 상기 프리-차지 회로는 상기 적어도 하나의 커패시터를 특정 전압으로 충전하기 위해 구성됨 를 더 포함하는 것을 특징으로 하는 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 1항에 있어서, 상기 적어도 하나의 커패시터가 내부 커패시터인 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 1항에 있어서, 전압 변환을 위한 장치는 스위칭 네트워크를 더 포함하되, 상기 스위칭 네트워크는 상기 적어도 하나의 커패시터를 선택적으로 바이패스하는 스위치들을 포함하는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 1항에 있어서, 상기 제어기는 상기 적어도 하나의 커패시터를 고립시키기 위해 상기 제 1 단자 및 상기 제 2 단자로 구성된 그룹에서 선택된 최대 하나의 단자의 연결을 해제하는 것으로 구성되는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 1항에 있어서, 상기 제 1 단자는 양극 단자인 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 6항에 있어서, 상기 전하 이동 경로에서 상기 커패시터들의 서브세트의 연결해제를 허용하기 위해 배치되는 스택 스위치들의 집합을 더 포함하되, 상기 제어기는 상기 전하 전송 경로로부터 상기 커패시터들의 서브세트의 연결을 해제하기 위해 상기 스택 스위치들의 서브세트를 선택적으로 개방하도록 구성되어짐으로써, 상기 전하 전송 경로를 재구성하는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 1항에 있어서, 상기 전압 변환을 위한 장치는 상기 전하 이동 경로에서 상기 커패시터들의 서브세트의 연결 해제를 허용하도록 배치되는 위상 스위치들의 집합을 더 포함하되, 상기 제어기는 상기 위상 스위치들의 서브세트를 선택적으로 개방하여 커패시터들의 서브세트가 상기 전하 전송 경로로부터 연결 해제됨으로써, 상기 전하 이동 경로를 재구성하도록 구성되는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 1 항에 있어서, 상기 전압 변환을 위한 장치는 상기 제 1 전압을 제공하기 위한 제 1 외부 회로를 더 포함하는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 1 항에 있어서, 상기 전압 변환을 위한 장치는 상기 제 2 전압을 수신하기 위한 제 2 외부 회로를 더 포함하는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 1항에 있어서, 상기 복수의 커패시터들 중 각각의 커패시터는, 제 2 단자에서, 복수의 위상 노들들 중 대응하는 하나에 연결되는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 1항에 있어서, 적어도 두 개의 상기 커패시터들은 공통 위상 노드에 연결되는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 1항에 있어서, 상기 전압 변환을 위한 장치는 복수의 커패시터들을 가지는 제 2 캐스케이드 멀티플라이어 스위치드 커패시터를 더 포함하되, 상기 복수의 커패시터들 각각은 상기 제 1 캐스케이드 멀티플라이어 스위치드 커패시터의 커패시터에 대응함으로써, 제 1 및 제 2 캐스케이드 멀티플라이어 스위치드 커패시터 네트워크들은 전기적으로 병렬 상태로 있는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 14항에 있어서, 상기 제 1 및 제 2 캐스케이드 멀티플라이어 스위치드 커패시터 네트워크들에서 대응하는 커패시터들은 캐스코드 스택 스위치들 사이에 공통 노드들에 연결되는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 1항에 있어서, 전압 변환을 위한 장치는 인접한 커패시터들 사이에 캐스코드 스택 스위치들을 더 포함하는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 16항에 있어서, 상기 캐스코드 스택 스위치들은 인접한 커패시터들 사이의 노드에서의 전압을 제어하기 위해 전압 클램프를 더 포함하는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 16항에 있어서, 상기 캐스코드 스택 스위치들은 인접한 커패시터들 사이의 노드에서의 전압을 제어하기 위해서 전압 레귤레이터를 더 포함하는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 1 전압을 제 2 전압으로 변환하기 위한 장치에 있어서, 상기 장치는 선택 가능한 변환 이득을 가지는 재구성 가능한 스위치드 커패시터 전력 컨버터를 포함하며,

상기 재구성 가능한 스위치드 커패시터 전력 컨버터는 커패시터들을 서로 및/혹은 연속적인 상태의 제 1 또는 제2 전압에 전기적으로 상호 연결하도록 구성되는 복수의 스위치 소자들- 상기 스위치 소자들은 적어도 몇 개의 커패시터들이 상기 스위치 소자들을 통하여 서로 상호 연결되도록 구성됨 -, 상기 재구성 가능한 스위치드 커패시터 전력 컨버터가 제 1 동작 모드와 제 2 동작 모드 사이에서 전이되도록 하는 제어기를 포함하되, 상기 제어기는 상기 제 1 모드에서 상기 제 2 모드로 전이를 발생시키는 전기적 과도현상을 최소화 하도록 구성됨으로써, 상기 제 1 동작모드에서 상기 재구성 가능한 스위치드 커패시터 전력 컨버터들은 제 1 변환이득으로 동작하며, 상기 제 2 동작모드에서 상기 재구성 스위치드 커패시터 전력 컨버터는 제 2 변환 이득으로 동작하는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치. - 제 19항에 있어서, 상기 제어기는 상기 전이 시간 동안에 상기 재구성 가능한 스위치드 커패시터 전력 컨버터의 스위칭 주파수를 상승시킴으로써 상기 제 1 모드에서 상기 제 2 모드로 전이 다음의 전이 시간 동안 전기적 과도현상을 최소화하도록 구성되는 것을 특징으로 하는 전압 변환 장치

- 제 20 항에 있어서, 프리 차지 바이패스 커패시터를 더 포함하며, 상기 제어기는 프리-차지된 바이패스 커패시터에서 스위치되는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 20 항에 있어서, 상기 제어기는 양방향(bidirectional) 전류 리미터(limiter)를 사용하여 입력 전류를 억압하도록 구성되는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 20항에 있어서, 상기 제어기는 온-저항을 변조함으로써 입력 전류를 억압하도록 구성되는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 19항에 있어서, 상기 제어기는 상기 제 1 모드의 동작 중지 이후 및 제 2 동작 모드의 시작 전의 과도 시간 동안, 상기 커패시터들이 제 2 모드 동안 도달하는 값으로 적어도 하나의 상기 커패시터들에 걸리는 전압을 슬루잉(slewing)함으로써 전기적 과도현상을 최소화 하도록 구성되어지는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 24항에 있어서, 상기 제어기는 전압 레귤레이터를 사용하여 상기 전압들을 슬루(slew) 하도록 구성되는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 24항에 있어서, 상기 제어기는 전류 레귤레이터를 사용하여 상기 전압들을 슬루(slew) 하도록 구성되는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 24항에 있어서 상기 제어기는 출력 전류를 사용하여 상기 전압들을 슬루(slew)하도록 구성되는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 21항에 있어서, 상기 제어기는 상기 제 1 모드의 동작 중지 이후 및 제 2 모드의 동작 시작 전의 전이 시간 동안, 전기적 과도현상을 최소화 하도록 구성되는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

- 제 1 전압을 제 2전압으로 변환하기 위한 장치에 있어서,

상기 장치는 선택할 수 있는 변환이득을 구비한 재구성 가능한 스위치드 커패시터 전력 컨버터를 포함하며,

상기 재구성 가능한 스위치드 커패시터 전력 컨버터는 커패시터들을 서로 및/혹은 연속적인 상태에 있는 제 1 또는 제 2 전압에 전기적으로 상호 연결하도록 구성되는 복수의 스위치 소자들 - 상기 스위치 소자들은 적어도 일부 커패시터들을 상기 스위치 소자들을 통하여 서로 상호 연결하도록 구성됨-, 상기 재구성 가능한 스위치드 커패시터 전력 컨버터를 제 1 동작 모드와 제 2 동작 모드 사이에 전이를 일으키기 위한 제어기를 포함하되,

상기 제 1 모드에서 상기 제 2 모드로 전이한 다음의 전이 시간 동안 전기적 과도현상을 최소화하도록 구성됨에 의해, 상기 제 1 동작 모드에서 상기 재구성 가능한 스위치드 커패시터 전력 컨버터는 제 1 변환이득으로 동작하고, 상기 제 2 동작모드에서 상기 재구성 가능한 스위치드 커패시터 전력 컨버터는 제 2 변환이득으로 동작하고,

상기 제어기는 상기 전이 시간 동안 상기 재구성 가능한 스위치드 커패시터 전력 컨버터의 스위칭 주파수를 상승시킴으로써 상기 제 1모드에서 상기 제 2모드로 전이 다음의 전이 시간 동안 전기적 과도현상을 최소화시키는 것, 프리-차지된 바이패스 커패시터에서의 스위칭, 및 쌍방향 전류 리미터 및 변조된 온-저항 중 하나를 사용하여 입력 전류를 억압하는 방법으로 구성된 그룹에서 선택된 동작을 수행하도록 구성되는 것을 특징으로 하는 제 1 전압을 제 2 전압으로 변환하기 위한 장치.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020217007362A KR102435623B1 (ko) | 2013-03-15 | 2014-03-12 | 재구성 가능한 스위치드 커패시터 전력 컨버터 기술들 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13/839,315 | 2013-03-15 | ||

| US13/839,315 US9203299B2 (en) | 2013-03-15 | 2013-03-15 | Controller-driven reconfiguration of switched-capacitor power converter |

| PCT/US2014/024143 WO2014150756A1 (en) | 2013-03-15 | 2014-03-12 | Reconfigurable switched capacitor power converter techniques |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020217007362A Division KR102435623B1 (ko) | 2013-03-15 | 2014-03-12 | 재구성 가능한 스위치드 커패시터 전력 컨버터 기술들 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20150131361A true KR20150131361A (ko) | 2015-11-24 |

| KR102228738B1 KR102228738B1 (ko) | 2021-03-16 |

Family

ID=51358596

Family Applications (4)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020217007362A KR102435623B1 (ko) | 2013-03-15 | 2014-03-12 | 재구성 가능한 스위치드 커패시터 전력 컨버터 기술들 |

| KR1020157029889A KR102228738B1 (ko) | 2013-03-15 | 2014-03-12 | 재구성 가능한 스위치드 커패시터 전력 컨버터 기술들 |

| KR1020237025761A KR20230116101A (ko) | 2013-03-15 | 2014-03-12 | 재구성 가능한 스위치드 커패시터 전력 컨버터 기술들 |

| KR1020227028647A KR102562452B1 (ko) | 2013-03-15 | 2014-03-12 | 재구성 가능한 스위치드 커패시터 전력 컨버터 기술들 |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020217007362A KR102435623B1 (ko) | 2013-03-15 | 2014-03-12 | 재구성 가능한 스위치드 커패시터 전력 컨버터 기술들 |

Family Applications After (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020237025761A KR20230116101A (ko) | 2013-03-15 | 2014-03-12 | 재구성 가능한 스위치드 커패시터 전력 컨버터 기술들 |

| KR1020227028647A KR102562452B1 (ko) | 2013-03-15 | 2014-03-12 | 재구성 가능한 스위치드 커패시터 전력 컨버터 기술들 |

Country Status (7)

| Country | Link |

|---|---|

| US (7) | US9203299B2 (ko) |

| KR (4) | KR102435623B1 (ko) |

| CN (2) | CN109217658B (ko) |

| DE (1) | DE112014001395T5 (ko) |

| GB (4) | GB2526493B (ko) |

| TW (1) | TWI631805B (ko) |

| WO (1) | WO2014150756A1 (ko) |

Families Citing this family (81)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10389235B2 (en) | 2011-05-05 | 2019-08-20 | Psemi Corporation | Power converter |

| GB2505371B (en) | 2011-05-05 | 2018-02-28 | Arctic Sand Technologies Inc | DC-DC converter with modular stages |

| US9882471B2 (en) | 2011-05-05 | 2018-01-30 | Peregrine Semiconductor Corporation | DC-DC converter with modular stages |

| US10680515B2 (en) | 2011-05-05 | 2020-06-09 | Psemi Corporation | Power converters with modular stages |

| TWI439840B (zh) * | 2012-03-13 | 2014-06-01 | Ili Technology Corp | Charge pump |

| US8724353B1 (en) * | 2013-03-15 | 2014-05-13 | Arctic Sand Technologies, Inc. | Efficient gate drivers for switched capacitor converters |

| US8619445B1 (en) * | 2013-03-15 | 2013-12-31 | Arctic Sand Technologies, Inc. | Protection of switched capacitor power converter |

| US9203299B2 (en) | 2013-03-15 | 2015-12-01 | Artic Sand Technologies, Inc. | Controller-driven reconfiguration of switched-capacitor power converter |

| WO2014174889A1 (ja) * | 2013-04-25 | 2014-10-30 | シャープ株式会社 | 表示装置及びその駆動方法 |

| US9716188B2 (en) * | 2013-08-30 | 2017-07-25 | Qualcomm Incorporated | Metal oxide semiconductor (MOS) capacitor with improved linearity |

| CN105612470B (zh) * | 2013-10-07 | 2019-04-30 | 莱恩半导体股份有限公司 | 混合电压调节器中的反馈控制 |

| EP2905885B1 (en) * | 2014-02-07 | 2018-06-13 | General Electric Technology GmbH | DC/DC converter |

| KR20160138068A (ko) * | 2014-03-28 | 2016-12-02 | 톰슨 라이센싱 | Dc/dc 컨버터 및 dc/dc 컨버터를 구동시키는 방법 |

| US9866110B2 (en) * | 2014-08-27 | 2018-01-09 | Analog Devices Global | DC-DC switched capacitor voltage converter with series and parallel switched capacitors during discharge |

| US9491151B2 (en) * | 2015-01-07 | 2016-11-08 | Ememory Technology Inc. | Memory apparatus, charge pump circuit and voltage pumping method thereof |

| US10879787B2 (en) * | 2015-03-11 | 2020-12-29 | Telcodium Inc. | Power supply connecting board with variable output voltage levels |

| DE112016001194T5 (de) | 2015-03-13 | 2017-11-30 | Peregrine Semiconductor Corporation | Gleichstrom-Gleichstrom-Wandler mit Induktivität zur Ermöglichung eines adiabatischen Inter-Kondensator-Ladungstransports |

| AU2016246814B2 (en) | 2015-04-10 | 2020-07-16 | Epc Power Corporation | Reconfigurable power converter |

| US9263965B1 (en) * | 2015-04-22 | 2016-02-16 | Lawrence A. Leske | Producing an odd number full wave voltage multiplier |

| PL3145069T3 (pl) | 2015-09-21 | 2019-08-30 | Politechnika Gdańska | Obwód i sposób kanonicznego i adiabatycznego przetwarzania napięcia dc-dc |

| TWI575858B (zh) * | 2015-10-07 | 2017-03-21 | 晨星半導體股份有限公司 | 切換式電壓轉換器 |

| WO2017143044A1 (en) * | 2016-02-16 | 2017-08-24 | Arctic Sand Technologies, Inc. | Switched capacitors for ac-dc applications |

| WO2017148404A1 (en) * | 2016-03-02 | 2017-09-08 | The Hong Kong University Of Science And Technology | Two-phase, three-phase reconfigurable switched-capacitor power converter |

| US10476382B2 (en) | 2016-03-03 | 2019-11-12 | The Regents Of The University Of Michigan | Energy harvester |

| US9800143B2 (en) * | 2016-03-03 | 2017-10-24 | The Regents Of The University Of Michigan | Moving-sum charge pump |

| JP2019512995A (ja) | 2016-03-11 | 2019-05-16 | ピーセミ コーポレーションpSemi Corporation | 断熱的スイッチドキャパシタ回路を有するバッテリ管理システム |

| US10541603B2 (en) * | 2016-04-18 | 2020-01-21 | Lion Semiconductor Inc. | Circuits for a hybrid switched capacitor converter |

| US10289146B2 (en) * | 2016-04-18 | 2019-05-14 | Lion Semiconductor Inc. | Reconfigurable dickson star switched capacitor voltage regulator |

| CN109478845B (zh) * | 2016-05-09 | 2021-03-23 | 派赛公司 | 功率转换器 |

| TWI605675B (zh) * | 2016-08-09 | 2017-11-11 | 新唐科技股份有限公司 | 直流對直流電源轉換器電路及使用其控制輸出電壓之方 法 |

| TWI626806B (zh) * | 2016-09-20 | 2018-06-11 | 立錡科技股份有限公司 | 充電電路及其電容式電源轉換電路與充電控制方法 |

| KR102214243B1 (ko) * | 2016-11-01 | 2021-02-09 | 라이온 세미컨덕터 인크. | 전하 재활용 스위치드 커패시터 레귤레이터 |

| US10270368B2 (en) * | 2016-12-02 | 2019-04-23 | Lawrence Livermore National Security, Llc | Bi-directional, transformerless voltage system |

| US11153819B2 (en) * | 2017-02-06 | 2021-10-19 | Itron Networked Solutions, Inc. | Battery control for safeguarding lower voltage integrated circuits |

| CN108429445B (zh) * | 2017-02-13 | 2020-04-14 | 珠海全志科技股份有限公司 | 一种应用于电荷泵的软启动电路 |

| DE102017204044A1 (de) * | 2017-02-14 | 2018-08-16 | Ellenberger & Poensgen Gmbh | Verfahren und Spannungsvervielfacher zur Wandlung einer Eingangsspannung sowie Trennschaltung |

| CN116707268A (zh) | 2017-04-03 | 2023-09-05 | 韩国科学技术院 | 多路径转换器及其控制方法 |

| KR102051570B1 (ko) * | 2017-04-03 | 2019-12-05 | 한국과학기술원 | 멀티 패스를 가지는 컨버터 및 이의 제어 방법 |

| US10122256B1 (en) * | 2017-07-13 | 2018-11-06 | Infineon Technologies Austria Ag | Method and apparatus for zero-current switching control in switched-capacitor converters |

| US10680512B2 (en) * | 2017-07-19 | 2020-06-09 | Infineon Technologies Austria Ag | Switched-capacitor converters with capacitor pre-charging |

| JP6608405B2 (ja) * | 2017-07-19 | 2019-11-20 | 矢崎総業株式会社 | 電圧変換ユニット |

| CN107257193B (zh) * | 2017-07-19 | 2019-05-03 | 深圳市华星光电半导体显示技术有限公司 | 一种过流保护电路及液晶显示器 |

| CN107422779B (zh) * | 2017-08-21 | 2019-02-22 | 南京矽力杰半导体技术有限公司 | 电压调节器 |

| KR101997838B1 (ko) * | 2017-09-19 | 2019-10-01 | 충북대학교 산학협력단 | 재구성가능한 스위치드 커패시터 어레이를 이용한 에너지 재활용 전압 스케일러 및 전압제어방법 |

| CN107834844B (zh) * | 2017-10-19 | 2020-04-03 | 华为技术有限公司 | 一种开关电容变换电路、充电控制系统及控制方法 |

| CN107742978B (zh) * | 2017-11-06 | 2019-12-03 | 北京大学深圳研究生院 | 具有增强驱动能力的电荷泵电路 |

| JP6958287B2 (ja) | 2017-11-24 | 2021-11-02 | トヨタ自動車株式会社 | 電力制御システムおよび車両 |

| US10224803B1 (en) | 2017-12-20 | 2019-03-05 | Infineon Technologies Austria Ag | Switched capacitor converter with compensation inductor |

| US10199928B1 (en) * | 2018-01-19 | 2019-02-05 | Infineon Technologies Austria Ag | Soft start of switched capacitor converters by reducing voltage provided by initial power switch |

| TWI671974B (zh) * | 2018-02-13 | 2019-09-11 | 立錡科技股份有限公司 | 充電電路及其電源轉換電路 |

| US10263514B1 (en) | 2018-03-13 | 2019-04-16 | Psemi Corporation | Selectable conversion ratio DC-DC converter |

| US10193448B1 (en) | 2018-03-26 | 2019-01-29 | Semiconductor Components Industries, Llc | Method of forming a power supply control circuit and structure therefor |

| US10439493B1 (en) | 2018-05-01 | 2019-10-08 | Semiconductor Components Industries, Llc | Methods and systems of operating a resonant dickson converter |

| US10790740B2 (en) | 2018-05-02 | 2020-09-29 | Analog Devices Global Unlimited Company | Techniques for switch capacitor regulator power savings |

| CN108599591B (zh) * | 2018-06-06 | 2023-08-25 | 三峡大学 | 一种自均流模块化大容量高升压整流器 |

| US10340794B1 (en) | 2018-06-21 | 2019-07-02 | Linear Technology Llc | Reverse capacitor voltage balancing for high current high voltage charge pump circuits |

| US20190393776A1 (en) | 2018-06-25 | 2019-12-26 | Psemi Corporation | Start-up of step-up power converter with switched-capacitor network |

| CN108880256B (zh) * | 2018-06-29 | 2019-12-24 | 西安交通大学 | 一种适用于多层堆叠负载的多路输出开关电容变换器 |

| US10749512B2 (en) * | 2018-10-08 | 2020-08-18 | Skyworks Solutions, Inc. | Switch control circuitry |

| TWI682614B (zh) * | 2018-10-26 | 2020-01-11 | 緯穎科技服務股份有限公司 | 多相位電源降壓系統 |

| CN111181401B (zh) * | 2018-11-12 | 2021-01-26 | 台达电子企业管理(上海)有限公司 | 开关谐振腔变换器 |

| CN109617394B (zh) * | 2018-12-05 | 2021-08-17 | 成都芯源系统有限公司 | 谐振开关电容变换器及其控制器和控制方法 |

| TWI689161B (zh) * | 2018-12-22 | 2020-03-21 | 新唐科技股份有限公司 | 功率轉換器 |

| US10693367B1 (en) * | 2019-02-19 | 2020-06-23 | Rolls-Royce North American Technologies, Inc. | Pre-charging circuit for power converters |

| US10686367B1 (en) | 2019-03-04 | 2020-06-16 | Psemi Corporation | Apparatus and method for efficient shutdown of adiabatic charge pumps |

| US10734893B1 (en) | 2019-05-03 | 2020-08-04 | Psemi Corporation | Driving circuit for switches used in a charge pump |

| US10693370B1 (en) * | 2019-05-08 | 2020-06-23 | Marko Krstic | Switched-capacitor converter with high step-up/step-down conversion ratio |

| EP4010975A4 (en) * | 2019-08-11 | 2023-08-16 | Barthold, Lionel O. | GRADUATED POWER CONVERSION |

| US10924006B1 (en) | 2019-09-30 | 2021-02-16 | Psemi Corporation | Suppression of rebalancing currents in a switched-capacitor network |

| US10958166B1 (en) | 2020-02-06 | 2021-03-23 | Psemi Corporation | Startup of switched capacitor step-down power converter |

| US11294438B2 (en) * | 2020-04-29 | 2022-04-05 | Dell Products L.P. | System and method of providing power from one portion of an information handling system to another portion of the information handling system |

| CN111682756B (zh) * | 2020-06-09 | 2021-10-26 | 杭州艾诺半导体有限公司 | 混合功率变换器及其控制方法 |

| CN111682753B (zh) * | 2020-06-09 | 2021-10-26 | 杭州艾诺半导体有限公司 | 混合功率变换器及其控制方法 |

| CN111682755B (zh) * | 2020-06-09 | 2022-02-15 | 杭州艾诺半导体有限公司 | 混合功率变换器 |

| US11374400B2 (en) | 2020-12-01 | 2022-06-28 | Rolls-Royce Singapore Pte. Ltd. | Topology of a solid state power controller with two mid-capacitors |