KR20150128743A - 전도성 나노-필러로 도핑된 유전성 폴리머 기반 프랙셔널 오더 커패시터 - Google Patents

전도성 나노-필러로 도핑된 유전성 폴리머 기반 프랙셔널 오더 커패시터 Download PDFInfo

- Publication number

- KR20150128743A KR20150128743A KR1020157026181A KR20157026181A KR20150128743A KR 20150128743 A KR20150128743 A KR 20150128743A KR 1020157026181 A KR1020157026181 A KR 1020157026181A KR 20157026181 A KR20157026181 A KR 20157026181A KR 20150128743 A KR20150128743 A KR 20150128743A

- Authority

- KR

- South Korea

- Prior art keywords

- fractional order

- capacitors

- capacitor

- manufacturing

- electrode layer

- Prior art date

Links

- 239000003990 capacitor Substances 0.000 title claims abstract description 181

- 239000000945 filler Substances 0.000 title claims abstract description 20

- 229920000642 polymer Polymers 0.000 title claims description 19

- 239000002114 nanocomposite Substances 0.000 claims abstract description 80

- 239000000463 material Substances 0.000 claims abstract description 61

- 230000001419 dependent effect Effects 0.000 claims abstract description 4

- 238000000034 method Methods 0.000 claims description 92

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 claims description 46

- 229910021389 graphene Inorganic materials 0.000 claims description 42

- 238000004519 manufacturing process Methods 0.000 claims description 27

- 238000004891 communication Methods 0.000 claims description 19

- 239000011159 matrix material Substances 0.000 claims description 17

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 claims description 17

- 229910052782 aluminium Inorganic materials 0.000 claims description 9

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 claims description 9

- 229920000144 PEDOT:PSS Polymers 0.000 claims description 8

- 238000005266 casting Methods 0.000 claims description 8

- 239000004020 conductor Substances 0.000 claims description 8

- 229910052697 platinum Inorganic materials 0.000 claims description 8

- 230000004044 response Effects 0.000 claims description 6

- 238000004806 packaging method and process Methods 0.000 claims description 5

- 238000007650 screen-printing Methods 0.000 claims description 4

- 238000007599 discharging Methods 0.000 claims description 3

- 238000010345 tape casting Methods 0.000 claims description 3

- 230000003111 delayed effect Effects 0.000 claims description 2

- 238000007731 hot pressing Methods 0.000 claims description 2

- 238000011017 operating method Methods 0.000 claims 1

- 239000010410 layer Substances 0.000 description 95

- 239000000758 substrate Substances 0.000 description 13

- 239000000243 solution Substances 0.000 description 11

- 229920000767 polyaniline Polymers 0.000 description 8

- 239000011248 coating agent Substances 0.000 description 7

- 238000000576 coating method Methods 0.000 description 7

- 238000013461 design Methods 0.000 description 7

- 239000004793 Polystyrene Substances 0.000 description 6

- 229920002223 polystyrene Polymers 0.000 description 6

- 230000008569 process Effects 0.000 description 6

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 5

- 230000015572 biosynthetic process Effects 0.000 description 5

- 238000011049 filling Methods 0.000 description 5

- 238000011068 loading method Methods 0.000 description 5

- 239000010703 silicon Substances 0.000 description 5

- 229910052710 silicon Inorganic materials 0.000 description 5

- IAZDPXIOMUYVGZ-UHFFFAOYSA-N Dimethylsulphoxide Chemical compound CS(C)=O IAZDPXIOMUYVGZ-UHFFFAOYSA-N 0.000 description 4

- 230000008901 benefit Effects 0.000 description 4

- 229910052751 metal Inorganic materials 0.000 description 4

- 239000002184 metal Substances 0.000 description 4

- 238000012360 testing method Methods 0.000 description 4

- 229910000838 Al alloy Inorganic materials 0.000 description 3

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 3

- 230000008859 change Effects 0.000 description 3

- 239000002131 composite material Substances 0.000 description 3

- 229920001940 conductive polymer Polymers 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 239000010949 copper Substances 0.000 description 3

- 229910002804 graphite Inorganic materials 0.000 description 3

- 239000010439 graphite Substances 0.000 description 3

- 239000000203 mixture Substances 0.000 description 3

- 239000002086 nanomaterial Substances 0.000 description 3

- 238000007645 offset printing Methods 0.000 description 3

- CSCPPACGZOOCGX-UHFFFAOYSA-N Acetone Chemical compound CC(C)=O CSCPPACGZOOCGX-UHFFFAOYSA-N 0.000 description 2

- 229910001316 Ag alloy Inorganic materials 0.000 description 2

- 229910000846 In alloy Inorganic materials 0.000 description 2

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 2

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 239000003989 dielectric material Substances 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 239000010931 gold Substances 0.000 description 2

- IKDUDTNKRLTJSI-UHFFFAOYSA-N hydrazine hydrate Chemical compound O.NN IKDUDTNKRLTJSI-UHFFFAOYSA-N 0.000 description 2

- 238000007641 inkjet printing Methods 0.000 description 2

- 239000012528 membrane Substances 0.000 description 2

- 239000002245 particle Substances 0.000 description 2

- 239000002861 polymer material Substances 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 239000004332 silver Substances 0.000 description 2

- 238000004088 simulation Methods 0.000 description 2

- 229920004142 LEXAN™ Polymers 0.000 description 1

- 239000004418 Lexan Substances 0.000 description 1

- 229910000861 Mg alloy Inorganic materials 0.000 description 1

- 229920001609 Poly(3,4-ethylenedioxythiophene) Polymers 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- 229920004738 ULTEM® Polymers 0.000 description 1

- ULGYAEQHFNJYML-UHFFFAOYSA-N [AlH3].[Ca] Chemical compound [AlH3].[Ca] ULGYAEQHFNJYML-UHFFFAOYSA-N 0.000 description 1

- JFBZPFYRPYOZCQ-UHFFFAOYSA-N [Li].[Al] Chemical compound [Li].[Al] JFBZPFYRPYOZCQ-UHFFFAOYSA-N 0.000 description 1

- JHYLKGDXMUDNEO-UHFFFAOYSA-N [Mg].[In] Chemical compound [Mg].[In] JHYLKGDXMUDNEO-UHFFFAOYSA-N 0.000 description 1

- 230000004075 alteration Effects 0.000 description 1

- SNAAJJQQZSMGQD-UHFFFAOYSA-N aluminum magnesium Chemical compound [Mg].[Al] SNAAJJQQZSMGQD-UHFFFAOYSA-N 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 238000012512 characterization method Methods 0.000 description 1

- HEDRZPFGACZZDS-UHFFFAOYSA-N chloroform Substances ClC(Cl)Cl HEDRZPFGACZZDS-UHFFFAOYSA-N 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 230000001276 controlling effect Effects 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- HTXDPTMKBJXEOW-UHFFFAOYSA-N dioxoiridium Chemical compound O=[Ir]=O HTXDPTMKBJXEOW-UHFFFAOYSA-N 0.000 description 1

- 238000003618 dip coating Methods 0.000 description 1

- 238000007606 doctor blade method Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 230000005518 electrochemistry Effects 0.000 description 1

- 238000004146 energy storage Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000001704 evaporation Methods 0.000 description 1

- 238000007646 gravure printing Methods 0.000 description 1

- LHJOPRPDWDXEIY-UHFFFAOYSA-N indium lithium Chemical compound [Li].[In] LHJOPRPDWDXEIY-UHFFFAOYSA-N 0.000 description 1

- YZASAXHKAQYPEH-UHFFFAOYSA-N indium silver Chemical compound [Ag].[In] YZASAXHKAQYPEH-UHFFFAOYSA-N 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 238000007733 ion plating Methods 0.000 description 1

- 229910052741 iridium Inorganic materials 0.000 description 1

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 1

- 229910000457 iridium oxide Inorganic materials 0.000 description 1

- GCICAPWZNUIIDV-UHFFFAOYSA-N lithium magnesium Chemical compound [Li].[Mg] GCICAPWZNUIIDV-UHFFFAOYSA-N 0.000 description 1

- SJCKRGFTWFGHGZ-UHFFFAOYSA-N magnesium silver Chemical compound [Mg].[Ag] SJCKRGFTWFGHGZ-UHFFFAOYSA-N 0.000 description 1

- WPBNNNQJVZRUHP-UHFFFAOYSA-L manganese(2+);methyl n-[[2-(methoxycarbonylcarbamothioylamino)phenyl]carbamothioyl]carbamate;n-[2-(sulfidocarbothioylamino)ethyl]carbamodithioate Chemical compound [Mn+2].[S-]C(=S)NCCNC([S-])=S.COC(=O)NC(=S)NC1=CC=CC=C1NC(=S)NC(=O)OC WPBNNNQJVZRUHP-UHFFFAOYSA-L 0.000 description 1

- 230000005499 meniscus Effects 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 239000003094 microcapsule Substances 0.000 description 1

- 239000011259 mixed solution Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 239000002159 nanocrystal Substances 0.000 description 1

- 210000000653 nervous system Anatomy 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 239000003960 organic solvent Substances 0.000 description 1

- 230000003204 osmotic effect Effects 0.000 description 1

- 239000000123 paper Substances 0.000 description 1

- 238000003909 pattern recognition Methods 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 230000010363 phase shift Effects 0.000 description 1

- 239000004033 plastic Substances 0.000 description 1

- 229920003023 plastic Polymers 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 229920000172 poly(styrenesulfonic acid) Polymers 0.000 description 1

- 229920001707 polybutylene terephthalate Polymers 0.000 description 1

- 239000004417 polycarbonate Substances 0.000 description 1

- 229920000515 polycarbonate Polymers 0.000 description 1

- 229920001601 polyetherimide Polymers 0.000 description 1

- 229920000139 polyethylene terephthalate Polymers 0.000 description 1

- 239000005020 polyethylene terephthalate Substances 0.000 description 1

- 229920005597 polymer membrane Polymers 0.000 description 1

- 229920000098 polyolefin Polymers 0.000 description 1

- 229920000123 polythiophene Polymers 0.000 description 1

- 229920000915 polyvinyl chloride Polymers 0.000 description 1

- 239000004800 polyvinyl chloride Substances 0.000 description 1

- 239000000843 powder Substances 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 238000007639 printing Methods 0.000 description 1

- XTUSEBKMEQERQV-UHFFFAOYSA-N propan-2-ol;hydrate Chemical compound O.CC(C)O XTUSEBKMEQERQV-UHFFFAOYSA-N 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000001105 regulatory effect Effects 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 238000007493 shaping process Methods 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

- 239000000725 suspension Substances 0.000 description 1

- 238000003786 synthesis reaction Methods 0.000 description 1

- 229910052718 tin Inorganic materials 0.000 description 1

- 239000011135 tin Substances 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 238000010023 transfer printing Methods 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- 238000001771 vacuum deposition Methods 0.000 description 1

- 235000012431 wafers Nutrition 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Chemical compound O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/005—Electrodes

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y30/00—Nanotechnology for materials or surface science, e.g. nanocomposites

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G2/00—Details of capacitors not covered by a single one of groups H01G4/00-H01G11/00

- H01G2/02—Mountings

- H01G2/06—Mountings specially adapted for mounting on a printed-circuit support

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/005—Electrodes

- H01G4/008—Selection of materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/018—Dielectrics

- H01G4/20—Dielectrics using combinations of dielectrics from more than one of groups H01G4/02 - H01G4/06

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/018—Dielectrics

- H01G4/20—Dielectrics using combinations of dielectrics from more than one of groups H01G4/02 - H01G4/06

- H01G4/206—Dielectrics using combinations of dielectrics from more than one of groups H01G4/02 - H01G4/06 inorganic and synthetic material

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/13—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals

- H03K5/14—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals by the use of delay lines

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/18—Printed circuits structurally associated with non-printed electric components

- H05K1/182—Printed circuits structurally associated with non-printed electric components associated with components mounted in the printed circuit board, e.g. insert mounted components [IMC]

-

- C—CHEMISTRY; METALLURGY

- C08—ORGANIC MACROMOLECULAR COMPOUNDS; THEIR PREPARATION OR CHEMICAL WORKING-UP; COMPOSITIONS BASED THEREON

- C08K—Use of inorganic or non-macromolecular organic substances as compounding ingredients

- C08K2201/00—Specific properties of additives

- C08K2201/001—Conductive additives

-

- C—CHEMISTRY; METALLURGY

- C08—ORGANIC MACROMOLECULAR COMPOUNDS; THEIR PREPARATION OR CHEMICAL WORKING-UP; COMPOSITIONS BASED THEREON

- C08K—Use of inorganic or non-macromolecular organic substances as compounding ingredients

- C08K2201/00—Specific properties of additives

- C08K2201/011—Nanostructured additives

-

- C—CHEMISTRY; METALLURGY

- C08—ORGANIC MACROMOLECULAR COMPOUNDS; THEIR PREPARATION OR CHEMICAL WORKING-UP; COMPOSITIONS BASED THEREON

- C08K—Use of inorganic or non-macromolecular organic substances as compounding ingredients

- C08K3/00—Use of inorganic substances as compounding ingredients

- C08K3/02—Elements

- C08K3/04—Carbon

- C08K3/042—Graphene or derivatives, e.g. graphene oxides

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Inorganic Chemistry (AREA)

- Materials Engineering (AREA)

- Fixed Capacitors And Capacitor Manufacturing Machines (AREA)

- Piezo-Electric Or Mechanical Vibrators, Or Delay Or Filter Circuits (AREA)

- Semiconductor Integrated Circuits (AREA)

- Nanotechnology (AREA)

- Parts Printed On Printed Circuit Boards (AREA)

- Composite Materials (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Crystallography & Structural Chemistry (AREA)

Abstract

제1 측과 상기 제1 측 반대편의 제2 측을 포함하며 두께 t를 가진 유전성 나노복합체층, 유전성 나노복합체 층의 제1 측에 연결된 제1 전극층, 유전성 나노복합체 층의 제2 측에 연결된 제2 전극층, 적어도 유전성 나노복합체층 내 충전 물질의 물질 중량 백분율에 종속적인 복소 임피던스 위상 각을 포함하는 프랙셔널 오더 커패시터가 개시된다.

Description

본 출원은 2013년 3월 14일 출원된 미국 가출원 제61/783,373호의 우선권을 주장한다. 인용된 출원(들)의 내용은 본 출원에 참조로서 포함된다.

본 명세서는 일반적으로 복소 임피던스 위상각(complex impedance phase angle)을 포함하는 커패시터 특성에 대한 개선된 제어를 갖는 프랙셔널 오더 커패시터(fractional order capacitor)에 관한 것이다. 커패시터는 충전 물질을 갖는 유전성 나노복합체 층을 포함하여 커패시터 특성에 대한 개선된 제어를 허용한다.

역사적으로, 프랙셔널 오더 미적분학은 그의 복잡성과 완전히 허용 가능한 기하학적 또는 물리적 실현성을 갖고 있지 않다는 사실 때문에 공학적으로 미개척되었다. 예를 들면, 전기 부품들은 일반적으로 각각 이상적인 -1, 0, 및 1 의 α값을 갖는 인덕터, 저항 및 커패시터의 특정한 특성들로 제한된다. 이러한 맥락에서, α는 - απ /2 식을 통해 장치의 전류 및 그 전압 사이의 위상 시프트를 결정하는 데 사용될 수 있다. 각도, 즉 90, 0 및 -90으로 변환될 때, 이들 값은 복소 임피던스 위상각을 나타낸다.

그러나, 실제 응용에서 구현될 때 전기 부품들은 정확한 정수 값 α를 갖지 않으므로, 표준 부품들읜 특성들 사이로 α 값을 의도적으로 제어할 수 있는 능력을 갖는 것은 자동 제어, 패턴 인식, 시스템 특성화, 신호 처리를 수행하는 것 및 전기화학(electrochemistry), 점탄성(viscoelasticity), 및 심지어 생물학 및 신경 시스템의 분야와 관련하여 필터 및 오실레이터를 적용하는 것을 포함하는 다양한 응용에 유용할 수 있다.

0 < α < 1 범위 내에서 특정한 α 값을 갖는 전기 부품들을 의도적으로 설계하고자 하는 이전의 시도들은 많은 경우에서 실제 응용 또는 회로에서 사용 가능하거나 실용적이지 않은 매우 부피가 큰 설계를 일반적으로 초래하였다. 예를 들면, 액체-전극-기반(liquid-electrode-based, LEB)형 프랙셔널 커패시터에 대하여, 구리 전극을 PMMA-클로로포름 용액 내에 담그고, 위상각은 전극이 담긴 깊이에 따라 변한다. 그러나 이 방법은 분명히 쉽게 인쇄회로보드 및/또는 전자회로와 집적할 수 없다. 또한, 이러한 셋업의 패키징은 매우 부피가 큰 장치를 초래한다.

다른 시도들로는 프랙탈형(fractal-type, FT) 프랙셔널 커패시터의 설계를 포함한다. 이들 설계는 일반적으로 웨이퍼 상에 제작되며 전송선 이론(transmission line theory)에 의존한다. 이러한 유형의 커패시터 이면의 기본적인 작동 원리는 스터브, 또는 전송선과 같은 프랙탈 기하(fractal geometries)를 생성하는 것을 수반하는데, 이는 다시 기하 및 기술적 파라미터에 기반한 특정 임피던스를 야기할 수 있다. 커패시터를 생성하는 대신, FT는 임피던스를 발생시키기 위하여 회로 상에 제작되는 일련의 금속 트레이스를 사용한다. 이는 집중 요소 설계(lumped element design)에 반하여 분산 요소 설계(distributed element design)로 종종 지칭된다. 또한, FT 프랙셔널 커패시터를 사용할 때, 얻어질 수 있는 α 값은 단지 0.46-0.5의 범위이다. 또한, 마이크로파 회로의 성질을 감안하면 매우 높은 주파수 범위(1MHz - 10GHz)에서 일정 위상 거동(constant phase behavior)이 일어나며, 위상각의 변화량은 약 5°이다.

다른 접근법은 프랙셔널 오더 문제를 디지털식으로 근사하고 근사적인 방법을 계산하여 시뮬레이션하는 것을 포함한다. 디지털 근사는 대역폭에서 필수적으로 제한되며, 컴퓨터 자원을 많이 소비하고, 유한 정밀도의 산술로 인한 불안정성을 겪을 수 있다. 이러한 한계는 디지털 기술이 빠른 공정이나 강한 대향력(opposing force)이 개입되는 "뻣뻣한(stiff)" 공정을 제어하는 것과 같은 많은 문제들을 해결하지 못하거나 비실용적인 것으로 만들 수 있다.

본 발명자들은, 또한 충전 물질로도 기술되는, 2차원 나노 재료의 무게 백분율이 커패시터의 복소 임피던스 각을 제어하는 데 사용될 수 있음을 발견하였다. 구체적으로, 커패시터의 유전층은 폴리머 매트릭스 내의 그 조합에 기반한 그래핀과 같은 충전 물질의 특정 중량%를 선택함으로써 형성될 수 있다. 중량 백분율은 α에 대해서 0 < α < 1 범위 내의 임의의 비-정수 값을 선택하기 위하여 사용될 수 있으며, 이는 상술한 바와 같은 커패시터의 복소 임피던스 위상각을 직접적으로 변경한다.

2차원 나노 물질로서 그래핀을 사용하는 것의 고유한 양상 중 하나는 유전층 내에서 마이크로-커패시터의 형성을 수반한다. 구체적으로, 프랙셔널 커패시턴스는 분산된 마이크로-커패시터의 형성을 초래하는 폴리머 매트릭스 내의 그래핀 시트의 로딩(loading)에 의해 제어된다. 이는 시뮬레이션에서 사용되는 RC 래더 네트워크와 매우 유사하며 복잡하고 큰 회로 설계의 필요 없이 α값을 조율하는 것이 가능하다. 그래핀은 또한 초고속에서 전자의 자유로운 흐름을 촉진하는 고유한 특성을 갖는다.

또한, 본 발명의 프랙셔널 오더 커패시터의 제조는 효과적인 제조 및 상업화를 허용한다.

본 명세서의 일 양상에 따르면, 프랙셔널 오더 커패시터 두께 t의 유전성 나노복합체 층을 포함하며 제1 측 및 제1 측 반대편의 제2 측을 포함한다. 프랙셔널 오더 커패시터는 유전성 나노복합체층의 제1 측에 연결된 제1 전극층과 유전성 나노복합체 층의 제2 측에 연결된 제2 전극층을 더 포함한다. 프랙셔널 오더 커패시터는 또한 적어도 유전성 나노복합체층 내 충전 물질의 물질 중량 백분율에 종속적인 복소 임피던스 위상 각을 포함한다.

본 명세서의 다른 양상에 따르면, 프랙셔널 오더 커패시터의 유전성 나노복합체 층은 매트릭스 재료와 전도성 충전 물질을 포함하며, 매트릭스 물질은 폴리머이고 전도성 충전 물질은 그래핀이다. 그래핀은 부분 산화되거나 완전 산화되지 않을 수 있다. 또한, 그래핀의 물질 중량 백분율은 유전성 나노복합체 층의 총 중량을 기준으로, 약 0.1% 내지 15% 사이이다.

본 명세서의 또 다른 양상에 따르면, 프랙셔널 오더 커패시터의 제1 및 제2 전극 층은 전도성 물질을 포함한다. 제1 전극 층은 백금을 포함하고, 제2 전극 층은 알루미늄을 포함한다. 제1 및 제2 전극 층은 대안적으로 PEDOT:PSS를 포함할 수 있다.

본 명세서의 추가의 양상에 따르면, 프랙셔널 오더 커패시터는 0°내지 - 90°사이의 복소 임피던스 위상각을 포함하거나, 주파수에 대해 대략 일정한 손실 탄젠트(loss tangent)를 포함하거나, 10kHz 내지 2MHz 사이의 주파수에 대하여 프랙셔널 거동(fractional behavior)을 나타낸다.

본 명세서의 다른 양상에 따르면, 프랙셔널 오더 커패시터는 인쇄회로보드 또는 집적 회로 내에 포함될 수 있으며 통신 회로, 감지 회로, 또는 제어 회로의 적어도 일부 내에서 사용될 수 있다. 프랙셔널 오더 커패시터는 또한 전자 기기 내에 포함될 수 있다.

본 명세서의 또 다른 양상에 따르면, 프랙셔널 오더 커패시터의 제조방법은 제1 전극 층을 획득하는 단계를 포함한다. 이 방법은 또한, 특정의 복소 임피던스 위상각을 얻기 위한 유전성 나노복합체층 내 충전 물질의 물질 중량%를 선택하는 단계를 포함한다. 이 방법은 제1 전극층 상에 유전성 나노복합체 층을 배치하는 단계를 추가로 포함한다. 이 방법은 또한 유전성 나노복합체층이 제1 전극층과 제2 전극층 사이에 배치되도록 유전성 나노복합체층 상에 제2 전극층을 배치하는 단계를 포함한다.

본 명세서의 추가의 양상에 따르면, 프랙셔널 오더 커패시터의 유전성 나노복합체 층은 매트릭스 재료와 전도성 충전 물질로 제조될 수 있으며, 매트릭스 물질은 폴리머이고 전도성 충전 물질은 그래핀이다. 그래핀은 부분 산화되거나 완전 산화되지 않을 수 있다. 또한, 그래핀의 물질 중량 백분율은 유전성 나노복합체 층의 총 중량을 기준으로, 약 0.1% 내지 15% 사이이다. 또한, 프랙셔널 오더 커패시터는 0°내지 - 90°의 복소 임피던스 위상각을 포함하거나, 주파수에 대해 대략 일정한 손실 탄젠트를 포함하거나, 10kHz 내지 2MHz 사이의 주파수에 대하여 프랙셔널 거동을 나타낸다.

본 명세서의 다른 양상에 따르면, 프랙셔널 오더 커패시터는 전도성 물질을 포함하는 제1 및 제2 전극층으로 제조될 수 있다. 제1 전극층은 백금을 포함하고, 제2 전극층은 알루미늄을 포함한다. 제1 및 제2 전극층은 대안적으로 PEDOT:PSS를 포함할 수 있다.

본 명세서의 또 다른 양상에 따르면, 프랙셔널 오더 커패시터의 유전성 나노복합체층은 용액 캐스팅에 의해, 닥터 블레이드에 의해, 또는 테이프 캐스팅에 의해, 또는 실크-스크린 인쇄에 의해, 또는 핫 프레스에 의해 제1 전극층 상에 배치될 수 있다. 제2 전극 층은 섀도우 마스크를 이용하여 유전성 나노복합체 층 상에 열증발(thermally-evaporated)될 수 있다. 본 명세서의 다른 양상에 따르면, 프랙셔널 오더 커패시터는 인쇄회로보드 또는 집적 회로 내에 패키징될 수 있다.

본 명세서의 추가의 양상에 따르면, 본 발명의 프랙셔널 오더 커패시터 중 임의의 것으로 전기 신호 상에 선택 지연을 부과하는 지연회로 작동 방법은 특정의 복소 임피던스 위상각을 얻기 위하여 상기 프랙셔널 오더 커패시터의 유전성 나노복합체층 내 충전 물질의 물질 중량%를 선택하는 단계를 포함한다. 이 방법은 또한 입력 신호에 응답하는 충전율로 상기 프랙셔널 오더 커패시터를 제1 전압으로 충전하는 단계를 포함한다. 이 방법은 입력 신호에 응답하는 충전율로 상기 프랙셔널 오더 커패시터를 제2 전압으로 방전하는 단계를 추가로 포함한다. 이 방법은 또한 상기 프랙셔널 오더 커패시터의 복소 임피던스 위상각의 함수로 지연 신호를 생성하는 단계를 포함한다.

본 명세서의 추가의 양상에 따르면, 저항과 본 발명의 프랙셔널 오더 커패시터 중 어느 하나를 포함하는 필터의 주파수 응답을 조절하는 방법은, 특정의 복소 임피던스 위상각을 얻기 위하여 프랙셔널 오더 커패시터의 유전성 나노복합체층 내 충전 물질의 물질 중량 백분율을 선택하는 단계를 포함한다. 이 방법은 또한 프랙셔널 커패시터 및 저항의 직렬 결합에 걸쳐 입력 전압을 공급하는 단계를 포함한다. 이 방법은 저항에 걸친 전압에 기초하여 출력 전압을 공급하는 단계를 추가로 포함한다. 이 방법은 또한 특정의 주파수에서 필터의 게인(gain)을 측정하는 단계를 포함한다. 이 방법은 복소 임피던스 위상각을 변화시킴으로써 특정 주파수에서 필터의 게인에 따라 프랙셔널 오더 커패시터의 커패시턴스를 조절하는 단계를 추가로 포함한다.

본 명세서의 다른 양상에 따르면, 본 발명의 프랙셔널 오더 커패시터 중 임의의 하나를 포함하는 RF 통신회로 작동 방법은, 특정의 복소 임피던스 위상각을 얻기 위하여 프랙셔널 오더 커패시터의 유전성 나노복합체층 내 충전 물질의 물질 중량%를 선택하는 단계를 포함한다. 이 방법은 또한 공진 주파수에서 RF 신호를 발생시키는 단계를 포함한다. 이 방법은 RF 통신 회로 내의 다른 구성요소의 직렬 저항 값을 검출하는 단계를 추가로 포함한다. 이 방법은 또한 복소 임피던스 위상각을 변화시킴으로써 RF 통신회로 내의 다른 구성요소의 등가 직렬 저항값의 적어도 일부를 오프셋(offset) 하기 위하여 프랙셔널 오더 커패시터의 음의 저항값을 설정하는 단계를 포함한다.

또한, 이하에서 본 발명의 구현예 1 내지 44가 개시된다. 구현예 1은 제1 측, 및 제1 측 반대편의 제2 측을 포함하는, 두께 t의 유전성 나노복합체 층; 유전성 나노복합체 층의 제1 측에 연결된 제1 전극 층; 유전성 나노복합체 층의 제2 측에 연결된 제2 전극층; 및 적어도 유전성 나노복합체 층 내 충전 물질의 물질 중량%에 종속적인 복소 임피던스 위상각을 포함하는 프랙셔널 오더 커패시터이다. 구현예 2는 유전성 나노복합체 층이 매트릭스 물질 및 전도성 충전 물질을 포함하는, 구현예 1의 프랙셔널 오더 커패시터이다. 구현예 3은 전도성 충전 물질이 그래핀인, 구현예 2의 프랙셔널 오더 커패시터이다. 구현예 4는 그래핀이 부분적으로 산화된, 구현예 3의 프랙셔널 오더 커패시터이다. 구현예 5는 그래핀이 완전히 비산화된, 구현예 3의 프랙셔널 오더 커패시터이다. 구현예 6은 그래핀의 물질 중량 백분율이 유전성 나노복합체 층의 총 중량을 기준으로, 약 0.1% 내지 15%를 포함하는, 구현예 3 내지 5 중 어느 하나의 프랙셔널 오더 커패시터이다. 구현예 7은 매트릭스 물질이 폴리머를 포함하는, 구현예 2 내지 6 중 어느 하나의 프랙셔널 오더 커패시터이다. 구현예 8은 제1 및 제2 전극 층이 전도성 물질을 포함하는, 구현예 1 내지 7 중 어느 하나의 프랙셔널 오더 커패시터이다. 구현예 9는 제1 전극층은 백금을 포함하고, 제2 전극층은 알루미늄을 포함하는, 구현예 8의 프랙셔널 오더 커패시터이다. 구현예 10은 제1 및 제2 전극층이 PEDOT:PSS를 포함하는, 구현예 8의 프랙셔널 오더 커패시터이다. 구현예 11은 0°내지 -90°사이의 복소 임피던스 위상각을 포함하는, 구현예 1 내지 10 중 어느 하나의 프랙셔널 오더 커패시터이다. 구현예 12는 주파수에 대해 대략 일정한 손실 탄젠트를 포함하는, 구현예 1 내지 11 중 어느 하나의 프랙셔널 오더 커패시터이다. 구현예 13은 프랙셔널 오더 커패시터가 10kHz내지 2MHz 사이의 주파수에 대하여 프랙셔널 거동을 나타내는, 구현예 1 내지 13 중 어느 하나의 프랙셔널 오더 커패시터이다. 구현예 14는 구현예 1 내지 13 중 어느 하나의 프랙셔널 오더 커패시터를 포함하는 인쇄회로보드이다. 구현예 15는 구현예 1 내지 13 중 어느 하나의 프랙셔널 오더 커패시터를 포함하는 집적 회로이다. 구현예 16은 프랙셔널 오더 커패시터가 통신 회로의 적어도 일부를 포함하는, 구현예 14의 인쇄회로보드이다. 구현예 17은 프랙셔널 오더 커패시터가 감지 회로의 적어도 일부를 포함하는, 구현예 14의 인쇄회로 기판이다. 구현예 18은 프랙셔널 오더 커패시터가 제어회로의 적어도 일부를 포함하는, 구현예 14의 인쇄회로보드이다. 구현예 19는 프랙셔널 오더 커패시터가 통신회로의 적어도 일부를 포함하는, 구현예 15의 집적 회로이다. 구현예 20은 프랙셔널 오더 커패시터가 감지회로의 적어도 일부를 포함하는, 구현예 15의 집적 회로이다. 구현예 21은 프랙셔널 오더 커패시터가 제어회로의 적어도 일부를 포함하는, 구현예 15의 집적 회로이다. 구현예 22는 구현예 1 내지 13 중 어느 하나의 프랙셔널 오더 커패시터를 포함하는 전자장치이다. 구현예 23은 제1 전극층을 획득하는 단계; 특정 복소 임피던스 위상각을 얻기 위한 유전성 나노복합체층 내 충전 물질의 물질 중량 백분율을 선택하는 단계; 제1 전극층 상에 유전성 나노복합체층을 배치하는 단계; 및 유전성 나노복합체층이 제1 전극층과 제2 전극층 사이에 배치되도록 유전성 나노복합체층 상에 제2 전극 층을 배치하는 단계를 포함하는, 프랙셔널 오더 커패시터의 제조방법이다. 구현예 24는 유전성 나노복합체 층이 적어도 매트릭스 물질 및 전도성 충전 물질을 포함하는, 구현예 23의 방법이다. 구현예 25는 전도성 충전 물질이 그래핀인, 구현예 24의 방법이다. 구현예 26은 그래핀이 부분적으로 산화된, 구현예 25의 방법이다. 구현예 27은 그래핀이 완전히 비산화된, 구현예 25의 방법이다. 구현예 28은 그래핀의 물질 중량%가 유전성 나노복합체 층의 총 중량을 기준으로, 약 0.1% 내지 15% 사이에서 선택되는, 구현예 25 내지 27 중 어느 하나의 방법이다. 구현예 29는 매트릭스 물질이 폴리머를 포함하는, 구현예 24 내지 28 중 어느 하나의 방법이다. 구현예 30은 제1 및 제2 전극층이 전도성 물질을 포함하는, 구현예 23 내지 29 중 어느 하나의 방법이다. 구현예 31은 제1 전극층은 백금을 포함하고, 제2 전극층은 알루미늄을 포함하는, 구현예 30의 방법이다. 구현예 32는 제1 및 제2 전극층이 PEDOT:PSS를 포함하는, 구현예 30의 방법이다. 구현예 33은 유전성 나노복합체 층이 용액 캐스팅에 의해 제1 전극층 상에 배치되는, 구현예 23 내지 32 중 어느 하나의 방법이다. 구현예 33은 유전성 나노복합체층이 용액 캐스팅에 의해 제1 전극 층 상에 배치되는, 구현예 23 내지 32 중 어느 하나의 방법이다. 구현예 34는 유전성 나노복합체층이 닥터 블레이드에 의해 제1 전극층 상에 배치되는, 구현예 23 내지 33 중 어느 하나의 방법이다. 구현예 35는 유전성 나노복합체층이 테이프 캐스팅에 의해 제1 전극층 상에 배치되는, 구현예 23 내지 34 중 어느 하나의 방법이다. 구현예 36은 유전성 나노복합체 층이 실크스크린 인쇄에 의해 제1 전극층 상에 배치되는, 구현예 23 내지 35 중 어느 하나의 방법이다. 구현예 37은 유전성 나노복합체 층이 핫 프레스에 의해 제1 전극층 상에 배치되는, 구현예 23 내지 36 중 어느 하나의 방법이다. 구현예 38은 제2 전극층이 섀도우 마스크를 이용하여 유전성 나노복합체 층 상에 열증발되는(thermally-evaporated), 구현예 23 내지 37 중 어느 하나의 방법이다. 구현예 39는 복소 임피던스 위상각이 0°내지 - 90°사이인, 구현예 23 내지 38 중 어느 하나의 방법이다. 구현예 40은 프랙셔널 오더 커패시터를 집적 회로 내에 패키징하는 단계를 추가로 포함하는, 구현예 23 내지 39 중 어느 하나의 방법이다. 구현예 41은 프랙셔널 오더 커패시터를 인쇄 회로 기판 내에 패키징하는 단계를 추가로 포함하는, 구현예 23 내지 40 중 어느 하나의 방법이다. 구현예 42는 구현예 1 내지 13으로부터의 프랙셔널 오더 커패시터 중 어느 하나로 전기 신호 상에 선택 지연을 부과하는 지연 회로 작동 방법으로서, 이 방법은 특정 복소 임피던스 위상각을 얻기 위하여 프랙셔널 오더 커패시터의 유전성 나노복합체 층 내 충전 물질의 물질 중량%를 선택하는 단계; 입력 신호에 응답하는 충전율로 상기 프랙셔널 오더 커패시터를 제1 전압으로 충전하는 단계; 입력 신호에 응답하는 충전율로 상기 프랙셔널 오더 커패시터를 제2 전압으로 방전하는 단계; 상기 프랙셔널 오더 커패시터의 복소 임피던스 위상각의 함수로, 지연된 신호를 생성하는 단계를 포함한다. 구현예 43은 저항과 구현예 1 내지 13 중 어느 하나로부터의 프랙셔널 오더 커패시터 중 어느 하나를 포함하는 필터의 주파수 응답을 조절하는 방법으로서, 이 방법은 특정 복소 임피던스 위상각을 얻기 위하여 프랙셔널 오더 커패시터의 유전성 나노복합체 층 내 충전 물질의 물질 중량%를 선택하는 단계; 프랙셔널 커패시터 및 저항의 직렬 결합에 걸쳐 입력 전압을 공급하는 단계; 저항에 걸친 전압에 기초하여 출력 전압을 공급하는 단계; 특정 주파수에서 필터의 게인을 측정하는 단계; 복소 임피던스 위상각을 변화시킴으로써 특정 주파수에서 필터의 게인에 따라 프랙셔널 오더 커패시터의 커패시턴스를 조절하는 단계를 포함한다. 구현예 44는 구현예 1 내지 13 중 어느 하나로부터의 프랙셔널 오더 커패시터 중 어느 하나를 포함하는 RF 통신 회로 작동 방법으로서, 이 방법은 특정의 복소 임피던스 위상각을 얻기 위하여 프랙셔널 오더 커패시터의 유전성 나노복합체층 내 충전 물질의 물질 중량%를 선택하는 단계; 공진 주파수에서 RF 신호를 발생시키는 단계; RF 통신회로 내의 다른 구성요소의 직렬 저항값을 검출하는 단계; 복소 임피던스 위상각을 변화시킴으로써 RF 통신회로 내의 다른 구성요소의 등가 직렬 저항값의 적어도 일부를 오프셋하기 위하여 프랙셔널 오더 커패시터의 음의 저항값을 설정하는 단계를 포함한다.

"약" 또는 "대략"의 용어는 이 분야의 통상의 기술자에게 이해되는 것과 근사한 것으로 정의되며, 하나의 비제한적인 구현예에서 이 용어들은 10% 이내, 바람직하게는 5% 이내, 더 바람직하게는 1% 이내, 그리고 가장 바람직하게는 0.5% 이내인 것으로 정의된다.

단어 "하나"(a 또는 an)의 사용은 청구범위 또는 명세서에서 "포함하는(comprising)"의 용어와 함께 사용되는 경우 "하나"(one)를 의미할 수 있지만, 이는 또한 "하나 또는 그 이상", "적어도 하나", 및 "하나 또는 하나보다 많은"의 의미와도 일치한다.

"포함하는"(comprising)"(및 "~들을 포함하다"(comprise) 및 "~을 포함하다"(comprises)와 같은 이의 임의의 형태), "갖는" (having) (및 "~들을 갖다" (have) 및 "~을 갖다"(has)와 같은 이의 임의의 형태), "포함하는"(including) (및 "~을 포함하다"(includes) 및 "~들을 포함하다"(include)와 같은 이의 임의의 형태), "함유하는"(containing)(및 "~을 함유하다"(contains) 및 "~들을 함유하다"(contain)와 같은 이의 임의의 형태)의 단어들은 포괄적이거나 또는 개방적인 것이며 추가의 열거되지 않은 요소 또는 방법 단계를 배제하지 않는다.

"연결된"(coupled)의 용어는 반드시 직접적으로는 아니며 또한 반드시 기계적으로도 아니더라도, 연결된(connected) 것으로 정의된다.

본 발명의 유전성 재료, 전극층, 프랙셔널 오더 커패시터, 및 전자장치는 명세서에 걸쳐 개시된 특정성분, 구성요소, 조성물 등을 "포함하거나"(comprise), "~로 본질적으로 구성되거나"(consist essentially of) 또는 "~로 구성될"(consist of) 수 있다. 하나의 비제한적인 양상에서, 전이 단계 "~로 본질적으로 구성된(consist essentially of)"에 대하여, 본 발명의 커패시터의 기본적이고 신규한 특성은 커패시터의 복소 임피던스 각을 제어하는 능력이다.

본 발명의 다른 목적, 특징 및 이점들은 이하의 도면, 상세한 설명 및 실시예들로부터 명백해질 것이다. 그러나, 도면, 상세한 설명, 실시예는 본 발명의 특정한 구현예를 지시하더라도 예시의 목적으로만 제시된 것이며 제한하고자 하는 의도가 아님이 이해되어야 한다. 또한, 이 상세한 설명으로부터 이 분야의 기술자들에게 본 발명의 정신 및 범위 내에서 변화와 변경이 명백하게 될 것임이 고려된다.

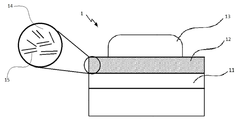

도 1은 본 발명의 프랙셔널 오더 커패시터이다.

도 2는 프랙셔널 오더 커패시터의 유전성 나노복합체 내의 충전 물질을 보여주는 단면도이다.

도 3은 본 발명의 프랙셔널 오더 커패시터가 유리하게 사용될 수 있는 예시적인 무선 통신 시스템을 나타내는 블록도이다.

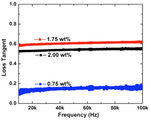

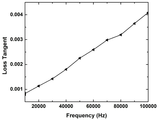

도 4는 측정된 주파수 범위에 걸쳐 일정한 값을 갖는 제조된 나노복합체 커패시터의 손실 탄젠트를 보여주는 그래핀을 갖는 P(VDF-TrFE-CFE) 이다.

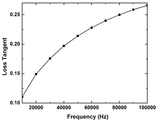

도 5는 10-100 kHz 사이의 증가하는 주파수에서 손실 탄젠트의 큰 증가를 보여주는 그래핀이 없는 P(VDF-TrFE-CFE) 이다.

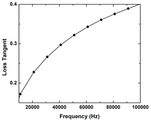

도 6은 10-100 kHz 사이의 증가하는 주파수에서 손실 탄젠트의 큰 증가를 보여주는 P(VDF-TrFE-CFE)/폴리아닐린 나노복합체이다.

도 7은 10-100 kHz 사이의 증가하는 주파수에서 손실 탄젠트의 큰 증가를 보여주는 폴리스티렌이다.

도 2는 프랙셔널 오더 커패시터의 유전성 나노복합체 내의 충전 물질을 보여주는 단면도이다.

도 3은 본 발명의 프랙셔널 오더 커패시터가 유리하게 사용될 수 있는 예시적인 무선 통신 시스템을 나타내는 블록도이다.

도 4는 측정된 주파수 범위에 걸쳐 일정한 값을 갖는 제조된 나노복합체 커패시터의 손실 탄젠트를 보여주는 그래핀을 갖는 P(VDF-TrFE-CFE) 이다.

도 5는 10-100 kHz 사이의 증가하는 주파수에서 손실 탄젠트의 큰 증가를 보여주는 그래핀이 없는 P(VDF-TrFE-CFE) 이다.

도 6은 10-100 kHz 사이의 증가하는 주파수에서 손실 탄젠트의 큰 증가를 보여주는 P(VDF-TrFE-CFE)/폴리아닐린 나노복합체이다.

도 7은 10-100 kHz 사이의 증가하는 주파수에서 손실 탄젠트의 큰 증가를 보여주는 폴리스티렌이다.

프랙셔널 오더 커패시터의 실현을 가능하게 하는, 커패시터를 위한 개선된 유전성 물질이 발견되었다. 특히, 그래핀과 같은 2차원 나노복합체 충전 물질을 폴리머 매트릭스 내로 결합하고, 충전 물질의 중량%를 변화시킴으로써, 커패시터의 복소 임피던스 위상각이 변할 수 있어, 프랙셔널 오더 커패시터의 실현을 가능하게 한다.

본 발명의 이들 및 다른 비제한적인 양상들이 다음 섹션에서 자세히 논의된다.

A.

프랙셔널

오더 커패시터

도 1은 유전성 나노복합체 층을 포함하는 본 발명의 프랙셔널 오더 커패시터의 단면도이다. 프랙셔널 오더 커패시터(1)는 기판(10), 하부 전극(11), 유전성 나노복합체층(12), 및 단부 전극(13)을 포함할 수 있다. 프랙셔널 오더 커패시터는 두 개의 전도성 전극(11 및 13) 사이에, 폴리머 매트릭스와, 또한 충전 물질로도 기술되는 2차원 나노 물질을 포함하는 유전성 나노복합체 층을 샌드위치함에 의하여 기판 상에 제조될 수 있다.

실질적으로 정수-차수 임피던스를 갖는 표준 커패시터와 대조적으로, 본 발명의 프랙셔널 오더 커패시터는 -90도의 값에 제한되지 않는 위상각 시프트를 얻을 수 있다. 예를 들면, 프랙셔널 오더 커패시터는 저항과 커패시터의 위상각 사이에 위상각 시프트(예로서 -0.5)를 가질 수 있다. 그 결과, 이는 전기 설계자가 특정한 필요에 대한 위상 및 에너지 저장/발산 관계를 선택하는 데 더 많은 옵션을 제공하며 이에 따라 통상적으로 사용 가능하지 않은 전기 회로 및 방법의 구현을 허용한다.

1.

기판(10)

기판(10)은 지지체로 사용된다. 본 발명의 프랙셔널 오더 커패시터는 여러 다른 기판을 사용하여 제조될 수 있다. 이 분야의 통상적인 기술자에게 알려진 많은 추가적인 기판 물질이 본 발명의 프랙셔널 오더 커패시터(1)와 함께 사용될 수 있다. 이러한 재료의 비제한적인 예는 실리콘, 플라스틱, 종이 등과 같은 무기 물질을 포함한다. 다른 예는 SABIC 폴리머, 및 폴리에테르이미드(예를 들어 ULTEM, EXTEM, SILTEM), 폴리(에틸렌테레프탈레이트), 폴리(부틸렌 테레프탈레이트), 폴리카보네이트(예를 들어 LEXAN), 폴리(페닐렌 옥사이드), 폴리올레핀, 폴리스티렌 및 폴리(비닐 클로라이드)를 포함하는 그의 코폴리머 및 혼합물을 기반으로 하는 기판이다. 프랙셔널 오더 커패시터는 실리콘 기판 및 금속 전극 상의 장치에서 또한 동일하게 수행하는 것으로 나타났다. 기판은 일반적으로 열 또는 유기 용제에 의해 쉽게 변경 또는 열화되지 않는 물질로 만들어진다.

2.

하부 전극 및 상부 전극(11, 13)

하부 전극(11)은 전도성 물질로 만들어진다. 일반적으로, 하부 전극(11)은 그러한 물질을 사용하여 막을 형성함으로써 얻어진다(예를 들면, 진공 증착, 스퍼터링, 이온-플레이팅, 플레이팅, 코팅 등). 대안적으로, 기판은 바닥 전극의 역할을 하는 높은 도전성의 폴리머(폴리(3,4-에틸렌다이옥시티오펜):폴리(스티렌 설폰산), ~4%의 디메틸설폭사이드(DMSO)로 도핑된 PEDOT:PSS Clevios PH-1000 (Heraeus))의 얇은 층으로 코팅될 수 있다. 전도성 막을 형성하기 위하여 사용될 수 있는 전도성 재료의 다른 비제한적인 예는 금, 백금, 은, 알루미늄 및 구리, 이리듐, 이리듐 산화물 등을 포함한다. 또한, 전도성 폴리머 재료의 비제한적인 예는 PEDOT: PSS, 폴리아닐린, 그래핀 등과 같은 전도성 폴리머를 포함한다. 하부 전극(11)을 위한 막의 두께는 일반적으로 20 nm 내지 500 nm이다.

상부 전극(13)은 패터닝 및 프로빙(probing)을 위한 섀도우 마스크(shadow mask)를 사용하여 열 증발(thermally evaporating)에 의하여 유전성 나노복합체 층(12) 상에 배치될 수 있다. 상부 전극은 또한 도핑된 PH1000의 잉크젯 인쇄를 통해 패터닝될 수 있다. 이러한 커패시터는 실리콘 기판 및 금속 전극 상의 장치에서 또한 동일하게 수행하는 것을 나타났다. 상부 전극(13)을 위해 사용되는 물질은 또한 전도성이며, 바람직하게는 알루미늄이다. 이러한 다른 재료의 비제한적인 예는 하부 전극(11)과 관련하여 위에서 논의된 것과 같은 금속, 금속 산화물 및 전도성 폴리머(예를 들면, 폴리아닐린, 폴리티오펜, 등)을 포함한다. 상부 전극(13)은 단일층 또는 각각 서로 다른 작업 기능을 갖는 물질로 이루어진 박판의 층들(laminated layers)일 수 있다. 또한, 이는 낮은 작업 기능을 갖는 하나 또는 그 이상의 재료와 금, 은, 백금, 구리, 망간, 티타늄, 코발트, 니켈, 텅스텐, 및 주석으로 이루어진 군으로부터 선택된 적어도 하나의 합금일 수 있다. 합금의 예는 리튬-알루미늄 합금, 리튬-마그네슘 합금, 리튬-인듐 합금, 마그네슘-은 합금, 마그네슘-인듐 합금, 마그네슘-알루미늄 합금, 인듐-은 합금, 및 칼슘-알루미늄 합금을 포함한다. 상부 전극(13) 막의 두께는 일반적으로 20 nm 내지 500 nm 사이이다.

3.

유전성 나노복합체 층(12)

도 2는 하부 전극(11)과 상부 전극(13) 사이에 개재된 유전성 나노복합체 층(12)의 단면이다. 유전성 나노복합체 층(12)은 충전 물질(15) 및 폴리머 물질(14)을 포함한다. 일 예에서, 유전성 나노복합체 층(12)은 충전 물질로 산화되지 않거나 일부 산화된 그래핀과 폴리머(14)를 사용한 혼합 용액일 수 있다. 폴리머(14)에 대한 그래핀의 농도는 0.1 중량% 내지 15 중량% 사이이다. 그래핀 합성의 비제한적인 예는 변경된 Hummer 방법에 따라 그라파이트로부터 그라파이트 산화물을 준비하는 것 (DOI: 10.1021/ja01539a017) 또는 그라파이트 산화물을 박리하여 그래핀 산화물 형성을 초래하는 하이드라진 모노하이드레이트 환원 (DOI:10.1016/j.carbon.2011.02.071)을 포함한다.

유전성 나노복합체 층은 폴리머와 현탁된(suspended) 충전 물질을 포함하는 용액을 얻는 것에 의하여 증착될 수 있다. 용액은 닥터 블레이드 코팅, 드롭-캐스팅, 스핀 코팅, 메니스커스 코팅, 전사 인쇄, 잉크젯 인쇄, 오프셋 인쇄, 스크린 인쇄 프로세스, 딥 코팅, 캐스팅, 바 코팅, 롤 코팅, 와이어 바 코팅, 스프레이, 스크린 인쇄, 그라비어 인쇄, 플렉소 인쇄, 오프셋 인쇄, 그라비어 오프셋 인쇄, 디스펜서 코팅, 노즐 코팅, 캐필러리 코팅(capillary coating) 등에 의해 증착될 수 있다.

B.

프랙셔널

오더 커패시터 제조를 위한 방법의

구현예

도 2를 참조하면, 프랙셔널 오더 커패시터(1)는 두 전도성 전극 사이에 충전 물질(15) 및 폴리머(14)의 유전성 나노복합체 층(12)을 배치함으로써 실리콘 기판 상에 제조된다. Pt 코팅된 실리콘 기판이 사용될 수 있으며 장치 제조 전에 아세톤, IPA 및 DI수로 세정된다. 원하는 로딩(loading)에 따라 0.1 내지 15 중량%의 그래핀 파우더가 계량되고 용액 내에 현탁되며, 1-10 시간 동안 초음파처리된다. 폴리머(14)가 용액에 첨가되고 연속적으로 교반된다. 그래핀/폴리머 용액이 1-300분으로부터 4번 초음파처리되어 결과적으로 캐스팅 준비가 완료된 폴리머 용액 내의 그래핀 현탁액(suspension)이 된다.

유전성 나노복합체 층(12) 용액은 드롭 캐스팅에 의해 증착될 수 있으며 이어서 1-24 시간 동안 건조되도록 둔다. 공기-건조된 막은 진공으로 이송되고 1-48 시간 동안 건조된다. 위 알루미늄 전극은 섀도우 마스크를 사용하여 막의 상부 표면 상에 열 증착되고 패터닝된다.

본 발명의 과정은 고성능 프랙셔널 오더 커패시터를 효과적으로 대량 생산할 수 있다.

C.

프랙셔널

오더 커패시터의 응용

커패시터는 집적 회로 내의 매우 중요한 요소 중의 하나이며 많은 전자 기기 내에서 광범위하게 사용된다. 본 발명의 프랙셔널 오더 커패시터는 일반적으로 이용 가능하지 않은 전기 회로 및 방법을 구현하는 데 사용될 수 있다. 이는 회로 내에서 요구되는 구성요소의 수를 줄이는 것, 회로의 공진 주파수를 높이는 것, 전자 필터의 주파수 응답 형성(shaping)에 더 큰 융통성을 허용하는 것, 및 음의 저항 및 주파수 의존 음의 저항의 실현을 가능하게 하는 것을 포함한다. 이들 후자의 이익은 매우 큰 가치를 가질 수 있으며 더 다재다능한 전자 회로로의 문호를 개방한다.

프랙셔널 오더 커패시터는 또한 에너지-저장 기능을 제공한다. 전압이 플레이트를 가로질러 인가될 때, 유전체 내의 전기장이 전하를 치환하며 이에 따라 에너지를 저장한다. 프랙셔널 오더 커패시터에 의해 저장되는 에너지의 양은 절연재료의 유전율 및 유전체의 치수(전체 면적 및 두께)에 의존한다. 본 발명의 프랙셔널 오더 커패시터의 유전율은 충전 물질의 양과 유형을 변경함에 의해 바뀔 수 있다. 커패시터가 축적할 수 있는 에너지의 전체 양을 최대화하기 위하여, 유전율은 최대화되고, 유전층의 두께는 최소화된다.

위에서 개시된 프랙셔널 오더 커패시터는 또한 집적 회로 내에 채용될 수 있다. 예를 들면, 프랙셔널 오더 커패시터는 마이크로프로세서와 같은 논리 장치의 NAND 또는 NOR 게이트의 일부일 수 있다. 특정한 회로가 설명되었지만 이 분야의 기술자라면 개시된 회로 모두가 본 명세서를 실현하는 데 필요한 것이 아님을 이해할 것이다. 또한, 특정한 공지의 회로는 본 명세서의 초점을 유지하기 위하여 설명되지 않았다.

도 3은 본 명세서의 구현예가 유리하게 채용될 수 있는 예시적인 무선통신 시스템(40)을 나타내는 블록도이다. 설명을 위하여, 도 3은 3개의 원격 유닛(42, 43, 45) 및 두 개의 베이스 스테이션(44)을 나타낸다. 무선통신 시스템이 더 많은 원격 유닛과 베이스 스테이션을 가질 수 있음을 알 수 있을 것이다. 원격 유닛(42, 43, 45)은 개시된 프랙셔널 오더 커패시터를 포함하는 집적회로 또는 인쇄회로 기판을 포함할 수 있는 회로장치(42A, 42C, 42B)를 포함한다. 베이스 스테이션, 스위칭 장치, 및 네트워크 장비를 포함하여, 집적회로 또는 인쇄회로 기판을 포함하는 임의의 장치가 또한 여기에서 개시된 프랙셔널 오더 커패시터를 포함할 수 있음을 알 수 있을 것이다. 도 3은 베이스 스테이션(44)으로부터 원격 유닛(42, 43, 45)으로의 순방향 링크 신호(48) 및 원격 유닛(42, 43, 45)으로부터 베이스 스테이션(44)으로의 역방향 링크 신호(49)를 보여준다.

도 3에서, 원격 유닛(42)은 이동전화로 도시되며, 원격 유닛(43)은 휴대용 컴퓨터로 도시되며, 원격 유닛(45)은 무선 로컬 루프 시스템 내의 고정위치 원격 유닛으로 도시되어 있다. 예를 들면, 원격 유닛은 이동전화, 휴대용 개인용 통신 시스템(hand-held personal communication systems, PCS) 유닛, 개인용 데이터 도우미(personal data assistants)와 같은 이동식 데이터 유닛, GPS 구동 장치, 내비게이션 장치, 셋업 박스, 음악 재생기, 비디오 재생기, 엔터테인먼트 유닛, 미터 판독 장치와 같은 고정 위치 데이터 유닛, 또는 데이터 또는 컴퓨터 명령을 저장하거나 검색하는 임의의 다른 장치, 또는 그 임의의 조합일 수 있다. 도 3이 본 명세서의 가르침에 따라 원격 유닛을 예시하고 있지만, 본 명세서는 이러한 예시적인 유닛에 제한되지 않는다. 본 명세서의 구현예는 프랙셔널 오더 커패시터(1)를 포함하는 임의의 장치에 적합하게 채용될 수 있다.

본 명세서와 그 이점들이 여기에서 자세히 설명되었지만, 첨부된 청구범위에 의해 정의되는 본 명세서의 기술로부터 벗어나지 않고 다양한 변화, 대체 및 변경이 이루어질 수 있음이 이해되어야 할 것이다. 또한, 본 출원의 범위는 명세서 내에 기재된 특정한 구현예의 공정, 기계, 제조, 조성물, 수단, 방법 및 단계에 제한하고자 하는 것이 아니다. 이 분야의 통상의 기술자라면 본 명세서에 따라 여기에서 기재된 대응하는 구현예와 실질적으로 동일한 기능을 수행하거나 실질적으로 동일한 결과를 획득하는 현재 존재하거나 이후에 개발될 공정, 기계, 제조, 조성물, 수단, 방법 및 단계가 사용될 수 있다는 점을 본 명세서로부터 쉽게 이해할 것이다. 따라서, 첨부된 청구범위는 그 범위 내에 이러한 공정, 기계, 제조, 조성물, 수단, 방법 및 단계를 포함하는 것으로 의도된다.

실시예

본 발명이 특정한 실시예에 의하여 더 자세히 설명된다. 이하의 실시예는 예시의 목적으로만 제공되는 것이며, 어떤 방법으로도 발명을 제한하고자 의도하지 않는다. 이 분야의 기술자는 변화 또는 변경될 수 있는 여러 중요하지 않은 파라미터가 본질적으로 동일한 결과를 가져올 수 있음을 쉽게 인식할 것이다.

실시예

1

측정된 주파수 범위에 걸쳐 일정한 값을 갖는 제조된 나노복합체 커패시터의 손실 탄젠트를 보여주는

그래핀을

갖는 P(

VDF

-

TrFE

-

CFE)

프랙셔널 커패시터가 주파수에 대하여 일정한 위상 거동을 나타내는 것을 보여주는 손실 탄젠트 테스트를 수행하였다. 동일하게, 프랙셔널 커패시터는 주파수에 대해 일정한 손실 탄젠트를 나타낼 것이다(즉, tan(손실 탄젠트) + 위상 = 90°). 실시예에서, 다른 로딩(loading)의 그래핀을 갖는 세 개의 샘플이 나타나 있으며, 큰 주파수 범위에 걸쳐 손실 탄젠트 및/또는 위상이 일정하다는 것이 명백하게 관찰된다. 도 4는 또한 0.75%의 로딩에 비하여 2% 및 1.75%의 로딩이 더 안정함을 보여준다(도 4 참조).

실시예

2

(10-

100 kHz

사이의 증가하는 주파수에서 손실 탄젠트 값의 큰 증가를 보여주는

그래핀이

없는 P(

VDF

-

TrFE

-CFE) )

본 발명의 프랙셔널 오더 커패시터의 고유한 결과를 확인하기 위하여, 3개의 다른 정전 커패시터로부터의 추가적인 손실 탄젠트 데이터를 획득하였다. 선택된 막은: (1) 그래핀이 없는 P(VDF-TrFE-CFE), (2) P(VDF-TrFE-CFE) + 폴리아닐린 (PANI), 및 (3) 폴리스티렌이다. 이들 테스트에서, 결과는 10-100 kHz 사이에서 P(VDF-TrFE-CFE) 폴리머 막에 대해 손실 탄젠트의 현저한 변화(~140% 편차)를 보여준다. 이는 일차적으로 그래핀 시트의 부재와 따라서 마이크로커패시터 형성이 이루어지지 않는 것에 기인한다. 손실 탄젠트의 안정성은 폴리머 매트릭스 내에 전도성 그래핀을 추가한 것의 효과임이 명백하다(도 5 참조).

실시예

3

(10-

100 kHz

사이의 증가하는 주파수에서 손실 탄젠트 값의 큰 증가를 보여주는 P(VDF-TrFE-CFE)/폴리아닐린 나노복합체)

다른 복합체 시스템을 사용하여 추가적인 테스트를 수행하였으며, P(VDF-TrFE-CFE)는 전도성 PANI 입자로 충전하였다. 도 6에서, 이들 막의 성능은 동일한 선택된 주파수 범위 내에서 손실 탄젠트의 큰 변화(>130%)를 명백히 나타낸다. 이것이 그래핀 시트에 비하여 삼투성인 복합체이지만, PANI 입자는 훨씬 낮은 종횡비를 가지며 RC 네트워크 시뮬레이션에 필요한 마이크로 커패시터 구조를 닮을 수 없다.

실시예

4

(10-

100 kHz

사이의 증가하는 주파수에서 손실 탄젠트 값의 큰 증가를 보여주는

폴리스티렌)

도 7에서 폴리스티렌의 통상적인 커패시터 막을 또한 테스트 하였다. 위의 커패시터 테스트와 비교할 때, 손실 탄젠트 값은 약 3차 규모 낮지만, 폴리스티렌은 손실에서 가장 큰 편차를 보인다(>400%).

Claims (44)

- 제1 측과 상기 제1 측 반대편의 제2 측을 포함하며 두께 t를 가진 유전성 나노복합체층;

상기 유전성 나노복합체 층의 상기 제1 측에 커플링되는 제1 전극층;

상기 유전성 나노복합체 층의 상기 제2 측에 커플링되는 제2 전극층; 및

적어도 유전성 나노복합체 층 내 충전 물질의 물질 중량 백분율에 종속적인 복소 임피던스 위상 각(complex impedance phase angle)을 포함하는,

프랙셔널 오더 커패시터(fractional order capacitor). - 제1항에 있어서,

상기 유전성 나노복합체 층은 매트릭스 물질 및 전도성 충전 물질을 포함하는,

프랙셔널 오더 커패시터. - 제2항에 있어서,

상기 전도성 충전 물질은 그래핀(graphene)인,

프랙셔널 오더 커패시터. - 제3항에 있어서,

상기 그래핀은 부분적으로 산화된(oxidized),

프랙셔널 오더 커패시터. - 제3항에 있어서,

상기 그래핀은 완전히 비산화된(un-oxidized),

프랙셔널 오더 커패시터. - 제3항에 있어서,

상기 그래핀의 상기 물질 중량 백분율은 상기 유전성 나노복합체 층의 총 중량을 기준으로 약 0.1% 내지 15%를 포함하는,

프랙셔널 오더 커패시터. - 제2항에 있어서,

상기 매트릭스 물질은 폴리머(polymer)를 포함하는,

프랙셔널 오더 커패시터. - 제1항에 있어서,

상기 제1 및 제2 전극 층은 전도성 물질을 포함하는,

프랙셔널 오더 커패시터. - 제8항에 있어서,

상기 제1 전극 층은 백금을 포함하며, 상기 제2 전극 층은 알루미늄을 포함하는,

프랙셔널 오더 커패시터. - 제8항에 있어서,

상기 제1 및 제2 전극 층은 PEDOT:PSS를 포함하는,

프랙셔널 오더 커패시터. - 제1항에 있어서,

0°내지 - 90°사이의 복소 임피던스 위상각을 포함하는,

프랙셔널 오더 커패시터. - 제1항에 있어서,

주파수에 대해 대략 일정한 손실 탄젠트(loss tangent)를 포함하는,

프랙셔널 오더 커패시터. - 제1항에 있어서,

상기 프랙셔널 오더 커패시터는 10kHz 내지 2MHz의 주파수에 대하여 프랙셔널 거동(fractional behavior)을 나타내는,

프랙셔널 오더 커패시터. - 청구항 1의 프랙셔널 오더 커패시터를 포함하는 인쇄회로보드.

- 청구항 1의 프랙셔널 오더 커패시터를 포함하는 집적 회로.

- 제14항에 있어서,

상기 프랙셔널 오더 커패시터는 통신 회로의 적어도 일부를 포함하는,

인쇄회로보드 - 제14항에 있어서,

상기 프랙셔널 오더 커패시터는 감지 회로의 적어도 일부를 포함하는,

인쇄회로보드 - 제14항에 있어서,

상기 프랙셔널 오더 커패시터는 제어 회로의 적어도 일부를 포함하는,

인쇄회로보드 - 제15항에 있어서,

상기 프랙셔널 오더 커패시터는 통신 회로의 적어도 일부를 구성하는,

집적 회로. - 제15항에 있어서,

상기 프랙셔널 오더 커패시터는 감지 회로의 적어도 일부를 포함하는,

집적 회로. - 제15항에 있어서,

상기 프랙셔널 오더 커패시터는 제어 회로의 적어도 일부를 포함하는,

집적 회로. - 제1항의 프랙셔널 오더 커패시터를 포함하는 전자 기기.

- 제1 전극 층을 획득하는 단계;

특정의 복소 임피던스 위상각을 얻기 위한, 유전성 나노복합체층 내 충전 물질의 물질 중량 백분율을 선택하는 단계;

상기 제1 전극 층 상에 상기 유전성 나노복합체층을 배치하는 단계; 및

상기 유전성 나노복합체 층이 상기 제1 전극층과 제2 전극층 사이에 배치되도록 상기 유전성 나노복합체층 상에 상기 제2 전극 층을 배치하는 단계;를 포함하는,

프랙셔널 오더 커패시터의 제조 방법. - 제23항에 있어서,

상기 유전성 나노복합체 층은 적어도 매트릭스 물질 및 전도성 충전 물질을 포함하는,

프랙셔널 오더 커패시터의 제조 방법. - 제24항에 있어서,

상기 전도성 충전 물질은 그래핀인,

프랙셔널 오더 커패시터의 제조 방법. - 제25항에 있어서,

상기 그래핀은 부분적으로 산화된,

프랙셔널 오더 커패시터의 제조 방법. - 제25항에 있어서,

상기 그래핀은 완전히 비산화된,

프랙셔널 오더 커패시터의 제조 방법. - 제25항에 있어서,

상기 그래핀의 상기 물질 중량 백분율은 상기 유전성 나노복합체층의 총 중량을 기준으로, 약 0.1% 내지 15% 사이에서 선택되는,

프랙셔널 오더 커패시터의 제조 방법. - 제24항에 있어서,

상기 매트릭스 물질은 폴리머를 포함하는,

프랙셔널 오더 커패시터의 제조 방법. - 제23항에 있어서,

상기 제1 및 제2 전극 층은 전도성 물질을 포함하는,

프랙셔널 오더 커패시터의 제조 방법. - 제30항에 있어서,

상기 제1 전극 층은 백금을 포함하며, 상기 제2 전극 층은 알루미늄을 포함하는,

프랙셔널 오더 커패시터의 제조 방법. - 제30항에 있어서,

상기 제1 및 제2 전극층은 PEDOT:PSS를 포함하는,

프랙셔널 오더 커패시터의 제조방법. - 제23항에 있어서,

상기 유전성 나노복합체층은 용액 캐스팅(solution casting)에 의해 상기 제1 전극층 상에 배치되는,

프랙셔널 오더 커패시터의 제조 방법. - 제23항에 있어서,

상기 유전성 나노복합체 층은 닥터 블레이드에 의해 상기 제1 전극층 상에 배치되는,

프랙셔널 오더 커패시터의 제조 방법. - 제23항에 있어서,

상기 유전성 나노복합체 층은 테이프 캐스팅(tape casting)에 의해 상기 제1 전극층 상에 배치되는,

프랙셔널 오더 커패시터의 제조 방법. - 제23항에 있어서,

상기 유전성 나노복합체 층은 실크-스크린 프린팅(silk-screen printing)에 의해 상기 제1 전극층 상에 배치되는,

프랙셔널 오더 커패시터의 제조 방법. - 제23항에 있어서,

상기 유전성 나노복합체층은 핫 프레스(hot pressing)에 의해 상기 제1 전극층 상에 배치되는,

프랙셔널 오더 커패시터의 제조 방법. - 제23항에 있어서,

상기 제2 전극층은 섀도우 마스크를 이용하여 상기 유전성 나노복합체 층 상에 열증발되는(thermally-evaporated),

프랙셔널 오더 커패시터의 제조 방법. - 제23항에 있어서,

상기 복소 임피던스 위상각은 0°내지 - 90°인,

프랙셔널 오더 커패시터의 제조 방법. - 제23항에 있어서,

상기 프랙셔널 오더 커패시터를 집적 회로 내에 패키징하는 단계를 더 포함하는,

프랙셔널 오더 커패시터의 제조 방법. - 제23항에 있어서,

상기 프랙셔널 오더 커패시터를 인쇄회로 기판 내에 패키징하는 단계를 더 포함하는,

프랙셔널 오더 커패시터의 제조 방법. - 제1항 내지 제13항 중 어느 한 항에 따른 프랙셔널 오더 커패시터로 전기 신호 상에 선택 지연(selected delay)을 부과하는 지연 회로 작동 방법으로서,

특정 복소 임피던스 위상각을 얻기 위하여 상기 프랙셔널 오더 커패시터의 유전성 나노복합체층 내 충전 물질의 물질 중량 백분율을 선택하는 단계;

입력 신호에 응답하는 충전율로 상기 프랙셔널 오더 커패시터를 제1 전압으로 충전하는 단계;

상기 입력 신호에 응답하는 충전율로 상기 프랙셔널 오더 커패시터를 제2 전압으로 방전하는 단계;

상기 프랙셔널 오더 커패시터의 상기 복소 임피던스 위상각의 함수로 지연 신호(delayed signal)를 생성하는 단계;를 포함하는,

지연 회로 작동 방법. - 저항 및 제1항 내지 제13항 중 어느 한 항에 따른 프랙셔널 오더 커패시터를 포함하는 필터의 주파수 응답을 조절하는 방법으로서,

특정 복소 임피던스 위상각을 얻기 위하여 상기 프랙셔널 오더 커패시터의 유전성 나노복합체층 내 충전 물질의 물질 중량 백분율을 선택하는 단계;

상기 프랙셔널 커패시터과 저항의 직렬 연결에 대해 입력 전압을 공급하는 단계;

상기 저항에 걸친 상기 전압에 기초하여 출력 전압을 공급하는 단계;

특정 주파수에서 상기 필터의 게인(gain)을 측정하는 단계;

상기 복소 임피던스 위상각을 변화시킴으로써 상기 특정 주파수에서 상기 필터의 상기 게인에 따라 상기 프랙셔널 오더 커패시터의 커패시턴스를 조절하는 단계;를 포함하는,

주파수 응답을 조절하는 방법. - 제1항 내지 제10항 중 어느 한 항에 따른 프랙셔널 오더 커패시터를 포함하는 RF 통신 회로 작동 방법으로서,

특정 복소 임피던스 위상각을 얻기 위하여 상기 프랙셔널 오더 커패시터의 유전성 나노복합체층 내 충전 물질의 물질 중량 백분율을 선택하는 단계;

공진 주파수에서 RF 신호를 발생시키는 단계;

상기 RF 통신회로 내의 다른 구성요소들의 직렬 저항값을 검출하는 단계;

상기 복소 임피던스 위상각을 변화시킴으로써 상기 RF 통신회로 내의 다른 구성요소들의 등가 직렬 저항값의 적어도 일부를 오프셋하기 위하여 상기 프랙셔널 오더 커패시터의 음의 저항값을 설정하는 단계를 포함하는,

RF 통신 회로 작동 방법.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201361783373P | 2013-03-14 | 2013-03-14 | |

| US61/783,373 | 2013-03-14 | ||

| PCT/US2014/021173 WO2014158970A1 (en) | 2013-03-14 | 2014-03-06 | Fractional order capacitor based on dielectric polymer doped with conductive nano-fillers |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20150128743A true KR20150128743A (ko) | 2015-11-18 |

Family

ID=50346167

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020157026181A KR20150128743A (ko) | 2013-03-14 | 2014-03-06 | 전도성 나노-필러로 도핑된 유전성 폴리머 기반 프랙셔널 오더 커패시터 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US9305706B2 (ko) |

| EP (2) | EP2973626A1 (ko) |

| JP (1) | JP6298878B2 (ko) |

| KR (1) | KR20150128743A (ko) |

| CN (1) | CN105190805A (ko) |

| TW (1) | TWI620215B (ko) |

| WO (1) | WO2014158970A1 (ko) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20190031928A (ko) * | 2017-09-19 | 2019-03-27 | 유덕첨단소재(주) | 그래핀을 이용한 적층 세라믹 커패시터 및 이의 제조 방법 |

| US10403436B2 (en) | 2016-12-19 | 2019-09-03 | Samsung Electro-Mechanics Co., Ltd. | Acrylic binder and multilayer electronic component using the same |

| US10699850B2 (en) | 2018-04-30 | 2020-06-30 | Samsung Electro-Mechanics Co., Ltd. | Multilayer capacitor including graphene platelets |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20140293513A1 (en) * | 2013-03-26 | 2014-10-02 | Custom Electronics, Inc. | Graphene-based high voltage electrodes and materials |

| US10091870B2 (en) * | 2015-03-31 | 2018-10-02 | International Business Machines Corporation | Methods for tuning propagation velocity with functionalized carbon nanomaterial |

| CN105790724B (zh) * | 2016-04-28 | 2018-04-13 | 华南理工大学 | 一种0到1阶功率级分数阶电容元件的制备方法 |

| CN106411291B (zh) * | 2016-07-31 | 2023-04-07 | 华南理工大学 | 一种阶数大于1的大功率可调高频分数阶电容及其控制方法 |

| WO2018193403A1 (en) * | 2017-04-19 | 2018-10-25 | Sabic Global Technologies, B.V. | Method of modeling a fractional order capacitor design |

| WO2018193405A1 (en) * | 2017-04-19 | 2018-10-25 | Sabic Global Technologies, B.V. | Phase angle tunable fractional-order capacitors including poly (vinylidene fluoride)-based polymers and blends and methods of manufacture thereof |

| WO2018193402A1 (en) * | 2017-04-19 | 2018-10-25 | Sabic Global Technologies, B.V. | Phase angle tunable fractional-order capacitors including multi-layer ferroelectric polymer dielectric and methods of manufacture thereof |

| WO2018193404A1 (en) * | 2017-04-19 | 2018-10-25 | Sabic Global Technologies, B.V. | Numerical design of fractional order capacitors |

| FR3066398B1 (fr) * | 2017-05-18 | 2019-07-05 | X'sin | Prise d'escalade a detection capacitive, procede de realisation et mur associes |

| CN111537400B (zh) * | 2020-05-19 | 2023-03-31 | 北京林业大学 | 一种在线测定水中颗粒物分形维数的方法 |

Family Cites Families (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0461704A (ja) * | 1990-06-27 | 1992-02-27 | Daishinku Co | 高分子複合誘電体 |

| JPH05307911A (ja) * | 1992-04-30 | 1993-11-19 | Japan Aviation Electron Ind Ltd | 高誘電率複合材料 |

| JPH07106181A (ja) * | 1993-10-04 | 1995-04-21 | Towa Electron Kk | 導体、誘電体混合型コンデンサ |

| US6444478B1 (en) * | 1999-08-31 | 2002-09-03 | Micron Technology, Inc. | Dielectric films and methods of forming same |

| WO2002100931A1 (en) * | 2001-06-08 | 2002-12-19 | Eikos, Inc. | Nanocomposite dielectrics |

| DE10338277A1 (de) * | 2003-08-20 | 2005-03-17 | Siemens Ag | Organischer Kondensator mit spannungsgesteuerter Kapazität |

| JP2006107770A (ja) * | 2004-09-30 | 2006-04-20 | Sumitomo Bakelite Co Ltd | 誘電体ペースト、キャパシタおよび基板 |

| US7623340B1 (en) | 2006-08-07 | 2009-11-24 | Nanotek Instruments, Inc. | Nano-scaled graphene plate nanocomposites for supercapacitor electrodes |

| US7875219B2 (en) | 2007-10-04 | 2011-01-25 | Nanotek Instruments, Inc. | Process for producing nano-scaled graphene platelet nanocomposite electrodes for supercapacitors |

| KR20100012583A (ko) * | 2008-07-29 | 2010-02-08 | 전남도립대학산학협력단 | 폴리머 나노복합체 및 이를 이용한 전기 절연체 |

| US8613898B2 (en) | 2010-01-28 | 2013-12-24 | University Of Central Florida Research Foundation, Inc. | Supramolecular structures comprising at least partially conjugated polymers attached to carbon nanotubes or graphenes |

| CN101882480B (zh) | 2010-06-18 | 2011-12-14 | 中国科学院电工研究所 | 一种聚吡咯/石墨烯复合材料的制备方法 |

| JP5327183B2 (ja) | 2010-10-19 | 2013-10-30 | ブラザー工業株式会社 | 印刷装置 |

| JP2014501028A (ja) | 2010-10-27 | 2014-01-16 | ▲海▼洋王照明科技股▲ふん▼有限公司 | 複合電極材及びその製造方法、並びに応用 |

| KR20120058127A (ko) * | 2010-11-29 | 2012-06-07 | 삼성전기주식회사 | 다층 배선기판용 절연 수지 조성물 및 이를 포함하는 다층 배선기판 |

| JP5674143B2 (ja) * | 2011-03-09 | 2015-02-25 | 株式会社豊田中央研究所 | 誘電材料 |

| US9593413B2 (en) | 2011-05-04 | 2017-03-14 | Uchicago Argonne, Llc | Composite materials for battery applications |

| JP6387300B2 (ja) | 2011-06-20 | 2018-09-05 | 矢崎総業株式会社 | 炭素の凝集アセンブリおよびその用途 |

| CN104093786A (zh) * | 2011-09-01 | 2014-10-08 | 伦斯勒理工学院 | 具有非线性电阻率的氧化石墨烯聚合物 |

| JP5957463B2 (ja) * | 2011-10-31 | 2016-07-27 | 昭和電工株式会社 | 伝送シート、伝送ユニット及びそれらを備えた非接触電力伝送システム |

| CN102509642A (zh) | 2011-11-21 | 2012-06-20 | 余泉茂 | 具有膨胀石墨/石墨烯/活性炭的超级电容器的制备方法 |

| CN102530931B (zh) | 2011-12-14 | 2014-04-02 | 天津大学 | 基于石墨烯的纳米复合材料及其制备方法 |

| CN102496481A (zh) | 2011-12-23 | 2012-06-13 | 北京航空航天大学 | 一种石墨烯/聚吡咯纳米管复合材料以及一种以其为电极的超级电容器及其制备方法 |

| CN102604275B (zh) * | 2012-03-07 | 2014-06-11 | 浙江工业大学 | 一种聚偏氟乙烯/石墨烯复合材料及其制备方法 |

| CN102627768A (zh) | 2012-04-10 | 2012-08-08 | 上海交通大学 | 超级电容器电极用石墨烯/聚吡咯纳米复合材料的制备方法 |

| CN102709053A (zh) * | 2012-06-04 | 2012-10-03 | 电子科技大学 | 一种聚合物叠片式电容器及其制备方法 |

-

2014

- 2014-03-06 EP EP14712145.3A patent/EP2973626A1/en not_active Ceased

- 2014-03-06 US US14/199,296 patent/US9305706B2/en not_active Expired - Fee Related

- 2014-03-06 CN CN201480013947.4A patent/CN105190805A/zh active Pending

- 2014-03-06 JP JP2016500731A patent/JP6298878B2/ja not_active Expired - Fee Related

- 2014-03-06 EP EP19158458.0A patent/EP3511964A1/en not_active Withdrawn

- 2014-03-06 KR KR1020157026181A patent/KR20150128743A/ko not_active Application Discontinuation

- 2014-03-06 WO PCT/US2014/021173 patent/WO2014158970A1/en active Application Filing

- 2014-03-14 TW TW103109506A patent/TWI620215B/zh not_active IP Right Cessation

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10403436B2 (en) | 2016-12-19 | 2019-09-03 | Samsung Electro-Mechanics Co., Ltd. | Acrylic binder and multilayer electronic component using the same |

| US10763044B2 (en) | 2016-12-19 | 2020-09-01 | Samsung Electro-Mechanics Co., Ltd. | Acrylic binder and multilayer electronic component using the same |

| US11004611B2 (en) | 2016-12-19 | 2021-05-11 | Samsung Electro-Mechanics Co., Ltd. | Acrylic binder and multilayer electronic component using the same |

| KR20190031928A (ko) * | 2017-09-19 | 2019-03-27 | 유덕첨단소재(주) | 그래핀을 이용한 적층 세라믹 커패시터 및 이의 제조 방법 |

| US10699850B2 (en) | 2018-04-30 | 2020-06-30 | Samsung Electro-Mechanics Co., Ltd. | Multilayer capacitor including graphene platelets |

Also Published As

| Publication number | Publication date |

|---|---|

| EP3511964A1 (en) | 2019-07-17 |

| JP6298878B2 (ja) | 2018-03-20 |

| WO2014158970A1 (en) | 2014-10-02 |

| CN105190805A (zh) | 2015-12-23 |

| US9305706B2 (en) | 2016-04-05 |

| EP2973626A1 (en) | 2016-01-20 |

| TWI620215B (zh) | 2018-04-01 |

| JP2016511550A (ja) | 2016-04-14 |

| TW201505052A (zh) | 2015-02-01 |

| US20140266374A1 (en) | 2014-09-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20150128743A (ko) | 전도성 나노-필러로 도핑된 유전성 폴리머 기반 프랙셔널 오더 커패시터 | |

| Flowers et al. | 3D printing electronic components and circuits with conductive thermoplastic filament | |

| Mahendia et al. | Electrical conductivity and dielectric spectroscopic studies of PVA–Ag nanocomposite films | |

| Arnal et al. | 3D multi-layer additive manufacturing of a 2.45 GHz RF front end | |

| CA2947983C (en) | Energy storage device and method of production thereof | |

| EP3143651B1 (en) | Capacitor and method of production thereof | |

| Haghzadeh et al. | All-printed flexible microwave varactors and phase shifters based on a tunable BST/polymer | |

| JP6421169B2 (ja) | 疲労特性および破壊特性が改善された強誘電体キャパシタ | |

| Adams et al. | 3D‐printed spherical dipole antenna integrated on small RF node | |

| Agambayev et al. | Towards fractional-order capacitors with broad tunable constant phase angles: Multi-walled carbon nanotube-polymer composite as a case study | |

| Janeczek et al. | Investigation of ultra-high-frequency antennas printed with polymer pastes on flexible substrates | |

| Eid et al. | Nanotechnology-empowered flexible printed wireless electronics: A review of various applications of printed materials | |

| Li et al. | All Screen‐Printed, Polymer‐Nanowire Based Foldable Electronics for mm‐Wave Applications | |

| Raj et al. | Novel nanomagnetic materials for high-frequency RF applications | |

| Matyas et al. | Antenna of silver nanoparticles mounted on a flexible polymer substrate constructed using inkjet print technology | |

| Matyas et al. | Microstrip antenna from silver nanoparticles printed on a flexible polymer substrate | |

| Willis | Compact form fitting small antennas using three-dimensional rapid prototyping | |

| Hajisaeid et al. | Printed planar tunable composite right/left‐handed leaky‐wave antenna based on a tunable polymer‐BST substrate | |

| Paragua et al. | Study and characterization of CNT Inkjet printed patterns for paper-based RF components | |

| Church et al. | Printed electronic processes for flexible hybrid circuits and antennas | |

| Le et al. | Inkjet printing of radio frequency electronics: design methodologies and application of novel nanotechnologies | |

| Vineetha et al. | Flexible bandpass filter with silver conductive layer for GPS, ISM, PCS, LTE and WLAN applications | |

| Raj et al. | Processing and dielectric properties of nanocomposite thin film “supercapacitors” for high-frequency embedded decoupling | |

| Vaseem et al. | 3D inkjet printed radio frequency inductors and capacitors | |

| Gbotemi et al. | Characterization of PMMA/BaTiO 3 composite layers through printed capacitor structures for microwave frequency applications |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| E902 | Notification of reason for refusal | ||

| E601 | Decision to refuse application |