KR20140058557A - 반도체 패키지 수지 조성물 및 그의 사용 방법 - Google Patents

반도체 패키지 수지 조성물 및 그의 사용 방법 Download PDFInfo

- Publication number

- KR20140058557A KR20140058557A KR1020147003608A KR20147003608A KR20140058557A KR 20140058557 A KR20140058557 A KR 20140058557A KR 1020147003608 A KR1020147003608 A KR 1020147003608A KR 20147003608 A KR20147003608 A KR 20147003608A KR 20140058557 A KR20140058557 A KR 20140058557A

- Authority

- KR

- South Korea

- Prior art keywords

- semiconductor package

- resin composition

- package resin

- substrate

- particles

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Ceased

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/29—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the material, e.g. carbon

- H01L23/293—Organic, e.g. plastic

- H01L23/296—Organo-silicon compounds

-

- C—CHEMISTRY; METALLURGY

- C08—ORGANIC MACROMOLECULAR COMPOUNDS; THEIR PREPARATION OR CHEMICAL WORKING-UP; COMPOSITIONS BASED THEREON

- C08L—COMPOSITIONS OF MACROMOLECULAR COMPOUNDS

- C08L63/00—Compositions of epoxy resins; Compositions of derivatives of epoxy resins

-

- C—CHEMISTRY; METALLURGY

- C08—ORGANIC MACROMOLECULAR COMPOUNDS; THEIR PREPARATION OR CHEMICAL WORKING-UP; COMPOSITIONS BASED THEREON

- C08K—Use of inorganic or non-macromolecular organic substances as compounding ingredients

- C08K3/00—Use of inorganic substances as compounding ingredients

- C08K3/34—Silicon-containing compounds

- C08K3/36—Silica

-

- C—CHEMISTRY; METALLURGY

- C08—ORGANIC MACROMOLECULAR COMPOUNDS; THEIR PREPARATION OR CHEMICAL WORKING-UP; COMPOSITIONS BASED THEREON

- C08K—Use of inorganic or non-macromolecular organic substances as compounding ingredients

- C08K9/00—Use of pretreated ingredients

- C08K9/04—Ingredients treated with organic substances

- C08K9/06—Ingredients treated with organic substances with silicon-containing compounds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the groups H01L21/18 - H01L21/326 or H10D48/04 - H10D48/07 e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

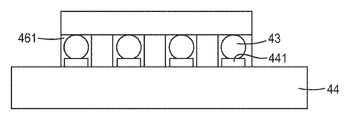

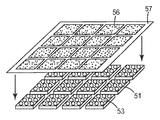

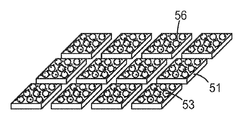

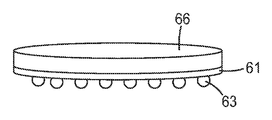

- H01L21/563—Encapsulation of active face of flip-chip device, e.g. underfilling or underencapsulation of flip-chip, encapsulation preform on chip or mounting substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/02—Containers; Seals

- H01L23/10—Containers; Seals characterised by the material or arrangement of seals between parts, e.g. between cap and base of the container or between leads and walls of the container

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/29—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the material, e.g. carbon

- H01L23/293—Organic, e.g. plastic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/29—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the material, e.g. carbon

- H01L23/293—Organic, e.g. plastic

- H01L23/295—Organic, e.g. plastic containing a filler

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32135—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/32145—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73253—Bump and layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/91—Methods for connecting semiconductor or solid state bodies including different methods provided for in two or more of groups H01L2224/80 - H01L2224/90

- H01L2224/92—Specific sequence of method steps

- H01L2224/921—Connecting a surface with connectors of different types

- H01L2224/9212—Sequential connecting processes

- H01L2224/92122—Sequential connecting processes the first connecting process involving a bump connector

- H01L2224/92125—Sequential connecting processes the first connecting process involving a bump connector the second connecting process involving a layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1204—Optical Diode

- H01L2924/12044—OLED

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/85—Packages

- H10H20/852—Encapsulations

- H10H20/854—Encapsulations characterised by their material, e.g. epoxy or silicone resins

Landscapes

- Chemical & Material Sciences (AREA)

- Engineering & Computer Science (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Organic Chemistry (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Health & Medical Sciences (AREA)

- Medicinal Chemistry (AREA)

- Polymers & Plastics (AREA)

- Manufacturing & Machinery (AREA)

- Structures Or Materials For Encapsulating Or Coating Semiconductor Devices Or Solid State Devices (AREA)

- Compositions Of Macromolecular Compounds (AREA)

- Wire Bonding (AREA)

- Epoxy Resins (AREA)

- Polymerisation Methods In General (AREA)

- Life Sciences & Earth Sciences (AREA)

- Materials Engineering (AREA)

- Wood Science & Technology (AREA)

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201161508344P | 2011-07-15 | 2011-07-15 | |

| US61/508,344 | 2011-07-15 | ||

| PCT/US2012/045916 WO2013012587A2 (en) | 2011-07-15 | 2012-07-09 | Semiconductor package resin composition and usage method thereof |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20140058557A true KR20140058557A (ko) | 2014-05-14 |

Family

ID=47558664

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020147003608A Ceased KR20140058557A (ko) | 2011-07-15 | 2012-07-09 | 반도체 패키지 수지 조성물 및 그의 사용 방법 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US9230873B2 (enExample) |

| JP (2) | JP6155261B2 (enExample) |

| KR (1) | KR20140058557A (enExample) |

| TW (1) | TWI550018B (enExample) |

| WO (1) | WO2013012587A2 (enExample) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2012134731A1 (en) * | 2011-03-28 | 2012-10-04 | 3M Innovative Properties Company | Curable composition, article, method of curing, and reaction product |

| JP6271164B2 (ja) * | 2013-06-17 | 2018-01-31 | 日立オートモティブシステムズ株式会社 | 箱型車載制御装置 |

| KR102186491B1 (ko) * | 2014-01-02 | 2020-12-03 | 헨켈 아이피 앤드 홀딩 게엠베하 | 나노-미립자 충전제를 함유하는 필름 |

| US9220183B1 (en) * | 2014-07-16 | 2015-12-22 | International Business Machines Corporation | Devices employing semiconductor die having hydrophobic coatings, and related cooling methods |

| JP6872313B2 (ja) * | 2015-10-13 | 2021-05-19 | リンテック株式会社 | 半導体装置および複合シート |

| WO2017122717A1 (ja) * | 2016-01-12 | 2017-07-20 | 日立化成株式会社 | 感光性樹脂組成物、それを用いたドライフィルム、プリント配線板、及びプリント配線板の製造方法 |

| JP7454906B2 (ja) * | 2016-10-14 | 2024-03-25 | 株式会社レゾナック | アンダーフィル材、電子部品装置及び電子部品装置の製造方法 |

| CN111758168B (zh) * | 2018-02-19 | 2024-05-17 | 昕诺飞控股有限公司 | 具有光引擎的经密封的设备 |

| JP7109940B2 (ja) * | 2018-03-08 | 2022-08-01 | 日東電工株式会社 | 封止用接着シート |

| WO2024228184A1 (en) * | 2023-05-04 | 2024-11-07 | Inpack Technologies - Limited Partnership | Method of forming non-conductive polymer layers with a controlled coefficient of thermal expansion |

Family Cites Families (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6228681B1 (en) | 1999-03-10 | 2001-05-08 | Fry's Metals, Inc. | Flip chip having integral mask and underfill providing two-stage bump formation |

| US6245595B1 (en) | 1999-07-22 | 2001-06-12 | National Semiconductor Corporation | Techniques for wafer level molding of underfill encapsulant |

| US6281046B1 (en) | 2000-04-25 | 2001-08-28 | Atmel Corporation | Method of forming an integrated circuit package at a wafer level |

| US6573122B2 (en) | 2001-03-28 | 2003-06-03 | International Rectifier Corporation | Wafer level insulation underfill for die attach |

| US6794761B2 (en) | 2001-04-26 | 2004-09-21 | Intel Corporation | No-flow underfill material |

| US20030111519A1 (en) | 2001-09-04 | 2003-06-19 | 3M Innovative Properties Company | Fluxing compositions |

| DE60232942D1 (de) * | 2001-10-09 | 2009-08-27 | Mitsubishi Chem Corp | Strahlungshärtbare Beschichtungszusammensetzung |

| US20030162911A1 (en) | 2002-01-31 | 2003-08-28 | Yue Xiao | No flow underfill composition |

| US20060194064A1 (en) | 2002-03-01 | 2006-08-31 | Xiao Allison Y | Underfill encapsulant for wafer packaging and method for its application |

| US20040101688A1 (en) | 2002-11-22 | 2004-05-27 | Slawomir Rubinsztajn | Curable epoxy compositions, methods and articles made therefrom |

| US20060147719A1 (en) | 2002-11-22 | 2006-07-06 | Slawomir Rubinsztajn | Curable composition, underfill, and method |

| US7022410B2 (en) | 2003-12-16 | 2006-04-04 | General Electric Company | Combinations of resin compositions and methods of use thereof |

| KR100774798B1 (ko) | 2004-05-13 | 2007-11-07 | 닛토덴코 가부시키가이샤 | 반도체 캡슐화용 에폭시 수지 조성물 및 이것을 이용한 반도체 장치 |

| WO2007049573A1 (ja) | 2005-10-28 | 2007-05-03 | Sumitomo Osaka Cement Co., Ltd. | 無機酸化物透明分散液と無機酸化物粒子含有樹脂組成物、発光素子封止用組成物及び発光素子、ハードコート膜と光学機能膜及び光学部品、並びに無機酸化物粒子含有樹脂組成物の製造方法 |

| JP2008180992A (ja) * | 2007-01-25 | 2008-08-07 | Hitachi Chem Co Ltd | 感光性樹脂組成物、永久レジスト用感光性フィルム、レジストパターンの形成方法、プリント配線板及び半導体パッケージ |

| EP2135276A2 (en) | 2007-03-13 | 2009-12-23 | Lord Corporation | Die attachment method with a covex surface underfill |

| JP2008297373A (ja) | 2007-05-29 | 2008-12-11 | Somar Corp | 液状エポキシ樹脂組成物からなるアンダーフィル材及びフリップチップ型半導体装置 |

| JP5004351B2 (ja) | 2007-11-30 | 2012-08-22 | 信越化学工業株式会社 | 半導体装置の製造方法 |

| WO2010098636A2 (ko) | 2009-02-27 | 2010-09-02 | 주식회사 엘지화학 | 내마모성 및 내오염성이 우수한 코팅 조성물 및 코팅 필름 |

| CN102458646B (zh) * | 2009-05-26 | 2014-12-03 | 3M创新有限公司 | 制备填充的树脂的工艺 |

-

2012

- 2012-07-09 JP JP2014520234A patent/JP6155261B2/ja not_active Expired - Fee Related

- 2012-07-09 US US14/131,827 patent/US9230873B2/en not_active Expired - Fee Related

- 2012-07-09 WO PCT/US2012/045916 patent/WO2013012587A2/en not_active Ceased

- 2012-07-09 KR KR1020147003608A patent/KR20140058557A/ko not_active Ceased

- 2012-07-13 TW TW101125423A patent/TWI550018B/zh not_active IP Right Cessation

-

2015

- 2015-07-28 US US14/810,631 patent/US9773714B2/en not_active Expired - Fee Related

-

2017

- 2017-03-08 JP JP2017043422A patent/JP2017133023A/ja active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| US9230873B2 (en) | 2016-01-05 |

| TW201311806A (zh) | 2013-03-16 |

| TWI550018B (zh) | 2016-09-21 |

| JP2014524957A (ja) | 2014-09-25 |

| WO2013012587A2 (en) | 2013-01-24 |

| US9773714B2 (en) | 2017-09-26 |

| JP6155261B2 (ja) | 2017-06-28 |

| US20140217622A1 (en) | 2014-08-07 |

| WO2013012587A3 (en) | 2013-04-18 |

| JP2017133023A (ja) | 2017-08-03 |

| US20150329740A1 (en) | 2015-11-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6155261B2 (ja) | 半導体パッケージ樹脂組成物及びその使用方法 | |

| JP4892164B2 (ja) | 液状エポキシ樹脂組成物及び電子部品装置 | |

| CN108137904B (zh) | 底部填充用树脂组合物、电子部件装置和电子部件装置的制造方法 | |

| WO2018221681A1 (ja) | 封止用液状樹脂組成物及び電子部品装置 | |

| CN110770275A (zh) | 压缩成型用液状树脂组合物及电子部件装置 | |

| JP6233441B2 (ja) | 液状エポキシ樹脂組成物及び電子部品装置 | |

| JP5664220B2 (ja) | 半導体封止材料及び半導体装置 | |

| JP2024096265A (ja) | 樹脂組成物及び電子部品装置 | |

| JP2015193851A (ja) | 液状エポキシ樹脂組成物及び電子部品装置 | |

| KR20190133564A (ko) | 반도체 소자 밀봉용 에폭시 수지 조성물 및 이를 이용하여 밀봉된 반도체 장치 | |

| JP5523816B2 (ja) | 変性樹脂組成物、その製造方法、及びそれを含む硬化性樹脂組成物 | |

| WO2012018684A1 (en) | Encapsulating resin composition | |

| TWI868209B (zh) | 壓縮成形用密封材及電子零件裝置 | |

| JP2009057575A (ja) | 液状エポキシ樹脂組成物及び電子部品装置 | |

| JP2005171209A (ja) | フィラー含有樹脂組成物及びその製造方法 | |

| JP5708666B2 (ja) | 液状エポキシ樹脂組成物及び電子部品装置 | |

| WO2017057637A1 (ja) | 封止用液状組成物、封止材、及び電子部品装置 | |

| JP5664358B2 (ja) | エポキシ樹脂組成物、半導体封止材料および半導体装置 | |

| JP2016040393A (ja) | 液状エポキシ樹脂組成物及び電子部品装置 | |

| JP2015180760A (ja) | 液状エポキシ樹脂組成物及び電子部品装置 | |

| JP5924443B2 (ja) | 液状エポキシ樹脂組成物及び電子部品装置 | |

| JP2015110803A (ja) | 液状エポキシ樹脂組成物及び電子部品装置 | |

| JP5929977B2 (ja) | 液状エポキシ樹脂組成物及び電子部品装置 | |

| JP7753740B2 (ja) | 熱硬化性樹脂組成物及び電子部品装置 | |

| KR101293791B1 (ko) | 반도체 소자 밀봉용 에폭시 수지 조성물 및 이를 이용한 반도체 소자 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0105 | International application |

Patent event date: 20140212 Patent event code: PA01051R01D Comment text: International Patent Application |

|

| PG1501 | Laying open of application | ||

| A201 | Request for examination | ||

| PA0201 | Request for examination |

Patent event code: PA02012R01D Patent event date: 20170405 Comment text: Request for Examination of Application |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

Comment text: Notification of reason for refusal Patent event date: 20171205 Patent event code: PE09021S01D |

|

| E601 | Decision to refuse application | ||

| PE0601 | Decision on rejection of patent |

Patent event date: 20180607 Comment text: Decision to Refuse Application Patent event code: PE06012S01D Patent event date: 20171205 Comment text: Notification of reason for refusal Patent event code: PE06011S01I |