KR20110061641A - 탄화규소 반도체 장치 - Google Patents

탄화규소 반도체 장치 Download PDFInfo

- Publication number

- KR20110061641A KR20110061641A KR1020117009510A KR20117009510A KR20110061641A KR 20110061641 A KR20110061641 A KR 20110061641A KR 1020117009510 A KR1020117009510 A KR 1020117009510A KR 20117009510 A KR20117009510 A KR 20117009510A KR 20110061641 A KR20110061641 A KR 20110061641A

- Authority

- KR

- South Korea

- Prior art keywords

- region

- type

- layer

- substrate

- semiconductor device

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 68

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 title claims abstract description 49

- 229910010271 silicon carbide Inorganic materials 0.000 title claims abstract description 46

- 239000012535 impurity Substances 0.000 claims abstract description 90

- 239000000758 substrate Substances 0.000 claims abstract description 78

- 238000000034 method Methods 0.000 claims description 35

- 239000000463 material Substances 0.000 claims description 20

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 claims description 16

- 229910052782 aluminium Inorganic materials 0.000 claims description 12

- 239000010936 titanium Substances 0.000 claims description 11

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 claims description 10

- 229910052719 titanium Inorganic materials 0.000 claims description 9

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 claims description 7

- 229910052759 nickel Inorganic materials 0.000 claims description 6

- 230000015556 catabolic process Effects 0.000 abstract description 24

- 239000010410 layer Substances 0.000 description 176

- 239000007789 gas Substances 0.000 description 14

- 230000000052 comparative effect Effects 0.000 description 13

- 238000010438 heat treatment Methods 0.000 description 13

- 239000004020 conductor Substances 0.000 description 9

- 238000005468 ion implantation Methods 0.000 description 9

- 238000005259 measurement Methods 0.000 description 9

- 230000015572 biosynthetic process Effects 0.000 description 8

- 238000004519 manufacturing process Methods 0.000 description 8

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 6

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 5

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 5

- 230000004913 activation Effects 0.000 description 5

- 230000007547 defect Effects 0.000 description 5

- 238000005530 etching Methods 0.000 description 5

- 238000002474 experimental method Methods 0.000 description 5

- 238000000206 photolithography Methods 0.000 description 5

- 229910052710 silicon Inorganic materials 0.000 description 5

- 239000010703 silicon Substances 0.000 description 5

- 238000002513 implantation Methods 0.000 description 4

- 238000002347 injection Methods 0.000 description 4

- 239000007924 injection Substances 0.000 description 4

- 150000002500 ions Chemical class 0.000 description 4

- 238000000137 annealing Methods 0.000 description 3

- 229910052786 argon Inorganic materials 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 230000002349 favourable effect Effects 0.000 description 3

- 229910052751 metal Inorganic materials 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- 230000003647 oxidation Effects 0.000 description 3

- 238000007254 oxidation reaction Methods 0.000 description 3

- ATUOYWHBWRKTHZ-UHFFFAOYSA-N Propane Chemical compound CCC ATUOYWHBWRKTHZ-UHFFFAOYSA-N 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 238000005275 alloying Methods 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 238000009826 distribution Methods 0.000 description 2

- 238000001312 dry etching Methods 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 230000014759 maintenance of location Effects 0.000 description 2

- 150000002739 metals Chemical class 0.000 description 2

- 229910052757 nitrogen Inorganic materials 0.000 description 2

- 238000001020 plasma etching Methods 0.000 description 2

- 238000002360 preparation method Methods 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 229910021332 silicide Inorganic materials 0.000 description 2

- JLTRXTDYQLMHGR-UHFFFAOYSA-N trimethylaluminium Chemical compound C[Al](C)C JLTRXTDYQLMHGR-UHFFFAOYSA-N 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- 229910005883 NiSi Inorganic materials 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- 230000002159 abnormal effect Effects 0.000 description 1

- 230000003213 activating effect Effects 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 239000012159 carrier gas Substances 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- ZOCHARZZJNPSEU-UHFFFAOYSA-N diboron Chemical compound B#B ZOCHARZZJNPSEU-UHFFFAOYSA-N 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 125000004435 hydrogen atom Chemical class [H]* 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 238000012423 maintenance Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910021334 nickel silicide Inorganic materials 0.000 description 1

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 239000012071 phase Substances 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 239000001294 propane Substances 0.000 description 1

- 239000000700 radioactive tracer Substances 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 239000002344 surface layer Substances 0.000 description 1

- 239000012808 vapor phase Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/0445—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising crystalline silicon carbide

- H01L21/048—Making electrodes

- H01L21/0485—Ohmic electrodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66053—Multistep manufacturing processes of devices having a semiconductor body comprising crystalline silicon carbide

- H01L29/66068—Multistep manufacturing processes of devices having a semiconductor body comprising crystalline silicon carbide the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/80—Field effect transistors with field effect produced by a PN or other rectifying junction gate, i.e. potential-jump barrier

- H01L29/808—Field effect transistors with field effect produced by a PN or other rectifying junction gate, i.e. potential-jump barrier with a PN junction gate, e.g. PN homojunction gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/86—Types of semiconductor device ; Multistep manufacturing processes therefor controllable only by variation of the electric current supplied, or only the electric potential applied, to one or more of the electrodes carrying the current to be rectified, amplified, oscillated or switched

- H01L29/861—Diodes

- H01L29/8613—Mesa PN junction diodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/0445—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising crystalline silicon carbide

- H01L21/0455—Making n or p doped regions or layers, e.g. using diffusion

- H01L21/046—Making n or p doped regions or layers, e.g. using diffusion using ion implantation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/08—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/0843—Source or drain regions of field-effect devices

- H01L29/0847—Source or drain regions of field-effect devices of field-effect transistors with insulated gate

- H01L29/0852—Source or drain regions of field-effect devices of field-effect transistors with insulated gate of DMOS transistors

- H01L29/0873—Drain regions

- H01L29/0878—Impurity concentration or distribution

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/16—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only elements of Group IV of the Periodic System

- H01L29/1608—Silicon carbide

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/30—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by physical imperfections; having polished or roughened surface

- H01L29/32—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by physical imperfections; having polished or roughened surface the imperfections being within the semiconductor body

Abstract

오믹 전극의 접촉 저항을 저감시키고, 높은 내압 특성을 실현하는 것이 가능한 탄화규소 반도체 장치가 얻어진다. 반도체 장치(1)는 기판(2)과 불순물층으로서의 p+ 영역(25)을 구비한다. 기판(2)은 탄화규소로 이루어지고, 전위 밀도가 5×103 ㎝-2 이하이며, 도전형은 제1 도전형(n형)이다. p+ 영역(25)은 기판(2) 상에 형성되고, 상기 제1 도전형과는 상이한 제2 도전형의 도전성 불순물 농도가 1×1020 ㎝-3 이상 5×1021 ㎝-3 이하이다.

Description

본 발명은 탄화규소 반도체 장치에 관한 것으로, 보다 특정적으로는, 오믹 전극을 구비하는 탄화규소 반도체 장치에 관한 것이다.

종래, 탄화규소(SiC)를 이용한 FET(전계 효과 트랜지스터) 등의 탄화규소 반도체 장치가 알려져 있다[예컨대, 반도체 SiC 기술과 응용 제191쪽(비특허 문헌 1) 참조]. 예컨대, SiC를 이용한 MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)는 유니폴라 소자이면서, Si를 이용한 소자에서는 GTO(Gate Turn-Off thyristor)나 IGBT(Insulated Gate Bipolar Transistor) 등의 바이폴라 트랜지스터 소자에서만 실현되는 높은 내압(예컨대, 1 ㎸ 이상)을 실현할 수 있기 때문에, 고내압, 저손실 또한 고속 스위칭이 가능한 소자로서 기대되고 있다. 또, Si를 이용한 파워 디바이스로서의 MOSFET에서는, DMOSFET(Double-Diffused-MOSFET) 구조가 널리 채용되고 있으나, SiC를 이용한 MOSFET의 경우, 선택적인 도전성 불순물의 도핑을 이온 주입에 의해 실시하기 때문에, 그러한 이온 주입에 의해 도전성 불순물이 주입된 MOSFET는 DiMOSFET(Double-Implanted MOSFET)라고 불리고 있다.

반도체 SiC 기술과 응용, 일본, 일간 공업 신문사, 2003년 3월 31일, p.191

전술한 MOSFET에 있어서는, 예컨대 도전성이 n형인 SiC 기판의 표면 상에, SiC로 이루어지는 에피택셜층을 형성하고, 그 에피택셜층에 도전형이 p형인 도전성 불순물을 이온 주입함으로써 p형 영역을 형성한다. 그 p형 영역에 접촉하도록 p형의 오믹 전극이 형성된다.

여기서, p형 영역과 오믹 전극의 접촉 저항을 저감시키기 위해, p형 영역에서의 p형 도전성 불순물의 농도를 높게 하는(즉, 상기 도전성 불순물의 주입량을 많게 하는) 것이 고려된다. 그러나, 이 경우 p형 영역에 있어서 이온 주입에 기인하는 결함이 많이 형성된다. 이러한 결함은 전류의 누설 경로(leak path)로서 작용하기 때문에, MOSFET의 내압 성능이 열화하게 된다. 즉, SiC를 이용한 반도체 장치에 있어서, 오믹 전극과 불순물 영역의 접촉 저항을 저감시키는 동시에, 높은 내압 특성을 실현하는 것은 종래에는 어려웠다.

본 발명은 상기와 같은 과제를 해결하기 위해 이루어진 것으로, 본 발명의 목적은 오믹 전극의 접촉 저항을 저감시키고, 높은 내압 특성을 실현하는 것이 가능한 탄화규소 반도체 장치를 제공하는 것이다.

본 발명에 따른 탄화규소 반도체 장치는 기판과 불순물층을 구비한다. 기판은 탄화규소로 이루어지고, 전위 밀도가 5×103 ㎝-2 이하이며, 도전형은 제1 도전형이다. 불순물층은 기판 상에 형성되고, 제1 도전형과는 상이한 제2 도전형의 도전성 불순물 농도가 1×1020 ㎝-3 이상 5×1021 ㎝-3 이하이다.

이렇게 하면, 불순물층에 접촉하도록 오믹 전극을 형성한 경우에, 그 오믹 전극과 불순물층과의 접촉 저항을 실용상 문제없을 정도로 낮게 할 수 있고, 전위 밀도가 전술한 바와 같은 값으로 저감된 기판을 이용함으로써, 기판이나 그 기판 상에 형성되는 불순물층에 있어서 누설 경로가 될 수 있는 결함의 밀도를 충분히 저감시킬 수 있기 때문에, 탄화규소 반도체 장치의 내압 특성을 양호하게 할 수 있다.

또, 기판의 전위 밀도를 5×103 ㎝-2 이하로 한 것은, 이렇게 하면 탄화규소 반도체 장치의 내압 특성을 양호하게 유지하는 것이 가능하기 때문이다. 또한, 불순물층에서의 도전성 불순물 농도의 하한을 1×1020 ㎝-3로 한 것은, 이 값보다 도전성 불순물 농도를 내리면, 불순물층에 접촉하도록 오믹 전극을 형성했을 때에 그 오믹 전극과 불순물층과의 접촉 저항이 허용 범위를 넘어 커지기 때문이다. 또한, 불순물층에서의 도전성 불순물 농도의 상한을 5×1021 ㎝-3로 한 것은, 이 이상 도전성 불순물을 도입하면, 불순물층의 결정성이 저하되어, 탄화규소 반도체 장치의 특성이 열화되기 때문이다.

이와 같이, 본 발명에 따르면, 오믹 전극의 접촉 저항을 문제없을 정도로 저감시킬 수 있는 동시에, 내압 특성이 양호한 탄화규소 반도체 장치를 얻을 수 있다.

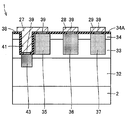

도 1은 본 발명에 따른 반도체 장치의 실시형태 1을 도시하는 단면 모식도이다.

도 2는 도 1에 도시한 반도체 장치의 제조 방법을 설명하기 위한 흐름도이다.

도 3은 본 발명에 따른 반도체 장치의 실시형태 2를 도시하는 단면 모식도이다.

도 4는 도 3에 도시한 반도체 장치의 제조 방법을 설명하기 위한 흐름도이다.

도 5는 실험을 위해 작성한 발명예의 시료를 도시하는 단면 모식도이다.

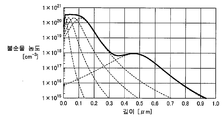

도 6은 도 5에 도시한 반도체 장치의 p+형층 및 p형층에서의 최외측 표면으로부터의 깊이 방향에서의 도전성 불순물의 농도 분포를 도시하는 그래프이다.

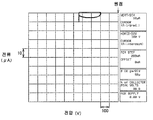

도 7은 본 발명의 발명예의 시료에 대한 역방향 전류 전압 특성을 도시하는 그래프이다.

도 8은 비교예 1의 시료에 대한 역방향 전류 전압 특성을 도시하는 그래프이다.

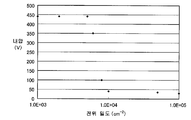

도 9는 실시예 2에서의 측정 결과를 도시하는 그래프이다.

도 10은 실시예 3에서의 측정 결과를 도시하는 그래프이다.

도 2는 도 1에 도시한 반도체 장치의 제조 방법을 설명하기 위한 흐름도이다.

도 3은 본 발명에 따른 반도체 장치의 실시형태 2를 도시하는 단면 모식도이다.

도 4는 도 3에 도시한 반도체 장치의 제조 방법을 설명하기 위한 흐름도이다.

도 5는 실험을 위해 작성한 발명예의 시료를 도시하는 단면 모식도이다.

도 6은 도 5에 도시한 반도체 장치의 p+형층 및 p형층에서의 최외측 표면으로부터의 깊이 방향에서의 도전성 불순물의 농도 분포를 도시하는 그래프이다.

도 7은 본 발명의 발명예의 시료에 대한 역방향 전류 전압 특성을 도시하는 그래프이다.

도 8은 비교예 1의 시료에 대한 역방향 전류 전압 특성을 도시하는 그래프이다.

도 9는 실시예 2에서의 측정 결과를 도시하는 그래프이다.

도 10은 실시예 3에서의 측정 결과를 도시하는 그래프이다.

이하, 도면에 기초하여 본 발명의 실시형태를 설명한다. 또, 이하의 도면에서 동일 또는 상당하는 부분에는 동일한 참조 번호를 붙이고 그 설명은 반복하지 않는다.

(실시형태 1)

도 1을 참조하여, 본 발명의 반도체 장치의 실시형태 1을 설명한다.

도 1을 참조하면, 본 발명에 따른 반도체 장치(1)는, 탄화규소 반도체 장치의 일례인 종형 DiMOSFET(Double Implanted MOSFET)로서, 기판(2), 버퍼층(21), 내압 유지층(22), p 영역(23), n+ 영역(24), p+ 영역(25), 산화막(26), 소스 전극(11) 및 상부 소스 전극(27), 게이트 전극(10) 및 기판(2)의 이면측에 형성된 드레인 전극(12)을 구비한다. 구체적으로는, 도전형이 n형인 탄화규소(SiC)로 이루어지는 기판(2)의 표면 상에, 탄화규소로 이루어지는 버퍼층(21)이 형성된다. 이 버퍼층(21)은 도전형이 n형이고, 그 두께는 예컨대 0.5 ㎛이며, 불순물 농도는 예컨대 5×1017 ㎝-3이다. 또한, 이 버퍼층(21) 상에는 내압 유지층(22)이 형성된다. 이 내압 유지층(22)은 도전형이 n형인 탄화규소로 이루어지고, 예컨대 그 두께는 예컨대 10 ㎛이다. 또한, 내압 유지층(22)에서의 n형의 도전성 불순물의 농도로서는, 예컨대 5×1015 ㎝-3의 값을 이용할 수 있다. 또, 전술한 버퍼층(21)을 형성하지 않고, 기판(2) 상에 직접 내압 유지층(22)을 형성할 수도 있다.

이 내압 유지층(22)의 표면에는, 도전형이 p형인 p 영역(23)이 서로 간격을 두고 형성된다. p 영역(23)에서의 p형의 도전성 불순물의 농도로서는, 예컨대 1×1017 ㎝-3의 값을 이용할 수 있다. p 영역(23)의 내부에 있어서는, p 영역(23)의 표면층에 n+ 영역(24)이 형성된다. n+ 영역(24)에서의 n형의 도전성 불순물의 농도로서는, 예컨대 1×1019 ㎝-3의 값을 이용할 수 있다. 또한, 이 n+ 영역(24)에 인접하는 위치에는, p+ 영역(25)이 형성된다. 이 p+ 영역(25)에서의 p형의 도전성 불순물의 농도로서는, 예컨대 1×1020 ㎝-3의 값을 이용할 수 있다. 한쪽의 p 영역(23)에서의 n+ 영역(24) 상으로부터, p 영역(23), 2개의 p 영역(23) 사이에서 노출되는 내압 유지층(22), 다른쪽의 p 영역(23) 및 그 다른쪽의 p 영역(23)에서의 n+ 영역(24) 상에까지 연장되도록, 산화막(26)이 형성된다. 산화막(26) 상에는 게이트 전극(10)이 형성된다. 또한, n+ 영역(24) 및 p+ 영역(25) 상에는 소스 전극(11)이 형성된다. 이 소스 전극(11) 상에는 상부 소스 전극(27)이 형성된다. 그리고, 기판(2)에 있어서, 버퍼층(21)이 형성된 측의 표면과는 반대측의 이면에, 드레인 전극(12)이 형성된다.

여기서, 전술한 반도체 장치(1)는 기판(2)과 불순물층으로서의 p+ 영역(25)을 구비한다. 기판(2)은 탄화규소로 이루어지고, 전위 밀도가 5×103 ㎝-2 이하이며, 도전형은 제1 도전형(n형)이다. p+ 영역(25)은 기판 상에 형성되고, 상기 제1 도전형과는 상이한 제2 도전형의 도전성 불순물 농도가 1×1020 ㎝-3 이상 5×1021 ㎝-3 이하이다.

이렇게 하면, p+ 영역(25)에 접촉하도록 오믹 전극인 소스 전극(11)을 형성한 경우에, 상기 소스 전극(11)과 p+ 영역(25)의 접촉 저항을 실용상 문제없을 정도로 낮게 할 수 있다. 또한, 전위 밀도가 전술한 바와 같은 값으로 저감된 기판(2)을 이용함으로써, 기판(2)이나 상기 기판 상에 형성되는 에피택셜층 등에 있어서 누설 경로가 될 수 있는 결함의 밀도를 충분히 저감시킬 수 있다. 이 때문에, 반도체 장치(1)의 내압 특성을 양호하게 할 수 있다.

또, 기판(2)의 전위 밀도는 기판(2)의 표면을 KOH 등의 약액을 이용하여 에칭해서, 그 에칭에 의해 형성되는 에치 피트수를 계측함으로써 측정할 수 있다. 또한, p+ 영역(25)에서의 도전성 불순물 농도는, 예컨대 SIMS(Secondary Ionization Mass Spectrometer) 등을 이용하여 측정할 수 있다.

다음으로, 도 1에 도시한 반도체 장치(1)의 동작에 대해 설명한다. 도 1을 참조하면, 게이트 전극(10)에 임계값 이하의 전압을 부여한 상태, 즉 오프 상태에서는, 게이트 절연막으로서의 산화막(26) 바로 아래에 위치하는 p 영역(23)과 도전형이 n형인 내압 유지층(22) 사이가 역바이어스가 되어, 비도통 상태가 된다. 한편, 게이트 전극(10)에 플러스 전압을 인가하게 되면, p 영역(23)의 산화막(26)과 접촉하는 부근인 채널 영역에서, 반전층이 형성된다. 그 결과, n+ 영역(24)과 내압 유지층(22)이 전기적으로 접속되어, 소스 전극(11)과 드레인 전극(12) 사이에 전류가 흐른다.

다음으로, 도 1에 도시한 반도체 장치(1)의 제조 방법을 설명한다. 도 2를 참조하여, 본 발명에 따른 반도체 장치의 실시형태 1의 제조 방법을 설명한다.

먼저, 도 2에 나타내는 바와 같이, 기판 준비 공정(S10)을 실시한다. 이 공정에서는, 구체적으로는 (0001)면의 <11-20> 방향에서의 오프 각도가 8도인 탄화규소 기판을 준비한다. 그 탄화규소 기판의 도전형은 n형이다. 이러한 기판(2)(도 1 참조)은, 예컨대 (0001)면을 주표면으로 하는 SiC 잉곳으로부터 전술한 오프각이 되도록 기판을 잘라내는 방법에 의해 얻을 수 있다.

다음으로, 버퍼층 형성 공정(S20)을 실시한다. 구체적으로는, 버퍼층으로서 도전형이 n형인 탄화규소로 이루어지는 에피택셜층을 형성한다. 또, 이 버퍼층 형성 공정(S20)을 실시하지 않고, 상기 공정(S10)에 이어서 후술하는 에피택셜층 형성 공정(S30)을 실시해도 된다.

다음으로 에피택셜층 형성 공정(S30)을 실시한다. 구체적으로는, 버퍼층(21) 상에 내압 유지층(22)을 형성한다. 이 내압 유지층(22)으로서는, 도전형이 n형인 탄화규소로 이루어지는 층을 에피택셜 성장법에 의해 형성한다. 이 에피택셜층 형성 공정(S30)에서는, 원료 가스로서 예컨대 SiH4 가스 및 C3H8 가스를 이용할 수 있다.

다음으로, 주입 공정(S40)을 실시한다. 구체적으로는, 포토리소그래피 및 에칭을 이용해서 형성한 산화막을 마스크로서 이용하여, 도전형이 p형인 불순물을 내압 유지층(22)에 주입한다. 이렇게 하여, p 영역(23)(도 1 참조)을 형성한다. 또한, 전술한 주입 공정에서 이용한 산화막을 제거한 후, 재차 새로운 패턴을 갖는 산화막을, 포토리소그래피 및 에칭을 이용하여 형성한다. 그리고, 그 산화막을 마스크로서 이용하여, n형의 도전성 불순물을 정해진 영역에 주입함으로써, n+ 영역(24)(도 1 참조)을 형성한다. 또한, 동일한 방법에 의해, 도전형이 p형인 도전성 불순물을 주입함으로써, p+ 영역(25)을 형성한다.

전술한 바와 같은 주입 공정(S40) 후에, 활성화 열처리를 실시한다. 이 활성화 열처리의 처리 조건으로서는, 예컨대 아르곤 가스를 분위기 가스로서 이용하고, 가열 온도를 1700℃, 가열 시간을 30분으로 한 조건을 이용할 수 있다.

다음으로, 도 2에 나타내는 바와 같이 게이트 절연막 형성 공정(S50)을 실시한다. 구체적으로는, 내압 유지층(22), p 영역(23), n+ 영역(24), p+ 영역(25) 위를 덮도록 산화막(26)(도 1 참조)이 되어야 할 산화막을 형성한다. 이 게이트 절연막이 되어야 할 산화막을 형성하는 방법으로서는, 예컨대 드라이 산화(열산화)를 실시해도 된다. 이 드라이 산화의 조건으로서는, 예컨대 산소 함유 분위기 내에서 가열 온도를 1200℃, 가열 시간을 30분이라고 하는 조건을 이용할 수 있다.

다음으로, 전극 형성 공정(S60)을 실시한다. 구체적으로는, 상기 산화막 상에 포토리소그래피를 이용하여 패턴을 갖는 레지스트막을 형성한다. 그 레지스트막을 마스크로서 이용하여, n+ 영역(24) 및 p+ 영역(25) 상에 위치하는 산화막의 부분을 에칭에 의해 제거한다. 이 후, 레지스트막 위에, 그리고 그 산화막에 형성된 개구부 내부에 있어서 n+ 영역(24) 및 p+ 영역(25)과 접촉하도록 금속 등으로 이루어지는 도전체막을 형성한다. 그 후, 레지스트막을 제거함으로써, 그 레지스트막 상에 위치해 있던 도전체막을 제거(리프트오프)한다.

여기서, 도전체막의 재료로서는, 예컨대 니켈(Ni)을 이용할 수 있다. 또한, 그 재료로서, 티탄(Ti), 알루미늄(Al) 및 이들 금속에 실리콘(Si)을 함유한 재료를 이용해도 된다. 이 결과, 도 1에 도시하는 바와 같이, 소스 전극(11)을 얻을 수 있다. 또한, 기판(2)의 이면 상에 드레인 전극(12)(도 1 참조)을 형성한다. 또, 여기서 얼로이화를 위한 열처리를 실시하는 것이 바람직하다. 구체적으로는, 예컨대 분위기 가스로서 비활성 가스인 아르곤(Ar)을 이용해서 가열 온도를 950℃, 가열 시간을 2분으로 하는 열처리(얼로이화 처리)를 실시해도 된다.

그 후, 소스 전극(11) 상에 상부 소스 전극(27)(도 1 참조)을 형성한다. 또한, 이때 한쪽의 n+ 영역(24) 상으로부터 다른쪽의 n+ 영역(24) 상까지 연장되도록, 산화막(26) 상에 게이트 전극(10)을 형성한다. 이렇게 하여, 도 1에 도시하는 반도체 장치를 얻을 수 있다.

(실시형태 2)

도 3을 참조하여, 본 발명에 따른 반도체 장치의 실시형태 2를 설명한다.

도 3을 참조하면, 본 발명에 따른 반도체 장치(1)는 탄화규소 반도체 장치의 일례인 횡형 구조의 JFET로서, 탄화규소(SiC)로 이루어지고, 도전형이 n형인 기판(2)과, 제1 p형층(32)과, n형층(33)과, 제2 p형층(34)과, 소스 영역(35)과, 게이트 영역(36)과, 드레인 영역(37)과, 산화막(38)과, 콘택트 전극(39)과, 상부 소스 전극(27)과, 상부 게이트 전극(28)과, 상부 드레인 전극(29)과, 전위 유지 영역(43)을 구비한다. 제1 p형층(32)은 기판(2)의 상부 표면 상에 형성된다. 제1 p형층(32)의 두께는 예컨대 10 ㎛로 할 수 있다. 또한, 제1 p형층(32)에서의 p형의 도전성 불순물의 농도는 예컨대 1×1016 ㎝-3로 할 수 있다. n형층(33)은 제1 p형층(32) 상에 형성된다. n형층(33)의 두께는 예컨대 0.4 ㎛로 할 수 있다. 또한, n형층(33)에서의 n형의 도전성 불순물의 농도는 예컨대 2×1017 ㎝-3로 할 수 있다. 제2 p형층(34)은 n형층(33) 상에 형성된다. 제2 p형층(34)의 두께는 예컨대 0.3 ㎛로 할 수 있다. 또한, 제2 p형층(34)에서의 p형의 도전성 불순물의 농도는 예컨대 2×1017 ㎝-3로 할 수 있다. 전술한 p형층 및 n형층은 각각 도전형이 p형 및 n형인 탄화규소로 이루어진다.

제2 p형층(34) 및 n형층(33)에는, n형층(33)보다 고농도의 도전형이 n형인 불순물(n형 불순물)을 포함하는 소스 영역(35) 및 드레인 영역(37)이 형성된다. 또한, 제2 p형층(34) 및 n형층(33)에는, 전술한 소스 영역(35) 및 드레인 영역(37) 사이에 끼워지도록, 제1 p형층(32) 및 제2 p형층(34)보다 고농도의 도전형이 p형인 불순물(p형 불순물)을 포함하는 게이트 영역(36)이 형성된다. 이와 같이, 소스 영역(35), 게이트 영역(36) 및 드레인 영역(37)은, 각각 제2 p형층(34)을 관통하여 n형층(33)에까지 도달하도록 형성된다. 또한, 소스 영역(35), 게이트 영역(36) 및 드레인 영역(37)의 바닥부는, 제1 p형층(32)의 상부 표면[제1 p형층(32)과 n형층(33)의 경계부]으로부터 간격을 두고 배치된다.

또한, 소스 영역(35)에서 보아 게이트 영역(36)과는 반대측에는, 제2 p형층(34)의 상부 표면(34A)[n형층(33)에 면하는 표면과는 반대측의 주요면]으로부터 제2 p형층(34)을 관통하여 n형층(33)에까지 도달하도록 홈부(41)가 형성된다. 홈부(41)의 바닥벽은 제1 p형층(32)과 n형층(33)의 계면으로부터 간격을 두고, n형층(33)의 내부에 배치된다. 또한, 홈부(41)의 바닥벽으로부터 n형층(33)을 관통하여, 제1 p형층(32)에 이르도록, 제1 p형층(32) 및 제2 p형층(34)보다 고농도의 p형 불순물을 포함하는 전위 유지 영역(43)이 형성된다. 이 전위 유지 영역(43)의 바닥부는 n형인 기판(2)의 상부 표면[기판(2)과 제1 p형층(32)의 경계부]으로부터 간격을 두고 배치된다.

소스 영역(35), 게이트 영역(36), 드레인 영역(37), 및 전위 유지 영역(43)의 각각의 상부 표면에 접촉하도록, 콘택트 전극(39)이 형성된다. 콘택트 전극(39)은 소스 영역(35), 게이트 영역(36), 드레인 영역(37) 및 전위 유지 영역(43)과 오믹 접촉 가능한 재료로 이루어진다. 콘택트 전극(39)의 재료로서, 예컨대 Ni를 이용할 수 있다. 또한, 콘택트 전극(39)은 Ti, Al, 또는 이들 금속의 실리사이드(silicide)로 구성될 수도 있다.

인접하는 콘택트 전극(39) 사이에는, 산화막(38)이 형성된다. 즉, 절연층으로서의 산화막(38)은 제2 p형층(34)의 상부 표면, 홈부(41)의 바닥벽 및 측벽에 있어서, 콘택트 전극(39)이 형성되어 있는 영역 이외의 영역 전체를 덮도록 형성된다. 이 결과, 인접하는 콘택트 전극(39)들 사이는 절연 상태가 된다.

소스 영역(35), 게이트 영역(36) 및 드레인 영역(37) 상에 위치하는 콘택트 전극(39)의 상부 표면 상에 접촉하도록, 각각 상부 소스 전극(27), 상부 게이트 전극(28), 상부 드레인 전극(29)이 형성된다. 이 결과, 상부 소스 전극(27), 상부 게이트 전극(28), 상부 드레인 전극(29)은, 콘택트 전극(39)을 통해, 각각 소스 영역(35), 게이트 영역(36) 및 드레인 영역(37)과 전기적으로 접속된다. 또한, 상부 소스 전극(27)은 소스 영역(35) 상의 콘택트 전극(39)의 상부 표면 상으로부터, 전위 유지 영역(43) 상의 콘택트 전극(39)의 상부 표면 상에까지 연장되도록 형성된다. 이 결과, 전위 유지 영역(43) 상의 콘택트 전극(39)은 소스 영역(35) 상의 콘택트 전극(39)과 동전위로 유지된다. 상부 소스 전극(27), 상부 게이트 전극(28), 상부 드레인 전극(29)은, 예컨대 Al 등의 도전체에 의해 구성된다.

도 3에 도시한 반도체 장치(1)는 기판(2)과 불순물층으로서의 게이트 영역(36)을 구비한다. 기판(2)은 탄화규소로 이루어지고, 전위 밀도가 5×103 ㎝-2 이하이며, 도전형은 제1 도전형(n형)이다. 불순물층인 게이트 영역(36)은 기판(2) 상에 형성되고, n형과는 상이한 제2 도전형(p형)의 도전성 불순물 농도가 1×1020 ㎝-3 이상 5×1021 ㎝-3 이하이다.

이렇게 하면, 실시형태 1에 나타낸 반도체 장치(1)와 마찬가지로, 불순물층인 게이트 영역(36)에 접촉하도록 오믹 전극인 콘택트 전극(39)을 형성한 경우에, 그 콘택트 전극(39)과 게이트 영역(36)의 접촉 저항을 실용상 문제없을 정도로 낮게 할 수 있다. 또한, 전위 밀도가 전술한 바와 같은 값으로 저감된 기판(2)을 이용함으로써, 기판(2)이나 그 기판 상에 형성되는 에피택셜층[제1 p형층(32), n형층(33), 제2 p형층(34)]에 있어서 누설 경로가 될 수 있는 결함의 밀도를 충분히 저감시킬 수 있다. 이 때문에, 반도체 장치(1)의 내압 특성을 양호하게 할 수 있다.

다음으로, 반도체 장치(1)의 동작에 대해 간단히 설명한다. 도 3을 참조하면, 상부 게이트 전극(28)에 인가되는 전압이 0 V인 상태에서는, n형층(33)에 있어서 게이트 영역(36)과 드레인 영역(37) 사이에 끼워진 영역 및 그 끼워진 영역과 제1 p형층(32) 사이에 끼워진 영역(드리프트 영역), 및 게이트 영역(36)과 제1 p형층(32) 사이에 끼워진 영역(채널 영역)은 공핍화되지 않는다. 이 때문에, 소스 영역(35)과 드레인 영역(37)은 n형층(33)을 통해 전기적으로 접속된 상태가 된다. 이에, 소스 영역(35)으로부터 드레인 영역(37)을 향해 전자가 이동함으로써 전류가 흐른다.

한편, 상부 게이트 전극(28)에 마이너스 전압을 인가하게 되면, 전술한 채널 영역 및 드리프트 영역의 공핍화가 진행한다. 이 결과, 소스 영역(35)과 드레인 영역(37)은 전기적으로 차단된 상태가 된다. 이에, 소스 영역(35)으로부터 드레인 영역(37)을 향해 전자가 이동할 수 없어, 전류는 흐르지 않는다.

다음으로, 도 3에 도시한 반도체 장치의 제조 방법에 대해 설명한다. 도 4를 참조하여, 본 발명에 따른 반도체 장치의 실시형태 2의 제조 방법을 설명한다.

도 4에 나타내는 바와 같이, 도 3에 도시한 반도체 장치(1)의 제조 방법에 있어서는, 먼저 기판 준비 공정(S10)을 실시한다. 구체적으로는, 도 2에 나타낸 공정(S10)과 마찬가지로, 도전형이 n형이고 전위 밀도가 5×103 ㎝-2 이하인 탄화규소로 이루어지는 기판(2)을 준비한다.

다음으로, 도 4에 나타내는 바와 같이, 에피택셜층 형성 공정(S30)을 실시한다. 구체적으로는, 전술한 공정(S10)에서 준비된 기판(2)의 한쪽 주표면 상에 예컨대 기상 에피택셜 성장법을 이용하여 탄화규소로 이루어지는 제1 p형층(32), n형층(33), 및 제2 p형층(34)을 순차 형성한다. 기상 에피택셜 성장법에 있어서, 예컨대 재료 가스로서 실란(SiH4) 가스 및 프로판(C3H8) 가스를 이용할 수 있다. 또한, 이때 캐리어 가스로서는 예컨대 수소(H2) 가스를 이용할 수도 있다. 또한, p형층을 형성하기 위해, 도전형이 p형인 불순물을 도입하는 p형 불순물 소스로서는, 예컨대 디보란(B2H6)이나 트리메틸알루미늄(TMA)을 이용할 수 있다. 또한, n형층을 형성하기 위해 이용하는 n형 불순물 소스로서는, 예컨대 질소(N2) 가스를 이용할 수 있다.

다음으로 전술한 바와 같이 하여 형성한 제2 p형층(34) 및 n형층(33)에 홈부를 형성한다. 구체적으로는, 제2 p형층(34)의 상부 표면(34A)으로부터 제2 p형층(34)을 관통하여 n형층(33)에 도달하도록, 예컨대 드라이 에칭을 이용하여 홈부(41)를 형성한다. 이 홈부(41)의 형성 공정에서는, 예컨대 홈부(41)를 형성해야 할 위치에 개구부를 갖는 마스크층을 제2 p형층(34)의 상부 표면(34A) 상에 형성하고, 그 마스크층을 마스크로서 이용하여 SF6 가스를 이용한 드라이 에칭을 실시해도 된다.

다음으로, 도 4에 나타내는 바와 같이 주입 공정(S40)을 실시한다. 구체적으로는, 먼저 제1 이온 주입 공정으로서, 고농도의 n형 불순물을 포함하는 영역인 소스 영역(35) 및 드레인 영역(37)을 형성한다. 구체적으로는, 먼저 제2 p형층(34)의 상부 표면(34A) 위에 그리고 홈부(41)의 내벽에 레지스트를 도포한 후, 노광 및 현상 처리를 실시함으로써(포토리소그래피에 의해), 원하는 소스 영역(35) 및 드레인 영역(37)의 형상에 따른 영역에 개구를 갖는 레지스트막을 형성한다. 그리고, 이 레지스트막을 마스크로서 이용하여, 인(P) 또는 질소(N) 등의 n형 불순물이 이온 주입법에 의해 제2 p형층(34) 및 n형층(33)에 주입된다. 이에 따라, 소스 영역(35) 및 드레인 영역(37)이 형성된다.

다음으로, 주입 공정(S40)으로서, 제2 이온 주입 공정을 실시한다. 구체적으로는, 전술한 제1 이온 주입 공정과 마찬가지로, 원하는 게이트 영역(36) 및 전위 유지 영역(43)의 평면 형상에 따른 영역에 개구를 갖는 레지스트막이 포토리소그래피법을 이용하여 형성된다. 그리고, 이 레지스트막을 마스크로서 이용하여, 알루미늄(Al) 또는 붕소(B) 등의 p형 불순물이 이온 주입법에 의해 제2 p형층(34), n형층(33) 및 제1 p형층(32)의 정해진 영역에 도입된다. 이 결과, 게이트 영역(36) 및 전위 유지 영역(43)이 형성된다.

다음으로, 주입한 n형 불순물 또는 p형 불순물을 활성화하기 위한 활성화 어닐링 공정을 실시한다. 이 활성화 어닐링 공정에서는, 전술한 주입 공정(S40)에서 이용된 레지스트막을 제거한 후, 이온이 주입된 제2 p형층(34), n형층(33) 및 제1 p형층(32)을 가열한다. 이 결과, 전술한 이온 주입에 의해 도입된 불순물이 활성화된다. 상기 활성화 어닐링 처리로서는, 예컨대 아르곤 가스를 분위기로서 이용하고, 가열 온도를 1700℃ 정도로 하며, 유지 시간을 30분 정도로 하는 열처리를 실시해도 된다.

다음으로, 도 4에 나타내는 바와 같이, 절연막 형성 공정(S70)을 실시한다. 이 공정(S70)에서는, 전술한 공정을 실시함으로써 정해진 이온 주입층이 형성된 제2 p형층(34), n형층(33) 및 제1 p형층(32)이 형성된 기판(2)의 표면이 열산화된다. 이에 따라, 이산화규소(SiO2)로 이루어지는 산화막(38)이 제2 p형층(34)의 상부 표면(34A) 및 홈부(41)의 내벽을 덮도록 형성된다.

다음으로, 도 4에 나타내는 바와 같이 전극 형성 공정(S60)을 실시한다. 구체적으로는, 소스 영역(35), 게이트 영역(36), 드레인 영역(37) 및 전위 유지 영역(43)의 각각의 상부 표면에 접촉하도록, 콘택트 전극(39)을 형성한다. 콘택트 전극(39)의 형성 방법으로서는, 먼저 형성해야 할 콘택트 전극(39)의 평면 형상에 따른 영역에, 포토리소그래피법을 이용하여 개구 패턴을 갖는 레지스트막을 형성한다. 그리고, 이 레지스트막을 마스크로서 이용하여, 예컨대 반응성 이온 에칭(RIE)에 의해 소스 영역(35), 게이트 영역(36), 드레인 영역(37) 및 전위 유지 영역(43) 상의 산화막(38)을 부분적으로 제거한다. 그 후, 예컨대 니켈(Ni)을 증착함으로써, 산화막(38)이 부분적으로 제거됨으로써 형성된 개구부로부터 노출되는 소스 영역(35), 게이트 영역(36), 드레인 영역(37) 및 전위 유지 영역(43)의 상부 표면 및 레지스트막의 상부 표면 상에 도전층(니켈막)이 형성된다. 그 후, 레지스트막을 제거함으로써, 레지스트막 상의 도전체층이 제거(리프트오프)된다. 이 결과, 산화막(38)의 개구부로부터 노출된 소스 영역(35), 게이트 영역(36), 드레인 영역(37) 및 전위 유지 영역(43)의 상부 표면 상에 도전체층이 잔존한다. 그 후, 예컨대 1000℃ 정도로 가열하는 열처리 공정을 실시함으로써, 전술한 도전체층이 실리사이드화된다. 이 결과, 소스 영역(35), 게이트 영역(36), 드레인 영역(37) 및 전위 유지 영역(43)에 오믹 접촉 가능한 NiSi(니켈실리사이드)로 이루어지는 콘택트 전극(39)이 형성된다. 또, 콘택트 전극(39)을 구성하는 재료로서 Ti 또는 Al, 또는 이들의 실리사이드를 이용해도 된다.

그 후, 콘택트 전극(39) 상에 상부 소스 전극(27), 상부 게이트 전극(28) 및 상부 드레인 전극(29)을 형성한다. 구체적으로는, 산화막(38) 상에 상부 소스 전극(27), 상부 게이트 전극(28) 및 상부 드레인 전극(29)의 평면 형상과 동일한 개구 패턴을 갖는 레지스트막을 형성한다. 이 레지스트막의 개구 패턴의 내부에서는 콘택트 전극(39)이 노출된다. 그리고, 그 레지스트막의 상부 표면 및 개구 패턴의 내부에 알루미늄 등의 도전체막을 증착한다. 그 후, 레지스트막과 함께 레지스트막 상의 도전체막을 제거한다(리프트오프). 이 결과, 도 3에 도시하는 바와 같은 상부 소스 전극(27), 상부 게이트 전극(28) 및 상부 드레인 전극(29)을 형성할 수 있다. 이렇게 하여, 도 3에 도시하는 바와 같은 반도체 장치를 얻을 수 있다.

여기서, 전술한 실시형태 1, 2에 나타낸 반도체 장치의 바람직한 변형예를 설명한다.

상기 반도체 장치(1)에 있어서, 기판(2)의 전위 밀도는 1×103 ㎝-2 이하여도 된다. 이 경우, 반도체 장치(1)의 내압 특성을 더욱 향상시킬 수 있다.

상기 반도체 장치(1)에 있어서, 기판(2)의 나선 전위 밀도는 1 ㎝-2 이하여도 된다. 여기서, 기판(2)의 나선 전위는 내압 특성의 열화를 초래하기(애발란치 파괴 전압을 저하시키는 요인이 되기) 때문에, 특히 그 밀도를 저감하는 것이 유효하다. 여기서, 기판(2)의 나선 전위 밀도의 상한을 1 ㎝-2로 한 것은, 나선 전위 밀도가 이 값을 초과하면, 내압이 열화되는 경우가 있기 때문이다.

상기 반도체 장치(1)에 있어서, 기판(2)의 나선 전위 밀도는 0.1 ㎝-2 이하여도 된다. 이 경우, 반도체 장치(1)의 내압 특성을 더욱 향상시킬 수 있다. 여기서, 기판(2)의 나선 전위 밀도의 보다 바람직한 상한을 0.1 ㎝-2로 한 것은, 이렇게 하면 확실하게 내압 향상을 실현할 수 있기 때문이다.

상기 반도체 장치(1)에서는, 불순물층으로서의 p+ 영역(25) 또는 게이트 영역(36)에서의 제2 도전형(p형)의 도전성 불순물 농도가 4×1020 ㎝-3 이상 5×1021 ㎝-3 이하여도 된다. 이 경우, 불순물층에 접촉하도록 오믹 전극으로서의 소스 전극(11) 또는 콘택트 전극(39)을 형성했을 때에, 그 소스 전극(11)과 p+ 영역(25) 사이, 또는 콘택트 전극(39)과 게이트 영역(36) 사이의 접촉 저항을 더욱 저감시킬 수 있다. 여기서, 도전성 불순물 농도의 보다 바람직한 하한을 4×1020 ㎝-3로 한 것은, 접촉 저항을 보다 저감할 수 있기 때문이라는 이유에 따른다. 또한, 도전성 불순물 농도의 보다 바람직한 상한을 5×1021 ㎝-3로 한 것은, 이 이상 도전성 불순물을 도입하면, 불순물층의 결정성이 저하되어, 탄화규소 반도체 장치의 특성이 열화되기 때문이다.

상기 반도체 장치(1)에 있어서, 불순물층[p+ 영역(25)]에 접촉하도록 형성되는 오믹 전극[소스 전극(11)]과, 기판(2)에 접촉하도록 형성되는 다른 오믹 전극[드레인 전극(12)]을 구비하여도 된다. 소스 전극(11)과 드레인 전극(12)은 동일한 재료로 구성되어도 된다. 이 경우, 상기 소스 전극(11)과 드레인 전극(12)을 동일한 재료를 이용하여 형성할 수 있기 때문에, 그 소스 전극(11) 및 드레인 전극(12)을 동시 또는 연속하여 형성할 수 있다. 이 때문에, 소스 전극(11) 및 드레인 전극(12)을 서로 상이한 재료로 구성하는 경우보다, 반도체 장치(1)의 제조 프로세스를 간략화할 수 있다.

상기 반도체 장치(1)에 있어서, 소스 전극(11) 및 드레인 전극(12)을 구성하는 재료는 니켈(Ni)을 포함하여도 된다. 이 경우, 서로 도전형이 상이한 불순물층[p+ 영역(25)]과 기판(2)에 각각 접촉하는 소스 전극(11) 및 드레인 전극(12)을, 니켈을 포함하는 재료로 형성함으로써, 동일한 재료를 이용하여, 불순물층[p+ 영역(25)]과 기판(2)의 양쪽에 대해 오믹 접촉한 전극[소스 전극(11) 및 드레인 전극(12)]을 형성할 수 있다.

상기 반도체 장치(1)에 있어서, 소스 전극(11) 및 드레인 전극(12)을 구성하는 재료는 티탄(Ti)과 알루미늄(Al)을 포함하여도 된다. 또한, 상기 반도체 장치(1)에 있어서, 소스 전극(11) 및 드레인 전극(12)을 구성하는 재료는 티탄과 알루미늄에 더하여 실리콘(Si)을 포함하여도 된다. 이 경우, 동일한 재료를 이용하여, 서로 도전형이 상이한 불순물층[p+ 영역(25)]과 기판(2)에 각각 오믹 접촉하는 전극[소스 전극(11) 및 드레인 전극(12)]을 형성할 수 있다.

상기 반도체 장치(1)에 있어서, 상기 소스 전극(11) 및 드레인 전극(12), 또는 콘택트 전극(39)을 구성하는 재료는 티탄, 알루미늄, 실리콘의 적층 구조를 이용해도 된다. 이 경우, 예컨대 티탄의 두께를 0 ㎚ 이상 40 ㎚ 이하, 알루미늄의 두께를 20 ㎚ 이상 100 ㎚ 이하, 실리콘의 두께를 10 ㎚ 이상 50 ㎚ 이하로 할 수 있다. 보다 바람직하게는, 티탄의 두께를 5 ㎚ 이상 30 ㎚ 이하, 알루미늄의 두께를 30 ㎚ 이상 70 ㎚ 이하, 실리콘의 두께를 15 ㎚ 이상 35 ㎚ 이하로 할 수 있다.

(실시예 1)

본 발명의 효과를 확인하기 위해, 이하와 같은 실험을 하였다.

(시료)

발명예의 시료:

도 5는 실험을 위해 작성한 발명예의 시료를 도시하는 단면 모식도이다. 도 5를 참조하여, 실시예에서 제작한 발명예의 시료의 구조를 설명한다.

도 5에 도시하는 바와 같이, 발명예의 시료인 소자에서는, 기판(2)의 주표면 상에 버퍼층(21)을 형성한다. 이 버퍼층(21) 상에는 n-형층(52)이 형성된다. 이 n-형층(52) 상에는 p형층(53)이 형성된다. p형층(53) 상에는 p+형층(54)이 형성된다. 이 p+형층(54)의 상부 표면 상에는 오믹 전극(55)이 형성된다. 오믹 전극(55)의 상부 표면 상에는 알루미늄으로 이루어지는 전극(56)이 형성된다. 그리고, 오믹 전극(55)의 단부면으로부터 기판(2)의 상부 표면에까지 도달하도록, 소자의 측면 상에는 산화막으로 이루어지는 절연막(57)이 형성된다. 또한, 기판(2)의 이면[버퍼층(51)이 형성된 측의 표면과는 반대측의 이면]에는 이면 전극(58)이 형성된다.

기판(2)으로서는, 탄화규소로 이루어지고, (0001)면의 <11-20> 방향에서의 오프 각도가 8도로 된 기판을 준비하였다. 기판(2)의 전위 밀도는 1×103 ㎝-2였다. 또한, 버퍼층(21)에서의 n형의 도전성 불순물의 농도는 5×1017 ㎝-3이다. n형의 도전성 불순물로서는 질소를 이용하였다. 또한, 버퍼층(21)의 두께는 0.5 ㎛로 하였다.

또한, n-형층(52)에서의 도전형이 n형인 도전성 불순물의 농도는 5×1015 ㎝-3로 하고, 그 두께는 2.2 ㎛로 하였다. 또, n-형층(52)에서의 도전형이 n형인 도전성 불순물로서는 전술한 버퍼층(21)과 동일한 원소를 이용하였다. 또한, p형층(53) 및 p+형층(54)에서의 도전성 불순물의 농도 프로파일은 도 6에 도시하는 바와 같다.

도 6을 참조하면, 가로축은 p+형층(54)의 상부 표면으로부터 기판(2)을 향하는 방향에서의 깊이(단위: ㎛)를 나타내고, 세로축은 p형을 나타내는 도전성 불순물의 농도를 나타낸다. 도 6으로부터도 알 수 있듯이, p+형층(54)의 두께는 약 0.1 ㎛ 정도이고, 그 도전성 불순물 농도는 대략 3×1020 ㎝-3 정도이다. 또한, p형층(53)은 그 두께가 대략 0.8 ㎛ 정도이고, 도 6에 도시하는 바와 같은 도전성 불순물의 농도 분포를 갖는다. 또한, 도 5에 도시한 반도체 장치의 평면 형상은 원형 형상이며 직경이 500 ㎛이다.

비교예의 시료:

비교예의 시료로서, 구조는 동일하지만, 기판(2)에서의 전위 밀도가 1×104 ㎝-2인 기판을 이용하였다. 그리고, 다른 구조는 도 5에 도시한 발명예의 시료와 동일한 구조로 하였다.

비교예 2의 시료:

비교예 2의 시료도, 도 5에 도시한 반도체 장치와 동일한 구조를 구비하지만, 기판(2)에서의 전위 밀도와 p+형층(54)에서의 도전성 불순물의 농도가 발명예의 시료와는 상이하다. 구체적으로는, 비교예 2의 반도체 장치를 구성하는 기판(2)에서의 전위 밀도는 1×104 ㎝-2로 하였다. 또한, p+형층(54)에서의 도전성 불순물의 농도를 5×1019 ㎝-3로 하였다.

(측정)

전술한 발명예 및 비교예 1, 2의 시료에 대해, 오믹 전극(55)과 p+형층(54)의 접촉 저항 및 형성한 시료에서의 역방향의 전류 전압 특성을 측정하였다. 접촉 저항의 측정 방법으로서는, TLM(Transmission Line Model)법을 이용하였다. 또한, 역방향의 전류 전압 특성의 측정 방법으로서는, 커브트레이서에 의한 전류 전압 특성 측정이라고 하는 방법을 이용하였다.

(결과)

발명예의 측정 결과를 도 7에 도시한다. 도 7에서 세로축은 전류(㎂)를 나타내고, 가로축은 전압(V)을 나타낸다. 세로축의 1매스는 10 ㎂이고, 가로축의 1매스는 100 V를 나타낸다. 또, 도 7의 그래프에서는, 우측 위의 코너가 원점이다.

도 7로부터 알 수 있듯이, 발명예의 시료에서는 약 450 V 정도에서 애발란치 파괴를 나타내었다. 이 데이터는 그 시료가 거의 이상(理想) 내압을 나타낸 것을 의미한다. 또한, 발명예의 시료에서의 오믹 전극(55)과 p+형층(54)과의 접촉 저항은 2×10-3 Ω㎝-2였다.

다음으로, 비교예 1의 측정 결과를 도 8에 도시한다. 도 8의 그래프에서의 세로축 및 가로축은 도 7에 도시한 그래프와 동일하다. 단, 도 8의 가로축에서는, 1매스가 10 V를 나타낸다. 도 8로부터도 알 수 있듯이, 비교예 1의 시료에서는 비교적 낮은 전압(거의 25 V 정도)으로부터 누설 전류가 검출되었다. 또한, 오믹 전극(55)의 접촉 저항은 2×10-3 Ω㎝-2였다. 이 오믹 전극의 접촉 저항 자체는 전술한 발명예의 시료에서의 오믹 전극의 접촉 저항과 거의 동등하였다.

비교예 2의 시료에 대해서는, 역방향에서의 전류 전압 특성은 비교예 1의 시료와 동일하고, 비교적 낮은 전압으로부터 누설 전류가 검출되었다. 또한, 비교예 2의 시료에서는, 오믹 전극의 접촉 저항은 2×10-2 Ω㎝-2로, 실시예 2나 비교예 1의 시료보다 큰 접촉 저항을 나타내었다.

(실시예 2)

본 발명에서의 기판의 전위 밀도와 내압의 관계를 확인하기 위해, 이하와 같은 실험을 하였다.

(시료)

측정용의 시료로서, 실시예 1과 마찬가지로 도 5에 도시한 구조의 시료를 준비하였다. 또, 여기서는 전위 밀도가 상이한 기판(2)(전위 밀도가 1×103 ㎝-2∼1×105 ㎝-2에 분포하는 8종류의 기판)을 이용하여 시료를 작성하였다. 또, 각 시료 모두 p+형층(54)에서의 도전성 불순물의 농도를 4×1020 ㎝-3로 하였다. 다른 구조는 실시예 1에서의 시료와 동일하다.

(측정)

실시예 1과 동일한 방법에 의해, 각 시료에 대해 역방향의 전류 전압 특성을 측정하였다. 그리고, 흐른 전류(누설 전류)가 10 ㎂를 초과했을 때의 전압을 내압이라고 정의하고, 각 시료에 대해 내압의 값을 결정하였다.

(결과)

측정 결과를 도 9에 도시한다. 도 9를 참조하면, 가로축은 각 시료의 기판의 전위 밀도(단위: ㎝-2)를 나타내고, 세로축은 내압(단위: V)을 나타낸다. 도 9로부터 알 수 있듯이, 기판의 전위 밀도가 5×103 ㎝-2 정도 이하이면 충분히 높은 내압을 나타내나, 전위 밀도가 1×104 ㎝-2를 초과하면 내압이 50 V 이하로 매우 낮아지는 것을 알 수 있다. 이 때문에, 기판의 전위 밀도는 5×103 ㎝-2로 하면 되는 것을 알 수 있다.

(실시예 3)

본 발명에 있어서, 오믹 전극이 접촉하도록 형성되는 불순물층의 도전성 불순물 농도와 오믹 전극의 접촉 저항의 관계를 확인하기 위해, 이하와 같은 실험을 하였다.

(시료)

측정용의 시료로서, 실시예 1의 발명예와 마찬가지로 도 5에 도시한 구조의 시료를 준비하였다. 또, 여기서는 본 발명의 불순물층에 대응하는 p+형층(54)의 불순물 농도를 변경한 시료[p+형층(54)의 불순물 농도가 1×1019 ㎝-3∼5×1020 ㎝-3에 분포하는 5종류의 시료]를 작성하였다. 또, 다른 구조는 실시예 1에서의 발명예의 시료와 동일하다.

(측정)

실시예 1과 동일한 방법에 의해, 각 시료에 대해 오믹 전극(55)과 p+형층(54)의 접촉 저항을 측정하였다.

(결과)

측정 결과를 도 10에 도시한다. 도 10을 참조하면, 가로축은 각 시료의 p+형층의 불순물 농도(단위: ㎝-3)를 나타내고, 세로축은 접촉 저항(접촉 저항률이라고도 말함)(단위: Ω㎝-2)을 나타낸다.

도 10으로부터 알 수 있듯이, p+형층(54)의 불순물 농도가 높아지면 접촉 저항이 저감하는 것을 알 수 있다. 그리고, 접촉 저항의 허용 최대값을 1×10-2 Ω㎝-2로 규정하면, p+형층(54)의 불순물 농도를 1×1020 ㎝-3 이상으로 함으로써, 접촉 저항을 허용 범위에 들어가게 하는(충분히 낮은 값으로 하는) 것이 가능한 것을 알 수 있다.

이번에 개시된 실시형태 및 실시예는 모든 점에서 예시이며 제한적인 것은 아니라고 생각되어야 한다. 본 발명의 범위는 상기한 설명이 아니라 특허청구범위에 의해 나타나며, 특허청구범위와 균등한 의미 및 범위 내에서의 모든 변경이 포함되는 것이 의도된다.

본 발명은 오믹 전극을 구비하는 탄화규소 반도체 장치에 적용될 수 있고, 특히 DiMOSFET나 JFET 등에 유리하게 적용된다.

1: 반도체 장치 2: 기판

10: 게이트 전극 11: 소스 전극

12: 드레인 전극 21, 51: 버퍼층

22: 내압 유지층 23: p 영역

24: n+ 영역 25: p+ 영역

26, 38: 산화막 27: 상부 소스 전극

28: 상부 게이트 전극 29: 상부 드레인 전극

32: 제1 p형층 33: n형층

34: 제2 p형층 34A: 상부 표면

35: 소스 영역 36: 게이트 영역

37: 드레인 영역 39: 콘택트 전극

41: 홈부 43: 전위 유지 영역

52: n-형층 53: p형층

54: p+형층 55: 오믹 전극

56: 전극 57: 절연막

58: 이면 전극

10: 게이트 전극 11: 소스 전극

12: 드레인 전극 21, 51: 버퍼층

22: 내압 유지층 23: p 영역

24: n+ 영역 25: p+ 영역

26, 38: 산화막 27: 상부 소스 전극

28: 상부 게이트 전극 29: 상부 드레인 전극

32: 제1 p형층 33: n형층

34: 제2 p형층 34A: 상부 표면

35: 소스 영역 36: 게이트 영역

37: 드레인 영역 39: 콘택트 전극

41: 홈부 43: 전위 유지 영역

52: n-형층 53: p형층

54: p+형층 55: 오믹 전극

56: 전극 57: 절연막

58: 이면 전극

Claims (8)

- 탄화규소로 이루어지고, 전위 밀도가 5×103 ㎝-2 이하인 제1 도전형의 기판(2)과,

상기 기판(2) 상에 형성되고, 상기 제1 도전형과는 상이한 제2 도전형의 도전성 불순물 농도가 1×1020 ㎝-3 이상 5×1021 ㎝-3 이하인 불순물층(25, 36, 54)

을 구비하는 탄화규소 반도체 장치(1). - 제1항에 있어서, 상기 기판(2)의 전위 밀도는 1×103 ㎝-2 이하인 것인 탄화규소 반도체 장치(1).

- 제1항에 있어서, 상기 기판(2)의 나선 전위 밀도는 1 ㎝-2 이하인 것인 탄화규소 반도체 장치(1).

- 제3항에 있어서, 상기 기판(2)의 나선 전위 밀도는 0.1 ㎝-2 이하인 것인 탄화규소 반도체 장치(1).

- 제1항에 있어서, 상기 불순물층(25, 36, 54)에서의 상기 제2 도전형의 도전성 불순물 농도는 4×1020 ㎝-3 이상 5×1021 ㎝-3 이하인 것인 탄화규소 반도체 장치(1).

- 제1항에 있어서, 상기 불순물층(25, 36, 54)에 접촉하도록 형성되는 오믹 전극(11, 55)과,

상기 기판(2)에 접촉하도록 형성되는 다른 오믹 전극(12, 58)을 구비하고,

상기 오믹 전극(11, 55)과 상기 다른 오믹 전극(12, 58)은 동일한 재료에 의해 구성되는 것인 탄화규소 반도체 장치(1). - 제6항에 있어서, 상기 오믹 전극(11, 55)과 상기 다른 오믹 전극(12, 58)을 구성하는 재료는 니켈을 포함하는 것인 탄화규소 반도체 장치(1).

- 제6항에 있어서, 상기 오믹 전극(11, 55)과 상기 다른 오믹 전극(12, 58)을 구성하는 재료는 티탄과 알루미늄을 포함하는 것인 탄화규소 반도체 장치(1).

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008257280A JP2010087397A (ja) | 2008-10-02 | 2008-10-02 | 炭化珪素半導体装置 |

| JPJP-P-2008-257280 | 2008-10-02 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20110061641A true KR20110061641A (ko) | 2011-06-09 |

Family

ID=42073324

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020117009510A KR20110061641A (ko) | 2008-10-02 | 2009-08-07 | 탄화규소 반도체 장치 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US20110175111A1 (ko) |

| EP (1) | EP2348530B1 (ko) |

| JP (1) | JP2010087397A (ko) |

| KR (1) | KR20110061641A (ko) |

| CN (1) | CN102171827A (ko) |

| CA (1) | CA2739410A1 (ko) |

| TW (1) | TW201025594A (ko) |

| WO (1) | WO2010038547A1 (ko) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101411490B1 (ko) * | 2013-01-23 | 2014-06-24 | 박종진 | 플라즈마 차폐 기능을 가진 도어 플레이트 |

| US9431246B2 (en) | 2012-12-27 | 2016-08-30 | Kabushiki Kaisha Toshiba | Semiconductor device with low contact resistance SIC region |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8188484B2 (en) * | 2008-12-25 | 2012-05-29 | Rohm Co., Ltd. | Semiconductor device |

| US8188538B2 (en) | 2008-12-25 | 2012-05-29 | Rohm Co., Ltd. | Semiconductor device and method of manufacturing semiconductor device |

| JP2011134910A (ja) | 2009-12-24 | 2011-07-07 | Rohm Co Ltd | SiC電界効果トランジスタ |

| JP5668414B2 (ja) * | 2010-11-01 | 2015-02-12 | 住友電気工業株式会社 | 半導体装置の製造方法 |

| EP2750198A4 (en) | 2011-08-26 | 2015-04-15 | Nat Univ Corp Nara Inst | SiC SEMICONDUCTOR ELEMENT AND METHOD FOR MANUFACTURING THE SAME |

| JP6069059B2 (ja) * | 2013-03-22 | 2017-01-25 | 住友電気工業株式会社 | 炭化珪素半導体装置 |

| JP6183200B2 (ja) * | 2013-12-16 | 2017-08-23 | 住友電気工業株式会社 | 炭化珪素半導体装置およびその製造方法 |

| CN103928322B (zh) * | 2014-04-21 | 2016-08-17 | 西安电子科技大学 | 穿通型碳化硅绝缘栅双极型晶体管的制备方法 |

| JP6208106B2 (ja) * | 2014-09-19 | 2017-10-04 | 株式会社東芝 | 半導体装置及びその製造方法 |

| JP6523886B2 (ja) * | 2015-09-11 | 2019-06-05 | 株式会社東芝 | 半導体装置 |

| JP6657963B2 (ja) * | 2016-01-05 | 2020-03-04 | 富士電機株式会社 | Mosfet |

| JP6880669B2 (ja) * | 2016-11-16 | 2021-06-02 | 富士電機株式会社 | 炭化珪素半導体装置および炭化珪素半導体装置の製造方法 |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3893734B2 (ja) * | 1998-04-23 | 2007-03-14 | 株式会社デンソー | 炭化珪素半導体装置の製造方法 |

| JP4880164B2 (ja) * | 2000-02-15 | 2012-02-22 | ザ フォックス グループ,インコーポレイティド | 低欠陥密度炭化ケイ素材料 |

| EP1315212A4 (en) * | 2000-11-21 | 2008-09-03 | Matsushita Electric Ind Co Ltd | SEMICONDUCTOR DEVICE AND METHOD OF MANUFACTURING THE SAME |

| JP2002368015A (ja) * | 2001-06-06 | 2002-12-20 | Nippon Steel Corp | 電界効果トランジスタ |

| DE10247017B4 (de) * | 2001-10-12 | 2009-06-10 | Denso Corp., Kariya-shi | SiC-Einkristall, Verfahren zur Herstellung eines SiC-Einkristalls, SiC-Wafer mit einem Epitaxiefilm und Verfahren zur Herstellung eines SiC-Wafers, der einen Epitaxiefilm aufweist |

| US20040045631A1 (en) * | 2002-09-09 | 2004-03-11 | White Mary L. | Rapid refilling device for paintball ammunition pods |

| US7221010B2 (en) * | 2002-12-20 | 2007-05-22 | Cree, Inc. | Vertical JFET limited silicon carbide power metal-oxide semiconductor field effect transistors |

| US7074643B2 (en) * | 2003-04-24 | 2006-07-11 | Cree, Inc. | Silicon carbide power devices with self-aligned source and well regions and methods of fabricating same |

| US7294324B2 (en) * | 2004-09-21 | 2007-11-13 | Cree, Inc. | Low basal plane dislocation bulk grown SiC wafers |

| US7314520B2 (en) * | 2004-10-04 | 2008-01-01 | Cree, Inc. | Low 1c screw dislocation 3 inch silicon carbide wafer |

| US7348612B2 (en) * | 2004-10-29 | 2008-03-25 | Cree, Inc. | Metal-semiconductor field effect transistors (MESFETs) having drains coupled to the substrate and methods of fabricating the same |

| JP2007096263A (ja) * | 2005-08-31 | 2007-04-12 | Denso Corp | 炭化珪素半導体装置およびその製造方法。 |

| JP5017865B2 (ja) * | 2006-01-17 | 2012-09-05 | 富士電機株式会社 | 半導体装置 |

| JP4751308B2 (ja) * | 2006-12-18 | 2011-08-17 | 住友電気工業株式会社 | 横型接合型電界効果トランジスタ |

-

2008

- 2008-10-02 JP JP2008257280A patent/JP2010087397A/ja active Pending

-

2009

- 2009-08-07 CA CA2739410A patent/CA2739410A1/en not_active Abandoned

- 2009-08-07 EP EP09817584.7A patent/EP2348530B1/en active Active

- 2009-08-07 KR KR1020117009510A patent/KR20110061641A/ko not_active Application Discontinuation

- 2009-08-07 WO PCT/JP2009/064002 patent/WO2010038547A1/ja active Application Filing

- 2009-08-07 US US13/121,893 patent/US20110175111A1/en not_active Abandoned

- 2009-08-07 CN CN2009801393503A patent/CN102171827A/zh active Pending

- 2009-09-10 TW TW098130582A patent/TW201025594A/zh unknown

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9431246B2 (en) | 2012-12-27 | 2016-08-30 | Kabushiki Kaisha Toshiba | Semiconductor device with low contact resistance SIC region |

| KR101411490B1 (ko) * | 2013-01-23 | 2014-06-24 | 박종진 | 플라즈마 차폐 기능을 가진 도어 플레이트 |

Also Published As

| Publication number | Publication date |

|---|---|

| TW201025594A (en) | 2010-07-01 |

| EP2348530B1 (en) | 2016-03-09 |

| EP2348530A4 (en) | 2013-01-23 |

| CA2739410A1 (en) | 2010-04-08 |

| EP2348530A1 (en) | 2011-07-27 |

| CN102171827A (zh) | 2011-08-31 |

| WO2010038547A1 (ja) | 2010-04-08 |

| JP2010087397A (ja) | 2010-04-15 |

| US20110175111A1 (en) | 2011-07-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20110061641A (ko) | 탄화규소 반도체 장치 | |

| US8564060B2 (en) | Semiconductor device with large blocking voltage and manufacturing method thereof | |

| US10263082B2 (en) | Semiconductor device having a gate electrode formed inside a trench | |

| KR101613930B1 (ko) | 탄화규소 반도체 장치 및 그 제조 방법 | |

| TWI390637B (zh) | 具混合井區之碳化矽裝置及用以製造該等碳化矽裝置之方法 | |

| WO2010110246A1 (ja) | 半導体装置 | |

| US10276709B2 (en) | Semiconductor device and method of manufacturing semiconductor device | |

| US8564017B2 (en) | Silicon carbide semiconductor device and method for manufacturing same | |

| JP2017092368A (ja) | 半導体装置および半導体装置の製造方法 | |

| JP3573149B2 (ja) | 炭化珪素半導体装置 | |

| CN102770960A (zh) | 半导体器件及其制造方法 | |

| JP2012164707A (ja) | 半導体装置およびその製造方法 | |

| WO2010098076A1 (ja) | 蓄積型絶縁ゲート型電界効果型トランジスタ | |

| JP2018060923A (ja) | 半導体装置および半導体装置の製造方法 | |

| CN104979395A (zh) | 半导体结构 | |

| US8994034B2 (en) | Semiconductor device and method of manufacturing the same | |

| JP4948784B2 (ja) | 半導体装置及びその製造方法 | |

| US10269952B2 (en) | Semiconductor device having steps in a termination region and manufacturing method thereof | |

| KR20100123589A (ko) | 반도체 장치 및 반도체 장치의 제조 방법 | |

| JP2014170886A (ja) | 半導体装置及びその製造方法 | |

| US8829605B2 (en) | Semiconductor device having deep and shallow trenches | |

| JP4730097B2 (ja) | 電界効果トランジスタ | |

| US6150671A (en) | Semiconductor device having high channel mobility and a high breakdown voltage for high power applications | |

| KR101603567B1 (ko) | 탄화 규소 반도체장치 및 그 제조방법 | |

| WO2015111177A1 (ja) | 半導体装置,パワーモジュール,電力変換装置,および鉄道車両 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E601 | Decision to refuse application |