KR101177039B1 - 솔더 및 필름 접착제를 사용하여 플립 칩 패키지에 히트 스프레더/스티프너를 접지하는 방법 - Google Patents

솔더 및 필름 접착제를 사용하여 플립 칩 패키지에 히트 스프레더/스티프너를 접지하는 방법 Download PDFInfo

- Publication number

- KR101177039B1 KR101177039B1 KR1020107018929A KR20107018929A KR101177039B1 KR 101177039 B1 KR101177039 B1 KR 101177039B1 KR 1020107018929 A KR1020107018929 A KR 1020107018929A KR 20107018929 A KR20107018929 A KR 20107018929A KR 101177039 B1 KR101177039 B1 KR 101177039B1

- Authority

- KR

- South Korea

- Prior art keywords

- holes

- stiffener

- substrate

- heat spreader

- die

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/50—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor for integrated circuit devices, e.g. power bus, number of leads

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/02—Containers; Seals

- H01L23/10—Containers; Seals characterised by the material or arrangement of seals between parts, e.g. between cap and base of the container or between leads and walls of the container

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/34—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements

- H01L23/36—Selection of materials, or shaping, to facilitate cooling or heating, e.g. heatsinks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49833—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers the chip support structure consisting of a plurality of insulating substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/552—Protection against radiation, e.g. light or electromagnetic waves

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73253—Bump and layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L24/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01057—Lanthanum [La]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1515—Shape

- H01L2924/15153—Shape the die mounting substrate comprising a recess for hosting the device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1517—Multilayer substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/161—Cap

- H01L2924/1615—Shape

- H01L2924/16195—Flat cap [not enclosing an internal cavity]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/3025—Electromagnetic shielding

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Materials Engineering (AREA)

- Chemical & Material Sciences (AREA)

- Health & Medical Sciences (AREA)

- Electromagnetism (AREA)

- Toxicology (AREA)

- Cooling Or The Like Of Semiconductors Or Solid State Devices (AREA)

- Wire Bonding (AREA)

Abstract

플립 칩 패키지에 대한 히트 스프레더/스티프너의 접지 방법이 제공 되며, 상기 방법은 기판에 접착 필름을 부착하는 단계 및 상기 접착 필름에 스티프너를 부착하는 단계를 포함한다. 접착 필름은 기판 상의 접지 패드에 대응하는 다수의 제1 홀들을 가질 수 있다. 접지 패드들은 전기적인 접지를 제공하도록 구성될 수 있다. 스티프너는 접착 필름의 다수의 홀들과 기판의 다수의 패드들에 대응하는 다수의 제2 홀들을 가질 수 있다. 일반적으로 접지 패드들은 제1 홀들 및 제2 홀들을 통해 노출될 수 있다.

Description

본 발명은 일반적으로 반도체 칩 어셈블리에 관한 것이고, 보다 상세하게는 솔더와 필름 접착제를 사용하여 플립 칩 패키지에 히트 스프레더/스티프너를 접지하는 방법 및/또는 구조에 관한 것이다.

전자기 차폐(electromagnetic shielding)를 위한 전통적인 패키지 접지는 히트 싱크(heat sink) 및/또는 히트 스프레더(heat spreader)를 통해 행해진다. 히트 싱크 및/또는 히트 스프레더는 클램프, 와이어, 또는 그 밖의 연결 수단을 사용하여 인쇄 회로 기판(PCB)에 연결된다. 전통적인 기법은 PCB를 위한 추가의 제조 단계들을 포함하여 비용이 많이 들고 취급상의 문제가 있다.

본 발명은 플립 칩 패키지(flip chip package)에 히트 스프레더/스티프너(heat spreader/stiffener)를 접지하는 방법에 관한 것으로, 상기 방법은 기판에 접착 필름을 부착하는 단계와 상기 접착 필름에 스티프너를 부착하는 단계를 포함한다. 접착 필름은 기판 상의 다수의 접지 패드에 대응하는 다수의 제1 홀들을 가질 수 있다. 접지 패드는 전기적인 접지를 제공하도록 구성될 수 있다. 스티프너는 접착 필름의 다수의 제1홀들과 기판의 다수의 접지 패드들에 대응하는 다수의 제2홀들을 가질 수 있다. 일반적으로 접지 패드는 제1홀들 및 제2홀들을 통해 노출된다.

본 발명의 목적, 특징 및 장점들은 솔더 및 필름 접착제를 사용하여 플립 칩 패키지에 히트 스프레더/스티프너를 접지하기 위한 방법 및/또는 구조를 제공하는 것을 포함하고, 이는 (i) 최종 사용자에게 투명한 차폐를 제공할 수 있고, (ii) 비용을 절감할 수 있고, (iii) 인쇄 회로 기판의 제조 단계들을 줄이거나 삭제할 수 있고, (iv) 취급 문제를 줄이거나 삭제할 수 있고, (v) 전자기 차폐를 집적 회로 패키지에 통합할 수 있고, 그리고/또는 (vi) 에폭시 부착에 비해 보다 높은 신뢰성을 제공할 수 있다.

본 발명의 이들 및 기타 목적, 특징 및 장점들은 다음의 상세한 설명, 첨부 특허청구범위 및 도면으로부터 명백해질 것이다:

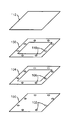

도 1은 본 발명에 따른 기판에 두-조각의 히트 스프레더/스티프너를 부착하는 것을 예시하는 도면이다;

도 2는 본 발명의 바람직한 실시예에 따른 통합된 투-피스(two-piece)의 히트 스프레더/스티프너의 횡-단면도를 예시하는 도면이다; 그리고

도 3은 본 발명에 따른 공정을 예시하는 순서도이다.

도 1은 본 발명에 따른 기판에 두-조각의 히트 스프레더/스티프너를 부착하는 것을 예시하는 도면이다;

도 2는 본 발명의 바람직한 실시예에 따른 통합된 투-피스(two-piece)의 히트 스프레더/스티프너의 횡-단면도를 예시하는 도면이다; 그리고

도 3은 본 발명에 따른 공정을 예시하는 순서도이다.

본 발명은 일반적으로 플립 칩 패키지에 히트 스프레더/스티프너를 접지하기 위한 방법 및 구조를 제공한다. 플립 칩 패키지는 제조업자들이 FPBGA, FCPBGA, FCBGA 등의 명칭을 사용하여 불리어질 수 있다. 일반적으로 본 발명은 패키지 기판을 통해 히트 스프레더/스티프너를 접지하여 패키지에 전자기 차폐를 통합시키기 위한 방법을 제공한다. 일 실시예에서, 필름 접착제 및 솔더의 조합은 히트 스프레더/스티프너를 패키지 기판에 기계적으로 그리고 전기적으로 연결시키는데 사용될 수 있다. 본 발명에 의해 제공되는 차폐는 고객(또는 최종 수요자)에 투명할 수 있다. 일반적으로 본 발명은 전통적인 접근법의 결함을 제거한다.

도 1을 참조하면, 본 발명에 따라 패키지 기판에 히트 스프레더/스티프너를 부착하는 것을 예시하는 도면이 도시되어 있다. 일 실시예에서, 기판(100)에는 다수의 패드(pads)(또는 트레이스(traces))(102)가 구비될 수 있다. 패드(102)는 전기적인 접지 연결을 제공하도록 구성될 수 있다. 패드(102)는 금속(예를 들면, 솔더, 주석(Sn), 니켈(Ni), 금(Au) 등)으로 피복될 수 있다. 일 실시예에서, 기판(100)은 플립 칩 패키지의 부분일 수 있다. 패드(102)는 기판(100)의 맨위 표면상에 있을 수 있다(예를 들면, 패키지 내부). 기판(100)의 바닥 표면은, 일 실시예에서, 볼 그리드 어레이(ball grid array)를 포함할 수 있다.

접착 필름(104)은 기판(100)의 맨위 표면에 적용, 부착, 접착될 수 있다. 접착 필름(104)은 기판(100)의 패드(102)에 대응하도록 위치될 수 있는 다수의 홀들(106)을 가질 수 있다. 일 실시예에서, 홀들(106)은 솔더(solder)를 포함할 수 있다. 일 실시예에서, 접착 필름(104)은 다이(미도시) 둘레에 끼워 맞춰지도록 환상의 링으로 패턴화될 수 있다. 접착 필름(104)은, 일 실시예에서, 스티프너(108)의 형상과 조화되도록 패턴화될 수 있다.

스티프너(108)는 전기적으로 전도성의 물질로 이루어질 수 있다. 일 실시예에서, 스티프너(108)은 금속(예를 들면, 구리 등)일 수 있다. 스티프너(108)는 다수의 홀들(110)을 가질 수 있고, 다수의 홀들(110)은 기판(100)의 패드(102)와 접착 필름(104)의 홀들(106)에 대응하도록 위치될 수 있다(예를 들면, 나란히 놓여짐). 일반적으로 패드(102)는 홀들(106, 110))을 통해 (접근가능하게) 노출된다. 일 실시예에서, 홀들(106, 110)은 원형일 수 있다. 하지만, 다른 형태의 홀들이 특정 구현의 설계 기준에 맞게 구현될 수 있다.

스티프너(108)의 홀들(110)과 접착 필름(104)의 홀들(106)은 패드(102)를 통해 스티프너를 기판(100)에 기계적으로 그리고 전기적으로 연결하도록 준비될 수 있다. 스티프너(108)는 접착 필름(104)에 의해 기판(100)에 부착 또는 접착될 수 있다. 예를 들면, 스티프너(108)는 접착 필름(104)을 사용하여 기판에 부착될 수 있다. 그 다음 접착 필름(104)은 경화될 수 있다. 일 실시예에서, 홀들(106, 110)은 등사에 의해 솔더 페이스트로 채워질(stenciled with solder paste) 수 있다. 다른 실시예에서, 솔더는 스티프너(108)가 접착 필름(104)에 부착된 후에, 홀들(106, 110)로 분배될 수 있다. 또 다른 실시예에서, 플럭스(flux)가 홀들(106, 110)에 분배되고 플럭스 후에 솔더 볼(solder ball)이 안에 떨어뜨려질 수 있다. 또 다른 실시예에서, 플럭스에 담궈진 솔더 볼들(flux dipped solder balls)이 홀들(110) 속에 떨어질 수 있다. 하지만, 스티프너(108)을 패드(102)에 전기적으로 연결하는 홀들(106, 110)의 다른 제조 방법은 특정 구현물의 설계 기준에 맞게 구현될 수 있다.

히트 스프레더(112)는 스티프너(108)에 부착되어 히트 스프레더(112)가 스티프너(108)와 기판(100)에 전기적으로 연결될 수 있다. 일 실시예에서, 히트 스프레더(112)는 전기 전도성 에폭시를 사용하여 스티프너(108)에 부착될 수 있다. 다른 실시예에서, 히트 스프레더(112)는 홀들(106, 110)에 있는 솔더를 통해 스티프너(108)에 더 부착될 수 있다. 하지만, 히트 스프레더(112)를 스티프너(108)에 기계적으로 그리고 전기적으로 부착하는 다른 방법은 특정 구현물의 설계 기준에 맞게 구현될 수 있다.

도 2를 참조하면, 본 발명의 실시예에 따른 패키지(150)의 횡-단면도를 예시하는 도면이 도시되어 있다. 패키지(150)는 플립 칩 패키지로서 구현될 수 있다. 패키지(150)는 본 발명에 따른 히트 스프레더/스티프너 접지 스킴(grounding scheme)을 구현할 수 있다. 패키지(150)는 예를 들면, 플립 칩 솔더 범프(flip chip solder bumps)(156)를 사용하여 기판(154)에 부착되는 다이(152)를 포함할 수 있다. 다이(152)와 기판(154) 사이의 틈은 언더필(underfill)(158)로 채워질 수 있다. 스티프너(160)은 접착 필름(162)과 솔더(또는 솔더 볼)(164)을 사용하여 기판(154)에 부착될 수 있다. 솔더(164)는 기판(154) 상의 접지 패드(166)와의 기계적인 그리고 전기적인 연결을 형성할 수 있다. 일 실시예에서, 솔더(164)는 스티프너(160)를 기판(154)의 패드(166)에 부착하도록 구성될 수 있다(예를 들면 솔더 볼(164a)로 예시됨).

히트 스프레더(168)는 (i) 열 전도성 물질(170)을 사용하여 다이(152)와 (ii) 전기 전도성 물질(172)를 사용하여 스티프너(160)에 부착될 수 있다. 일 실시예에서, 솔더(164)는 스티프너(160)와 히트 스프레더(168) 양쪽 모두를 기판(154) 상의 패드(166)에 전기적으로 연결하도록 구성될 수 있다(예를 들면, 솔더 볼(164b)로 예시됨). 일 실시예에서, 열 전도성 물질(170)은 써멀 그리스(thermal grease) 등의 낮은 모듈러스 물질(low modulus material)을 포함할 수 있다. 하지만, 다른 열 전도성 물질들은 특정 구현의 설계 기준에 맞게 구비될 수 있다. 전기 전도성 물질(172)은 일 실시예에서, 전기 전도성 에폭시, 에폭시 필름 등의 높은 모듈러스 물질을 포함할 수 있다. 하지만, 다른 전기 전도성 물질은 히트 스프레더(168)와 스티프너(160)를 결합하는데 사용될 수 있다. 일 실시예에서, 다이(152)의 맨위(또는 뒤) 면(예를 들면 히트 스프레더(168)을 바라보는 면)이 상기 물질(170) 대신에 전기 전도성 물질을 사용하여 접지될 수 있다. 기판(154)은, 일 실시예에서, 다이(152) 반대편 측면 상에 솔더 볼(174)을 가질 수 있다.

도 3을 참조하면, 본 발명의 바람직한 실시예에 따른 방법(200)을 예시하는 순서도가 도시되어 있다. 일 실시예에서, 방법(200)은 단계(또는 공정)(202), 단계(또는 공정)(204), 단계(또는 공정)(206), 단계(또는 공정)(208) 그리고 단계(또는 공정)(210)을 포함할 수 있다. 일반적으로 단계(202)는, 일 실시예로, 접착 필름을 사용하여 기판에 스티프너를 부착하는 것을 포함한다. 스티프너 그리고 접착 필름은 기판 상의 접지 패드에 대응하는 홀들을 가질 수 있다. 일반적으로 단계(204)는 접착 필름을 경화하는 것을 포함한다. 일반적으로 단계(206)은 하나 이상의 솔더, 플럭스 및/또는 솔더 볼을 스티프너에 있는 홀들에 분배하는 것을 포함한다. 일반적으로 단계(208)은, 일 실시예로, 전기 전도성 에폭시를 사용하여, 스티프너에 히트 스프레더를 부착하는 것을 포함한다. 일반적으로 단계(210)은 리플로 공정(reflow process)을 포함하고, 이 리플로 공정 동안 스티프너의 홀들에 있는 솔더(또는 솔더 볼)는 고체 솔더-패드와 솔더-스티프너 (또는 솔더-스티프너-히트 스프레더)의 계면을 형성한다. 일 실시예에서, 다이와 커패시터는, 어떤 것이든, 스티프너의 부착 전에 전통적인 기법들을 사용하여 기판에 부착될 수 있다.

본 발명은 본 발명의 바람직한 실시예를 참조하여 구체적으로 설명되고 기술되었지만, 이 기술분야에서 통상의 지식을 가진 자라면 형태와 세부사항에 있어서의 다양한 변경들이 본 발명의 사상을 이탈함이 없이 이루어질 수 있음을 이해할 수 있을 것이다.

Claims (23)

- 플립 칩 패키지에 히트 스프레더/스티프너를 접지하는 방법으로서:

접착 필름을 기판에 부착시키는 단계로, 상기 접착 필름은 상기 기판 상의 다수의 접지 패드에 대응하는 다수의 제1 홀들을 갖고, 상기 접지 패드들은 전기적인 접지를 제공하도록 구성되는, 접착 필름을 기판에 부착시키는 단계;

스티프너를 상기 접착 필름에 부착시키는 단계로, 상기 스티프너는 상기 접착 필름의 상기 다수의 제1 홀들과 상기 기판의 상기 접지 패드들에 대응하는 다수의 제2 홀들을 갖고, 상기 접지 패드들은 상기 제1 홀들 및 상기 제2 홀들을 통해 노출되는, 스티프너를 상기 접착 필름에 부착시키는 단계;

상기 기판에 집적 회로를 포함하는 다이를 부착시키는 단계; 및

상기 다이가 상기 기판의 접지 패드에 전기적으로 연결되도록 상기 다이와 상기 스티프너에 히트 스프레더를 부착하는 단계를 포함하는 플립 칩 패키지에 대한 히트 스프레더/스티프너의 접지 방법. - 제1항에 있어서, 상기 제2 홀들 내부에 솔더 페이스트를 등사에 의해 채우는 단계를 더 포함하는 플립 칩 패키지에 대한 히트 스프레더/스티프너의 접지 방법.

- 제1항에 있어서, 상기 제2 홀들 내부에 솔더 페이스트를 분배하는 단계를 더 포함하는 플립 칩 패키지에 대한 히트 스프레더/스티프너의 접지 방법.

- 제1항에 있어서,

상기 제2 홀들 내부에 플럭스를 분배하는 단계; 및

상기 제2 홀들 내부에 솔더 볼들을 떨어트리는 단계를 더 포함하는 플립 칩 패키지에 대한 히트 스프레더/스티프너의 접지 방법. - 제1항에 있어서, 상기 제2 홀들에 플럭스 피복 솔더 볼들을 떨어트리는 단계를 더 포함하는 플립 칩 패키지에 대한 히트 스프레더/스티프너의 접지 방법.

- 제1항에 있어서, 상기 히트 스프레더가 상기 기판의 상기 접지 패드에 전기적으로 연결되도록 상기 히트 스프레더는 상기 스티프너에 부착하는 것을 특징으로 하는 플립 칩 패키지에 대한 히트 스프레더/스티프너의 접지 방법.

- 제1항에 있어서, 상기 다이는 전기 전도성 물질을 사용하여 상기 히트 스프레더에 부착되는 것을 특징으로 하는 플립 칩 패키지에 대한 히트 스프레더/스티프너의 접지 방법.

- 제1항에 있어서, 상기 다이는 상기 스티프너에 부착되기 전에 상기 기판에 부착되는 것을 특징으로 하는 플립 칩 패키지에 대한 히트 스프레더/스티프너의 접지 방법.

- 전기적인 접지를 제공하도록 구성된 다수의 접지 패드들을 갖는 기판;

상기 기판의 상기 다수의 접지 패드들에 대응하는 다수의 제1 홀들을 갖는 스티프너;

상기 다수의 접지 패드들과 상기 다수의 제1 홀들에 대응하는 다수의 제2 홀들을 갖는 접착 필름; 및

상기 기판에 전기적으로 부착하도록 구성된 다이를 포함하고,

상기 접착 필름은 상기 접지 패드가 상기 제1 홀들 및 상기 제2 홀들을 통해 노출되도록 상기 스티프너를 상기 기판에 기계적으로 부착시켜 구성되고,

상기 다이는 히트 스프레더에 전기적으로 부착되고 상기 히트 스프레더는 상기 접지 패드에 전기적으로 연결되는 것을 특징으로 하는 장치. - 제9항에 있어서, 상기 접지 패드는 금속으로 피복되는 것을 특징으로 하는 장치.

- 제9항에 있어서, 상기 제1 홀들 및 상기 제2 홀들 내부의 솔더 페이스트를 더 포함하는 장치.

- 제9항에 있어서, 상기 제1 홀들 및 상기 제2 홀들 내부의 플럭스와 솔더 볼들을 더 포함하는 장치.

- 제9항에 있어서, 솔더가 상기 제1 홀들 및 상기 제2 홀들을 통해 상기 접지 패드에 상기 스티프너를 전기적으로 연결하는 것을 특징으로 하는 장치.

- 제9항에 있어서, 솔더가 상기 제1 홀들 및 상기 제2 홀들을 통해 상기 접지 패드에 상기 스티프너와 히트 스프레더를 전기적으로 연결하는 것을 특징으로 하는 장치.

- 제9항에 있어서, 상기 기판에 상기 다이를 기계적으로 그리고 전기적으로 연결하도록 구성된 솔더 범프들의 에이리어 어레이 인터커넥트(area array interconnect)를 더 포함하는 장치.

- 제9항에 있어서, 상기 다이는 전기 전도성 물질에 의해 상기 히트 스프레더에 부착되는 것을 특징으로 하는 장치.

- 제9항에 있어서, 상기 기판 반대 편의 상기 다이의 측면이 상기 히트 스프레더, 상기 스티프너 및 상기 접지 패드를 포함하는 전기 전도성 경로를 통해 전기적으로 접지되는 것을 특징으로 하는 장치.

- 전기적인 접지를 제공하도록 구성된 다수의 접지 패드를 갖는 기판;

상기 기판의 상기 다수의 접지 패드에 대응하는 다수의 제1 홀들을 갖는 스티프너;

상기 다수의 접지 패드와 상기 다수의 제1 홀들에 대응하는 다수의 제2 홀들을 갖는 접착 필름;

상기 기판에 전기적으로 연결된 다이; 및

상기 다이, 상기 스티프너 및 상기 접지 패드들에 전기적으로 연결된 히트 스프레더를 포함하고,

상기 접착 필름은 상기 접지 패드가 상기 제1 홀들 및 상기 제2 홀들을 통해 노출되도록 상기 스티프너를 상기 기판에 기계적으로 부착하여 구성되는 것을 특징으로 하는 플립 칩 패키지 집적 회로. - 제18항에 있어서, 상기 제1 홀들 및 상기 제2 홀들 내부에 솔더 페이스트를 더 포함하는 플립 칩 패키지 집적 회로.

- 제18항에 있어서, 상기 제1 홀들 및 상기 제2 홀들 내부에 플럭스와 솔더 볼들을 더 포함하는 플립 칩 패키지 집적 회로.

- 제18항에 있어서, 상기 히트 스프레더는 상기 다이 및 상기 접지 패드들에 하나 이상의 전기 전도성 물질을 통해 연결되는 것을 특징으로 하는 플립 칩 패키지 집적 회로.

- 제21항에 있어서, 상기 히트 스프레더는 전기 전도성 에폭시를 사용하여 상기 스티프너에 부착되는 것을 특징으로 하는 플립 칩 패키지 집적 회로.

- 제21항에 있어서, 상기 히트 스프레더는 상기 제1 홀들 및 상기 제2 홀들 내의 솔더를 통해 상기 스티프너에 부착되는 것을 특징으로 하는 플립 칩 패키지 집적 회로.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US12/038,911 US7968999B2 (en) | 2008-02-28 | 2008-02-28 | Process of grounding heat spreader/stiffener to a flip chip package using solder and film adhesive |

| US12/038,911 | 2008-02-28 | ||

| PCT/US2008/012957 WO2009108171A1 (en) | 2008-02-28 | 2008-11-20 | Process of grounding heat spreader/stiffener to a flip chip package using solder and film adhesive |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20100126708A KR20100126708A (ko) | 2010-12-02 |

| KR101177039B1 true KR101177039B1 (ko) | 2012-08-27 |

Family

ID=41012540

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020107018929A KR101177039B1 (ko) | 2008-02-28 | 2008-11-20 | 솔더 및 필름 접착제를 사용하여 플립 칩 패키지에 히트 스프레더/스티프너를 접지하는 방법 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US7968999B2 (ko) |

| EP (1) | EP2248165B1 (ko) |

| JP (1) | JP5226087B2 (ko) |

| KR (1) | KR101177039B1 (ko) |

| CN (1) | CN101960586B (ko) |

| TW (1) | TWI379364B (ko) |

| WO (1) | WO2009108171A1 (ko) |

Families Citing this family (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20090321925A1 (en) * | 2008-06-30 | 2009-12-31 | Gealer Charles A | Injection molded metal ic package stiffener and package-to-package interconnect frame |

| US8247900B2 (en) * | 2009-12-29 | 2012-08-21 | Taiwan Semiconductor Manufacturing Company, Ltd. | Flip chip package having enhanced thermal and mechanical performance |

| US9254532B2 (en) * | 2009-12-30 | 2016-02-09 | Intel Corporation | Methods of fabricating low melting point solder reinforced sealant and structures formed thereby |

| US20110292612A1 (en) * | 2010-05-26 | 2011-12-01 | Lsi Corporation | Electronic device having electrically grounded heat sink and method of manufacturing the same |

| US8823407B2 (en) | 2012-03-01 | 2014-09-02 | Integrated Device Technology, Inc. | Test assembly for verifying heat spreader grounding in a production test |

| US9041192B2 (en) * | 2012-08-29 | 2015-05-26 | Broadcom Corporation | Hybrid thermal interface material for IC packages with integrated heat spreader |

| US8946871B2 (en) | 2012-11-07 | 2015-02-03 | Lsi Corporation | Thermal improvement of integrated circuit packages |

| US9607951B2 (en) * | 2013-08-05 | 2017-03-28 | Mediatek Singapore Pte. Ltd. | Chip package |

| US9282649B2 (en) * | 2013-10-08 | 2016-03-08 | Cisco Technology, Inc. | Stand-off block |

| US9735043B2 (en) | 2013-12-20 | 2017-08-15 | Taiwan Semiconductor Manufacturing Company, Ltd. | Semiconductor packaging structure and process |

| CN105514080B (zh) * | 2014-10-11 | 2018-12-04 | 意法半导体有限公司 | 具有再分布层和加强件的电子器件及相关方法 |

| US9460980B2 (en) * | 2015-02-18 | 2016-10-04 | Qualcomm Incorporated | Systems, apparatus, and methods for heat dissipation |

| JP6569375B2 (ja) * | 2015-08-11 | 2019-09-04 | 株式会社ソシオネクスト | 半導体装置、半導体装置の製造方法及び電子装置 |

| US20170053858A1 (en) * | 2015-08-20 | 2017-02-23 | Intel Corporation | Substrate on substrate package |

| US20170170087A1 (en) | 2015-12-14 | 2017-06-15 | Intel Corporation | Electronic package that includes multiple supports |

| US20170287799A1 (en) * | 2016-04-01 | 2017-10-05 | Steven A. Klein | Removable ic package stiffener |

| CN107708328A (zh) * | 2017-06-27 | 2018-02-16 | 安徽华东光电技术研究所 | 提高芯片充分接地和散热的焊接方法 |

| JP6579396B2 (ja) * | 2017-07-18 | 2019-09-25 | 株式会社ダイレクト・アール・エフ | 半導体装置、及び基板 |

| US20190206839A1 (en) * | 2017-12-29 | 2019-07-04 | Intel Corporation | Electronic device package |

| US11081450B2 (en) | 2019-09-27 | 2021-08-03 | Intel Corporation | Radiation shield around a component on a substrate |

| CN115116860A (zh) * | 2022-06-17 | 2022-09-27 | 北京比特大陆科技有限公司 | 芯片封装方法及芯片 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20020108768A1 (en) | 2000-11-30 | 2002-08-15 | International Business Machines Corporation | I/C chip assembly and method of forming same |

| US20040104469A1 (en) | 2000-10-02 | 2004-06-03 | Yoshihiko Yagi | Card type recording medium and production method therefor |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5736074A (en) * | 1995-06-30 | 1998-04-07 | Micro Fab Technologies, Inc. | Manufacture of coated spheres |

| JP3437369B2 (ja) | 1996-03-19 | 2003-08-18 | 松下電器産業株式会社 | チップキャリアおよびこれを用いた半導体装置 |

| JP2770820B2 (ja) * | 1996-07-01 | 1998-07-02 | 日本電気株式会社 | 半導体装置の実装構造 |

| US6051888A (en) * | 1997-04-07 | 2000-04-18 | Texas Instruments Incorporated | Semiconductor package and method for increased thermal dissipation of flip-chip semiconductor package |

| US6011304A (en) * | 1997-05-05 | 2000-01-04 | Lsi Logic Corporation | Stiffener ring attachment with holes and removable snap-in heat sink or heat spreader/lid |

| US6114761A (en) | 1998-01-20 | 2000-09-05 | Lsi Logic Corporation | Thermally-enhanced flip chip IC package with extruded heatspreader |

| JP2000114413A (ja) * | 1998-09-29 | 2000-04-21 | Sony Corp | 半導体装置、その製造方法および部品の実装方法 |

| US6639321B1 (en) | 2000-10-06 | 2003-10-28 | Lsi Logic Corporation | Balanced coefficient of thermal expansion for flip chip ball grid array |

| US6528892B2 (en) | 2001-06-05 | 2003-03-04 | International Business Machines Corporation | Land grid array stiffener use with flexible chip carriers |

| KR100394809B1 (ko) | 2001-08-09 | 2003-08-14 | 삼성전자주식회사 | 반도체 패키지 및 그 제조 방법 |

| US6472762B1 (en) | 2001-08-31 | 2002-10-29 | Lsi Logic Corporation | Enhanced laminate flipchip package using a high CTE heatspreader |

| US6854633B1 (en) * | 2002-02-05 | 2005-02-15 | Micron Technology, Inc. | System with polymer masking flux for fabricating external contacts on semiconductor components |

| US6987032B1 (en) * | 2002-07-19 | 2006-01-17 | Asat Ltd. | Ball grid array package and process for manufacturing same |

| JP4639600B2 (ja) * | 2004-02-04 | 2011-02-23 | 凸版印刷株式会社 | 半導体パッケージ |

| JP2006013029A (ja) * | 2004-06-24 | 2006-01-12 | Toppan Printing Co Ltd | 半導体パッケージ |

| US7451432B2 (en) * | 2004-10-01 | 2008-11-11 | Microsoft Corporation | Transformation of componentized and extensible workflow to a declarative format |

| JP4860994B2 (ja) * | 2005-12-06 | 2012-01-25 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

-

2008

- 2008-02-28 US US12/038,911 patent/US7968999B2/en active Active

- 2008-11-10 TW TW097143311A patent/TWI379364B/zh not_active IP Right Cessation

- 2008-11-20 KR KR1020107018929A patent/KR101177039B1/ko active IP Right Grant

- 2008-11-20 CN CN2008801275042A patent/CN101960586B/zh active Active

- 2008-11-20 JP JP2010548652A patent/JP5226087B2/ja not_active Expired - Fee Related

- 2008-11-20 WO PCT/US2008/012957 patent/WO2009108171A1/en active Application Filing

- 2008-11-20 EP EP08872772.2A patent/EP2248165B1/en active Active

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20040104469A1 (en) | 2000-10-02 | 2004-06-03 | Yoshihiko Yagi | Card type recording medium and production method therefor |

| US20020108768A1 (en) | 2000-11-30 | 2002-08-15 | International Business Machines Corporation | I/C chip assembly and method of forming same |

Also Published As

| Publication number | Publication date |

|---|---|

| EP2248165A4 (en) | 2012-04-18 |

| WO2009108171A1 (en) | 2009-09-03 |

| US7968999B2 (en) | 2011-06-28 |

| EP2248165B1 (en) | 2017-01-18 |

| TW200937539A (en) | 2009-09-01 |

| EP2248165A1 (en) | 2010-11-10 |

| JP5226087B2 (ja) | 2013-07-03 |

| CN101960586B (zh) | 2012-07-18 |

| US20090218680A1 (en) | 2009-09-03 |

| TWI379364B (en) | 2012-12-11 |

| JP2011513970A (ja) | 2011-04-28 |

| KR20100126708A (ko) | 2010-12-02 |

| CN101960586A (zh) | 2011-01-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101177039B1 (ko) | 솔더 및 필름 접착제를 사용하여 플립 칩 패키지에 히트 스프레더/스티프너를 접지하는 방법 | |

| KR100734816B1 (ko) | 전자 소자 캐리어를 위한 최적화된 덮개의 장착 | |

| TWI529878B (zh) | 集成電路封裝件及其裝配方法 | |

| US6518089B2 (en) | Flip chip semiconductor device in a molded chip scale package (CSP) and method of assembly | |

| US6546620B1 (en) | Flip chip integrated circuit and passive chip component package fabrication method | |

| US7211889B2 (en) | Semiconductor package and method for manufacturing the same | |

| US8987919B2 (en) | Built-in electronic component substrate and method for manufacturing the substrate | |

| JP5649805B2 (ja) | 半導体装置の製造方法 | |

| KR100442695B1 (ko) | 열 방출판이 부착된 플립칩 패키지 제조 방법 | |

| US6819566B1 (en) | Grounding and thermal dissipation for integrated circuit packages | |

| KR20070076084A (ko) | 스택 패키지와 그 제조 방법 | |

| TW201207961A (en) | Semiconductor package device using underfill material and packaging method thereof | |

| US7554197B2 (en) | High frequency IC package and method for fabricating the same | |

| US20060273467A1 (en) | Flip chip package and method of conducting heat therefrom | |

| US20020196615A1 (en) | Shielded electronics package structure with enhanced mechanical reliability | |

| KR100370116B1 (ko) | 반도체 패키지 및 그 제조방법 | |

| JPH08236911A (ja) | ボール状外部接続端子の構造 | |

| JP7526642B2 (ja) | 半導体装置およびその製造方法 | |

| JP2004119882A (ja) | 半導体装置 | |

| KR100666990B1 (ko) | Bga 패키지 및 그 제조방법 | |

| KR100648044B1 (ko) | 반도체 패키지의 제조 방법 | |

| JP2007096025A (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| A302 | Request for accelerated examination | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20160801 Year of fee payment: 5 |

|

| FPAY | Annual fee payment |

Payment date: 20170811 Year of fee payment: 6 |

|

| FPAY | Annual fee payment |

Payment date: 20180801 Year of fee payment: 7 |