KR100997490B1 - 위상동기루프회로에서의 잡음억제용 시스템 및 방법 - Google Patents

위상동기루프회로에서의 잡음억제용 시스템 및 방법 Download PDFInfo

- Publication number

- KR100997490B1 KR100997490B1 KR1020057006976A KR20057006976A KR100997490B1 KR 100997490 B1 KR100997490 B1 KR 100997490B1 KR 1020057006976 A KR1020057006976 A KR 1020057006976A KR 20057006976 A KR20057006976 A KR 20057006976A KR 100997490 B1 KR100997490 B1 KR 100997490B1

- Authority

- KR

- South Korea

- Prior art keywords

- frequency

- signal

- pll

- value

- delete delete

- Prior art date

Links

- 238000000034 method Methods 0.000 title claims abstract description 39

- 230000001629 suppression Effects 0.000 claims abstract description 25

- 238000000926 separation method Methods 0.000 description 16

- 238000004891 communication Methods 0.000 description 6

- 238000010586 diagram Methods 0.000 description 5

- 230000008901 benefit Effects 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 229920000729 poly(L-lysine) polymer Polymers 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 230000015556 catabolic process Effects 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 230000005764 inhibitory process Effects 0.000 description 1

- 238000004377 microelectronic Methods 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 238000011084 recovery Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/16—Indirect frequency synthesis, i.e. generating a desired one of a number of predetermined frequencies using a frequency- or phase-locked loop

- H03L7/18—Indirect frequency synthesis, i.e. generating a desired one of a number of predetermined frequencies using a frequency- or phase-locked loop using a frequency divider or counter in the loop

- H03L7/197—Indirect frequency synthesis, i.e. generating a desired one of a number of predetermined frequencies using a frequency- or phase-locked loop using a frequency divider or counter in the loop a time difference being used for locking the loop, the counter counting between numbers which are variable in time or the frequency divider dividing by a factor variable in time, e.g. for obtaining fractional frequency division

- H03L7/1974—Indirect frequency synthesis, i.e. generating a desired one of a number of predetermined frequencies using a frequency- or phase-locked loop using a frequency divider or counter in the loop a time difference being used for locking the loop, the counter counting between numbers which are variable in time or the frequency divider dividing by a factor variable in time, e.g. for obtaining fractional frequency division for fractional frequency division

- H03L7/1976—Indirect frequency synthesis, i.e. generating a desired one of a number of predetermined frequencies using a frequency- or phase-locked loop using a frequency divider or counter in the loop a time difference being used for locking the loop, the counter counting between numbers which are variable in time or the frequency divider dividing by a factor variable in time, e.g. for obtaining fractional frequency division for fractional frequency division using a phase accumulator for controlling the counter or frequency divider

- H03L7/1978—Indirect frequency synthesis, i.e. generating a desired one of a number of predetermined frequencies using a frequency- or phase-locked loop using a frequency divider or counter in the loop a time difference being used for locking the loop, the counter counting between numbers which are variable in time or the frequency divider dividing by a factor variable in time, e.g. for obtaining fractional frequency division for fractional frequency division using a phase accumulator for controlling the counter or frequency divider using a cycle or pulse removing circuit

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

Landscapes

- Stabilization Of Oscillater, Synchronisation, Frequency Synthesizers (AREA)

Abstract

Description

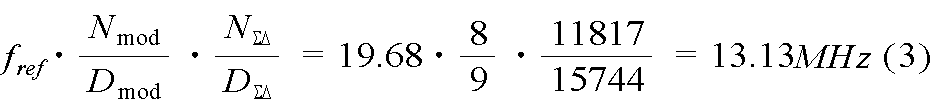

| fvco | fref | R | Nmod | Dmod | K | P | S | NΣΔ | DΣΔ |

| 905.29MHz | 19.68MHz | 1 | 8 | 9 | 4 | 12 | 3 | 11817 | 15744 |

Claims (44)

- 기준신호를 기초로 하여 위상동기루프(PLL)로부터 주파수 신호를 발생하는 단계와,상기 PLL의 피드백 루프에서의 주파수 체감기(frequency divider)를 상기 PLL의 루프 대역폭 밖으로 소정 차수의 스퓨리어스 신호(spurious signal)를 이동시키는 값으로 설정함으로써 상기 주파수 신호로부터 잡음을 제거하는 단계를 포함하고,상기 주파수 체감기의 설정은상기 주파수 체감기에서의 스왈로 카운터(swallow counter)와 프로그램 카운터(program counter) 중 적어도 하나를 상기 PLL의 루프 대역폭 밖으로 상기 소정 차수의 스퓨리어스 신호를 이동시키는 값으로 조정하는 것을 포함하는 잡음억제방법.

- 제 1 항에 있어서,상기 루프 대역폭은 상기 PLL에서 루프필터의 컷오프 주파수에 의해 정의되고, 상기 루프 대역폭은 상기 PLL로부터 발생된 주파수 신호와 상기 PLL에서의 루프필터의 컷오프 주파수 사이에 있는 주파수 범위에 해당하는 잡음억제방법.

- 제 1 항에 있어서,상기 잡음은 상기 스왈로 카운터와 상기 프로그램 카운터 중 적어도 하나를 상기 PLL의 루프 대역폭 밖으로 1차 스퓨리어스 신호를 이동시키는 값으로 조정함으로써 제거되는 잡음억제방법.

- 제 1 항에 있어서,상기 스왈로 카운터와 상기 프로그램 카운터 중 적어도 하나는 시그마-델타(Sigma-Delta) 변조기에 의해 설정되고,상기 PLL의 루프 대역폭을 기초로 하여 상기 시그마-델타 변조기의 변조비를 계산하는 단계와,상기 시그마-델타 변조기가 계산한 상기 변조비를 기초로 상기 스왈로 카운터와 상기 프로그램 카운터 중 적어도 하나의 값을 설정하는 단계를 더 포함하는 잡음억제방법.

- 제 1 항에 있어서,상기 스퓨리어스 신호는 상기 PLL의 위상 및 주파수 검출기와 전하펌프 중 적어도 하나에 대한 부정합(mismatch)에 의해 발생되는 잡음억제방법.

- 제 1 항에 있어서,상기 스왈로 카운터와 상기 프로그램 카운터 중 적어도 하나의 값은 상기 시그마-델타 변조기의 변조비를 기초로 제어되는 잡음억제방법.

- 제 6 항에 있어서,상기 변조비의 분자(NΣΔ)는 상기 변조비의 분모(DΣΔ)의 적어도 50%이고,기준변조기를 이용해 상기 PLL에 입력되는 상기 기준신호를 변조하는 단계를 더 포함하고, 상기 기준변조기는 Nmod가 Dmod의 적어도 50%이도록 변조비(Nmod/Dmod)를 갖는 잡음억제방법.

- 제 1 항에 있어서,상기 스퓨리어스 신호는 상기 PLL에서의 위상 및 주파수 검출기와 전하펌프 중 적어도 하나에서의 부정합으로 인해 발생되고, 상기 전하펌프에서의 부정합은 업 다운(up and down) 전류소스 사이의 부정합을 포함하며, 상기 스퓨리어스 신호는 상기 위상 및 주파수 검출기에서의 업 다운 신호경로 간의 부정합으로 인해 발생되는 잡음억제방법.

- 제 1 항에 있어서,상기 주파수 체감기의 값은 상기 스퓨리어스 신호를 제거하기 위한 시그마 델타 변조기의 변조비를 기초로 설정되는 잡음억제방법.

- 제 1 항에 있어서,상기 기준신호를 상기 PLL의 위상 및 주파수 검출기에 입력하기 위한 분수 고정값으로 변경하는 단계를 더 포함하고, 상기 분수 고정값은 상기 소정 차수의 스퓨리어스 신호를 또한 이동시키는 잡음억제방법.

- 제 1 항에 있어서,상기 스왈로 카운터와 상기 프로그램 카운터는 모두 상기 소정 차수의 스퓨리어스 신호를 상기 PLL의 루프 대역폭 밖으로 이동시키도록 조정되고, 상기 스왈로 카운터와 상기 프로그램 카운터의 값은 상기 시그마 델타 변조기의 변조비를 기초로 제어되며, 상기 스왈로 카운터와 상기 프로그램 카운터의 값은 상기 소정 차수의 스퓨리어스 신호를 상기 PLL의 루프 대역폭 밖으로 이동시키는 상기 값을 발생하도록 제어되는 잡음억제방법.

- 제 11 항에 있어서,상기 PLL에 입력되는 상기 기준신호를 변조하는 단계와,상기 변조된 기준신호와 변조되지 않은 기준신호의 고조파가 일치하지 않는 한, 상기 PLL에 대한 비교신호로서 상기 변조된 기준신호를 사용하는 단계를 더 포함하며,상기 PLL의 주파수 신호(fvco)는 하기 식:에 따라 발생되고,여기서, fref는 기준신호이며, R은 기준신호 분주기의 값이고, Nmod 및 Dmod는 상기 기준신호에 대한 변조비를 정의하고, P는 프로그램 카운터의 값이며, S는 스왈로 카운터의 값이고, NΣΔ 및 DΣΔ는 시그마-델타 변조기의 변조비이며, 그리고 K는 펄스 스왈로 주파수 체감기에서 프리스케일러의 값인 잡음억제방법.

- 기준신호를 기초로 하여 주파수 신호를 발생하는 위상동기루프(PLL)와,소정 차수의 스퓨리어스 신호를 상기 PLL의 루프 대역폭 밖으로 이동시키는 잡음 억제기(noise suppressor)를 구비하고,상기 잡음 억제기는 상기 위상동기루프의 피드백 루프에서 주파수 체감기과, 상기 소정 차수의 스퓨리어스 신호를 상기 위상동기루프(PLL)의 루프 대역폭 밖으로 이동시키는 값으로 상기 주파수 체감기를 설정하는 컨트롤러를 포함하며,상기 주파수 체감기는 스왈로 카운터와 프로그램 카운터를 포함하고, 상기 스왈로 카운터와 프로그램 카운터의 값은 시그마 델타 변조기의 변조비를 기초로 제어되며, 상기 스왈로 카운터와 프로그램 카운터의 값은 상기 소정 차수의 스퓨리어스 신호를 상기 위상동기루프(PLL)의 루프 대역폭 밖으로 이동시키는 값을 발생하도록 제어되는 주파수 발생기.

- 제 14 항에 있어서,상기 위상동기루프는 루프필터를 포함하고, 상기 루프 대역폭은 상기 루프필터의 컷오프 주파수에 의해 정의되며, 상기 루프 대역폭은 상기 PLL로부터 발생된 주파수 신호와 상기 루프필터의 컷오프 주파수 사이에 있는 주파수 범위에 해당하는 주파수 발생기.

- 제 14 항에 있어서,상기 스왈로 카운터와 상기 프로그램 카운터의 값은 1차 스퓨리어스 신호를 상기 위상동기루프의 루프 대역폭 밖으로 이동시키도록 제어되는 주파수 발생기.

- 제 14 항에 있어서,상기 위상동기루프에 입력되는 상기 기준신호를 변조하는 변조기를 더 구비하고, 상기 스퓨리어스 신호는 상기 PLL의 위상 및 주파수 검출기와 전하펌프 중 적어도 하나에 대한 부정합으로 인해 발생되는 주파수 발생기.

- 제 14 항에 있어서,상기 기준신호를 상기 PLL의 위상 및 주파수 검출기에 입력하기 위한 분수 고정값으로 변경하는 주파수 변환기(frequency shifter)를 더 구비하고, 상기 분수 고정값은 상기 소정 차수의 스퓨리어스 신호를 또한 이동시키는 주파수 발생기.

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US42106002P | 2002-10-25 | 2002-10-25 | |

| US60/421,060 | 2002-10-25 | ||

| US10/689,986 US6952125B2 (en) | 2002-10-25 | 2003-10-22 | System and method for suppressing noise in a phase-locked loop circuit |

| US10/689,986 | 2003-10-22 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20050070078A KR20050070078A (ko) | 2005-07-05 |

| KR100997490B1 true KR100997490B1 (ko) | 2010-12-01 |

Family

ID=32179836

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020057006976A KR100997490B1 (ko) | 2002-10-25 | 2003-10-23 | 위상동기루프회로에서의 잡음억제용 시스템 및 방법 |

Country Status (9)

| Country | Link |

|---|---|

| US (1) | US6952125B2 (ko) |

| EP (1) | EP1556952A4 (ko) |

| JP (1) | JP4754825B2 (ko) |

| KR (1) | KR100997490B1 (ko) |

| AU (1) | AU2003284893A1 (ko) |

| CA (1) | CA2502841A1 (ko) |

| HK (1) | HK1081739A1 (ko) |

| TW (1) | TWI342674B (ko) |

| WO (1) | WO2004040898A2 (ko) |

Families Citing this family (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7288998B2 (en) * | 2003-05-02 | 2007-10-30 | Silicon Laboratories Inc. | Voltage controlled clock synthesizer |

| US7436227B2 (en) * | 2003-05-02 | 2008-10-14 | Silicon Laboratories Inc. | Dual loop architecture useful for a programmable clock source and clock multiplier applications |

| US7295077B2 (en) * | 2003-05-02 | 2007-11-13 | Silicon Laboratories Inc. | Multi-frequency clock synthesizer |

| US7187241B2 (en) * | 2003-05-02 | 2007-03-06 | Silicon Laboratories Inc. | Calibration of oscillator devices |

| US7113009B2 (en) * | 2004-03-24 | 2006-09-26 | Silicon Laboratories Inc. | Programmable frequency divider |

| US7405601B2 (en) * | 2004-05-03 | 2008-07-29 | Silicon Laboratories Inc. | High-speed divider with pulse-width control |

| US7187216B2 (en) * | 2004-05-03 | 2007-03-06 | Silicon Laboratories Inc. | Phase selectable divider circuit |

| KR100723152B1 (ko) | 2005-05-27 | 2007-05-30 | 삼성전기주식회사 | 주파수 분주기 및 이를 이용한 위상 동기 루프 장치 |

| US7406297B2 (en) * | 2005-05-30 | 2008-07-29 | Semiconductor Energy Laboratory Co., Ltd. | Clock generation circuit and semiconductor device provided therewith |

| KR100616688B1 (ko) * | 2005-06-21 | 2006-08-28 | 삼성전기주식회사 | 저분주비 프로그램가능 주파수 분주기 및 그 방법 |

| TWI282218B (en) * | 2005-07-01 | 2007-06-01 | Realtek Semiconductor Corp | Method of generating spread spectrum and/or over-clock and its circuit thereof |

| WO2007004465A1 (ja) * | 2005-07-04 | 2007-01-11 | Matsushita Electric Industrial Co., Ltd. | 半導体装置およびそれを用いた無線回路装置 |

| US7372341B2 (en) * | 2006-04-25 | 2008-05-13 | Sun Microsystems, Inc. | Noise immunity circuitry for phase locked loops and delay locked loops |

| US7551009B2 (en) * | 2007-02-28 | 2009-06-23 | Silicon Laboratories Inc. | High-speed divider with reduced power consumption |

| TWI355199B (en) * | 2007-03-26 | 2011-12-21 | Realtek Semiconductor Corp | Display control device and method |

| US7929929B2 (en) * | 2007-09-25 | 2011-04-19 | Motorola Solutions, Inc. | Method and apparatus for spur reduction in a frequency synthesizer |

| CN101221230B (zh) * | 2007-12-26 | 2010-10-06 | 西安华迅微电子有限公司 | 一种多通道公共相位噪声的抑制装置及抑制方法 |

| GB0804342D0 (en) * | 2008-03-07 | 2008-04-16 | Cambridge Silicon Radio Ltd | Charge transfer in a phase-locked loop |

| US7983378B2 (en) * | 2008-06-30 | 2011-07-19 | Intel Corporation | Extended multi-modulus prescaler |

| US8121569B2 (en) * | 2008-09-30 | 2012-02-21 | Intel Corporation | Frequency generation techniques |

| WO2010096770A2 (en) * | 2009-02-20 | 2010-08-26 | California Institute Of Technology | Noise suppression techniques in high precision long-term frequency/timing measurements |

| TWI382671B (zh) * | 2009-03-13 | 2013-01-11 | Ncku Res & Dev Foundation | 可重新組態之積分三角調變模組 |

| US8941443B1 (en) * | 2012-03-01 | 2015-01-27 | Rockwell Collins, Inc. | Electronically tuned cavity filter |

| CN102931984B (zh) * | 2012-09-26 | 2014-11-19 | 成都嘉纳海威科技有限责任公司 | 一种用于毫米波超宽带频率合成器 |

| GB2533556A (en) * | 2014-12-16 | 2016-06-29 | Nordic Semiconductor Asa | Oscillator calibration |

| US9444465B1 (en) * | 2015-03-23 | 2016-09-13 | Peregrine Semiconductor Corporation | Low phase noise frequency divider |

| US9553714B2 (en) * | 2015-06-26 | 2017-01-24 | Broadcom Corporation | Frequency multiplier for a phase-locked loop |

| US10715157B2 (en) * | 2016-03-31 | 2020-07-14 | Apple Inc. | Methods and mobile communication devices for performing spur relocation for phase-locked loops |

| US9998129B1 (en) | 2017-09-21 | 2018-06-12 | Qualcomm Incorporated | PLL post divider phase continuity |

| CN110764439B (zh) * | 2018-07-25 | 2022-09-06 | 上海英威腾工业技术有限公司 | 伺服驱动脉冲输出分频器及其使用方法 |

| JP7420537B2 (ja) * | 2019-11-26 | 2024-01-23 | ローム株式会社 | 位相ロックループ回路 |

| US11165432B1 (en) * | 2020-11-06 | 2021-11-02 | Movellus Circuits, Inc. | Glitch-free digital controlled delay line apparatus and method |

| CN112491415A (zh) * | 2020-12-09 | 2021-03-12 | 北京中科飞鸿科技股份有限公司 | 一种超宽频带低杂散双锁相环频率源 |

| CN112636747A (zh) * | 2020-12-22 | 2021-04-09 | 成都华微电子科技有限公司 | 锁相环参考杂散快速仿真方法 |

| US11387834B1 (en) * | 2021-05-13 | 2022-07-12 | Texas Instruments Incorporated | Methods and apparatus to implement pulse swallowing circuitry in a phase frequency detector |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20030062959A1 (en) | 2001-10-02 | 2003-04-03 | Kazutoshi Tsuda | Fractional N frequency synthesizer |

| US6566964B1 (en) | 1999-10-29 | 2003-05-20 | Matsushita Electric Industrial Co., Ltd. | Frequency synthesizer and oscillation frequency control method |

| US6603360B2 (en) | 2001-03-23 | 2003-08-05 | Samsung Electronics Co., Ltd. | Phase locked loop circuit for a fractional-N frequency synthesizer |

| US6642800B2 (en) | 2002-04-04 | 2003-11-04 | Ati Technologies, Inc. | Spurious-free fractional-N frequency synthesizer with multi-phase network circuit |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5038117A (en) * | 1990-01-23 | 1991-08-06 | Hewlett-Packard Company | Multiple-modulator fractional-N divider |

| US5070310A (en) * | 1990-08-31 | 1991-12-03 | Motorola, Inc. | Multiple latched accumulator fractional N synthesis |

| JPH10247851A (ja) * | 1997-03-04 | 1998-09-14 | Hitachi Denshi Ltd | フラクショナル−n方式の周波数シンセサイザおよびそれを使用した中継装置 |

| JPH10285027A (ja) * | 1997-04-03 | 1998-10-23 | Sony Tektronix Corp | Pll発振回路 |

| US5825253A (en) * | 1997-07-15 | 1998-10-20 | Qualcomm Incorporated | Phase-locked-loop with noise shaper |

| US5777521A (en) * | 1997-08-12 | 1998-07-07 | Motorola Inc. | Parallel accumulator fractional-n frequency synthesizer |

| JPH11195986A (ja) * | 1997-12-26 | 1999-07-21 | Hitachi Denshi Ltd | 集積回路 |

| US20020030546A1 (en) * | 2000-05-31 | 2002-03-14 | Keating Pierce Vincent | Frequency synthesizer having an offset frequency summation path |

| JP3415574B2 (ja) * | 2000-08-10 | 2003-06-09 | Necエレクトロニクス株式会社 | Pll回路 |

| KR100346839B1 (ko) * | 2000-10-10 | 2002-08-03 | 삼성전자 주식회사 | 시그마-델타 변조기를 이용한 분수-n 주파수 합성 장치및 그 방법 |

| JP3548557B2 (ja) * | 2001-10-02 | 2004-07-28 | Nec化合物デバイス株式会社 | フラクショナルn周波数シンセサイザ |

-

2003

- 2003-10-22 US US10/689,986 patent/US6952125B2/en not_active Expired - Lifetime

- 2003-10-23 AU AU2003284893A patent/AU2003284893A1/en not_active Abandoned

- 2003-10-23 EP EP03779214A patent/EP1556952A4/en not_active Withdrawn

- 2003-10-23 JP JP2004548450A patent/JP4754825B2/ja not_active Expired - Lifetime

- 2003-10-23 KR KR1020057006976A patent/KR100997490B1/ko active IP Right Grant

- 2003-10-23 CA CA002502841A patent/CA2502841A1/en not_active Abandoned

- 2003-10-23 WO PCT/US2003/033709 patent/WO2004040898A2/en active Application Filing

- 2003-10-24 TW TW092129621A patent/TWI342674B/zh not_active IP Right Cessation

-

2006

- 2006-02-08 HK HK06101646A patent/HK1081739A1/xx not_active IP Right Cessation

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6566964B1 (en) | 1999-10-29 | 2003-05-20 | Matsushita Electric Industrial Co., Ltd. | Frequency synthesizer and oscillation frequency control method |

| US6603360B2 (en) | 2001-03-23 | 2003-08-05 | Samsung Electronics Co., Ltd. | Phase locked loop circuit for a fractional-N frequency synthesizer |

| US20030062959A1 (en) | 2001-10-02 | 2003-04-03 | Kazutoshi Tsuda | Fractional N frequency synthesizer |

| US6642800B2 (en) | 2002-04-04 | 2003-11-04 | Ati Technologies, Inc. | Spurious-free fractional-N frequency synthesizer with multi-phase network circuit |

Also Published As

| Publication number | Publication date |

|---|---|

| US6952125B2 (en) | 2005-10-04 |

| AU2003284893A8 (en) | 2004-05-25 |

| AU2003284893A1 (en) | 2004-05-25 |

| CA2502841A1 (en) | 2004-05-13 |

| WO2004040898A3 (en) | 2004-09-02 |

| TWI342674B (en) | 2011-05-21 |

| HK1081739A1 (en) | 2006-05-19 |

| WO2004040898A2 (en) | 2004-05-13 |

| EP1556952A4 (en) | 2005-12-21 |

| US20040085103A1 (en) | 2004-05-06 |

| JP2006504352A (ja) | 2006-02-02 |

| JP4754825B2 (ja) | 2011-08-24 |

| KR20050070078A (ko) | 2005-07-05 |

| EP1556952A2 (en) | 2005-07-27 |

| TW200421715A (en) | 2004-10-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100997490B1 (ko) | 위상동기루프회로에서의 잡음억제용 시스템 및 방법 | |

| US9838026B2 (en) | Apparatus and methods for fractional-N phase-locked loops with multi-phase oscillators | |

| JP4536734B2 (ja) | サブμ技術に適したデジタル位相同期回路 | |

| JP2756728B2 (ja) | 多段蓄積器シグマデルタ分数nの合成 | |

| US9215062B1 (en) | Low-noise flexible frequency clock generation from two fixed-frequency references | |

| US7274231B1 (en) | Low jitter frequency synthesizer | |

| US6873213B2 (en) | Fractional N frequency synthesizer | |

| US20100321120A1 (en) | Fractional-n frequency synthesizer and method thereof | |

| KR100819390B1 (ko) | 2개의 위상 동기 루프를 사용한 주파수 합성기 | |

| US9628066B1 (en) | Fast switching, low phase noise frequency synthesizer | |

| JP4903969B2 (ja) | 回転周波数合成器 | |

| EP1729432B1 (en) | Generation of a phase locked loop output signal having reduced spurious spectral components | |

| Fridi et al. | A low power fully-integrated 76-81 GHz ADPLL for automotive radar applications with 150 MHz/us FMCW chirp rate and-95dBc/Hz phase noise at 1 MHz offset in FDSOI | |

| JPH0451098B2 (ko) | ||

| US7579916B1 (en) | Low noise frequency synthesizer | |

| US9077592B2 (en) | Low phase-noise indirect frequency synthesizer | |

| WO2006065478A2 (en) | Method and apparatus for generating a phase-locked output signal | |

| CN100362743C (zh) | 用于抑制锁相环电路中的噪声的系统和方法 | |

| KR101251708B1 (ko) | 저주파수 기생 발산의 제거를 이용하는 광대역 주파수 합성기 | |

| US6636086B2 (en) | High performance microwave synthesizer using multiple-modulator fractional-N divider | |

| JP2003179490A (ja) | フラクショナルn周波数シンセサイザ | |

| US20140184274A1 (en) | Fractional-n frequency synthesizer with low quantization noise | |

| Eikenbroek | Design of a Delta-Sigma Synthesizer for a Bluetooth® Transmitter | |

| KR100638894B1 (ko) | Σ△ 변조를 이용한 프로그램가능 주파수 분주기 | |

| JPH0348699B2 (ko) |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20131118 Year of fee payment: 4 |

|

| FPAY | Annual fee payment |

Payment date: 20141117 Year of fee payment: 5 |

|

| FPAY | Annual fee payment |

Payment date: 20151124 Year of fee payment: 6 |

|

| FPAY | Annual fee payment |

Payment date: 20161124 Year of fee payment: 7 |

|

| FPAY | Annual fee payment |

Payment date: 20171117 Year of fee payment: 8 |

|

| FPAY | Annual fee payment |

Payment date: 20181120 Year of fee payment: 9 |

|

| FPAY | Annual fee payment |

Payment date: 20191118 Year of fee payment: 10 |