KR100956716B1 - Dc 소스/드레인 아래 산화물 홀을 갖는 차별적 soi - Google Patents

Dc 소스/드레인 아래 산화물 홀을 갖는 차별적 soi Download PDFInfo

- Publication number

- KR100956716B1 KR100956716B1 KR1020067013487A KR20067013487A KR100956716B1 KR 100956716 B1 KR100956716 B1 KR 100956716B1 KR 1020067013487 A KR1020067013487 A KR 1020067013487A KR 20067013487 A KR20067013487 A KR 20067013487A KR 100956716 B1 KR100956716 B1 KR 100956716B1

- Authority

- KR

- South Korea

- Prior art keywords

- soi

- region

- substrate

- delete delete

- node

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/20—Deposition of semiconductor materials on a substrate, e.g. epitaxial growth solid phase epitaxy

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

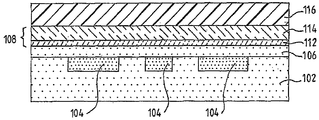

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/201—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates the substrates comprising an insulating layer on a semiconductor body, e.g. SOI

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6758—Thin-film transistors [TFT] characterised by the insulating substrates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/113—Isolations within a component, i.e. internal isolations

- H10D62/115—Dielectric isolations, e.g. air gaps

- H10D62/116—Dielectric isolations, e.g. air gaps adjoining the input or output regions of field-effect devices, e.g. adjoining source or drain regions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Thin Film Transistor (AREA)

- Element Separation (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/754,320 US6958516B2 (en) | 2004-01-08 | 2004-01-08 | Discriminative SOI with oxide holes underneath DC source/drain |

| US10/754,320 | 2004-01-08 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20060123434A KR20060123434A (ko) | 2006-12-01 |

| KR100956716B1 true KR100956716B1 (ko) | 2010-05-06 |

Family

ID=34739363

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020067013487A Expired - Fee Related KR100956716B1 (ko) | 2004-01-08 | 2005-01-06 | Dc 소스/드레인 아래 산화물 홀을 갖는 차별적 soi |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US6958516B2 (enExample) |

| EP (1) | EP1706905A1 (enExample) |

| JP (1) | JP5527922B2 (enExample) |

| KR (1) | KR100956716B1 (enExample) |

| CN (1) | CN1906762A (enExample) |

| IL (1) | IL176686A (enExample) |

| TW (1) | TWI339414B (enExample) |

| WO (1) | WO2005069373A1 (enExample) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7160788B2 (en) * | 2004-08-23 | 2007-01-09 | Micron Technology, Inc. | Methods of forming integrated circuits |

| US7202513B1 (en) | 2005-09-29 | 2007-04-10 | International Business Machines Corporation | Stress engineering using dual pad nitride with selective SOI device architecture |

| US7659172B2 (en) * | 2005-11-18 | 2010-02-09 | International Business Machines Corporation | Structure and method for reducing miller capacitance in field effect transistors |

| JP4867396B2 (ja) * | 2006-03-01 | 2012-02-01 | セイコーエプソン株式会社 | 半導体装置及びその製造方法 |

| US7482656B2 (en) * | 2006-06-01 | 2009-01-27 | International Business Machines Corporation | Method and structure to form self-aligned selective-SOI |

| US7795910B1 (en) | 2007-08-21 | 2010-09-14 | Marvell International Ltd. | Field-programmable gate array using charge-based nonvolatile memory |

| US8921190B2 (en) | 2008-04-08 | 2014-12-30 | International Business Machines Corporation | Field effect transistor and method of manufacture |

| US7989893B2 (en) * | 2008-08-28 | 2011-08-02 | International Business Machines Corporation | SOI body contact using E-DRAM technology |

| CN102064097B (zh) * | 2009-11-17 | 2012-11-07 | 中国科学院上海微系统与信息技术研究所 | 一种混晶材料的制备方法及用该材料制备的半导体器件 |

| CN101924138B (zh) * | 2010-06-25 | 2013-02-06 | 中国科学院上海微系统与信息技术研究所 | 防止浮体及自加热效应的mos器件结构及其制备方法 |

| CN101986435B (zh) * | 2010-06-25 | 2012-12-19 | 中国科学院上海微系统与信息技术研究所 | 防止浮体及自加热效应的mos器件结构的制造方法 |

| PT2446792E (pt) | 2010-10-29 | 2015-02-18 | Gruppo Cimbali Spa | Peça de extremidade substituível para uma boca de descarga de vapor de uma máquina de café |

| CN102214684B (zh) * | 2011-06-03 | 2012-10-10 | 清华大学 | 一种具有悬空源漏的半导体结构及其形成方法 |

| US9892910B2 (en) * | 2015-05-15 | 2018-02-13 | International Business Machines Corporation | Method and structure for forming a dense array of single crystalline semiconductor nanocrystals |

| US9722057B2 (en) * | 2015-06-23 | 2017-08-01 | Global Foundries Inc. | Bipolar junction transistors with a buried dielectric region in the active device region |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20010095471A (ko) * | 2000-03-30 | 2001-11-07 | 윤종용 | 에스오아이 기판과 그 제조방법 및 이를 이용한에스오아이 엠오에스에프이티 |

Family Cites Families (28)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| NL8006339A (nl) * | 1979-11-21 | 1981-06-16 | Hitachi Ltd | Halfgeleiderinrichting en werkwijze voor de vervaar- diging daarvan. |

| JPS577161A (en) * | 1980-06-16 | 1982-01-14 | Toshiba Corp | Mos semiconductor device |

| JPS59119723A (ja) * | 1982-12-27 | 1984-07-11 | Toshiba Corp | 半導体装置の製造方法 |

| JPS61265859A (ja) * | 1985-05-20 | 1986-11-25 | Toshiba Corp | 相補型mos半導体装置 |

| US4683637A (en) * | 1986-02-07 | 1987-08-04 | Motorola, Inc. | Forming depthwise isolation by selective oxygen/nitrogen deep implant and reaction annealing |

| US4810664A (en) * | 1986-08-14 | 1989-03-07 | Hewlett-Packard Company | Method for making patterned implanted buried oxide transistors and structures |

| JPH0794721A (ja) * | 1993-09-24 | 1995-04-07 | Nippon Steel Corp | 半導体装置及びその製造方法 |

| US5382818A (en) * | 1993-12-08 | 1995-01-17 | Philips Electronics North America Corporation | Lateral semiconductor-on-insulator (SOI) semiconductor device having a buried diode |

| US5841126A (en) * | 1994-01-28 | 1998-11-24 | California Institute Of Technology | CMOS active pixel sensor type imaging system on a chip |

| US5489792A (en) * | 1994-04-07 | 1996-02-06 | Regents Of The University Of California | Silicon-on-insulator transistors having improved current characteristics and reduced electrostatic discharge susceptibility |

| US5583368A (en) | 1994-08-11 | 1996-12-10 | International Business Machines Corporation | Stacked devices |

| US5481126A (en) | 1994-09-27 | 1996-01-02 | Purdue Research Foundation | Semiconductor-on-insulator electronic devices having trench isolated monocrystalline active regions |

| DE4441901C2 (de) * | 1994-11-24 | 1998-07-02 | Siemens Ag | MOSFET auf SOI-Substrat und Verfahren zu dessen Herstellung |

| JPH08316335A (ja) * | 1995-05-18 | 1996-11-29 | Sony Corp | 半導体装置およびその製造方法 |

| US5712173A (en) | 1996-01-24 | 1998-01-27 | Advanced Micro Devices, Inc. | Method of making semiconductor device with self-aligned insulator |

| US5873364A (en) * | 1996-02-22 | 1999-02-23 | Kopelowicz; Alberto | Latex prophylactics |

| KR100226794B1 (ko) * | 1996-06-10 | 1999-10-15 | 김영환 | 모스펫 제조방법 |

| KR100281109B1 (ko) * | 1997-12-15 | 2001-03-02 | 김영환 | 에스오아이(soi)소자및그의제조방법 |

| US6214653B1 (en) * | 1999-06-04 | 2001-04-10 | International Business Machines Corporation | Method for fabricating complementary metal oxide semiconductor (CMOS) devices on a mixed bulk and silicon-on-insulator (SOI) substrate |

| US6333532B1 (en) * | 1999-07-16 | 2001-12-25 | International Business Machines Corporation | Patterned SOI regions in semiconductor chips |

| KR100304713B1 (ko) | 1999-10-12 | 2001-11-02 | 윤종용 | 부분적인 soi 구조를 갖는 반도체소자 및 그 제조방법 |

| US6376286B1 (en) | 1999-10-20 | 2002-04-23 | Advanced Micro Devices, Inc. | Field effect transistor with non-floating body and method for forming same on a bulk silicon wafer |

| US6429099B1 (en) * | 2000-01-05 | 2002-08-06 | International Business Machines Corporation | Implementing contacts for bodies of semiconductor-on-insulator transistors |

| US6287901B1 (en) | 2000-01-05 | 2001-09-11 | International Business Machines Corporation | Method and semiconductor structure for implementing dual plane body contacts for silicon-on-insulator (SOI) transistors |

| JP2002208696A (ja) * | 2001-01-11 | 2002-07-26 | Seiko Epson Corp | 半導体装置及びその製造方法 |

| JP4352616B2 (ja) | 2001-02-05 | 2009-10-28 | 株式会社デンソー | 半導体力学量センサとその製造方法 |

| US6531375B1 (en) * | 2001-09-18 | 2003-03-11 | International Business Machines Corporation | Method of forming a body contact using BOX modification |

| US6936522B2 (en) | 2003-06-26 | 2005-08-30 | International Business Machines Corporation | Selective silicon-on-insulator isolation structure and method |

-

2004

- 2004-01-08 US US10/754,320 patent/US6958516B2/en not_active Expired - Lifetime

-

2005

- 2005-01-03 TW TW094100107A patent/TWI339414B/zh not_active IP Right Cessation

- 2005-01-06 WO PCT/EP2005/050039 patent/WO2005069373A1/en not_active Ceased

- 2005-01-06 CN CNA2005800015468A patent/CN1906762A/zh active Pending

- 2005-01-06 EP EP05701449A patent/EP1706905A1/en not_active Withdrawn

- 2005-01-06 JP JP2006548301A patent/JP5527922B2/ja not_active Expired - Fee Related

- 2005-01-06 KR KR1020067013487A patent/KR100956716B1/ko not_active Expired - Fee Related

-

2006

- 2006-07-03 IL IL176686A patent/IL176686A/en not_active IP Right Cessation

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20010095471A (ko) * | 2000-03-30 | 2001-11-07 | 윤종용 | 에스오아이 기판과 그 제조방법 및 이를 이용한에스오아이 엠오에스에프이티 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20050151193A1 (en) | 2005-07-14 |

| TW200524047A (en) | 2005-07-16 |

| JP2007519239A (ja) | 2007-07-12 |

| TWI339414B (en) | 2011-03-21 |

| IL176686A0 (en) | 2006-10-31 |

| CN1906762A (zh) | 2007-01-31 |

| KR20060123434A (ko) | 2006-12-01 |

| IL176686A (en) | 2010-12-30 |

| WO2005069373A1 (en) | 2005-07-28 |

| US6958516B2 (en) | 2005-10-25 |

| EP1706905A1 (en) | 2006-10-04 |

| JP5527922B2 (ja) | 2014-06-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100735654B1 (ko) | 디커플링 캐패시터 및 그 제조 방법 | |

| KR100343288B1 (ko) | 에스오아이 모스 트랜지스터의 플로팅 바디 효과를제거하기 위한 에스오아이 반도체 집적회로 및 그 제조방법 | |

| KR100456691B1 (ko) | 이중격리구조를 갖는 반도체 소자 및 그 제조방법 | |

| CN101026157B (zh) | 半导体器件及其制作方法 | |

| US6518645B2 (en) | SOI-type semiconductor device and method of forming the same | |

| KR100956716B1 (ko) | Dc 소스/드레인 아래 산화물 홀을 갖는 차별적 soi | |

| US20080248615A1 (en) | Cmos structure for body ties in ultra-thin soi (utsoi) substrates | |

| JPH10242420A (ja) | 半導体装置およびその製造方法 | |

| KR100432887B1 (ko) | 다중격리구조를 갖는 반도체 소자 및 그 제조방법 | |

| US6436798B2 (en) | MOSFET device | |

| US20190019876A1 (en) | High voltage transistor using buried insulating layer as gate dielectric | |

| US10062704B2 (en) | Buried-channel MOSFET and a surface-channel MOSFET of a same type and fabrication method thereof | |

| US6469350B1 (en) | Active well schemes for SOI technology | |

| US6541822B2 (en) | Method of manufacturing an SOI type semiconductor that can restrain floating body effect | |

| KR19980058391A (ko) | Soi 반도체 소자 및 그의 제조방법 | |

| US5949103A (en) | MOSFET with tunneling insulation and fabrication method thereof | |

| EP0989613B1 (en) | SOI transistor with body contact and method of forming same | |

| JP2005039057A (ja) | 半導体装置およびその製造方法 | |

| US7517742B2 (en) | Area diode formation in SOI application | |

| KR100263475B1 (ko) | 반도체 소자의 구조 및 제조 방법 | |

| CN118231414B (zh) | Pdsoi晶体管及其制造方法 | |

| KR20030045634A (ko) | 반도체 장치와 그 제조 방법 | |

| KR100464535B1 (ko) | 반도체소자의 트랜지스터 형성 방법 | |

| KR100679833B1 (ko) | 반도체 소자 및 그 제조 방법 | |

| KR20080022275A (ko) | 디이모스 소자의 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0105 | International application |

St.27 status event code: A-0-1-A10-A15-nap-PA0105 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| A201 | Request for examination | ||

| E13-X000 | Pre-grant limitation requested |

St.27 status event code: A-2-3-E10-E13-lim-X000 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-3-3-R10-R18-oth-X000 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-3-3-R10-R18-oth-X000 |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U12-oth-PR1002 Fee payment year number: 1 |

|

| PG1601 | Publication of registration |

St.27 status event code: A-4-4-Q10-Q13-nap-PG1601 |

|

| LAPS | Lapse due to unpaid annual fee | ||

| PC1903 | Unpaid annual fee |

St.27 status event code: A-4-4-U10-U13-oth-PC1903 Not in force date: 20130430 Payment event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE |

|

| PC1903 | Unpaid annual fee |

St.27 status event code: N-4-6-H10-H13-oth-PC1903 Ip right cessation event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE Not in force date: 20130430 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |