KR100242523B1 - 반도체장치의 소자격리방법 - Google Patents

반도체장치의 소자격리방법 Download PDFInfo

- Publication number

- KR100242523B1 KR100242523B1 KR1019970067209A KR19970067209A KR100242523B1 KR 100242523 B1 KR100242523 B1 KR 100242523B1 KR 1019970067209 A KR1019970067209 A KR 1019970067209A KR 19970067209 A KR19970067209 A KR 19970067209A KR 100242523 B1 KR100242523 B1 KR 100242523B1

- Authority

- KR

- South Korea

- Prior art keywords

- trench

- hard mask

- mask layer

- filler

- semiconductor substrate

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/76224—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using trench refilling with dielectric materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/308—Chemical or electrical treatment, e.g. electrolytic etching using masks

- H01L21/3081—Chemical or electrical treatment, e.g. electrolytic etching using masks characterised by their composition, e.g. multilayer masks, materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/308—Chemical or electrical treatment, e.g. electrolytic etching using masks

- H01L21/3083—Chemical or electrical treatment, e.g. electrolytic etching using masks characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane

- H01L21/3086—Chemical or electrical treatment, e.g. electrolytic etching using masks characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane characterised by the process involved to create the mask, e.g. lift-off masks, sidewalls, or to modify the mask, e.g. pre-treatment, post-treatment

Abstract

본 발명은 반도체장치의 소자격리방법에 관한 것으로서 반도체기판 상에 제 1 하드마스크층 및 제 2 하드마스크층을 순차적으로 형성하고 상기 반도체기판이 노출되도록 패터닝하여 소자격리영역과 활성영역을 한정하는 공정과, 상기 반도체기판의 노출된 부분에 소정 깊이의 깊은 트렌치를 형성하고 상기 트렌치의 표면에 버퍼산화막을 형성하는 공정과, 상기 제 2 하드마스크층 상에 상기 트렌치를 채우도록 제 1 및 제 2 필러를 순차적으로 형성하는 공정과, 상기 제 2 필러를 상기 트렌치 내에만 잔류하도록 에치 백하고 상기 제 1 필러와 상기 제 2 하드마스크층을 건식 식각 방법으로 선택적으로 제거하는 공정과, 상기 제 1 하드마스크층을 제거하는 공정을 구비한다. 따라서, 이후 공정인 게이트 형성시 식각 잔류물이 남는 것을 방지할 수 있어 소자의 신뢰성을 향상시킬 수 있다.

Description

본 발명은 반도체장치의 소자격리방법에 관한 것으로서, 특히, 깊은 트렌치(deep trench)를 이용한 반도체장치의 소자격리방법에 관한 것이다.

반도체장치의 집적화가 거듭되면서 반도체장치의 상당한 면적을 점유하는 소자격리영역을 줄이기 위한 기술 개발이 활발히 진행되고 있다.

반도체장치의 집적화가 거듭되면서 반도체장치의 상당한 면적을 점유하는 소자격리영역을 줄이기 위한 기술 개발이 활발히 진행되고 있다.

일반적으로 반도체장치는 LOCOS(Local Oxidation of Silicon) 방법으로 소자를 격리하였다. LOCOS 방법은 활성영역을 한정하는 산화마스크인 질화막과 반도체기판의 열적 특성이 다르기 때문에 발생하는 스트레스를 해소하기 위하여 질화막과 반도체기판 사이에 박막의 버퍼산화막(buffer oxide)을 형성하고 산화시켜 소자격리영역으로 이용되는 필드산화막를 형성한다. 상기에서 필드산화막은 반도체기판의 수직 방향으로 성장할 뿐만 아니라 산화체(Oxidant : 02)가 버퍼산화막을 따라 수평 방향으로도 확산되므로 질화막의 패턴 엣지(edage)밑으로 성장되게 되는 특징을 갖는다.

이와같이 필드산화막이 활성 영역을 잠식하는 현상을 그 형상이 새의 부리 모양과 유사하여 버즈 비크(Bird's Beak)이라 한다. 이러한 버드 비크의 길이는 필드산화막 두께의 1/2이나 된다. 그러므로, 활성 영역의 크기가 감소되는 것을 줄이기 위하여는 버즈 비크의 길이를 최소화 하여야 한다.

버즈 비크의 길이를 줄이기 위한 방법으로 필드산화막의 두께를 감소시키는 방식이 도입되었으나 16M DRAM급 이상에서 필드산화막의 두께를 감소시키면 배선과 반도체기판 사이의 정전 용량이 증가되어 신호전달 속도가 저하되는 문제가 발생된다. 또한, 소자의 게이트로 사용되는 배선에 의해 소자 사이의 격리영역에 형성되는 기생 트랜지스터의 문턱전압(Vt)이 저하되어 소자 사이의 격리특성이 저하되는 문제점이 있다.

따라서, 버즈 비크의 길이를 감소시키면서 소자격리를 하는 방법이 개발되었다. 버즈 비크의 길이를 감소시키면서 소자격리를 하는 방법으로는 스트레스 완충용 버퍼산화막의 두께를 낮추고 반도체기판과 질화막 사이에 다결정실리콘층을 개입시킨 PBLOCOS(Poly Si Buffered LOCOS), 버퍼산화막의 측벽을 질화막으로 보호하는 SILO(Sealed Interface LOCOS), 그리고, 반도체기판 내에 필드산화막을 형성시키는 리세스(Recessed) LOCOS 기술들이 있다.

그러나, 상기 기술들은 격리 영역 표면의 평탄도와 정밀한 디자인 룰(Design Rule) 등의 이유로 256M DRAM급 이상의 집적도를 갖는 차세대 소자의 소자격리기술로 적합하지 않게 되었다.

따라서, 기존의 여러 소자격리기술들의 문제점을 극복할 수 있는 BOX(buried oxide)형 낮은트렌치소자격리(shallow trench isolation) 기술이 개발되었다. BOX형 소자격리기술 반도체기판에 트렌치를 형성하고 화학기상증착(Chemical Vapor Deposition : 이하, CVD라 칭함) 방법으로 산화실리콘 또는 불순물이 도핑되지 않은 다결정실리콘을 매립한 구조를 갖는다. 그러므로, 버즈 비크가 발생되지 않아 활성영역의 손실이 전혀 없으며, 또한, 산화막을 메립하고 에치 백(etch back)하여 평탄한 표면을 얻을 수 있다.

또한, 고전압 소자는 통상의 STI로 충분한 소자격리 효과를 얻을 수 없으므로 깊은트렌치소자격리(deep trench isolation) 기술이 개발되었다.

도 1a 내지 도 1d는 종래 기술에 따른 깊은 트렌치를 이용한 소자격리방법을 도시하는 공정도이다.

도 1a를 참조하면, 반도체기판(11) 상에 열산화 방법으로 제 1 버퍼산화막(13)을 형성한다. 그리고, 제 1 버퍼산화막(13) 상에 화학기상증착(Chemical Vapor Deposition : 이하, CVD라 칭함) 방법으로 질화실리콘 및 산화실리콘을 순차적으로 증착하여 제 1 하드마스크층(15) 및 제 2 하드마스크층(17)을 형성한다. 그리고, 제 2 하드마스크층(17) 상에 포토레지스트(18)를 도포한 후 노광 및 현상하여 소정 부분을 노출시킨다. 그 다음, 잔류하는 포토레지스트(18)를 마스크로 사용하여 반도체기판(11)의 소정 부분이 노출되도록 제 2 하드마스크층(17), 제 1 하드마스크층(15) 및 제 1 버퍼산화막(13)을 순차적으로 패터닝하여 소자격리영역과 활성영역을 한정한다.

도 1b를 참조하면, 포토레지스트(18)를 마스크로 사용하여 반도체기판(11)의 노출된 소자격리영역을 소정 깊이로 깊게 식각하여 트렌치(19)를 형성한다. 그리고, 트렌치(19)를 형성할 때 반응성이온식각(Reactive Ion Etching : 이하, RIE라 칭함) 방법이나 플라즈마 식각 방법으로 경사식각하여 트렌치(19)의 측면이 정(positive)의 경사를 갖도록 한다.

포토레지스트(18)을 제거하고 트렌치(19)의 표면을 열산화하여 제 2 버퍼산화막(21)을 형성한다. 상기에서 제 2 버퍼산화막(21)은 트렌치(19)을 형성할 때 발생된 표면의 손상을 제거한다.

도 1c를 참조하면, 제 2 하드마스크층(17)과 트렌치(19)의 표면에 산화실리콘을 CVD 방법으로 증착하여 제 1 필러(filler : 23)를 형성하고, 이 제 1 필러(23) 상에 트렌치(19)를 채우도록 다결정실리콘을 CVD 방법으로 증착하여 제 2 필러(25)를 형성한다.

도 1d를 참조하면, 제 2 필러(25)를 RIE 방법으로 에치 백하여 제 1 필러(23)가 노출되며 트렌치(19) 내에만 잔류하도록 한다. 그리고, 제 1 필러(23)와 제 2 하드마스크층(17)을 습식식각하여 제거한다. 이 때, 제 1 필러(23)은 제 2 필러(25)의 표면 보다 하부로 식각되어 트렌치(19)와 제 2 필러(25) 사이에 공간이 형성된다.

도 1e를 참조하면, 제 1 하드마스크층(15)과 제 1 버퍼산화막(13)을 습식 식각 방법으로 순차적으로 제거하여 반도체기판(11)의 활성영역을 노출시킨다.

그러나, 상술한 종래의 반도체장치의 소자격리방법은 제 1 필러와 제 2 하드마스크층을 습식식각하여 제거할 때 트렌치와 제 2 필러 사이에 형성되는 공간에 게이트 형성시 잔류물이 남게 되어 소자의 신뢰성을 저하시키는 문제점이 있었다.

따라서, 본 발명의 목적은 트렌치와 제 2 필러 사이에 공간의 형성에 의해 게이트 잔류물이 남는 것을 방지하여 소자의 신뢰성을 향상시킬 수 있는 반도체장치의 소자격리방법을 제공함에 있다.

상기 목적을 달성하기 위해 본 발명에 따른 반도체장치의 소자격리방법은 반도체기판 상에 제 1 하드마스크층 및 제 2 하드마스크층을 순차적으로 형성하고 상기 반도체기판이 노출되도록 패터닝하여 소자격리영역과 활성영역을 한정하는 공정과, 상기 반도체기판의 노출된 부분에 소정 깊이의 깊은 트렌치를 형성하고 상기 트렌치의 표면에 버퍼산화막을 형성하는 공정과, 상기 제 2 하드마스크층 상에 상기 트렌치를 채우도록 제 1 및 제 2 필러를 순차적으로 형성하는 공정과, 상기 제 2 필러를 상기 트렌치 내에만 잔류하도록 에치 백하고 상기 제 1 필러와 상기 제 2 하드마스크층을 건식 식각 방법으로 선택적으로 제거하는 공정과, 상기 제 1 하드마스크층을 제거하는 공정을 구비한다.

도 1a 내지 도 1e는 종래 기술에 따른 깊은 트렌치를 이용한 반도체장치의 소자격리방법을 도시하는 공정도

도 2a 내지 도 2e는 본 발명에 따른 깊은 트렌치를 이용한 반도체장치의 소자격리방법을 도시하는 공정도

이하, 첨부한 도면을 참조하여 본 발명을 상세히 설명한다.

도 2a 내지 도 2e는 본 발명에 따른 깊은 트렌치를 이용한 반도체장치의 소자격리방법을 도시하는 공정도이다.

도 2a를 참조하면, 반도체기판(31) 상에 열산화 방법으로 200∼400Å 정도 두께의 제 1 버퍼산화막(33)을 형성한다. 그리고, 제 1 버퍼산화막(33) 상에 CVD 방법으로 질화실리콘 및 산화실리콘을 순차적으로 각각 1200∼1600Å 정도의 두께와 4000∼7000Å 정도 두께로 증착하여 제 1 하드마스크층(35) 및 제 2 하드마스크층(37)을 형성한다. 그리고, 제 2 하드마스크층(37) 상에 포토레지스트(38)를 도포한 후 노광 및 현상하여 소정 부분을 노출시킨다.

그 다음, 잔류하는 포토레지스트(38)를 마스크로 사용하여 반도체기판(31)의 소정 부분이 노출되도록 제 2 하드마스크층(37), 제 1 하드마스크층(35) 및 제 1 버퍼산화막(33)을 순차적으로 이방성 식각 방법으로 패터닝하여 소자격리영역과 활성영역을 한정한다.

도 2b를 참조하면, 포토레지스트(38)를 마스크로 사용하여 반도체기판(31)의 노출된 소자격리영역을 4∼8㎛ 정도의 깊이로 깊게 식각하여 트렌치(39)를 형성한다. 상기에서 제 2 하드마스크층(37)은 트렌치(39)를 깊게 형성할 때 발생되는 포토레지스트(38)의 붕괴에 의한 트렌치(39) 크기의 증가를 방지한다. 그리고, 트렌치(39)를 형성할 때 RIE 방법이나 플라즈마 식각 방법으로 경사식각하여 트렌치(39)의 측면이 정(positive)의 경사를 갖도록 한다.

포토레지스트(38)을 제거하고 트렌치(39)의 표면을 열산화 방법으로 500∼1500Å 정도 두께의 제 2 버퍼산화막(41)을 형성한다. 상기에서 제 2 버퍼산화막(41)은 트렌치(39)을 형성할 때 발생된 표면의 손상을 제거한다.

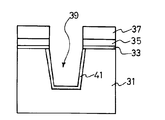

도 2c를 참조하면, 제 2 하드마스크층(37) 상에 CVD 방법으로 산화실리콘과 다결정실리콘을 트렌치(39)를 채우도록 순차적으로 증착하여 제 1 및 제 2 필러(43)(45)를 형성한다. 상기에서, 제 1 필러(43)는 제 2 하드마스크층(37)과 트렌치(39)의 표면 상에 2000∼4000Å 정도의 두께로 형성하며, 제 2 필러(45)는 제 1 필러(45) 상에 트렌치(39)를 채우도록 6000∼10000Å 정도의 두께로 형성한다. 트렌치(39)의 측면이 정(positive)의 경사를 가지고 제 2 필러(45)를 형성하는 다결정실리콘의 증착 특성이 양호하므로 내부에 보이드(void)의 형성이 억제된다.

도 2d를 참조하면, 제 2 필러(45)를 제 1 필러(43)가 노출되며 트렌치(39) 내에만 잔류하도록 에치 백한다. 그리고, 제 1 필러(43)와 제 2 하드마스크층(37)을 저압에서 건식 식각 방법으로 선택적으로 제거한다. 즉, 제 1 필러(43)와 제 2 하드마스크층(37)을 30∼250mTorr의 저압에서 CHF3가스에 CF4, C4F8, C2F6, 또는 C3F8등의 가스를 혼합하여 제 2 필러(45) 및 제 1 하드마스크층(35)과 선택적으로 식각하여 제거한다. 이 때, 제 1 필러(43)가 제 2 필러(45)의 표면 보다 하부로 식각되지 않도록하여 트렌치(39)와 제 2 필러(45) 사이에 공간이 형성되는 것을 방지한다.

도 2e를 참조하면, 제 1 하드마스크층(35)과 제 1 버퍼산화막(33)을 습식 식각 방법으로 순차적으로 제거하여 반도체기판(31)의 활성영역을 노출시킨다.

상술한 바와 같이 본 발명에 따른 반도체장치의 소자격리방법은 깊은 트렌치 내에 제 1 필라와 제 2 필라를 증착하여 이 트렌치를 채우고 제 2 필러를 트렌치 내에만 잔류하도록 에치 백한 후 제 1 필러와 제 2 하드마스크층을 저압에서 건식 식각 방법으로 선택적으로 제거하되 제 1 필러가 제 2 필러의 표면 보다 하부로 식각되지 않도록하여 트렌치와 제 2 필러 사이에 공간이 형성되는 것을 방지한다.

따라서, 본 발명은 이후 공정인 게이트 형성시 식각 잔류물이 남는 것을 방지할 수 있어 소자의 신뢰성을 향상시킬 수 있는 잇점이 있다.

Claims (6)

- 반도체기판 상에 제 1 하드마스크층 및 제 2 하드마스크층을 순차적으로 형성하고 상기 반도체기판이 노출되도록 패터닝하여 소자격리영역과 활성영역을 한정하는 공정과,상기 반도체기판의 노출된 부분에 소정 깊이의 깊은 트렌치를 형성하고 상기 트렌치의 표면에 버퍼산화막을 형성하는 공정과,상기 제 2 하드마스크층 상에 상기 트렌치를 채우도록 제 1 및 제 2 필러를 순차적으로 형성하는 공정과,상기 제 2 필러를 상기 트렌치 내에만 잔류하도록 에치 백하고 상기 제 1 필러와 상기 제 2 하드마스크층을 건식 식각 방법으로 선택적으로 제거하는 공정과,상기 제 1 하드마스크층을 제거하는 공정을 구비하는 반도체장치의 소자격리방법.

- 청구항 1에 있어서 상기 제 1 및 제 2 하드마스크층을 질화실리콘 및 산화실리콘으로 각각 형성하는 반도체장치의 소자격리방법.

- 청구항 1에 있어서 상기 트렌치를 4∼8㎛의 깊이로 형성하는 반도체장치의 소자격리방법.

- 청구항 1에 있어서 상기 제 1 및 제 2 필러를 산화실리콘과 다결정실리콘으로 각각 형성하는 반도체장치의 소자격리방법.

- 청구항 1에 있어서 상기 제 1 필러를 2000∼4000Å의 두께로 형성하며, 상기 제 2 필러를 6000∼10000Å의 두께로 형성하는 반도체장치의 소자격리방법.

- 청구항 1에 있어서 상기 제 1 필러와 제 2 하드마스크층을 30∼250mTorr의 저압에서 CHF3가스에 CF4, C4F8, C2F6, 또는 C3F8의 가스를 혼합한 가스로 식각하는 반도체장치의 소자격리방법.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1019970067209A KR100242523B1 (ko) | 1997-12-10 | 1997-12-10 | 반도체장치의 소자격리방법 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1019970067209A KR100242523B1 (ko) | 1997-12-10 | 1997-12-10 | 반도체장치의 소자격리방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR19990048487A KR19990048487A (ko) | 1999-07-05 |

| KR100242523B1 true KR100242523B1 (ko) | 2000-03-02 |

Family

ID=19526858

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019970067209A KR100242523B1 (ko) | 1997-12-10 | 1997-12-10 | 반도체장치의 소자격리방법 |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR100242523B1 (ko) |

-

1997

- 1997-12-10 KR KR1019970067209A patent/KR100242523B1/ko not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| KR19990048487A (ko) | 1999-07-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100249025B1 (ko) | 반도체장치의 소자분리방법 | |

| KR100312943B1 (ko) | 반도체장치 및 그의 제조방법 | |

| KR100226501B1 (ko) | 반도체장치의 소자격리방법 | |

| KR100242523B1 (ko) | 반도체장치의 소자격리방법 | |

| KR100596876B1 (ko) | 반도체 소자의 소자 분리막 형성 방법 | |

| KR100226500B1 (ko) | 반도체장치의 소자격리방법 | |

| KR100246197B1 (ko) | 반도체장치의 소자격리방법 | |

| KR100242526B1 (ko) | 반도체장치의 소자격리방법 | |

| KR19990070373A (ko) | 반도체장치의 소자격리방법 | |

| KR100271802B1 (ko) | 반도체장치의소자격리방법 | |

| KR100232522B1 (ko) | 반도체장치의 소자격리막 형성방법 | |

| KR100246198B1 (ko) | 반도체장치의 소자격리방법 | |

| KR100236720B1 (ko) | 반도체장치의 소자분리방법 | |

| KR100269623B1 (ko) | 반도체장치의 소자격리방법 | |

| KR19990010307A (ko) | 반도체장치의 소자격리방법 | |

| KR100474588B1 (ko) | 반도체장치의소자격리방법 | |

| KR19990041569A (ko) | 반도체장치의 소자격리방법 | |

| KR20000019068A (ko) | 반도체장치의 소자격리방법 | |

| KR100269603B1 (ko) | 반도체장치의 필드산화막 형성방법 | |

| KR19990081483A (ko) | 반도체장치의 소자 격리 방법 | |

| KR19990048259A (ko) | 반도체장치의 소자격리방법 | |

| KR19990000764A (ko) | 반도체장치의 소자격리방법 | |

| KR19990039742A (ko) | 반도체장치의 소자격리방법 | |

| KR20000015298A (ko) | 반도체장치의 소자격리방법 | |

| KR19990010247A (ko) | 반도체장치의 소자격리방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20071025 Year of fee payment: 9 |

|

| LAPS | Lapse due to unpaid annual fee |