JP7697397B2 - ポリシリコンウェーハの製造方法 - Google Patents

ポリシリコンウェーハの製造方法 Download PDFInfo

- Publication number

- JP7697397B2 JP7697397B2 JP2022067299A JP2022067299A JP7697397B2 JP 7697397 B2 JP7697397 B2 JP 7697397B2 JP 2022067299 A JP2022067299 A JP 2022067299A JP 2022067299 A JP2022067299 A JP 2022067299A JP 7697397 B2 JP7697397 B2 JP 7697397B2

- Authority

- JP

- Japan

- Prior art keywords

- polysilicon

- wafer

- polysilicon layer

- film thickness

- thickness distribution

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H10P14/24—

-

- C—CHEMISTRY; METALLURGY

- C01—INORGANIC CHEMISTRY

- C01B—NON-METALLIC ELEMENTS; COMPOUNDS THEREOF; METALLOIDS OR COMPOUNDS THEREOF NOT COVERED BY SUBCLASS C01C

- C01B33/00—Silicon; Compounds thereof

- C01B33/02—Silicon

- C01B33/021—Preparation

- C01B33/027—Preparation by decomposition or reduction of gaseous or vaporised silicon compounds other than silica or silica-containing material

- C01B33/03—Preparation by decomposition or reduction of gaseous or vaporised silicon compounds other than silica or silica-containing material by decomposition of silicon halides or halosilanes or reduction thereof with hydrogen as the only reducing agent

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/22—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the deposition of inorganic material, other than metallic material

- C23C16/24—Deposition of silicon only

-

- H10P14/29—

-

- H10P14/2905—

-

- H10P14/2924—

-

- H10P14/3411—

-

- H10P14/3456—

-

- H10P90/00—

Landscapes

- Chemical & Material Sciences (AREA)

- Organic Chemistry (AREA)

- Engineering & Computer Science (AREA)

- Inorganic Chemistry (AREA)

- General Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Materials Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Metallurgy (AREA)

- Mechanical Engineering (AREA)

- General Chemical & Material Sciences (AREA)

- Silicon Compounds (AREA)

- Chemical Vapour Deposition (AREA)

- Crystallography & Structural Chemistry (AREA)

Description

本発明は、ポリシリコンウェーハの製造方法、特には、Poly-Siウェーハのウェーハ形状を再現性良く制御できるポリシリコンウェーハの製造方法に関する。

ポリシリコン(Poly-Si)ウェーハの形状(Bow)によってRFデバイスのノイズ特性が変動するためその微小な形状制御が求められている。Poly-Si成膜プロセスとして生産性向上のため2層成長プロセス(1層目:低温デポ+2層目:高温デポ)が広く知られており、その成膜温度や成膜膜厚によってウェーハ形状を調整することができる。

基板の形状制御の方法としては、特許文献1には、ウェーハの湾曲面を測定し、その湾曲面の湾曲方向を判定し、いずれかの面にポリシリコンを付け反りが小さくなるように製造する方法が開示されている。特許文献2には、カーボン基材にSiC膜をCVD成長する際に、表裏面の形状を同一とすることで、反りの発生を抑制する製造方法が記載されている。

しかしながら、従来の方法では微小な形状調整が難しく、成膜装置間やチャンバー間のバラツキを低減する必要がある。

本発明は、上記問題を解決するためになされたものであり、成膜装置やチャンバーが異なっても、微小なウェーハ形状のバラツキを低減して再現性良くポリシリコンウェーハを製造することができるポリシリコンウェーハの製造方法を提供することを目的とする。

上記課題を解決するために、本発明では、

シリコン単結晶基板上にポリシリコン層が成膜されたポリシリコンウェーハの製造方法であって、

(1)シリコン単結晶基板上に、CVD法により1000℃以下の温度で第一のポリシリコン層を成膜する工程、

(2)前記第一のポリシリコン層上に、CVD法により1000℃より高い温度で第二のポリシリコン層を成膜する工程、

を有し、かつ、

前記工程(1)において、成膜する前記第一のポリシリコン層の面内膜厚分布の値(%)を、予め定めた範囲内に制御するようにし、かつ、前記予め定めた範囲の最大値(%)と最小値(%)の差を5.2(%)以内とするポリシリコンウェーハの製造方法を提供する。

シリコン単結晶基板上にポリシリコン層が成膜されたポリシリコンウェーハの製造方法であって、

(1)シリコン単結晶基板上に、CVD法により1000℃以下の温度で第一のポリシリコン層を成膜する工程、

(2)前記第一のポリシリコン層上に、CVD法により1000℃より高い温度で第二のポリシリコン層を成膜する工程、

を有し、かつ、

前記工程(1)において、成膜する前記第一のポリシリコン層の面内膜厚分布の値(%)を、予め定めた範囲内に制御するようにし、かつ、前記予め定めた範囲の最大値(%)と最小値(%)の差を5.2(%)以内とするポリシリコンウェーハの製造方法を提供する。

このようなポリシリコンウェーハの製造方法であれば、成膜装置やチャンバーが異なっても、微小なウェーハ形状のバラツキを低減して再現性良くポリシリコンウェーハを製造することができる。

また、前記工程(1)において、前記予め定めた範囲の最大値(%)を、1.5%以下に制御することが好ましい。

面内膜厚分布をこのように制御すれば、より安定的に微小なウェーハ形状のバラツキを低減して再現性良くポリシリコンウェーハを製造することができる。

また、前記工程(1)において、前記シリコン単結晶基板の面内温度分布を制御することによって、成膜する前記第一のポリシリコン層の面内膜厚分布を制御することが好ましい。

このようにすれば、第一のポリシリコン層の面内膜厚分布の制御を容易に行うことができる。

また本発明では、

2以上の異なる製造設備を用いてポリシリコンウェーハを製造するためのポリシリコンウェーハの製造方法であって、

前記2以上の異なる製造設備の各々において、上記のポリシリコンウェーハの製造方法を用いてポリシリコンウェーハを製造するポリシリコンウェーハの製造方法を提供する。

2以上の異なる製造設備を用いてポリシリコンウェーハを製造するためのポリシリコンウェーハの製造方法であって、

前記2以上の異なる製造設備の各々において、上記のポリシリコンウェーハの製造方法を用いてポリシリコンウェーハを製造するポリシリコンウェーハの製造方法を提供する。

本発明のポリシリコンウェーハの製造方法は、2以上の異なる製造設備を用いてポリシリコンウェーハの量産を行う上で、極めて有用である。

以上のように、本発明のポリシリコンウェーハの製造方法であれば、成膜装置やチャンバーが異なっても、微小なウェーハ形状のバラツキを低減して再現性良くポリシリコンウェーハを製造することができる。特に本発明は、高精度でウェーハ形状を制御することが求められるRFデバイス向けSiウェーハの量産において、極めて有益である。

2層成長プロセス(1層目:低温デポ+2層目:高温デポ)において、その成膜温度や成膜膜厚によってウェーハ形状を調整することができる。しかしながら、これらの方法では微小な形状調整が難しく、成膜装置間やチャンバー間のバラツキの微小な調整が困難となっていた。

本発明者らは、上記課題について鋭意検討を重ねた結果、一層目のポリシリコン層の面内膜厚分布を所定範囲内に制御することによって、成膜装置やチャンバーが異なっても、微小な形状調整ができ、再現性よく同レベルのウェーハ形状のポリシリコンウェーハを製造できることを見出し、本発明を完成させた。

即ち、本発明は、シリコン単結晶基板上にポリシリコン層が成膜されたポリシリコンウェーハの製造方法であって、(1)シリコン単結晶基板上に、CVD法により1000℃以下の温度で第一のポリシリコン層を成膜する工程、(2)前記第一のポリシリコン層上に、CVD法により1000℃より高い温度で第二のポリシリコン層を成膜する工程、を有し、かつ、前記工程(1)において、成膜する前記第一のポリシリコン層の面内膜厚分布の値(%)を、予め定めた範囲内に制御するようにし、かつ、前記予め定めた範囲の最大値(%)と最小値(%)の差を5.2(%)以内とするポリシリコンウェーハの製造方法である。

以下、本発明について詳細に説明するが、本発明はこれらに限定されるものではない。

[ポリシリコンウェーハの製造方法]

本発明のポリシリコンウェーハの製造方法は、工程(1)と工程(2)を有する。以下、図2、3を参照しながら詳細に説明する。

本発明のポリシリコンウェーハの製造方法は、工程(1)と工程(2)を有する。以下、図2、3を参照しながら詳細に説明する。

<工程(1)>

工程(1)は、シリコン単結晶基板上に、CVD法により1000℃以下の温度で第一のポリシリコン層を成膜する工程であり、本工程では、成膜する第一のポリシリコン層の面内膜厚分布の値(%)を、予め定めた範囲内に制御するようにし、かつ、予め定めた範囲の最大値(%)と最小値(%)の差を5.2(%)以内とする。

工程(1)は、シリコン単結晶基板上に、CVD法により1000℃以下の温度で第一のポリシリコン層を成膜する工程であり、本工程では、成膜する第一のポリシリコン層の面内膜厚分布の値(%)を、予め定めた範囲内に制御するようにし、かつ、予め定めた範囲の最大値(%)と最小値(%)の差を5.2(%)以内とする。

シリコン単結晶基板としては特に限定されない。例えば、CZ単結晶であってもFZ単結晶であってもよいし、ドープされていてもノンドープであってもよい。またドープされている場合、ドーパントの種類、濃度も特に限定はされず、例えばn型ではP、Sb、又はAsドープ、p型ではB、Al、又はGaドープ等が挙げられる。基板の直径も特に限定はされず、例えば、直径100~300mmとすることができる。基板の抵抗率にも特に制限はないが、例えば、抵抗率が5000Ω・cm以上の高抵抗とすることができる。

本工程では、図2に示すように、1000℃以下の低温でのCVD法による成膜を行う。このときの成膜温度は1000℃以下であれば特に限定されないが、好ましくは980℃未満とすることができる。また、成膜温度の下限に特に制限はないが、例えば、800℃以上とすることができる。本工程では、図3に示すように、低温での成膜によってシリコン単結晶基板1上にシード層となる第一のポリシリコン層2を成膜する。

このとき、第一のポリシリコン層2の面内膜厚分布の値(%)を上記の予め定めた範囲内に制御しておくことによって、後述の工程(2)で第二のポリシリコン層を成膜した後に狙い通りの反り形状のポリシリコンウェーハを得ることができる。一方、第一のポリシリコン層の面内膜厚分布の値(%)を上記の予め定めた範囲に制御しなければ、たとえ後述の工程(2)で第二のポリシリコン層の面内膜厚分布の値(%)を精度よく制御したとしても、再現性よく同レベルの形状のウェーハを製造することはできない。

成膜する第一のポリシリコン層の面内膜厚分布を制御する方法としては特に限定はされず、従来公知の方法を用いればよいが、例えば、シリコン単結晶基板の面内温度分布を制御することによって、成膜する第一のポリシリコン層の面内膜厚分布を制御することが好ましい。シリコン単結晶基板の面内温度分布を制御する方法としても特に制限はないが、一般的に使用されている成膜装置の機能を用いればよい。

本発明において、面内膜厚分布の値(%)としては公知の方法によって算出した値を用いればよいが、例えば、以下の式によって求めた値とすることができる。

面内膜厚分布(%)=(最大膜厚-最小膜厚)/(最大膜厚+最小膜厚)×100

面内膜厚分布(%)=(最大膜厚-最小膜厚)/(最大膜厚+最小膜厚)×100

予め定めた範囲は、該範囲の最大値(%)と最小値(%)の差が5.2(%)以内となるような範囲であれば、特に限定されない。つまり、第一のポリシリコン層の面内膜厚分布の値(%)自体は高くても低くてもよく、その面内膜厚分布の値(%)が高精度に制御されていればよい。すなわち、面内膜厚分布(%)が高い値で高精度に制御されていてもよいし、面内膜厚分布(%)が低い値で高精度に制御されていてもよい。いわば、第一のポリシリコン層の面内膜厚分布(%)を均一方向にしても悪化方向にしても、同レベルの膜厚分布であれば、ウェーハ形状は同レベルに調整することができる。予め定めた範囲の最大値(%)と最小値(%)の差は0(%)以上とすることができるが、より再現性のよいウェーハ製造を行う観点から、予め定めた範囲の最大値(%)と最小値(%)の差は好ましくは3%以内、より好ましくは1.5%以内、さらに好ましくは1.0%以内、きわめて好ましくは0.5%以内、とりわけ好ましくは0%(毎回一定)に制御するのがよい。

また、成膜する第一のポリシリコン層の面内膜厚分布の値(%)は、例えば、予め定めた範囲の最大値(%)が10%以下となるように制御することができるが、最大値(%)が1.5%以下となるように制御することがより安定的にウェーハ形状を同レベルに調整できる観点から好ましい。

以下、予め定めた範囲について、より具体的な例を挙げて説明する。

(具体例1)

第一のポリシリコン層の面内膜厚分布の値(%)が1.5%の一定値になるように制御するとき、予め定めた範囲の最大値は1.5(%)、最小値も1.5(%)であるから、予め定めた範囲の最大値(%)と最小値(%)の差は0(%)である。

第一のポリシリコン層の面内膜厚分布の値(%)が1.5%の一定値になるように制御するとき、予め定めた範囲の最大値は1.5(%)、最小値も1.5(%)であるから、予め定めた範囲の最大値(%)と最小値(%)の差は0(%)である。

(具体例2)

第一のポリシリコン層の面内膜厚分布の値(%)が1.5%±0.5%になるように制御するとき、予め定めた範囲の最大値は2.0(%)、最小値は1.0(%)であるから、予め定めた範囲の最大値(%)と最小値(%)の差は1(%)である。

第一のポリシリコン層の面内膜厚分布の値(%)が1.5%±0.5%になるように制御するとき、予め定めた範囲の最大値は2.0(%)、最小値は1.0(%)であるから、予め定めた範囲の最大値(%)と最小値(%)の差は1(%)である。

(具体例3)

第一のポリシリコン層の面内膜厚分布の値(%)が6.8%の一定値になるように制御するとき、予め定めた範囲の最大値は6.8(%)、最小値も6.8(%)であるから、予め定めた範囲の最大値(%)と最小値(%)の差は0(%)である。

第一のポリシリコン層の面内膜厚分布の値(%)が6.8%の一定値になるように制御するとき、予め定めた範囲の最大値は6.8(%)、最小値も6.8(%)であるから、予め定めた範囲の最大値(%)と最小値(%)の差は0(%)である。

(具体例4)

第一のポリシリコン層の面内膜厚分布の値(%)が6.8%±0.5%になるように制御するとき、予め定めた範囲の最大値は7.3(%)、最小値は6.3(%)であるから、予め定めた範囲の最大値(%)と最小値(%)の差は1(%)である。

第一のポリシリコン層の面内膜厚分布の値(%)が6.8%±0.5%になるように制御するとき、予め定めた範囲の最大値は7.3(%)、最小値は6.3(%)であるから、予め定めた範囲の最大値(%)と最小値(%)の差は1(%)である。

<工程(2)>

工程(2)は、第一のポリシリコン層上に、CVD法により1000℃より高い温度で第二のポリシリコン層を成膜する工程である。

工程(2)は、第一のポリシリコン層上に、CVD法により1000℃より高い温度で第二のポリシリコン層を成膜する工程である。

本工程では、図2に示すように、成長速度を高めて生産性を上げるため1000℃より高い高温でのCVD法により所望の膜厚まで成膜する。このときの成膜温度は1000℃より高ければ特に限定されないが、好ましくは1050℃以上とすることができる。また、成膜温度の上限に特に制限はないが、例えば、1200℃以下とすることができる。本工程では、図3に示すように、高温での成膜によって第一のポリシリコン層2上に第二のポリシリコン層3を成膜し、ポリシリコンウェーハ4を得ることができる。

第二のポリシリコン層についても、第一のポリシリコン層と同様に、面内膜厚分布(%)を予め定めた範囲に制御することが好ましい。第二のポリシリコン層の面内膜厚分布を精度よく制御することによって、なおいっそう、再現性よく同レベルの形状のウェーハを製造することができる。

なお、工程(1)で成膜する第一のポリシリコン層の厚さと、工程(2)で成膜する第二のポリシリコン層の厚さとの比率をどのようにするかは任意であるが、高温の方がポリシリコン層の成長速度が上昇するので、工程(2)で工程(1)よりも厚く成膜するように工程を設計することが生産性向上の観点から好ましい。

以上のように、本発明であれば、成膜装置やチャンバーが異なっても、微小なウェーハ形状のバラツキを低減して再現性良くポリシリコンウェーハを製造することができる。

[2以上の異なる製造設備を用いてポリシリコンウェーハを製造するためのポリシリコンウェーハの製造方法]

また本発明では、2以上の異なる製造設備を用いてポリシリコンウェーハを製造するためのポリシリコンウェーハの製造方法であって、前記2以上の異なる製造設備の各々において、上記のポリシリコンウェーハの製造方法を用いてポリシリコンウェーハを製造するポリシリコンウェーハの製造方法を提供する。

また本発明では、2以上の異なる製造設備を用いてポリシリコンウェーハを製造するためのポリシリコンウェーハの製造方法であって、前記2以上の異なる製造設備の各々において、上記のポリシリコンウェーハの製造方法を用いてポリシリコンウェーハを製造するポリシリコンウェーハの製造方法を提供する。

上述のように、本発明のポリシリコンウェーハの製造方法は、成膜装置やチャンバーが異なっても、微小なウェーハ形状のバラツキを低減して再現性良くポリシリコンウェーハを製造することができる。すなわち、製造設備によらず同等品質のポリシリコンウェーハを再現性良く製造することができる。したがって、本発明のポリシリコンウェーハの製造方法は、複数の製造設備を用いて、同時並行的にポリシリコンウェーハを量産するのに特に好適である。

以下、実施例及び比較例を用いて本発明を具体的に説明するが、本発明はこれらに限定されるものではない。

なお、以下の実施例1~3、及び比較例1では、膜厚分布の調整方法については、ポリシリコン成長時のシリコン単結晶基板の温度分布を調整することにより膜厚分布を調整した。しかし、本発明において、膜厚分布の調整方法はこれに限定されるものではない。

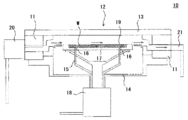

以下の実施例1~3、及び比較例1で用いたPoly-Si成長する枚葉式の気相成長装置(反応炉)を示す概略図を図4に示す。気相成長装置10のチャンバー(反応容器)12は、チャンバーベース11とチャンバーベース11を上下から挟む透明石英部材13、14とから形成される。このチャンバー12内には、シリコン単結晶基板Wを上面のウェーハ載置面(座ぐり部)19で支持するサセプタ17が配置されている。このサセプタ17には、例えば3つ以上の貫通孔16が設けられ、この貫通孔16に挿入されて上下動することでシリコン単結晶基板Wの載置、離間を行うウェーハリフトピン15が配置されている。このサセプタ17はウェーハ回転機構18に接続されており、エピタキシャル成長中はサセプタ17を回転させることで、載置されたシリコン単結晶基板Wを回転させ、Poly-Si層をシリコン単結晶基板W上に膜厚均一に成長させる。チャンバー12には、チャンバー12内に原料ガスおよびキャリアガス(例えば、水素)を含む気相成長ガスを導入して、サセプタ17上に載置されたシリコン単結晶基板Wの表面上に原料ガスとキャリアガスを供給するガス導入管20が接続されている。また、チャンバー12のガス導入管20が接続された側の反対側には、チャンバー12内からガスを排出するガス排出管21が接続されている。

(実施例1)

異なる2つの反応炉(RCT-A、RCT-B)にて以下の実験を実施した。不純物としてボロンを含有した抵抗率が5000Ω・cm以上、直径が200mmのシリコン単結晶基板を用意した。そのシリコン単結晶基板上に、成長温度870℃、成膜ガスにトリクロロシラン(TCS)を用いてPoly-Si膜厚0.3μm(1層目)となるようなノンドープのPoly-Si膜(第一のポリシリコン層)を成長させ、その後、成長温度1070℃に変更し、Poly-Si膜厚1.9μm(2層目)となるようなノンドープのPoly-Si膜(第二のポリシリコン層)を連続で成膜するCVD法を行うことによってサンプルとなるPoly-Siウェーハを製造した。

異なる2つの反応炉(RCT-A、RCT-B)にて以下の実験を実施した。不純物としてボロンを含有した抵抗率が5000Ω・cm以上、直径が200mmのシリコン単結晶基板を用意した。そのシリコン単結晶基板上に、成長温度870℃、成膜ガスにトリクロロシラン(TCS)を用いてPoly-Si膜厚0.3μm(1層目)となるようなノンドープのPoly-Si膜(第一のポリシリコン層)を成長させ、その後、成長温度1070℃に変更し、Poly-Si膜厚1.9μm(2層目)となるようなノンドープのPoly-Si膜(第二のポリシリコン層)を連続で成膜するCVD法を行うことによってサンプルとなるPoly-Siウェーハを製造した。

このときRCT-AおよびBの1層目の成膜工程で膜厚分布をいずれも1.5%に調整(予め定めた範囲の最大値(%)と最小値(%)の差を0(%)に制御)したうえで2層目の膜厚分布もRCT-A、Bどちらも1.5%となるように調整した。

このとき製造されたPoly-Siウェーハのウェーハ形状(Bow)を測定した。図1にそのときの結果を示す。図1より、RCT-A、Bで製造したウェーハのBowの値はいずれも4.35μm程度であり、RCT-A、Bの1層目の膜厚分布を同レベルにすることで同レベルのウェーハ形状を再現できることが確認できた。

図1中における左図は、1層目の膜厚分布を確認するために、1層目を本来の0.3μmよりも厚く(2.5μm程度に)成膜して、ウェーハ面内の膜厚をプロットした図である。また、上記左図の横軸は膜厚測定位置を示しており、CTR:ウェーハ中心部、R/2:ウェーハ中心部から50mm、10mm:ウェーハ中心部から90mm(外周から10mm)である。図1中における右図は、設計膜厚(1層目0.3μm、2層目1.9μm)通りに成膜したときのウェーハのBowの値である。なお、1層目を本来の0.3μmに成膜した場合もより厚く成膜した場合も、面内膜厚分布(%)の計算値は理論上同じ値になる。

(実施例2)

RCT-Aの1層目の成膜工程で膜厚分布を1.5%に調整し、RCT-Bの1層目の成膜工程で膜厚分布を6.7%に調整(予め定めた範囲の最大値(%)と最小値(%)の差を5.2(%)に制御)した以外は、実施例1と同様にしてPoly-Siウェーハを製造した。なお、2層目の膜厚分布も、実施例1と同様、RCT-A、Bどちらも1.5%となるように調整した。

RCT-Aの1層目の成膜工程で膜厚分布を1.5%に調整し、RCT-Bの1層目の成膜工程で膜厚分布を6.7%に調整(予め定めた範囲の最大値(%)と最小値(%)の差を5.2(%)に制御)した以外は、実施例1と同様にしてPoly-Siウェーハを製造した。なお、2層目の膜厚分布も、実施例1と同様、RCT-A、Bどちらも1.5%となるように調整した。

実施例2で製造したPoly-Siウェーハのウェーハ形状(Bow)を測定したところ、RCT-A、Bで製造したウェーハのBowの値はいずれも4.35μm程度であり、RCT-AとRCT-Bで同レベルの形状(Bow)のウェーハが得られた。

(実施例3)

RCT-Aの1層目の成膜工程で膜厚分布を6.8%に調整し、RCT-Bの1層目の成膜工程で膜厚分布を6.8%に調整(予め定めた範囲の最大値(%)と最小値(%)の差を0(%)に制御)した以外は、実施例1と同様にしてPoly-Siウェーハを製造した。なお、2層目の膜厚分布も、実施例1と同様、RCT-A、Bどちらも1.5%となるように調整した。

RCT-Aの1層目の成膜工程で膜厚分布を6.8%に調整し、RCT-Bの1層目の成膜工程で膜厚分布を6.8%に調整(予め定めた範囲の最大値(%)と最小値(%)の差を0(%)に制御)した以外は、実施例1と同様にしてPoly-Siウェーハを製造した。なお、2層目の膜厚分布も、実施例1と同様、RCT-A、Bどちらも1.5%となるように調整した。

実施例3で製造したPoly-Siウェーハのウェーハ形状(Bow)を測定したところ、RCT-A、Bで製造したウェーハのBowの値はいずれも3.20μm程度であり、RCT-AとRCT-Bで同レベルの形状(Bow)のウェーハが得られた。

(比較例1)

RCT-Aの1層目の成膜工程で膜厚分布を1.5%、RCT-Bの1層目の成膜工程で膜厚分布を6.8%に調整(予め定めた範囲の最大値(%)と最小値(%)の差を5.3(%)に制御)した以外は、実施例1と同様にしてPoly-Siウェーハを製造した。なお、実施例1と同様、2層目の膜厚分布もRCT-A、Bどちらも1.5%となるように調整した。

RCT-Aの1層目の成膜工程で膜厚分布を1.5%、RCT-Bの1層目の成膜工程で膜厚分布を6.8%に調整(予め定めた範囲の最大値(%)と最小値(%)の差を5.3(%)に制御)した以外は、実施例1と同様にしてPoly-Siウェーハを製造した。なお、実施例1と同様、2層目の膜厚分布もRCT-A、Bどちらも1.5%となるように調整した。

このとき製造されたPoly-Siウェーハのウェーハ形状(Bow)を測定した。図1にそのときの結果を示す。図1より、RCT-Aで製造したウェーハのBowは4.35μm程度であったのに対し、RCT-Bで製造したウェーハのBowは3.20μm程度であり、第一のポリシリコン層の面内膜厚分布を最大値(%)と最小値(%)の差が5.2(%)以内となる範囲に制御しなかったことで、異なるウェーハ形状となることが確認できた。

本明細書は、以下の発明を包含する。

[1]:シリコン単結晶基板上にポリシリコン層が成膜されたポリシリコンウェーハの製

造方法であって、(1)シリコン単結晶基板上に、CVD法により1000℃以

下の温度で第一のポリシリコン層を成膜する工程、(2)前記第一のポリシリコ

ン層上に、CVD法により1000℃より高い温度で第二のポリシリコン層を成

膜する工程、を有し、かつ、前記工程(1)において、成膜する前記第一のポリ

シリコン層の面内膜厚分布の値(%)を、予め定めた範囲内に制御するようにし

、かつ、前記予め定めた範囲の最大値(%)と最小値(%)の差を5.2(%)

以内とすることを特徴とするポリシリコンウェーハの製造方法。

[2]:前記工程(1)において、前記予め定めた範囲の最大値(%)を、1.5%以下

に制御することを特徴とする請求項1に記載のポリシリコンウェーハの製造方法

。

[3]:前記工程(1)において、前記シリコン単結晶基板の面内温度分布を制御するこ

とによって、成膜する前記第一のポリシリコン層の面内膜厚分布を制御すること

を特徴とする上記[1]に記載のポリシリコンウェーハの製造方法。

[4]:前記工程(1)において、前記シリコン単結晶基板の面内温度分布を制御するこ

とによって、成膜する前記第一のポリシリコン層の面内膜厚分布を制御すること

を特徴とする上記[2]に記載のポリシリコンウェーハの製造方法。

[5]:2以上の異なる製造設備を用いてポリシリコンウェーハを製造するためのポリシ

リコンウェーハの製造方法であって、前記2以上の異なる製造設備の各々におい

て、上記[1]、上記[2]、上記[3]、又は上記[4]に記載のポリシリコ

ンウェーハの製造方法を用いてポリシリコンウェーハを製造することを特徴とす

るポリシリコンウェーハの製造方法。

[1]:シリコン単結晶基板上にポリシリコン層が成膜されたポリシリコンウェーハの製

造方法であって、(1)シリコン単結晶基板上に、CVD法により1000℃以

下の温度で第一のポリシリコン層を成膜する工程、(2)前記第一のポリシリコ

ン層上に、CVD法により1000℃より高い温度で第二のポリシリコン層を成

膜する工程、を有し、かつ、前記工程(1)において、成膜する前記第一のポリ

シリコン層の面内膜厚分布の値(%)を、予め定めた範囲内に制御するようにし

、かつ、前記予め定めた範囲の最大値(%)と最小値(%)の差を5.2(%)

以内とすることを特徴とするポリシリコンウェーハの製造方法。

[2]:前記工程(1)において、前記予め定めた範囲の最大値(%)を、1.5%以下

に制御することを特徴とする請求項1に記載のポリシリコンウェーハの製造方法

。

[3]:前記工程(1)において、前記シリコン単結晶基板の面内温度分布を制御するこ

とによって、成膜する前記第一のポリシリコン層の面内膜厚分布を制御すること

を特徴とする上記[1]に記載のポリシリコンウェーハの製造方法。

[4]:前記工程(1)において、前記シリコン単結晶基板の面内温度分布を制御するこ

とによって、成膜する前記第一のポリシリコン層の面内膜厚分布を制御すること

を特徴とする上記[2]に記載のポリシリコンウェーハの製造方法。

[5]:2以上の異なる製造設備を用いてポリシリコンウェーハを製造するためのポリシ

リコンウェーハの製造方法であって、前記2以上の異なる製造設備の各々におい

て、上記[1]、上記[2]、上記[3]、又は上記[4]に記載のポリシリコ

ンウェーハの製造方法を用いてポリシリコンウェーハを製造することを特徴とす

るポリシリコンウェーハの製造方法。

なお、本発明は、上記実施形態に限定されるものではない。上記実施形態は例示であり、本発明の特許請求の範囲に記載された技術的思想と実質的に同一な構成を有し、同様な作用効果を奏するものは、いかなるものであっても本発明の技術的範囲に包含される。

1…シリコン単結晶基板、 2…第一のポリシリコン層、

3…第二のポリシリコン層、 4…ポリシリコンウェーハ、 10…気相成長装置、

11…チャンバーベース、 12…チャンバー、 13、14…透明石英部材、

15…ウェーハリフトピン、 16…貫通孔、 17…サセプタ、

18…ウェーハ回転機構、 19…ウェーハ載置面、 20…ガス導入管、

21…ガス排出管。 W…シリコン単結晶基板。

3…第二のポリシリコン層、 4…ポリシリコンウェーハ、 10…気相成長装置、

11…チャンバーベース、 12…チャンバー、 13、14…透明石英部材、

15…ウェーハリフトピン、 16…貫通孔、 17…サセプタ、

18…ウェーハ回転機構、 19…ウェーハ載置面、 20…ガス導入管、

21…ガス排出管。 W…シリコン単結晶基板。

Claims (5)

- シリコン単結晶基板上にポリシリコン層が成膜されたポリシリコンウェーハの製造方法であって、

(1)シリコン単結晶基板上に、CVD法により1000℃以下の温度で第一のポリシリコン層を成膜する工程、

(2)前記第一のポリシリコン層上に、CVD法により1000℃より高い温度で第二のポリシリコン層を成膜する工程、

を有し、かつ、

前記工程(1)において、成膜する前記第一のポリシリコン層の面内膜厚分布の値(%)を、予め定めた範囲内に制御するようにし、かつ、前記予め定めた範囲の最大値(%)と最小値(%)の差を5.2(%)以内とすることを特徴とするポリシリコンウェーハの製造方法。 - 前記工程(1)において、前記予め定めた範囲の最大値(%)を、1.5%以下に制御することを特徴とする請求項1に記載のポリシリコンウェーハの製造方法。

- 前記工程(1)において、前記シリコン単結晶基板の面内温度分布を制御することによって、成膜する前記第一のポリシリコン層の面内膜厚分布を制御することを特徴とする請求項1に記載のポリシリコンウェーハの製造方法。

- 前記工程(1)において、前記シリコン単結晶基板の面内温度分布を制御することによって、成膜する前記第一のポリシリコン層の面内膜厚分布を制御することを特徴とする請求項2に記載のポリシリコンウェーハの製造方法。

- 2以上の異なる製造設備を用いてポリシリコンウェーハを製造するためのポリシリコンウェーハの製造方法であって、

前記2以上の異なる製造設備の各々において、請求項1から請求項4のいずれか一項に記載のポリシリコンウェーハの製造方法を用いてポリシリコンウェーハを製造することを特徴とするポリシリコンウェーハの製造方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2022067299A JP7697397B2 (ja) | 2022-04-15 | 2022-04-15 | ポリシリコンウェーハの製造方法 |

| PCT/JP2023/008830 WO2023199656A1 (ja) | 2022-04-15 | 2023-03-08 | ポリシリコンウェーハの製造方法 |

| CN202380033330.8A CN118922913A (zh) | 2022-04-15 | 2023-03-08 | 多晶硅晶圆的制造方法 |

| KR1020247033803A KR20250005115A (ko) | 2022-04-15 | 2023-03-08 | 폴리실리콘 웨이퍼의 제조방법 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2022067299A JP7697397B2 (ja) | 2022-04-15 | 2022-04-15 | ポリシリコンウェーハの製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2023157404A JP2023157404A (ja) | 2023-10-26 |

| JP7697397B2 true JP7697397B2 (ja) | 2025-06-24 |

Family

ID=88329283

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2022067299A Active JP7697397B2 (ja) | 2022-04-15 | 2022-04-15 | ポリシリコンウェーハの製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| JP (1) | JP7697397B2 (ja) |

| KR (1) | KR20250005115A (ja) |

| CN (1) | CN118922913A (ja) |

| WO (1) | WO2023199656A1 (ja) |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000183153A (ja) | 1998-12-17 | 2000-06-30 | Mitsubishi Materials Silicon Corp | 誘電体分離ウェーハおよびその製造方法 |

| JP2004158685A (ja) | 2002-11-07 | 2004-06-03 | Canon Inc | 多結晶シリコン薄膜およびその製法 |

| JP2014011178A (ja) | 2012-06-27 | 2014-01-20 | Tokyo Electron Ltd | プラズマ処理方法及びプラズマ処理装置 |

| WO2017221563A1 (ja) | 2016-06-23 | 2017-12-28 | 信越半導体株式会社 | 貼り合わせsoiウェーハの製造方法 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS57197834A (en) * | 1981-05-29 | 1982-12-04 | Toko Inc | Manufacture of insulated and isolated substrate |

| JPH1116991A (ja) | 1997-06-19 | 1999-01-22 | Tokai Carbon Co Ltd | 半導体製造装置用カーボン支持体 |

| JP5343409B2 (ja) | 2008-06-06 | 2013-11-13 | 株式会社Sumco | 半導体ウェーハの湾曲判定方法、膜付きウェーハの製造方法 |

-

2022

- 2022-04-15 JP JP2022067299A patent/JP7697397B2/ja active Active

-

2023

- 2023-03-08 CN CN202380033330.8A patent/CN118922913A/zh active Pending

- 2023-03-08 KR KR1020247033803A patent/KR20250005115A/ko active Pending

- 2023-03-08 WO PCT/JP2023/008830 patent/WO2023199656A1/ja not_active Ceased

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000183153A (ja) | 1998-12-17 | 2000-06-30 | Mitsubishi Materials Silicon Corp | 誘電体分離ウェーハおよびその製造方法 |

| JP2004158685A (ja) | 2002-11-07 | 2004-06-03 | Canon Inc | 多結晶シリコン薄膜およびその製法 |

| JP2014011178A (ja) | 2012-06-27 | 2014-01-20 | Tokyo Electron Ltd | プラズマ処理方法及びプラズマ処理装置 |

| WO2017221563A1 (ja) | 2016-06-23 | 2017-12-28 | 信越半導体株式会社 | 貼り合わせsoiウェーハの製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20250005115A (ko) | 2025-01-09 |

| WO2023199656A1 (ja) | 2023-10-19 |

| JP2023157404A (ja) | 2023-10-26 |

| CN118922913A (zh) | 2024-11-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP3260581B1 (en) | Method for producing silicon carbide single crystal epitaxial wafer and silicon carbide single crystal epitaxial wafer | |

| JP2005503000A (ja) | トリシランを用いる混合基板への成膜 | |

| CN104718601A (zh) | 具有SiC外延膜的SiC衬底 | |

| JP5910430B2 (ja) | エピタキシャル炭化珪素ウエハの製造方法 | |

| US8038793B2 (en) | Epitaxial growth method | |

| JP7694744B2 (ja) | SiCデバイス及びSiCデバイスの製造方法 | |

| CN115537922B (zh) | 一种降低外延片自掺杂的方法 | |

| JP2009038294A (ja) | 出力調整方法、シリコンエピタキシャルウェーハの製造方法、及びサセプタ | |

| JP7285890B2 (ja) | SiCエピタキシャルウェハ及びSiCエピタキシャルウェハの製造方法 | |

| JP7697397B2 (ja) | ポリシリコンウェーハの製造方法 | |

| JP2008186944A (ja) | 気相成長用サセプタ及び気相成長装置並びに気相成長用サセプタの設計方法及び気相成長方法 | |

| JP5780491B2 (ja) | シリコンエピタキシャルウェーハの製造方法 | |

| JPH10189695A (ja) | 気相成長用サセプタ及びその製造方法 | |

| US20240191393A1 (en) | Epitaxy susceptor, epitaxy growth apparatus and manufacturing method of semiconductor device | |

| JP3424069B2 (ja) | エピタキシャルシリコン基板の製造方法 | |

| JP2021031363A (ja) | 炭化ケイ素多結晶基板の製造方法 | |

| JP7392526B2 (ja) | 炭化ケイ素単結晶基板の製造方法 | |

| JP7255473B2 (ja) | 炭化ケイ素多結晶基板の製造方法 | |

| JP7567210B2 (ja) | 炭化珪素単結晶基板の製造方法 | |

| JP7816191B2 (ja) | SiCエピタキシャルウェハ及びSiCデバイス | |

| WO2020158657A1 (ja) | 成膜装置及び成膜方法 | |

| JPH08250430A (ja) | 単結晶薄膜の製造方法 | |

| JP3112796B2 (ja) | 化学気相成長方法 | |

| CN120767187A (zh) | 外延晶圆及改善外延晶圆平坦度的方法和装置 | |

| KR101905860B1 (ko) | 웨이퍼 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20240327 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20250513 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20250526 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7697397 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |