JP7190430B2 - 回路ダイと相互接続部との間の自動位置合せ - Google Patents

回路ダイと相互接続部との間の自動位置合せ Download PDFInfo

- Publication number

- JP7190430B2 JP7190430B2 JP2019527215A JP2019527215A JP7190430B2 JP 7190430 B2 JP7190430 B2 JP 7190430B2 JP 2019527215 A JP2019527215 A JP 2019527215A JP 2019527215 A JP2019527215 A JP 2019527215A JP 7190430 B2 JP7190430 B2 JP 7190430B2

- Authority

- JP

- Japan

- Prior art keywords

- channels

- circuit die

- channel

- substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000007788 liquid Substances 0.000 claims description 153

- 239000000758 substrate Substances 0.000 claims description 82

- 239000000853 adhesive Substances 0.000 claims description 80

- 230000001070 adhesive effect Effects 0.000 claims description 80

- 239000007787 solid Substances 0.000 claims description 75

- 238000000034 method Methods 0.000 claims description 58

- 239000000976 ink Substances 0.000 description 39

- 239000000463 material Substances 0.000 description 37

- 230000008569 process Effects 0.000 description 17

- 239000012790 adhesive layer Substances 0.000 description 15

- 239000012530 fluid Substances 0.000 description 14

- 230000009471 action Effects 0.000 description 12

- 239000008393 encapsulating agent Substances 0.000 description 12

- 239000010410 layer Substances 0.000 description 9

- 238000001704 evaporation Methods 0.000 description 7

- ZWEHNKRNPOVVGH-UHFFFAOYSA-N 2-Butanone Chemical compound CCC(C)=O ZWEHNKRNPOVVGH-UHFFFAOYSA-N 0.000 description 6

- 238000004891 communication Methods 0.000 description 6

- 239000000203 mixture Substances 0.000 description 6

- 239000004065 semiconductor Substances 0.000 description 6

- 238000001723 curing Methods 0.000 description 5

- 230000008020 evaporation Effects 0.000 description 5

- 239000002184 metal Substances 0.000 description 5

- 229910052751 metal Inorganic materials 0.000 description 5

- 230000007935 neutral effect Effects 0.000 description 5

- 238000003847 radiation curing Methods 0.000 description 5

- 238000007711 solidification Methods 0.000 description 5

- 230000008023 solidification Effects 0.000 description 5

- 238000001029 thermal curing Methods 0.000 description 5

- 150000001875 compounds Chemical class 0.000 description 4

- 239000004020 conductor Substances 0.000 description 4

- 238000012986 modification Methods 0.000 description 4

- 230000004048 modification Effects 0.000 description 4

- -1 polyethylene terephthalate Polymers 0.000 description 4

- 238000007639 printing Methods 0.000 description 4

- 238000007789 sealing Methods 0.000 description 4

- 238000009736 wetting Methods 0.000 description 4

- CSCPPACGZOOCGX-UHFFFAOYSA-N Acetone Chemical compound CC(C)=O CSCPPACGZOOCGX-UHFFFAOYSA-N 0.000 description 3

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 3

- YXFVVABEGXRONW-UHFFFAOYSA-N Toluene Chemical compound CC1=CC=CC=C1 YXFVVABEGXRONW-UHFFFAOYSA-N 0.000 description 3

- 238000005452 bending Methods 0.000 description 3

- 230000008901 benefit Effects 0.000 description 3

- 239000010949 copper Substances 0.000 description 3

- 239000003989 dielectric material Substances 0.000 description 3

- 230000005499 meniscus Effects 0.000 description 3

- 229920002635 polyurethane Polymers 0.000 description 3

- 239000004814 polyurethane Substances 0.000 description 3

- 229910052709 silver Inorganic materials 0.000 description 3

- 239000004332 silver Substances 0.000 description 3

- 239000011800 void material Substances 0.000 description 3

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- 239000012776 electronic material Substances 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 238000007641 inkjet printing Methods 0.000 description 2

- 229910001338 liquidmetal Inorganic materials 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 238000000520 microinjection Methods 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 229920000139 polyethylene terephthalate Polymers 0.000 description 2

- 239000005020 polyethylene terephthalate Substances 0.000 description 2

- 238000007650 screen-printing Methods 0.000 description 2

- 239000011343 solid material Substances 0.000 description 2

- 239000002904 solvent Substances 0.000 description 2

- 238000010146 3D printing Methods 0.000 description 1

- 241000473391 Archosargus rhomboidalis Species 0.000 description 1

- 229920001342 Bakelite® Polymers 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 239000004593 Epoxy Substances 0.000 description 1

- JOYRKODLDBILNP-UHFFFAOYSA-N Ethyl urethane Chemical compound CCOC(N)=O JOYRKODLDBILNP-UHFFFAOYSA-N 0.000 description 1

- 239000004698 Polyethylene Substances 0.000 description 1

- 239000004793 Polystyrene Substances 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 1

- 239000004676 acrylonitrile butadiene styrene Substances 0.000 description 1

- 239000004637 bakelite Substances 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 229920001940 conductive polymer Polymers 0.000 description 1

- 238000007596 consolidation process Methods 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 238000001035 drying Methods 0.000 description 1

- 238000004049 embossing Methods 0.000 description 1

- 238000005538 encapsulation Methods 0.000 description 1

- 229920006332 epoxy adhesive Polymers 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 239000000835 fiber Substances 0.000 description 1

- 238000011049 filling Methods 0.000 description 1

- 229920005570 flexible polymer Polymers 0.000 description 1

- 230000014509 gene expression Effects 0.000 description 1

- 238000007646 gravure printing Methods 0.000 description 1

- 239000004615 ingredient Substances 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 238000011068 loading method Methods 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 229910001092 metal group alloy Inorganic materials 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 238000000465 moulding Methods 0.000 description 1

- 239000002105 nanoparticle Substances 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000037361 pathway Effects 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 229920000573 polyethylene Polymers 0.000 description 1

- 229920002223 polystyrene Polymers 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 238000002174 soft lithography Methods 0.000 description 1

- 238000004381 surface treatment Methods 0.000 description 1

- 238000005382 thermal cycling Methods 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L24/23—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process

- H01L24/24—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process of an individual high density interconnect connector

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B81—MICROSTRUCTURAL TECHNOLOGY

- B81C—PROCESSES OR APPARATUS SPECIALLY ADAPTED FOR THE MANUFACTURE OR TREATMENT OF MICROSTRUCTURAL DEVICES OR SYSTEMS

- B81C3/00—Assembling of devices or systems from individually processed components

- B81C3/002—Aligning microparts

- B81C3/005—Passive alignment, i.e. without a detection of the position of the elements or using only structural arrangements or thermodynamic forces

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/12—Mountings, e.g. non-detachable insulating substrates

- H01L23/13—Mountings, e.g. non-detachable insulating substrates characterised by the shape

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49805—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers the leads being also applied on the sidewalls or the bottom of the substrate, e.g. leadless packages for surface mounting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/4985—Flexible insulating substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/544—Marks applied to semiconductor devices or parts, e.g. registration marks, alignment structures, wafer maps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/02—Bonding areas ; Manufacturing methods related thereto

- H01L24/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L24/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L24/19—Manufacturing methods of high density interconnect preforms

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L24/23—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process

- H01L24/25—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process of a plurality of high density interconnect connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/82—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by forming build-up interconnects at chip-level, e.g. for high density interconnects [HDI]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/91—Methods for connecting semiconductor or solid state bodies including different methods provided for in two or more of groups H01L24/80 - H01L24/90

- H01L24/92—Specific sequence of method steps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2223/00—Details relating to semiconductor or other solid state devices covered by the group H01L23/00

- H01L2223/544—Marks applied to semiconductor devices or parts

- H01L2223/54426—Marks applied to semiconductor devices or parts for alignment

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/03—Manufacturing methods

- H01L2224/034—Manufacturing methods by blanket deposition of the material of the bonding area

- H01L2224/0346—Plating

- H01L2224/03462—Electroplating

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0555—Shape

- H01L2224/05552—Shape in top view

- H01L2224/05553—Shape in top view being rectangular

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0555—Shape

- H01L2224/05552—Shape in top view

- H01L2224/05554—Shape in top view being square

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0556—Disposition

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/05599—Material

- H01L2224/056—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05638—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/05644—Gold [Au] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/05599—Material

- H01L2224/056—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05638—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/05647—Copper [Cu] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/06—Structure, shape, material or disposition of the bonding areas prior to the connecting process of a plurality of bonding areas

- H01L2224/061—Disposition

- H01L2224/0612—Layout

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16104—Disposition relative to the bonding area, e.g. bond pad

- H01L2224/16105—Disposition relative to the bonding area, e.g. bond pad the bump connector connecting bonding areas being not aligned with respect to each other

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L2224/23—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process

- H01L2224/24—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process of an individual high density interconnect connector

- H01L2224/2401—Structure

- H01L2224/24011—Deposited, e.g. MCM-D type

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L2224/23—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process

- H01L2224/24—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process of an individual high density interconnect connector

- H01L2224/241—Disposition

- H01L2224/24151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/24221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/24225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L2224/23—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process

- H01L2224/24—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process of an individual high density interconnect connector

- H01L2224/2499—Auxiliary members for HDI interconnects, e.g. spacers, alignment aids

- H01L2224/24991—Auxiliary members for HDI interconnects, e.g. spacers, alignment aids being formed on the semiconductor or solid-state body to be connected

- H01L2224/24992—Flow barrier

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L2224/23—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process

- H01L2224/24—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process of an individual high density interconnect connector

- H01L2224/2499—Auxiliary members for HDI interconnects, e.g. spacers, alignment aids

- H01L2224/24996—Auxiliary members for HDI interconnects, e.g. spacers, alignment aids being formed on an item to be connected not being a semiconductor or solid-state body

- H01L2224/24998—Reinforcing structures, e.g. ramp-like support

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L2224/23—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process

- H01L2224/25—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process of a plurality of high density interconnect connectors

- H01L2224/251—Disposition

- H01L2224/2512—Layout

- H01L2224/25175—Parallel arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/2612—Auxiliary members for layer connectors, e.g. spacers

- H01L2224/26152—Auxiliary members for layer connectors, e.g. spacers being formed on an item to be connected not being a semiconductor or solid-state body

- H01L2224/26175—Flow barriers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/27—Manufacturing methods

- H01L2224/273—Manufacturing methods by local deposition of the material of the layer connector

- H01L2224/2731—Manufacturing methods by local deposition of the material of the layer connector in liquid form

- H01L2224/27312—Continuous flow, e.g. using a microsyringe, a pump, a nozzle or extrusion

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L2224/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

- H01L2224/29001—Core members of the layer connector

- H01L2224/29099—Material

- H01L2224/2919—Material with a principal constituent of the material being a polymer, e.g. polyester, phenolic based polymer, epoxy

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73267—Layer and HDI connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies and for methods related thereto

- H01L2224/76—Apparatus for connecting with build-up interconnects

- H01L2224/7615—Means for depositing

- H01L2224/76151—Means for direct writing

- H01L2224/76152—Syringe

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/80001—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by connecting a bonding area directly to another bonding area, i.e. connectorless bonding, e.g. bumpless bonding

- H01L2224/8012—Aligning

- H01L2224/80143—Passive alignment, i.e. self alignment, e.g. using surface energy, chemical reactions, thermal equilibrium

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/82—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by forming build-up interconnects at chip-level, e.g. for high density interconnects [HDI]

- H01L2224/821—Forming a build-up interconnect

- H01L2224/82101—Forming a build-up interconnect by additive methods, e.g. direct writing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/82—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by forming build-up interconnects at chip-level, e.g. for high density interconnects [HDI]

- H01L2224/821—Forming a build-up interconnect

- H01L2224/82101—Forming a build-up interconnect by additive methods, e.g. direct writing

- H01L2224/82102—Forming a build-up interconnect by additive methods, e.g. direct writing using jetting, e.g. ink jet

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/82—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by forming build-up interconnects at chip-level, e.g. for high density interconnects [HDI]

- H01L2224/8212—Aligning

- H01L2224/82136—Aligning involving guiding structures, e.g. spacers or supporting members

- H01L2224/82138—Aligning involving guiding structures, e.g. spacers or supporting members the guiding structures being at least partially left in the finished device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/82—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by forming build-up interconnects at chip-level, e.g. for high density interconnects [HDI]

- H01L2224/8212—Aligning

- H01L2224/82143—Passive alignment, i.e. self alignment, e.g. using surface energy, chemical reactions, thermal equilibrium

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/82—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by forming build-up interconnects at chip-level, e.g. for high density interconnects [HDI]

- H01L2224/828—Bonding techniques

- H01L2224/8285—Bonding techniques using a polymer adhesive, e.g. an adhesive based on silicone, epoxy, polyimide, polyester

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/82—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by forming build-up interconnects at chip-level, e.g. for high density interconnects [HDI]

- H01L2224/82909—Post-treatment of the connector or the bonding area

- H01L2224/82951—Forming additional members

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/83001—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector involving a temporary auxiliary member not forming part of the bonding apparatus

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/83001—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector involving a temporary auxiliary member not forming part of the bonding apparatus

- H01L2224/83005—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector involving a temporary auxiliary member not forming part of the bonding apparatus being a temporary or sacrificial substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/8312—Aligning

- H01L2224/83121—Active alignment, i.e. by apparatus steering, e.g. optical alignment using marks or sensors

- H01L2224/83132—Active alignment, i.e. by apparatus steering, e.g. optical alignment using marks or sensors using marks formed outside the semiconductor or solid-state body, i.e. "off-chip"

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/8312—Aligning

- H01L2224/83136—Aligning involving guiding structures, e.g. spacers or supporting members

- H01L2224/83138—Aligning involving guiding structures, e.g. spacers or supporting members the guiding structures being at least partially left in the finished device

- H01L2224/8314—Guiding structures outside the body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/8312—Aligning

- H01L2224/83136—Aligning involving guiding structures, e.g. spacers or supporting members

- H01L2224/83138—Aligning involving guiding structures, e.g. spacers or supporting members the guiding structures being at least partially left in the finished device

- H01L2224/83141—Guiding structures both on and outside the body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/8319—Arrangement of the layer connectors prior to mounting

- H01L2224/83192—Arrangement of the layer connectors prior to mounting wherein the layer connectors are disposed only on another item or body to be connected to the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/8319—Arrangement of the layer connectors prior to mounting

- H01L2224/83194—Lateral distribution of the layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/838—Bonding techniques

- H01L2224/8385—Bonding techniques using a polymer adhesive, e.g. an adhesive based on silicone, epoxy, polyimide, polyester

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/8512—Aligning

- H01L2224/85143—Passive alignment, i.e. self alignment, e.g. using surface energy, chemical reactions, thermal equilibrium

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/91—Methods for connecting semiconductor or solid state bodies including different methods provided for in two or more of groups H01L2224/80 - H01L2224/90

- H01L2224/92—Specific sequence of method steps

- H01L2224/922—Connecting different surfaces of the semiconductor or solid-state body with connectors of different types

- H01L2224/9222—Sequential connecting processes

- H01L2224/92242—Sequential connecting processes the first connecting process involving a layer connector

- H01L2224/92244—Sequential connecting processes the first connecting process involving a layer connector the second connecting process involving a build-up interconnect

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/93—Batch processes

- H01L2224/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L2224/9512—Aligning the plurality of semiconductor or solid-state bodies

- H01L2224/95143—Passive alignment, i.e. self alignment, e.g. using surface energy, chemical reactions, thermal equilibrium

- H01L2224/95146—Passive alignment, i.e. self alignment, e.g. using surface energy, chemical reactions, thermal equilibrium by surface tension

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/12—Mountings, e.g. non-detachable insulating substrates

- H01L23/14—Mountings, e.g. non-detachable insulating substrates characterised by the material or its electrical properties

- H01L23/145—Organic substrates, e.g. plastic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49866—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers characterised by the materials

- H01L23/49894—Materials of the insulating layers or coatings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/02—Bonding areas ; Manufacturing methods related thereto

- H01L24/03—Manufacturing methods

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/02—Bonding areas ; Manufacturing methods related thereto

- H01L24/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L24/06—Structure, shape, material or disposition of the bonding areas prior to the connecting process of a plurality of bonding areas

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L24/27—Manufacturing methods

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L24/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L24/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L24/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L24/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/73—Means for bonding being of different types provided for in two or more of groups H01L24/10, H01L24/18, H01L24/26, H01L24/34, H01L24/42, H01L24/50, H01L24/63, H01L24/71

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies

- H01L24/75—Apparatus for connecting with bump connectors or layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies

- H01L24/76—Apparatus for connecting with build-up interconnects

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1515—Shape

- H01L2924/15153—Shape the die mounting substrate comprising a recess for hosting the device

- H01L2924/15155—Shape the die mounting substrate comprising a recess for hosting the device the shape of the recess being other than a cuboid

- H01L2924/15156—Side view

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/38—Effects and problems related to the device integration

- H01L2924/384—Bump effects

- H01L2924/3841—Solder bridging

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Manufacturing Of Printed Wiring (AREA)

- Structures For Mounting Electric Components On Printed Circuit Boards (AREA)

- Structure Of Printed Boards (AREA)

- Die Bonding (AREA)

- Non-Metallic Protective Coatings For Printed Circuits (AREA)

Description

ある特定の用語が、本明細書及び特許請求の範囲の全体を通して使用されており、これらの大部分については周知であるが、何らかの説明が必要とされる場合もある。以下を理解されたい:

用語「導電性液体」は、毛管現象によってチャネル内を流動可能な液体組成物を指す。本明細書中に記載される導電性液体は、固化させて、導電性トレースを形成することができる。導電性液体は、導電性トレースの形成に使用するのに望ましい性質を有する任意の適切な電子材料を含んでもよい。

用語「接着剤インク」は、液体キャリア及び1つ以上の接着剤を含む液体組成物を指す。本明細書中に記載される接着剤インクは、固化させて、接着剤層を形成することができる。

実施形態1~13、14~21、22~30及び31~39はいずれも組み合わせることができることを理解されたい。

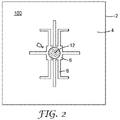

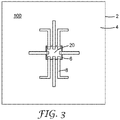

主表面を有する基板であって、主表面上にポケット及び1つ以上のチャネルが形成されており、チャネルはそれぞれ、チャネルの第1端部と第2端部との間に延び、第1端部は、ポケットに流体的に接続されている、基板と、

ポケット内に配置された固体回路ダイであって、固体回路ダイの表面上に、チャネルの第1端部と位置合わせされた1つ以上の接触パッドを有する、固体回路ダイと、

1つ以上のチャネル内に形成された1つ以上の導電性トレースであって、チャネルの第1端部まで延び、固体回路ダイの前記接触パッドと直接接触している、導電性トレースと、

を備える、物品。

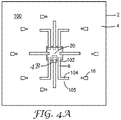

基板の主表面上にポケット及び1つ以上のチャネルを形成することであって、チャネルはそれぞれ、チャネルの第1端部と第2端部との間に延び、第1端部は、ポケットに流体的に接続されている、ことと、

ポケット内に固体回路ダイを配置することであって、固体回路ダイの表面上に、チャネルの第1端部と位置合わせされた1つ以上の接触パッドを有する、ことと、

チャネルの第2端部に導電性液体を配置することと、

導電性液体を、主に毛細管圧によって、チャネル内において第1端部に向かって流し、固体回路ダイの接触パッドと直接接触させることと、

導電性液体を硬化させて、固体回路ダイの接触パッドと直接接触する1つ以上の導電性トレースを形成することと、

を含む、方法。

Claims (5)

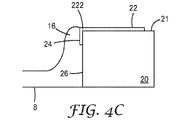

- 主表面を有する基板であって、前記主表面上にポケット及び1つ以上のチャネルが形成されており、前記1つ以上のチャネルは、それぞれ、各チャネルの第1端部と第2端部との間に延び、前記第1端部は、前記ポケットに流体的に接続されている、基板と、

前記ポケット内に配置された固体回路ダイであって、前記固体回路ダイの表面上に、前記1つ以上のチャネルの前記第1端部と位置合わせされた1つ以上の接触パッドを有する、固体回路ダイと、

前記1つ以上のチャネル内に形成された1つ以上の導電性トレースであって、前記1つ以上のチャネルの前記第1端部まで延び、前記固体回路ダイの前記接触パッドと直接接触している導電性トレースと、

を備え、

前記1つ以上のチャネルは、入口チャネル及び出口チャネルを備え、前記入口チャネル及び前記出口チャネルのそれぞれは、前記ポケット内に延び、前記ポケット内で流体的に接続されて内部チャネルを形成する各々の第1端部を有し、前記内部チャネルの少なくとも一部分は、前記固体回路ダイの下にある、物品。 - 前記接触パッドの少なくとも1つは、前記固体回路ダイの底面上に、前記内部チャネルに対向して位置する、請求項1に記載の物品。

- 主表面を有する基板であって、前記主表面上にポケット及び1つ以上のチャネルが形成されており、前記1つ以上のチャネルは、それぞれ、各チャネルの第1端部と第2端部との間に延び、前記第1端部は、前記ポケットに流体的に接続されている、基板と、

前記ポケット内に配置された固体回路ダイであって、前記固体回路ダイの表面上に、前記1つ以上のチャネルの前記第1端部と位置合わせされた1つ以上の接触パッドを有する、固体回路ダイと、

前記1つ以上のチャネル内に形成された1つ以上の導電性トレースであって、前記1つ以上のチャネルの前記第1端部まで延び、前記固体回路ダイの前記接触パッドと直接接触している導電性トレースと、

を備え、

前記基板は、前記1つ以上のチャネルの少なくとも1つに隣接して配置された1つ以上の安全チャネルを更に備え、前記安全チャネルは、それぞれ、前記ポケットの側壁を横切って、前記隣接するチャネルに対して実質的に平行な方向に延びる、物品。 - 主表面を有する基板を用意することと、

前記基板の前記主表面上にポケット及び1つ以上のチャネルを形成することであって、前記1つ以上のチャネルは、それぞれ、各チャネルの第1端部と第2端部との間に延び、前記第1端部は、前記ポケットに流体的に接続されている、ことと、

前記ポケット内に固体回路ダイを配置することであって、前記固体回路ダイの表面上に、前記1つ以上のチャネルの前記第1端部と位置合わせされた1つ以上の接触パッドを有する、ことと、

前記1つ以上のチャネルの前記第2端部に接着剤インクを配置することと、前記接着剤インクを、主に毛細管圧によって、前記1つ以上のチャネル内において前記第1端部に向かって流し、前記ポケットの側壁と前記固体回路ダイとの間の間隙を少なくとも部分的に充填することと、

前記1つ以上のチャネルの前記第2端部に導電性液体を配置することと、

前記導電性液体を、主に毛細管圧によって、前記1つ以上のチャネル内において前記第1端部に向かって流し、前記固体回路ダイの前記接触パッドと直接接触させることと、

前記導電性液体を硬化させて、前記固体回路ダイの前記接触パッドと直接接触する1つ以上の導電性トレースを形成することと、

を含む、方法。 - 前記導電性液体は、前記固体回路ダイの側面上の1つの接触パッドに向かって流れ、前記1つの接触パッドと直接接触する、請求項4に記載の方法。

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201662424686P | 2016-11-21 | 2016-11-21 | |

| US62/424,686 | 2016-11-21 | ||

| US201762584223P | 2017-11-10 | 2017-11-10 | |

| US62/584,223 | 2017-11-10 | ||

| PCT/US2017/062030 WO2018094057A1 (en) | 2016-11-21 | 2017-11-16 | Automatic registration between circuit dies and interconnects |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2020504438A JP2020504438A (ja) | 2020-02-06 |

| JP2020504438A5 JP2020504438A5 (ja) | 2020-12-24 |

| JP7190430B2 true JP7190430B2 (ja) | 2022-12-15 |

Family

ID=62146802

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019527215A Active JP7190430B2 (ja) | 2016-11-21 | 2017-11-16 | 回路ダイと相互接続部との間の自動位置合せ |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US10971468B2 (ja) |

| EP (1) | EP3542398A4 (ja) |

| JP (1) | JP7190430B2 (ja) |

| CN (1) | CN110024120A (ja) |

| WO (1) | WO2018094057A1 (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11906759B2 (en) * | 2018-05-22 | 2024-02-20 | 3M Innovative Properties Company | Optical film with light control edge |

| WO2020058815A1 (en) * | 2018-09-17 | 2020-03-26 | 3M Innovative Properties Company | Flexible device including conductive traces with enhanced stretchability |

| EP3906759A4 (en) | 2018-12-31 | 2022-10-12 | 3M Innovative Properties Company | FLEXIBLE CIRCUITS ON FLEXIBLE SUBSTRATES |

| US11937381B2 (en) * | 2018-12-31 | 2024-03-19 | 3M Innovative Properties Company | Forming electrical interconnections using capillary microfluidics |

| US12020951B2 (en) | 2019-04-29 | 2024-06-25 | 3M Innovative Properties Company | Methods for registration of circuit dies and electrical interconnects |

| EP3905861A1 (de) * | 2020-04-30 | 2021-11-03 | ZKW Group GmbH | Barriere gegen verschwimmen von smt-bauteilen |

| US11911814B2 (en) * | 2020-08-04 | 2024-02-27 | Xtpl S.A. | Method of forming an elongate electrical connection feature traversing a microscopic step |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20060237229A1 (en) | 2005-04-25 | 2006-10-26 | Brother Kogyo Kabushiki Kaisha | Method for forming pattern and a wired board |

| JP2006324315A (ja) | 2005-05-17 | 2006-11-30 | Shin Etsu Polymer Co Ltd | 導電性回路及びその形成方法 |

| JP2006332615A (ja) | 2005-04-25 | 2006-12-07 | Brother Ind Ltd | パターン形成方法 |

| JP2008211150A (ja) | 2007-02-28 | 2008-09-11 | Seiko Instruments Inc | 3次元構造体部品、及びその製造方法 |

| US20080258313A1 (en) | 2007-04-19 | 2008-10-23 | Ali M Zaki | Connecting microsized devices using ablative films |

| JP2009224450A (ja) | 2008-03-14 | 2009-10-01 | Konica Minolta Holdings Inc | 金属パターン形成用インクジェットインクおよび金属パターン形成方法 |

| JP2011249357A (ja) | 2010-05-21 | 2011-12-08 | Panasonic Electric Works Co Ltd | 回路基板および回路基板の製造方法 |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS52149066A (en) * | 1976-06-04 | 1977-12-10 | Hitachi Ltd | Connecting method of silicon semiconductor chip to ceramic substrate |

| JPH0438522Y2 (ja) * | 1986-08-01 | 1992-09-09 | ||

| JPH06350233A (ja) * | 1993-06-10 | 1994-12-22 | Sankyo Seiki Mfg Co Ltd | 回路基板 |

| US5842275A (en) * | 1995-09-05 | 1998-12-01 | Ford Motor Company | Reflow soldering to mounting pads with vent channels to avoid skewing |

| JP4117807B2 (ja) * | 1997-06-24 | 2008-07-16 | 松下電工株式会社 | 電子部品のハンダ付け方法 |

| JP2002198638A (ja) * | 2000-12-27 | 2002-07-12 | Shinko Electric Ind Co Ltd | チップ部品の実装用基板及びその製造方法並びに実装構造及び実装方法 |

| GR1004106B (el) | 2002-01-24 | 2003-01-13 | Εκεφε "Δημοκριτος" Ινστιτουτο Μικροηλεκτρονικης | Ολοκληρωμενοι θερμικοι αισθητηρες πυριτιου χαμηλης ισχυος και διαταξεις μικρο-ροης βασισμενοι στην χρηση τεχνολογιας κοιλοτητας αερα σφραγισμενης με μεμβρανη πορωδους πυριτιου ή τεχνολογιας μικρο-καναλιων |

| US7276802B2 (en) | 2002-04-15 | 2007-10-02 | Micron Technology, Inc. | Semiconductor integrated circuit package having electrically disconnected solder balls for mounting |

| US6902260B2 (en) * | 2003-07-24 | 2005-06-07 | Hewlett-Packard Development Company, L.P. | Fluid ejection device adherence |

| EP1915320A1 (en) * | 2005-08-11 | 2008-04-30 | Koninklijke Philips Electronics N.V. | Method for manufacturing a microelectronic package comprising a silicon mems microphone |

| US9113547B2 (en) | 2008-10-24 | 2015-08-18 | Intel Corporation | Same layer microelectronic circuit patterning using hybrid laser projection patterning (LPP) and semi-additive patterning(SAP) |

| CN102282661A (zh) * | 2009-01-27 | 2011-12-14 | 松下电工株式会社 | 半导体芯片的安装方法、使用该方法获得的半导体装置以及半导体芯片的连接方法与表面设有布线的立体结构物及其制法 |

| TW201342538A (zh) * | 2012-04-13 | 2013-10-16 | Advanced Semiconductor Eng | 半導體封裝結構及其製造方法 |

| WO2014113045A1 (en) * | 2013-01-16 | 2014-07-24 | 3M Innovative Properties Company | Light emitting semiconductor device and substrate therefore |

| KR20140115021A (ko) * | 2013-03-20 | 2014-09-30 | 에스케이하이닉스 주식회사 | 반도체 패키지 및 그 제조방법 |

| FR3003689B1 (fr) * | 2013-03-25 | 2016-11-25 | Commissariat Energie Atomique | Support pour auto-assemblage capillaire avec stabilisation horizontale, procede de fabrication et utilisation |

| US9401306B2 (en) | 2013-11-11 | 2016-07-26 | Regents Of The University Of Minnesota | Self-aligned capillarity-assisted microfabrication |

| AT517203B1 (de) * | 2015-07-06 | 2016-12-15 | Zkw Group Gmbh | Leiterplatte sowie Verfahren zur Herstellung einer Leiterplatte |

| US20180190614A1 (en) * | 2016-12-05 | 2018-07-05 | Ananda H. Kumar | Massively parallel transfer of microLED devices |

-

2017

- 2017-11-16 JP JP2019527215A patent/JP7190430B2/ja active Active

- 2017-11-16 US US16/461,015 patent/US10971468B2/en active Active

- 2017-11-16 CN CN201780072072.9A patent/CN110024120A/zh not_active Withdrawn

- 2017-11-16 EP EP17872717.8A patent/EP3542398A4/en not_active Withdrawn

- 2017-11-16 WO PCT/US2017/062030 patent/WO2018094057A1/en active Application Filing

Patent Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20060237229A1 (en) | 2005-04-25 | 2006-10-26 | Brother Kogyo Kabushiki Kaisha | Method for forming pattern and a wired board |

| JP2006332615A (ja) | 2005-04-25 | 2006-12-07 | Brother Ind Ltd | パターン形成方法 |

| JP2006324315A (ja) | 2005-05-17 | 2006-11-30 | Shin Etsu Polymer Co Ltd | 導電性回路及びその形成方法 |

| JP2008211150A (ja) | 2007-02-28 | 2008-09-11 | Seiko Instruments Inc | 3次元構造体部品、及びその製造方法 |

| US20080258313A1 (en) | 2007-04-19 | 2008-10-23 | Ali M Zaki | Connecting microsized devices using ablative films |

| CN101681851A (zh) | 2007-04-19 | 2010-03-24 | 伊斯曼柯达公司 | 使用烧蚀膜连接微尺寸器件 |

| JP2010527509A (ja) | 2007-04-19 | 2010-08-12 | イーストマン コダック カンパニー | アブレーション膜を用いたマイクロサイズデバイスの接続 |

| JP2009224450A (ja) | 2008-03-14 | 2009-10-01 | Konica Minolta Holdings Inc | 金属パターン形成用インクジェットインクおよび金属パターン形成方法 |

| JP2011249357A (ja) | 2010-05-21 | 2011-12-08 | Panasonic Electric Works Co Ltd | 回路基板および回路基板の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP3542398A4 (en) | 2020-12-02 |

| CN110024120A (zh) | 2019-07-16 |

| EP3542398A1 (en) | 2019-09-25 |

| JP2020504438A (ja) | 2020-02-06 |

| US10971468B2 (en) | 2021-04-06 |

| US20190273061A1 (en) | 2019-09-05 |

| WO2018094057A1 (en) | 2018-05-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7190430B2 (ja) | 回路ダイと相互接続部との間の自動位置合せ | |

| US20210035875A1 (en) | Automatic registration between circuit dies and interconnects | |

| EP1720389B1 (en) | Method for forming pattern and a wired board | |

| US8659154B2 (en) | Semiconductor device including adhesive covered element | |

| CN106158774B (zh) | 半导体封装结构及其制造方法 | |

| JP2006332615A (ja) | パターン形成方法 | |

| TWI536886B (zh) | 用於裝配電子元件於可撓性基板上的方法和設備以及電子元件和可撓性基板的組件 | |

| US20170322376A1 (en) | Methods of attaching surfaces together by adhesives, and devices including surfaces attached together by adhesives | |

| US11937381B2 (en) | Forming electrical interconnections using capillary microfluidics | |

| KR20170114825A (ko) | 반도체 패키지 기판 및 그 제조방법 | |

| KR20220163964A (ko) | 변형가능 인덕터들 | |

| CN112154539A (zh) | 包括电路管芯的超薄且柔性的装置 | |

| US20210235586A1 (en) | Electrical device having jumper | |

| CN103985679A (zh) | 包括穿孔箔片的3dic 封装件 | |

| JP2011159857A (ja) | 電子装置の製造方法 | |

| JP2013179351A (ja) | 電子装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20201113 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20201113 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20211014 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20211207 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20220216 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220303 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20220304 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220309 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20220802 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20221024 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20221108 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20221205 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7190430 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |