JP6922397B2 - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP6922397B2 JP6922397B2 JP2017095983A JP2017095983A JP6922397B2 JP 6922397 B2 JP6922397 B2 JP 6922397B2 JP 2017095983 A JP2017095983 A JP 2017095983A JP 2017095983 A JP2017095983 A JP 2017095983A JP 6922397 B2 JP6922397 B2 JP 6922397B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- insulating film

- amorphous

- alumina

- semiconductor layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Formation Of Insulating Films (AREA)

- Junction Field-Effect Transistors (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Description

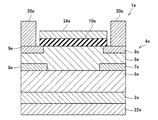

2:半導体基板

4:窒化物半導体層

6:p型窒化物半導体層

8:n型窒化物半導体層

10:絶縁膜

20:ソース電極

22:ドレイン電極

24:ゲート電極

Claims (6)

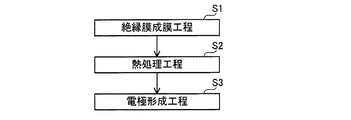

- 電極構造体を有する半導体装置の製造方法であって、

半導体層上に少なくともアルミナと酸化シリコンが混合された非晶質層を有する絶縁膜を成膜する絶縁膜成膜工程と、

前記絶縁膜成膜工程時の成膜温度よりも高い温度で前記絶縁膜を熱処理する熱処理工程と、

前記絶縁膜上に電極を形成する電極形成工程と、を備えており、

前記非晶質層は、シリコン原子とアルミニウム原子の総和に対するシリコン原子の割合が13%以上である、製造方法。 - 前記絶縁膜成膜工程は、非晶質のアルミナからなるアルミナ層と非晶質の酸化シリコンからなる酸化シリコン層を交互に積層し、前記非晶質層を形成する積層工程を有する、請求項1に記載の製造方法。

- 前記積層工程では、原子層堆積法を利用して、5原子層以上連続して成膜されない条件下で前記アルミナ層を成膜する、請求項2に記載の製造方法。

- 前記半導体層が、窒化物半導体層である、請求項1〜3のいずれか一項に記載の製造方法。

- 前記半導体層と前記絶縁膜と前記電極が絶縁ゲート部を構成する、請求項1〜4のいずれか一項に記載の製造方法。

- 電極構造体を有する半導体装置であって、

半導体層と、

前記半導体層上に設けられる絶縁膜と、

前記絶縁膜上に設けられる電極と、を備えており、

前記絶縁膜は、アルミナと酸化シリコンが混合された非晶質層を有しており、

前記非晶質層は、シリコン原子とアルミニウム原子の総和に対するシリコン原子の割合が13%以上である、半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017095983A JP6922397B2 (ja) | 2017-05-12 | 2017-05-12 | 半導体装置及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017095983A JP6922397B2 (ja) | 2017-05-12 | 2017-05-12 | 半導体装置及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2018195626A JP2018195626A (ja) | 2018-12-06 |

| JP6922397B2 true JP6922397B2 (ja) | 2021-08-18 |

Family

ID=64569005

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017095983A Active JP6922397B2 (ja) | 2017-05-12 | 2017-05-12 | 半導体装置及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6922397B2 (ja) |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3786566B2 (ja) * | 2000-06-27 | 2006-06-14 | 株式会社東芝 | 半導体装置及びその製造方法 |

| JP3773448B2 (ja) * | 2001-06-21 | 2006-05-10 | 松下電器産業株式会社 | 半導体装置 |

| JP3840207B2 (ja) * | 2002-09-30 | 2006-11-01 | 株式会社東芝 | 絶縁膜及び電子素子 |

| JP2011151366A (ja) * | 2009-12-26 | 2011-08-04 | Canon Anelva Corp | 誘電体膜の製造方法 |

-

2017

- 2017-05-12 JP JP2017095983A patent/JP6922397B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2018195626A (ja) | 2018-12-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8525274B2 (en) | Semiconductor device and method of manufacturing the same | |

| JP6251071B2 (ja) | 半導体装置 | |

| JP5166576B2 (ja) | GaN系半導体素子の製造方法 | |

| JP6235702B2 (ja) | 半導体装置 | |

| JP2010232377A (ja) | 半導体素子 | |

| KR102505057B1 (ko) | 반도체 전력 디바이스를 위한 하이브리드 게이트 유전체 | |

| JP2023118942A (ja) | 半導体装置 | |

| JP5306438B2 (ja) | 電界効果トランジスタおよびその製造方法 | |

| JP2014045174A (ja) | 窒化物半導体装置 | |

| CN106663634A (zh) | 半导体器件及半导体器件的制造方法 | |

| JP2012114320A (ja) | 窒化物半導体電界効果トランジスタ | |

| CN105336789A (zh) | 一种高质量MIS结构的GaN基场效应晶体管及其制备方法 | |

| JP2013004750A (ja) | 化合物半導体装置及びその製造方法 | |

| JP2019050232A (ja) | 半導体装置の製造方法および半導体装置 | |

| JP2013140866A (ja) | 半導体装置及び半導体装置の製造方法 | |

| JP2019134164A (ja) | 半導体装置および半導体装置の製造方法 | |

| JP7165328B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| JP6267706B2 (ja) | 半導体装置およびその製造方法 | |

| WO2023008308A1 (ja) | 半導体装置 | |

| JP2018200932A (ja) | 半導体装置の製造方法および半導体装置 | |

| JP2014078561A (ja) | 窒化物半導体ショットキバリアダイオード | |

| JP6922397B2 (ja) | 半導体装置及びその製造方法 | |

| JP2009049099A (ja) | 炭化珪素半導体装置の製造方法 | |

| JP5220904B2 (ja) | GaN系化合物半導体装置 | |

| JP6707995B2 (ja) | 電極構造体、電極構造体を用いる半導体装置及び電極構造体の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20200221 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20210308 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20210323 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20210629 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20210712 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6922397 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |