JP6810280B2 - 積層型量子コンピューティングデバイスにおける回路要素の集積 - Google Patents

積層型量子コンピューティングデバイスにおける回路要素の集積 Download PDFInfo

- Publication number

- JP6810280B2 JP6810280B2 JP2019550195A JP2019550195A JP6810280B2 JP 6810280 B2 JP6810280 B2 JP 6810280B2 JP 2019550195 A JP2019550195 A JP 2019550195A JP 2019550195 A JP2019550195 A JP 2019550195A JP 6810280 B2 JP6810280 B2 JP 6810280B2

- Authority

- JP

- Japan

- Prior art keywords

- chip

- layer

- qubit

- dielectric

- superconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 230000010354 integration Effects 0.000 title description 6

- 239000002096 quantum dot Substances 0.000 claims description 156

- 239000002887 superconductor Substances 0.000 claims description 143

- 238000000034 method Methods 0.000 claims description 57

- 239000000758 substrate Substances 0.000 claims description 57

- 238000000059 patterning Methods 0.000 claims description 22

- 239000003989 dielectric material Substances 0.000 claims description 21

- 230000005672 electromagnetic field Effects 0.000 claims description 13

- 239000010410 layer Substances 0.000 description 209

- 239000000463 material Substances 0.000 description 60

- 230000008569 process Effects 0.000 description 33

- 238000004519 manufacturing process Methods 0.000 description 22

- 238000010586 diagram Methods 0.000 description 16

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 10

- 229910052782 aluminium Inorganic materials 0.000 description 10

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 10

- 238000005240 physical vapour deposition Methods 0.000 description 8

- 229910052594 sapphire Inorganic materials 0.000 description 8

- 239000010980 sapphire Substances 0.000 description 8

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 7

- 230000008878 coupling Effects 0.000 description 7

- 238000010168 coupling process Methods 0.000 description 7

- 238000005859 coupling reaction Methods 0.000 description 7

- 238000005530 etching Methods 0.000 description 7

- 229910052751 metal Inorganic materials 0.000 description 7

- 239000002184 metal Substances 0.000 description 7

- 238000012545 processing Methods 0.000 description 6

- 229910052710 silicon Inorganic materials 0.000 description 6

- 239000010703 silicon Substances 0.000 description 6

- 229910052581 Si3N4 Inorganic materials 0.000 description 5

- 230000009471 action Effects 0.000 description 5

- 238000005137 deposition process Methods 0.000 description 5

- 230000004907 flux Effects 0.000 description 5

- 235000012239 silicon dioxide Nutrition 0.000 description 5

- 239000000377 silicon dioxide Substances 0.000 description 5

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 5

- 230000005540 biological transmission Effects 0.000 description 4

- 239000010408 film Substances 0.000 description 4

- 230000006870 function Effects 0.000 description 4

- 230000005283 ground state Effects 0.000 description 4

- 239000010409 thin film Substances 0.000 description 4

- 235000012431 wafers Nutrition 0.000 description 4

- 230000008901 benefit Effects 0.000 description 3

- 238000000151 deposition Methods 0.000 description 3

- 229910001275 Niobium-titanium Inorganic materials 0.000 description 2

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- 238000000137 annealing Methods 0.000 description 2

- 238000004364 calculation method Methods 0.000 description 2

- 238000004590 computer program Methods 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 230000005281 excited state Effects 0.000 description 2

- 229910052738 indium Inorganic materials 0.000 description 2

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- 229910052758 niobium Inorganic materials 0.000 description 2

- 239000010955 niobium Substances 0.000 description 2

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 2

- RJSRQTFBFAJJIL-UHFFFAOYSA-N niobium titanium Chemical compound [Ti].[Nb] RJSRQTFBFAJJIL-UHFFFAOYSA-N 0.000 description 2

- 238000000926 separation method Methods 0.000 description 2

- 238000013459 approach Methods 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 230000001427 coherent effect Effects 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 239000010931 gold Substances 0.000 description 1

- 230000001939 inductive effect Effects 0.000 description 1

- 230000010365 information processing Effects 0.000 description 1

- 230000003993 interaction Effects 0.000 description 1

- 230000002452 interceptive effect Effects 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 238000003754 machining Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 238000003672 processing method Methods 0.000 description 1

- 230000005233 quantum mechanics related processes and functions Effects 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 229910052702 rhenium Inorganic materials 0.000 description 1

- WUAPFZMCVAUBPE-UHFFFAOYSA-N rhenium atom Chemical compound [Re] WUAPFZMCVAUBPE-UHFFFAOYSA-N 0.000 description 1

- 238000007788 roughening Methods 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N10/00—Quantum computing, i.e. information processing based on quantum-mechanical phenomena

- G06N10/40—Physical realisations or architectures of quantum processors or components for manipulating qubits, e.g. qubit coupling or qubit control

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L25/0657—Stacked arrangements of devices

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N10/00—Quantum computing, i.e. information processing based on quantum-mechanical phenomena

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/5222—Capacitive arrangements or effects of, or between wiring layers

- H01L23/5225—Shielding layers formed together with wiring layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/552—Protection against radiation, e.g. light or electromagnetic waves

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L24/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L24/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N60/00—Superconducting devices

- H10N60/20—Permanent superconducting devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

- H01L2224/131—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/13101—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of less than 400°C

- H01L2224/13109—Indium [In] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

- H01L2224/131—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/13101—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of less than 400°C

- H01L2224/13116—Lead [Pb] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

- H01L2224/131—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/13163—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than 1550°C

- H01L2224/13164—Palladium [Pd] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

- H01L2224/131—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/13163—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than 1550°C

- H01L2224/13179—Niobium [Nb] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

- H01L2224/131—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/13163—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than 1550°C

- H01L2224/13183—Rhenium [Re] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/1354—Coating

- H01L2224/13599—Material

- H01L2224/136—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/13638—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/13644—Gold [Au] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16135—Disposition the bump connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/16145—Disposition the bump connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06513—Bump or bump-like direct electrical connections between devices, e.g. flip-chip connection, solder bumps

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Computer Hardware Design (AREA)

- Theoretical Computer Science (AREA)

- Data Mining & Analysis (AREA)

- Mathematical Analysis (AREA)

- Pure & Applied Mathematics (AREA)

- Computing Systems (AREA)

- General Engineering & Computer Science (AREA)

- Mathematical Physics (AREA)

- Software Systems (AREA)

- Mathematical Optimization (AREA)

- Evolutionary Computation (AREA)

- Computational Mathematics (AREA)

- Artificial Intelligence (AREA)

- Health & Medical Sciences (AREA)

- Electromagnetism (AREA)

- Toxicology (AREA)

- Superconductor Devices And Manufacturing Methods Thereof (AREA)

Description

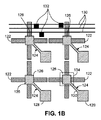

102 第1のチップ

104 第2のチップ

106 バンプボンド

108 ギャップ

122 超伝導キュビット

124 キュビット読み出しデバイス

126 パッド要素

128 共振器要素

130 細長アーム、制御ワイヤ

132 パッド

134 読み出し領域

202 第1のチップ

204 第2のチップ

214 超伝導体接地面、接地面の部分

216 誘電体層

218 遮蔽層

220a 側壁

220b 側壁

222a キュビット、超伝導キュビットの部分

222b キュビット、超伝導キュビットの部分

222c キュビット、超伝導キュビットの部分

224a キュビット読み出しデバイス

224b キュビット読み出しデバイス

226a パッド要素

226b パッド要素

228a 共振器要素

228b 共振器要素

230 配線要素

302 第1のチップ

304 第2のチップ

314 超伝導体接地面、接地面の部分

316 誘電体層

318 遮蔽層

320 バンプボンド

322a キュビット、超伝導キュビットの部分

324 キュビット読み出しデバイス

326 ビア

328 接触パッド

330 配線要素

404 チップ

415 側壁

416 誘電体層

418 第2の超伝導体層

424 第1の超伝導体層

426 ビア

428 接触パッド

430 配線要素

450 キュビット読み出し要素

460 キュビット制御要素

502 チップ

504 第1の超伝導体層

506 制御ワイヤ

508 誘電体層

510 第2の超伝導体層

512 側壁

518 キュビット読み出し要素

602 チップ

604 第1の超伝導体層

606 超伝導体材料の層

608 超伝導体材料の層

610 超伝導体材料の層

612 誘電体材料の層

614 誘電体材料の層

616 誘電体材料の層

618 誘電体材料の層

620 ビアインターコネクト

622 ビアインターコネクト

624 ビアインターコネクト

626 ビアインターコネクト

628 最上層

630 キュビット制御要素

632 遮蔽層

Claims (21)

- 第1の誘電体基板と、

前記第1の誘電体基板上の超伝導キュビットと

を含む第1のチップと、

前記第1のチップに結合された第2のチップであって、

第2の誘電体基板と、

前記第2の誘電体基板上のキュビット読み出し要素と、

前記第2の誘電体基板上の制御ワイヤと、

前記制御ワイヤを覆う誘電体層と、

前記誘電体層を覆う遮蔽層と

を含む第2のチップと

を含み、

前記遮蔽層は、前記制御ワイヤからの電磁場と前記超伝導キュビットからの電磁場とを互いに干渉しないように隔離することによって、前記第2のチップ上の前記制御ワイヤと前記第1のチップ上の前記超伝導キュビットとの間のクロストークを低減するように配置されている、デバイス。 - 前記誘電体層は、前記キュビット読み出し要素を露出させる開口を含む、請求項1に記載のデバイス。

- 前記誘電体層は、約1GHzと約10GHzとの間の周波数で約10−5より大きい損失正接を有する誘電体材料を含む、請求項1または2に記載のデバイス。

- 前記超伝導キュビットは読み出し領域を含み、

前記キュビット読み出し要素は前記超伝導キュビットの前記読み出し領域と重なる、請求項1から3のいずれか一項に記載のデバイス。 - 前記キュビット読み出し要素は、パッド要素に電気的に結合された共振器要素を含み、前記共振器要素が前記超伝導キュビットの前記読み出し領域と重なることなく、前記パッド要素は前記超伝導キュビットの前記読み出し領域と重なる、請求項4に記載のデバイス。

- 前記第1のチップは超伝導体接地面を含み、前記共振器要素は前記超伝導体接地面と重なる、請求項5に記載のデバイス。

- 前記誘電体層は、

前記誘電体層の表面から前記誘電体層を通って前記制御ワイヤまで延びるビアと、

前記ビア内にあり、前記制御ワイヤに電気的に結合されたインターコネクトと、

前記誘電体層の前記表面上にあり、前記インターコネクトに電気的に結合された制御接点と

を含む、請求項1から6のいずれか一項に記載のデバイス。 - 前記制御接点は前記遮蔽層によって横方向に囲まれ、前記遮蔽層から物理的に分離されている、請求項7に記載のデバイス。

- 前記制御接点は前記超伝導キュビットと重なる、請求項7または8に記載のデバイス。

- 前記制御接点は、前記超伝導キュビットと重なることなく、前記超伝導キュビットから横方向にずれている、請求項7から9のいずれか一項に記載のデバイス。

- 前記遮蔽層は前記誘電体層の側壁を覆っている、請求項1から10のいずれか一項に記載のデバイス。

- 前記キュビット読み出し要素、前記制御ワイヤ、および前記遮蔽層のそれぞれは超伝導体である、請求項1から11のいずれか一項に記載のデバイス。

- 前記第2のチップは、複数の制御ワイヤと、複数の誘電体層とを含み、

前記複数の制御ワイヤは前記複数の誘電体層内に埋め込まれ、

前記遮蔽層は前記複数の誘電体層を覆っている、

請求項1から12のいずれか一項に記載のデバイス。 - 前記第1のチップは前記第2のチップにバンプボンディングされている、請求項1から13のいずれか一項に記載のデバイス。

- 第1の誘電体基板と、

前記第1の誘電体基板上の超伝導キュビットと

を含む第1のチップを提供するステップと、

第2のチップを提供するステップであって、

第2の誘電体基板を提供するステップと、

前記第2の誘電体基板上に第1の超伝導体層を形成するステップと、

前記第1の超伝導体層が制御ワイヤを含むように前記第1の超伝導体層をパターニングするステップと、

前記制御ワイヤを含む前記第1の超伝導体層上に誘電体層を形成するステップと、

前記誘電体層をパターニングしてパターニングされた誘電体層を提供するステップと、

前記パターニングされた誘電体層上に第2の超伝導体層を形成するステップと、

前記第2の超伝導体層と前記第1の超伝導体層とをパターニングしてキュビット読み出し要素および遮蔽層を提供するステップと

を含む、ステップと、

前記第2のチップを前記第1のチップに結合するステップと

を含み、

前記遮蔽層は、前記制御ワイヤからの電磁場と前記超伝導キュビットからの電磁場とを互いに干渉しないように隔離することによって、前記第2のチップ上の前記制御ワイヤと前記第1のチップ上の前記超伝導キュビットとの間のクロストークを低減するように配置される、方法。 - 前記誘電体層をパターニングするステップは、前記誘電体層にビアを形成して前記制御ワイヤの一部を露出させるステップであって、前記ビアは前記誘電体層の表面から前記制御ワイヤの露出した前記一部まで延びる、ステップを含む、請求項15に記載の方法。

- 前記第2の超伝導体層を形成するステップは、前記ビア内にインターコネクトを形成するステップであって、前記インターコネクトは前記制御ワイヤの露出した前記一部と接触する、ステップを含む、請求項16に記載の方法。

- 前記第2の超伝導体層をパターニングするステップは、前記誘電体層の前記表面上に制御接点を形成するステップを含む、請求項17に記載の方法。

- 前記キュビット読み出し要素が前記超伝導キュビットと重なるように結合する前に、前記第2の誘電体基板を前記第1のチップに位置合わせするステップ

をさらに含む、請求項15に記載の方法。 - 第1のチップを第2のチップに結合する方法であって、

前記第1のチップを提供するステップであって、前記第1のチップは、第1の誘電体基板と、前記第1の誘電体基板上の超伝導キュビットとを含む、ステップと、

前記第2のチップを提供するステップであって、前記第2のチップは、第2の誘電体基板と、前記第2の誘電体基板上のキュビット読み出し要素と、前記第2の誘電体基板上の制御ワイヤと、前記制御ワイヤを覆う誘電体層と、前記誘電体層を覆う遮蔽層とを含む、ステップと、

超伝導体バンプボンドで前記第1のチップを前記第2のチップに結合するステップと

を含み、

前記遮蔽層は、前記制御ワイヤからの電磁場と前記超伝導キュビットからの電磁場とを互いに干渉しないように隔離することによって、前記第2のチップ上の前記制御ワイヤと前記第1のチップ上の前記超伝導キュビットとの間のクロストークを低減するように配置される、方法。 - 第1の誘電体基板と、

前記第1の誘電体基板上の超伝導キュビットと

を含む第1のチップと、

前記第1のチップに結合された第2のチップであって、

第2の誘電体基板と、

前記第2の誘電体基板上の第1の超伝導体層であって、前記第1の超伝導体層の第1の領域がキュビット読み出し要素を形成し、前記第1の超伝導体層の第2の領域がキュビット制御要素を形成する、第1の超伝導体層と、

前記第1の超伝導体層の前記第2の領域上の誘電体層と、

前記キュビット制御要素の一部を露出させるための前記誘電体層内のビアであって、前記誘電体層の表面から前記キュビット制御要素の露出した前記一部まで延びる、ビアと、

前記誘電体層上の第2の超伝導体層であって、前記第2の超伝導体層は前記ビア内にインターコネクトを形成し、前記インターコネクトは、前記キュビット制御要素の露出した前記一部に接触し、前記第2の超伝導体層は、前記インターコネクトから電気的に隔離された遮蔽層を形成する、第2の超伝導体層と

を含む第2のチップと

を含み、

前記遮蔽層は、前記キュビット制御要素からの電磁場と前記超伝導キュビットからの電磁場とを互いに干渉しないように隔離することによって、前記第2のチップ上の前記キュビット制御要素と前記第1のチップ上の前記超伝導キュビットとの間のクロストークを低減するように配置されている、量子コンピューティング回路デバイス。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201762470694P | 2017-03-13 | 2017-03-13 | |

| US62/470,694 | 2017-03-13 | ||

| PCT/US2017/066574 WO2018169585A1 (en) | 2017-03-13 | 2017-12-15 | Integrating circuit elements in a stacked quantum computing device |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2020511794A JP2020511794A (ja) | 2020-04-16 |

| JP6810280B2 true JP6810280B2 (ja) | 2021-01-06 |

Family

ID=60935992

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019550195A Active JP6810280B2 (ja) | 2017-03-13 | 2017-12-15 | 積層型量子コンピューティングデバイスにおける回路要素の集積 |

Country Status (8)

| Country | Link |

|---|---|

| US (3) | US11436516B2 (ja) |

| EP (2) | EP3580702B1 (ja) |

| JP (1) | JP6810280B2 (ja) |

| KR (1) | KR102217205B1 (ja) |

| CN (2) | CN110431568B (ja) |

| AU (1) | AU2017404536B2 (ja) |

| CA (1) | CA3056596C (ja) |

| WO (1) | WO2018169585A1 (ja) |

Families Citing this family (36)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2013180780A2 (en) | 2012-03-08 | 2013-12-05 | D-Wave Systems Inc. | Systems and methods for fabrication of superconducting integrated circuits |

| US10068181B1 (en) * | 2015-04-27 | 2018-09-04 | Rigetti & Co, Inc. | Microwave integrated quantum circuits with cap wafer and methods for making the same |

| JP7223711B2 (ja) | 2017-02-01 | 2023-02-16 | ディー-ウェイブ システムズ インコーポレイテッド | 超伝導集積回路の製造のためのシステム及び方法 |

| AU2017404530B2 (en) | 2017-03-13 | 2020-05-14 | Google Llc | Integrating circuit elements in a stacked quantum computing device |

| US11121301B1 (en) | 2017-06-19 | 2021-09-14 | Rigetti & Co, Inc. | Microwave integrated quantum circuits with cap wafers and their methods of manufacture |

| US10811588B2 (en) * | 2018-08-06 | 2020-10-20 | International Business Machines Corporation | Vertical dispersive readout of qubits of a lattice surface code architecture |

| CN109494218B (zh) * | 2018-09-30 | 2021-07-30 | 华东计算技术研究所(中国电子科技集团公司第三十二研究所) | 双面超导量子芯片 |

| US10720563B1 (en) | 2018-11-13 | 2020-07-21 | Google Llc | Quantum processor design to increase control footprint |

| US20200152851A1 (en) | 2018-11-13 | 2020-05-14 | D-Wave Systems Inc. | Systems and methods for fabricating superconducting integrated circuits |

| US10692795B2 (en) * | 2018-11-13 | 2020-06-23 | International Business Machines Corporation | Flip chip assembly of quantum computing devices |

| WO2020168097A1 (en) | 2019-02-15 | 2020-08-20 | D-Wave Systems Inc. | Kinetic inductance for couplers and compact qubits |

| US10840428B2 (en) * | 2019-03-07 | 2020-11-17 | International Business Machines Corporation | Scalable quantum devices with vertical coaxial resonators |

| US10796069B1 (en) * | 2019-06-06 | 2020-10-06 | International Business Machines Corporation | Bump connection placement in quantum devices in a flip chip configuration |

| US10944039B2 (en) | 2019-06-19 | 2021-03-09 | International Business Machines Corporation | Fabricating transmon qubit flip-chip structures for quantum computing devices |

| JP7427914B2 (ja) * | 2019-10-30 | 2024-02-06 | 日本電気株式会社 | 超伝導回路装置、スペーサ、及び超伝導回路装置の製造方法 |

| US11568296B2 (en) * | 2019-12-11 | 2023-01-31 | International Business Machines Corporation | Highway jumper to enable long range connectivity for superconducting quantum computer chip |

| JP7528564B2 (ja) | 2020-06-29 | 2024-08-06 | 日本電気株式会社 | 量子デバイス及びその製造方法 |

| EP3937093B1 (en) * | 2020-07-09 | 2024-09-04 | IQM Finland Oy | Quantum computing circuit comprising a plurality of chips and method for manufacturing the same |

| CN111967603B (zh) * | 2020-09-01 | 2022-04-08 | 腾讯科技(深圳)有限公司 | 量子芯片、量子处理器及量子计算机 |

| CA3198725A1 (en) * | 2020-10-14 | 2022-06-16 | Daniel Yohannes | Interconnections between quantum computing module and non-quantum processing modules in quantum computing systems |

| US11469485B2 (en) | 2020-10-21 | 2022-10-11 | International Business Machines Corporation | Embedded microstrip transmission line |

| US12033981B2 (en) * | 2020-12-16 | 2024-07-09 | International Business Machines Corporation | Create a protected layer for interconnects and devices in a packaged quantum structure |

| EP4227862A4 (en) * | 2020-12-31 | 2024-04-24 | Origin Quantum Computing Technology (Hefei) Co., Ltd | SUPERCONDUCTING QUANTUM CHIP STRUCTURE AND FABRICATION METHOD FOR SUPERCONDUCTING QUANTUM CHIP |

| WO2022232717A2 (en) * | 2021-02-17 | 2022-11-03 | Cornell University | Integrated quantum computing with epitaxial materials |

| WO2022178130A1 (en) * | 2021-02-19 | 2022-08-25 | D-Wave Systems Inc. | Systems and methods for fabrication of superconducting integrated circuits with improved coherence |

| CN115050886B (zh) * | 2021-03-09 | 2024-08-16 | 本源量子计算科技(合肥)股份有限公司 | 一种量子芯片及制备方法 |

| EP4352664A1 (en) | 2021-06-11 | 2024-04-17 | Seeqc Inc. | System and method of flux bias for superconducting quantum circuits |

| US20240284805A1 (en) * | 2021-07-01 | 2024-08-22 | MAX-PLANCK-Gesellschaft zur Förderung der Wissenschaften e.V. | Method for producing a solid-state component, solid-state component, quantum component and apparatus for producing a solid-state component |

| WO2023284816A1 (zh) * | 2021-07-14 | 2023-01-19 | 合肥本源量子计算科技有限责任公司 | 一种量子芯片、量子计算机及量子芯片制备方法 |

| CN113725208A (zh) * | 2021-08-13 | 2021-11-30 | 中国科学院物理研究所 | 一种三维量子芯片及其制备方法 |

| WO2023132063A1 (ja) | 2022-01-07 | 2023-07-13 | 富士通株式会社 | 量子演算装置及び量子演算装置の製造方法 |

| CN114757140B (zh) * | 2022-03-31 | 2024-06-04 | 本源科仪(成都)科技有限公司 | 量子比特版图的布线方法、装置、电子设备及存储介质 |

| WO2023188391A1 (ja) * | 2022-03-31 | 2023-10-05 | 富士通株式会社 | 量子デバイス及び量子デバイスの製造方法 |

| WO2024102504A2 (en) * | 2022-08-09 | 2024-05-16 | 1372934 B.C. Ltd. | Systems and methods for fabrication of superconducting integrated circuits having flip-chip arrangements with high coherence devices |

| CN115312656A (zh) * | 2022-09-02 | 2022-11-08 | 量子科技长三角产业创新中心 | 一种超导量子约瑟夫森结及其制备方法 |

| WO2024129567A2 (en) | 2022-12-13 | 2024-06-20 | Google Llc | Multi-layer chip architecture and fabrication |

Family Cites Families (28)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS59138390A (ja) * | 1983-01-28 | 1984-08-08 | Hitachi Ltd | 超電導スイツチング装置 |

| JP2964112B2 (ja) * | 1992-08-11 | 1999-10-18 | セイコーインスツルメンツ株式会社 | 直流駆動型超伝導量子干渉素子 |

| JP2835307B2 (ja) * | 1996-01-29 | 1998-12-14 | 株式会社移動体通信先端技術研究所 | 超伝導平面回路 |

| JP5289673B2 (ja) * | 2005-10-21 | 2013-09-11 | 中国電力株式会社 | 超電導接合素子および超電導接合回路 |

| CA2667640C (en) * | 2006-12-01 | 2016-10-04 | D-Wave Systems, Inc. | Superconducting shielding for use with an intergrated circuit for quantum computing |

| US8301214B1 (en) | 2010-01-08 | 2012-10-30 | Hypres, Inc. | System and method for providing multi-conductive layer metallic interconnects for superconducting integrated circuits |

| CA2898598C (en) * | 2013-01-18 | 2023-01-03 | Yale University | Superconducting device with at least one enclosure |

| KR102192270B1 (ko) | 2013-01-18 | 2020-12-18 | 예일 유니버시티 | 적어도 하나의 인클로저를 구비한 초전도 디바이스를 제조하는 방법 |

| US9219298B2 (en) * | 2013-03-15 | 2015-12-22 | International Business Machines Corporation | Removal of spurious microwave modes via flip-chip crossover |

| CN107408224B (zh) * | 2015-02-27 | 2022-09-13 | 耶鲁大学 | 将平面量子位耦合至非平面共振器的技术以及相关系统 |

| US9836699B1 (en) * | 2015-04-27 | 2017-12-05 | Rigetti & Co. | Microwave integrated quantum circuits with interposer |

| US10068181B1 (en) * | 2015-04-27 | 2018-09-04 | Rigetti & Co, Inc. | Microwave integrated quantum circuits with cap wafer and methods for making the same |

| US10381542B2 (en) * | 2015-04-30 | 2019-08-13 | International Business Machines Corporation | Trilayer Josephson junction structure with small air bridge and no interlevel dielectric for superconducting qubits |

| EP3266063B1 (en) * | 2015-05-14 | 2020-03-18 | D-Wave Systems Inc. | Frequency multiplexed resonator input and/or output for a superconducting device |

| US9524470B1 (en) * | 2015-06-12 | 2016-12-20 | International Business Machines Corporation | Modular array of vertically integrated superconducting qubit devices for scalable quantum computing |

| US10134972B2 (en) * | 2015-07-23 | 2018-11-20 | Massachusetts Institute Of Technology | Qubit and coupler circuit structures and coupling techniques |

| JP6883870B2 (ja) * | 2016-01-15 | 2021-06-09 | イェール ユニバーシティーYale University | 2キュービット量子状態の操作のための技術ならびに関連のある系および方法 |

| AU2017404530B2 (en) * | 2017-03-13 | 2020-05-14 | Google Llc | Integrating circuit elements in a stacked quantum computing device |

| US11362257B2 (en) | 2017-05-16 | 2022-06-14 | National Institute Of Advanced Industrial Science And Technology | Quantum bit device |

| US10535809B1 (en) * | 2017-08-30 | 2020-01-14 | Rigetti & Co, Inc. | Substrate materials for quantum processors |

| US10305015B1 (en) * | 2017-11-30 | 2019-05-28 | International Business Machines Corporation | Low loss architecture for superconducting qubit circuits |

| US10811588B2 (en) * | 2018-08-06 | 2020-10-20 | International Business Machines Corporation | Vertical dispersive readout of qubits of a lattice surface code architecture |

| US11121302B2 (en) * | 2018-10-11 | 2021-09-14 | SeeQC, Inc. | System and method for superconducting multi-chip module |

| US11223355B2 (en) * | 2018-12-12 | 2022-01-11 | Yale University | Inductively-shunted transmon qubit for superconducting circuits |

| US11011693B2 (en) * | 2019-06-24 | 2021-05-18 | Intel Corporation | Integrated quantum circuit assemblies for cooling apparatus |

| US10978631B2 (en) * | 2019-09-11 | 2021-04-13 | International Business Machines Corporation | Combined dolan bridge and quantum dot josephson junction in series |

| KR20210128787A (ko) * | 2020-04-17 | 2021-10-27 | 삼성전자주식회사 | 양자 컴퓨팅 장치 |

| US20230200260A1 (en) | 2021-12-16 | 2023-06-22 | International Business Machines Corporation | Scaled quantum circuits |

-

2017

- 2017-12-15 WO PCT/US2017/066574 patent/WO2018169585A1/en active Search and Examination

- 2017-12-15 CN CN201780088460.6A patent/CN110431568B/zh active Active

- 2017-12-15 JP JP2019550195A patent/JP6810280B2/ja active Active

- 2017-12-15 AU AU2017404536A patent/AU2017404536B2/en active Active

- 2017-12-15 EP EP17825709.3A patent/EP3580702B1/en active Active

- 2017-12-15 CN CN202410181623.7A patent/CN118133978A/zh active Pending

- 2017-12-15 KR KR1020197026011A patent/KR102217205B1/ko active IP Right Grant

- 2017-12-15 CA CA3056596A patent/CA3056596C/en active Active

- 2017-12-15 EP EP21153943.2A patent/EP3852021B1/en active Active

- 2017-12-15 US US16/493,400 patent/US11436516B2/en active Active

-

2022

- 2022-09-02 US US17/902,731 patent/US12033029B2/en active Active

- 2022-09-02 US US17/902,695 patent/US20230004847A1/en active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| CN118133978A (zh) | 2024-06-04 |

| KR102217205B1 (ko) | 2021-02-18 |

| EP3580702B1 (en) | 2021-03-17 |

| KR20190113923A (ko) | 2019-10-08 |

| AU2017404536A1 (en) | 2019-09-12 |

| CN110431568B (zh) | 2024-03-08 |

| CA3056596C (en) | 2022-01-04 |

| US20200012961A1 (en) | 2020-01-09 |

| AU2017404536B2 (en) | 2020-05-14 |

| EP3852021A1 (en) | 2021-07-21 |

| EP3580702A1 (en) | 2019-12-18 |

| WO2018169585A1 (en) | 2018-09-20 |

| CN110431568A (zh) | 2019-11-08 |

| US20230004848A1 (en) | 2023-01-05 |

| CA3056596A1 (en) | 2018-09-20 |

| JP2020511794A (ja) | 2020-04-16 |

| US11436516B2 (en) | 2022-09-06 |

| EP3852021B1 (en) | 2024-07-31 |

| US12033029B2 (en) | 2024-07-09 |

| US20230004847A1 (en) | 2023-01-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6810280B2 (ja) | 積層型量子コンピューティングデバイスにおける回路要素の集積 | |

| CN110402446B (zh) | 在堆叠量子计算设备中的集成电路元件 | |

| JP7392037B2 (ja) | フリップチップ形状の低フットプリント共振器 | |

| US20240162050A1 (en) | Signal distribution for a quantum computing system |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20191031 |

|

| A529 | Written submission of copy of amendment under article 34 pct |

Free format text: JAPANESE INTERMEDIATE CODE: A529 Effective date: 20191031 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20191031 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20201116 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20201210 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6810280 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |