JP6776205B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP6776205B2 JP6776205B2 JP2017180736A JP2017180736A JP6776205B2 JP 6776205 B2 JP6776205 B2 JP 6776205B2 JP 2017180736 A JP2017180736 A JP 2017180736A JP 2017180736 A JP2017180736 A JP 2017180736A JP 6776205 B2 JP6776205 B2 JP 6776205B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- trench

- insulating layer

- semiconductor

- gate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 167

- 238000004519 manufacturing process Methods 0.000 title claims description 37

- 239000012535 impurity Substances 0.000 claims description 14

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 8

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 8

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 2

- 238000001039 wet etching Methods 0.000 claims description 2

- 239000010410 layer Substances 0.000 description 114

- 239000011229 interlayer Substances 0.000 description 23

- 238000000034 method Methods 0.000 description 23

- 239000000463 material Substances 0.000 description 12

- 238000001020 plasma etching Methods 0.000 description 8

- 238000005229 chemical vapour deposition Methods 0.000 description 7

- 230000010354 integration Effects 0.000 description 7

- 238000005530 etching Methods 0.000 description 5

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 5

- 238000009413 insulation Methods 0.000 description 4

- 229910052751 metal Inorganic materials 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 3

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000001459 lithography Methods 0.000 description 2

- 230000000873 masking effect Effects 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 229910015900 BF3 Inorganic materials 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- -1 boron fluoride ions Chemical class 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/10—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode not carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/1095—Body region, i.e. base region, of DMOS transistors or IGBTs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7827—Vertical transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/08—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/0843—Source or drain regions of field-effect devices

- H01L29/0847—Source or drain regions of field-effect devices of field-effect transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/401—Multistep manufacturing processes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

- H01L29/41725—Source or drain electrodes for field effect devices

- H01L29/41766—Source or drain electrodes for field effect devices with at least part of the source or drain electrode having contact below the semiconductor surface, e.g. the source or drain electrode formed at least partially in a groove or with inclusions of conductor inside the semiconductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42356—Disposition, e.g. buried gate electrode

- H01L29/4236—Disposition, e.g. buried gate electrode within a trench, e.g. trench gate electrode, groove gate electrode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66234—Bipolar junction transistors [BJT]

- H01L29/66325—Bipolar junction transistors [BJT] controlled by field-effect, e.g. insulated gate bipolar transistors [IGBT]

- H01L29/66333—Vertical insulated gate bipolar transistors

- H01L29/66348—Vertical insulated gate bipolar transistors with a recessed gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66666—Vertical transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66674—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/66712—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/66734—Vertical DMOS transistors, i.e. VDMOS transistors with a step of recessing the gate electrode, e.g. to form a trench gate electrode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/739—Transistor-type devices, i.e. able to continuously respond to applied control signals controlled by field-effect, e.g. bipolar static induction transistors [BSIT]

- H01L29/7393—Insulated gate bipolar mode transistors, i.e. IGBT; IGT; COMFET

- H01L29/7395—Vertical transistors, e.g. vertical IGBT

- H01L29/7396—Vertical transistors, e.g. vertical IGBT with a non planar surface, e.g. with a non planar gate or with a trench or recess or pillar in the surface of the emitter, base or collector region for improving current density or short circuiting the emitter and base regions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/739—Transistor-type devices, i.e. able to continuously respond to applied control signals controlled by field-effect, e.g. bipolar static induction transistors [BSIT]

- H01L29/7393—Insulated gate bipolar mode transistors, i.e. IGBT; IGT; COMFET

- H01L29/7395—Vertical transistors, e.g. vertical IGBT

- H01L29/7396—Vertical transistors, e.g. vertical IGBT with a non planar surface, e.g. with a non planar gate or with a trench or recess or pillar in the surface of the emitter, base or collector region for improving current density or short circuiting the emitter and base regions

- H01L29/7397—Vertical transistors, e.g. vertical IGBT with a non planar surface, e.g. with a non planar gate or with a trench or recess or pillar in the surface of the emitter, base or collector region for improving current density or short circuiting the emitter and base regions and a gate structure lying on a slanted or vertical surface or formed in a groove, e.g. trench gate IGBT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/7813—Vertical DMOS transistors, i.e. VDMOS transistors with trench gate electrode, e.g. UMOS transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7816—Lateral DMOS transistors, i.e. LDMOS transistors

- H01L29/7825—Lateral DMOS transistors, i.e. LDMOS transistors with trench gate electrode

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

- H10B63/30—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices comprising selection components having three or more electrodes, e.g. transistors

- H10B63/34—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices comprising selection components having three or more electrodes, e.g. transistors of the vertical channel field-effect transistor type

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Electrodes Of Semiconductors (AREA)

Description

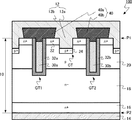

本実施形態の半導体装置は、第1の面と、第1の面と対向する第2の面を有する半導体層と、第1の面に接する第1の電極と、第2の面に接する第2の電極と、半導体層の中に設けられた第1導電型の第1の半導体領域と、半導体層の中に設けられ、第1の半導体領域と第2の面との間に位置する第2導電型の第2の半導体領域と、半導体層の中に設けられ、第1の半導体領域と第1の面との間に位置する第2導電型の第3の半導体領域と、半導体層の中に設けられた第1のゲート電極と、半導体層の中に設けられ、第1のゲート電極との間に第1の半導体領域が位置する第2のゲート電極と、第1のゲート電極と第1の半導体領域との間に設けられた第1のゲート絶縁膜と、第2のゲート電極と第1の半導体領域との間に設けられた第2のゲート絶縁膜と、第1のゲート電極と第1の電極との間、及び、第2のゲート電極と第1の電極との間に設けられた絶縁層と、を備える。そして、第1の電極が第1の領域と第2の領域を有し、第1の領域は半導体層に接し、第1の領域は第2の領域と第1の半導体領域との間に位置し、第1の領域の一部は第1のゲート電極と第2のゲート電極との間に位置し、第1の領域の別の一部は絶縁層の第1の部分と第2の部分との間に挟まれ、第1の領域の別の一部は逆テーパ形状を有する。

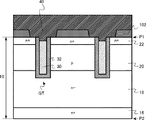

ゲート電極30は、例えば、CVD法による膜堆積と、等方性のドライエッチング法によるエッチバックにより形成する。

12 ソース電極(第1の電極、電極)

12a コンタクト領域(第1の領域)

12b 配線領域(第2の領域)

14 ドレイン電極(第2の電極)

16 ドレイン領域

18 ドリフト領域(第2の半導体領域)

20 ベース領域(第1の半導体領域)

22 ソース領域(第3の半導体領域)

24 ベースコンタクト領域(第4の半導体領域)

30 ゲート電極

30a 第1のゲート電極

30b 第2のゲート電極

32 ゲート絶縁膜

32a 第1のゲート絶縁膜

32b 第2のゲート絶縁膜

40 層間絶縁層(絶縁層、第2の絶縁層)

40a 第1の部分

40b 第2の部分

100 縦型MOSFET(半導体装置)

102 第1のマスク材(第1の絶縁層)

104 第1の開口部

106 第1の側壁

108 第2の開口部

110 第2の側壁

GT ゲートトレンチ(第1のトレンチ)

GT1 第1のゲートトレンチ(第1のトレンチ)

GT2 第2のゲートトレンチ(第2のトレンチ)

CT コンタクトトレンチ(第3のトレンチ、第2のトレンチ)

P1 第1の面

P2 第2の面

Claims (6)

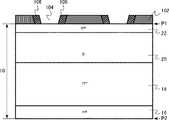

- 第1の面と、前記第1の面と対向する第2の面を有し、第1導電型の第1の半導体領域と、前記第1の半導体領域と前記第2の面との間に位置する第2導電型の第2の半導体領域と、前記第1の半導体領域と前記第1の面との間に位置する第2導電型の第3の半導体領域と、を有する半導体層の上に、第1の絶縁層を形成し、

前記第1の絶縁層に第1の開口部を形成し、

前記第1の開口部の内壁面に第1の側壁を形成し、

前記半導体層に、前記第1の絶縁層と前記第1の側壁をマスクに、前記第1の半導体領域よりも深い第1のトレンチを形成し、

前記第1のトレンチの中にゲート絶縁膜を形成し、

前記第1のトレンチの中の前記ゲート絶縁膜の上にゲート電極を形成し、

前記ゲート電極の上に第2の絶縁層を形成し、

前記第1の絶縁層の上の前記第2の絶縁層を除去し、

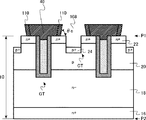

前記第1の絶縁層を除去して前記第2の絶縁層に第2の開口部を形成し、

前記第2の開口部の内壁面に逆テーパ形状を有する第2の側壁を形成し、

前記半導体層に、前記第2の絶縁層と前記第2の側壁をマスクに、前記第3の半導体領域よりも深く前記第1の半導体領域よりも浅い第2のトレンチを形成し、

前記第2の側壁の少なくとも一部を除去し、

前記第2のトレンチの中に電極を形成する半導体装置の製造方法。 - 第1の面と、前記第1の面と対向する第2の面を有し、第1導電型の第1の半導体領域と、前記第1の半導体領域と前記第2の面との間に位置する第2導電型の第2の半導体領域と、前記第1の半導体領域と前記第1の面との間に位置する第2導電型の第3の半導体領域と、を有する半導体層の上に、第1の絶縁層を形成し、

前記第1の絶縁層に第1の開口部を形成し、

前記第1の開口部の内壁面に第1の側壁を形成し、

前記半導体層に、前記第1の絶縁層と前記第1の側壁をマスクに、前記第1の半導体領域よりも深い第1のトレンチを形成し、

前記第1のトレンチの中にゲート絶縁膜を形成し、

前記第1のトレンチの中の前記ゲート絶縁膜の上にゲート電極を形成し、

前記ゲート電極の上に第2の絶縁層を形成し、

前記第1の絶縁層の上の前記第2の絶縁層を除去し、

前記第1の絶縁層を除去して前記第2の絶縁層に逆テーパ形状を有する第2の開口部を形成し、

前記第2の開口部の内壁面に第2の側壁を形成し、

前記半導体層に、前記第2の絶縁層と前記第2の側壁をマスクに、前記第3の半導体領域よりも深く前記第1の半導体領域よりも浅い第2のトレンチを形成し、

前記第2の側壁の少なくとも一部を除去し、

前記第2のトレンチの中に電極を形成する半導体装置の製造方法。 - 前記第2の側壁の少なくとも一部の除去は、ウェットエッチングによる請求項1又は請求項2記載の半導体装置の製造方法。

- 前記第1の開口部が順テーパ形状を有する請求項1ないし請求項3いずれか一項記載の半導体装置の製造方法。

- 前記第2のトレンチを形成した後、前記第2のトレンチの底部の前記半導体層の中に前記第1の半導体領域の第1導電型の不純物濃度よりも第1導電型の不純物濃度の高い第1導電型の第4の半導体領域を、更に形成する請求項1ないし請求項4いずれか一項記載の半導体装置の製造方法。

- 前記第1の絶縁層は窒化シリコンを含み、前記第2の絶縁層は酸化シリコンを含む請求項1ないし請求項5いずれか一項記載の半導体装置の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017180736A JP6776205B2 (ja) | 2017-09-20 | 2017-09-20 | 半導体装置の製造方法 |

| US15/912,711 US10546953B2 (en) | 2017-09-20 | 2018-03-06 | Semiconductor device including an electrode having a part with an inverse tapered shape |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017180736A JP6776205B2 (ja) | 2017-09-20 | 2017-09-20 | 半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2019057603A JP2019057603A (ja) | 2019-04-11 |

| JP2019057603A5 JP2019057603A5 (ja) | 2019-09-19 |

| JP6776205B2 true JP6776205B2 (ja) | 2020-10-28 |

Family

ID=65721160

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017180736A Active JP6776205B2 (ja) | 2017-09-20 | 2017-09-20 | 半導体装置の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US10546953B2 (ja) |

| JP (1) | JP6776205B2 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7319496B2 (ja) * | 2020-03-17 | 2023-08-02 | 株式会社東芝 | 半導体装置 |

| US11355630B2 (en) * | 2020-09-11 | 2022-06-07 | Wolfspeed, Inc. | Trench bottom shielding methods and approaches for trenched semiconductor device structures |

| JP7414677B2 (ja) * | 2020-09-15 | 2024-01-16 | 株式会社東芝 | 半導体装置及びその製造方法 |

| JP7387566B2 (ja) * | 2020-09-18 | 2023-11-28 | 株式会社東芝 | 半導体装置 |

| US11605717B2 (en) * | 2020-12-17 | 2023-03-14 | International Business Machines Corporation | Wrapped-around contact for vertical field effect transistor top source-drain |

| CN116666223B (zh) * | 2023-07-28 | 2023-11-03 | 江西萨瑞半导体技术有限公司 | 一种改善sgt阈值电压稳定性的工艺方法及sgt器件 |

Family Cites Families (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6551881B1 (en) * | 2001-10-01 | 2003-04-22 | Koninklijke Philips Electronics N.V. | Self-aligned dual-oxide umosfet device and a method of fabricating same |

| US7701001B2 (en) * | 2002-05-03 | 2010-04-20 | International Rectifier Corporation | Short channel trench power MOSFET with low threshold voltage |

| US6987305B2 (en) * | 2003-08-04 | 2006-01-17 | International Rectifier Corporation | Integrated FET and schottky device |

| US7390717B2 (en) * | 2004-02-09 | 2008-06-24 | International Rectifier Corporation | Trench power MOSFET fabrication using inside/outside spacers |

| JP2006344760A (ja) * | 2005-06-08 | 2006-12-21 | Sharp Corp | トレンチ型mosfet及びその製造方法 |

| JP2009302510A (ja) * | 2008-03-03 | 2009-12-24 | Fuji Electric Device Technology Co Ltd | トレンチゲート型半導体装置およびその製造方法 |

| JP2012174989A (ja) | 2011-02-23 | 2012-09-10 | Toshiba Corp | 半導体装置の製造方法 |

| JP2012199468A (ja) * | 2011-03-23 | 2012-10-18 | Toshiba Corp | 半導体装置の製造方法 |

| JP2013058575A (ja) * | 2011-09-07 | 2013-03-28 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP2013182934A (ja) * | 2012-02-29 | 2013-09-12 | Toshiba Corp | 半導体装置およびその製造方法 |

| JP5807597B2 (ja) * | 2012-03-26 | 2015-11-10 | 株式会社デンソー | 半導体装置及び半導体装置の製造方法 |

| JP2014033079A (ja) | 2012-08-03 | 2014-02-20 | Renesas Electronics Corp | 半導体装置の製造方法および半導体装置 |

| KR20140022517A (ko) * | 2012-08-13 | 2014-02-25 | 삼성전자주식회사 | 반도체 장치 및 그 제조 방법 |

| KR101792276B1 (ko) * | 2012-08-23 | 2017-11-02 | 매그나칩 반도체 유한회사 | 반도체 소자 및 그 소자의 제조 방법 |

| JP2014063852A (ja) | 2012-09-20 | 2014-04-10 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP2014110402A (ja) * | 2012-12-04 | 2014-06-12 | Rohm Co Ltd | 半導体装置 |

| JP5831526B2 (ja) * | 2013-01-17 | 2015-12-09 | 株式会社デンソー | 半導体装置およびその製造方法 |

| JP6036765B2 (ja) * | 2014-08-22 | 2016-11-30 | トヨタ自動車株式会社 | 半導体装置及び半導体装置の製造方法 |

| JP6478884B2 (ja) * | 2015-09-11 | 2019-03-06 | 株式会社東芝 | 半導体装置 |

| US10505028B2 (en) * | 2015-09-16 | 2019-12-10 | Fuji Electric Co., Ltd. | Semiconductor device including a shoulder portion and manufacturing method |

| JP6584966B2 (ja) * | 2016-01-12 | 2019-10-02 | 株式会社東芝 | 半導体装置、半導体装置の製造方法、インバータ回路、駆動装置、車両、及び昇降機 |

-

2017

- 2017-09-20 JP JP2017180736A patent/JP6776205B2/ja active Active

-

2018

- 2018-03-06 US US15/912,711 patent/US10546953B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20190088778A1 (en) | 2019-03-21 |

| US10546953B2 (en) | 2020-01-28 |

| JP2019057603A (ja) | 2019-04-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6776205B2 (ja) | 半導体装置の製造方法 | |

| US10121892B2 (en) | Semiconductor device | |

| JP6203697B2 (ja) | 半導体装置およびその製造方法 | |

| JP5799046B2 (ja) | 半導体装置 | |

| US9214526B2 (en) | Semiconductor device | |

| JP6047297B2 (ja) | 半導体装置 | |

| JP2007311557A (ja) | 半導体装置及びその製造方法 | |

| JP2019057596A (ja) | 半導体装置及びその製造方法 | |

| JP7073872B2 (ja) | スイッチング素子とその製造方法 | |

| TWI590449B (zh) | Silicon carbide semiconductor device, method of manufacturing the silicon carbide semiconductor device, and method of designing the silicon carbide semiconductor device | |

| CN106463542B (zh) | 半导体装置 | |

| JP2012174989A (ja) | 半導体装置の製造方法 | |

| JP6004109B2 (ja) | 半導体装置及びその製造方法 | |

| KR20160150349A (ko) | 전력 반도체 소자 | |

| JP2018198267A (ja) | 半導体装置及びその製造方法 | |

| US10388725B2 (en) | Semiconductor device and method of manufacturing semiconductor device | |

| JP5971218B2 (ja) | 半導体装置 | |

| TW202030841A (zh) | 斷閘極金氧半場效電晶體的閘極結構及其製造方法 | |

| JP5556863B2 (ja) | ワイドバンドギャップ半導体縦型mosfet | |

| JP2010040686A (ja) | 半導体装置およびその製造方法 | |

| US20160218190A1 (en) | Semiconductor device and method for manufacturing semiconductor device | |

| JP7159949B2 (ja) | 半導体装置 | |

| JP5151636B2 (ja) | トレンチゲートを有する横型半導体装置とその製造方法 | |

| US9905686B2 (en) | Insulated gate bipolar transistor with improved on/off resistance | |

| US9059283B1 (en) | Semiconductor structure |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180130 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190807 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20190807 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20200520 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20200602 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200729 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20200908 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20201007 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6776205 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |