JP6719692B1 - 電力変換装置 - Google Patents

電力変換装置 Download PDFInfo

- Publication number

- JP6719692B1 JP6719692B1 JP2020512896A JP2020512896A JP6719692B1 JP 6719692 B1 JP6719692 B1 JP 6719692B1 JP 2020512896 A JP2020512896 A JP 2020512896A JP 2020512896 A JP2020512896 A JP 2020512896A JP 6719692 B1 JP6719692 B1 JP 6719692B1

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- sub

- module

- semiconductor

- series

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 claims abstract description 79

- 238000004146 energy storage Methods 0.000 claims abstract description 21

- 238000006243 chemical reaction Methods 0.000 claims description 29

- 239000003990 capacitor Substances 0.000 description 54

- 238000010586 diagram Methods 0.000 description 19

- 230000006870 function Effects 0.000 description 10

- 238000000034 method Methods 0.000 description 6

- 238000004804 winding Methods 0.000 description 5

- 230000004048 modification Effects 0.000 description 4

- 238000012986 modification Methods 0.000 description 4

- 230000008901 benefit Effects 0.000 description 3

- 230000005540 biological transmission Effects 0.000 description 3

- 230000000052 comparative effect Effects 0.000 description 3

- 230000008569 process Effects 0.000 description 2

- 230000008859 change Effects 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 230000005611 electricity Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 239000013307 optical fiber Substances 0.000 description 1

- 230000001629 suppression Effects 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M7/00—Conversion of ac power input into dc power output; Conversion of dc power input into ac power output

- H02M7/42—Conversion of dc power input into ac power output without possibility of reversal

- H02M7/44—Conversion of dc power input into ac power output without possibility of reversal by static converters

- H02M7/48—Conversion of dc power input into ac power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M7/483—Converters with outputs that each can have more than two voltages levels

- H02M7/4835—Converters with outputs that each can have more than two voltages levels comprising two or more cells, each including a switchable capacitor, the capacitors having a nominal charge voltage which corresponds to a given fraction of the input voltage, and the capacitors being selectively connected in series to determine the instantaneous output voltage

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M7/00—Conversion of ac power input into dc power output; Conversion of dc power input into ac power output

- H02M7/42—Conversion of dc power input into ac power output without possibility of reversal

- H02M7/44—Conversion of dc power input into ac power output without possibility of reversal by static converters

- H02M7/48—Conversion of dc power input into ac power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M7/53—Conversion of dc power input into ac power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal

- H02M7/537—Conversion of dc power input into ac power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only, e.g. single switched pulse inverters

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/32—Means for protecting converters other than automatic disconnection

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Inverter Devices (AREA)

- Rectifiers (AREA)

Abstract

Description

<電力変換装置の全体構成>

図1は、電力変換装置1の概略構成図である。図1を参照して、電力変換装置1は、互いに直列接続された複数のサブモジュール(図1中の「SM」に対応)7を含むモジュラーマルチレベル変換器によって構成されている。電力変換装置1は、直流回路14と交流回路12との間で電力変換を行なう。電力変換装置1は、電力変換器2と、制御装置3とを含む。

交流電圧検出器10は、交流回路12のU相の交流電圧Vacu、V相の交流電圧Vacv、およびW相の交流電圧Vacwを検出する。交流電流検出器16は、交流回路12のU相の交流電流Iacu、V相の交流電流Iacv、およびW相の交流電流Iacwを検出する。直流電圧検出器11Aは、直流回路14に接続された正極直流端子Npの直流電圧Vdcpを検出する。直流電圧検出器11Bは、直流回路14に接続された負極直流端子Nnの直流電圧Vdcnを検出する。

図2は、図1の各レグ回路を構成するサブモジュールの一例を示す回路図である。具体的には、図2(a)に示すサブモジュール7は、ハーフブリッジ構成と呼ばれる回路構成を有する。以下では、図2(a)の回路構成を有する「サブモジュール7」を「サブモジュール7HB」とも称する。

実施の形態1では、複数のサブモジュール7のうちの規定数のサブモジュール7を、短絡事故電流を抑制する機能を有するサブモジュール7SUとして構成し、残りのサブモジュール7をサブモジュール7HBとして構成する。これにより、直流回路14の短絡事故時における短絡電流を抑制する。実施の形態1との比較のため、まず、複数のサブモジュール7のすべてがサブモジュール7HBで構成される比較例における短絡電流経路について説明する。

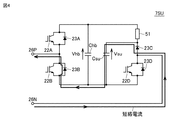

図4は、実施の形態1に従うサブモジュール7SU内の短絡電流経路を示す図である。ここでは、キャパシタChbの電圧Vhbと、キャパシタCsuの電圧Vsuとはほぼ同一となっているものとする。

図6は、実施の形態1に従う制御装置3の処理手順を示すフローチャートである。典型的には、以下の各ステップは、制御装置3の演算部によって実行される。

実施の形態1によると、電力変換用のキャパシタと、短絡電流の抑制用のキャパシタとを独自に有している。したがって、電力変換に適したキャパシタと、短絡電流の抑制に適したキャパシタとを個別に設計できるため、直流回路の短絡事故によって生じる事故電流を容易に抑制できる。結果として、サブモジュール内の素子の破損を防ぐことができる。

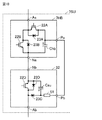

実施の形態1では、各サブモジュール7に流れる短絡電流を抑制することにより、サブモジュール内の素子の破損を防ぐ構成について説明した。実施の形態2では、サブモジュール7SUを用いて、バイパス回路に短絡電流を転流する構成について説明する。

実施の形態2によると、直流回路の短絡事故によって生じる事故電流をバイパス回路に転流することができる。結果として、サブモジュール内の半導体素子の破損を防ぐことができる。また、実施の形態1の構成例よりも、サブモジュール7SUの個数を全体として削減することができる。

(1)上述した実施の形態において、サブモジュール7HBと半導体回路32とを組み合わせることで、サブモジュール7SUに相当する回路を設けてもよい。

Claims (8)

- 直流回路と交流回路との間で電力変換を行なう電力変換装置であって、

直列接続された複数のサブモジュールを含むレグ回路を備え、

前記複数のサブモジュールのうちの少なくとも1つは第1サブモジュールであり、

前記第1サブモジュールは、第1エネルギー蓄積要素と、直列接続された2つのスイッチング素子を有する第1半導体回路と、第2半導体回路とを含み、

前記第1エネルギー蓄積要素、前記第1半導体回路、および前記第2半導体回路は、互いに並列接続されており、

前記第2半導体回路は、

直列接続されたスイッチング素子と半導体素子とを含む直列回路と、

前記直列回路に並列接続された第2エネルギー蓄積要素と、

前記直列回路および前記第2エネルギー蓄積要素を含む並列回路に直列接続された抵抗成分を有する素子とを含む、電力変換装置。 - 前記半導体素子は、ダイオードである、請求項1に記載の電力変換装置。

- 前記抵抗成分を有する素子は、抵抗素子、ダイオード、またはリアクトルである、請求項1または請求項2に記載の電力変換装置。

- 前記第1サブモジュールの数は、前記交流回路の電圧の最大値を前記第2エネルギー蓄積要素の電圧で除算した数よりも多い、請求項1〜請求項3のいずれか1項に記載の電力変換装置。

- 前記複数のサブモジュールのうち、前記第1サブモジュール以外の第2サブモジュールは、エネルギー蓄積要素と、直列接続された2つのスイッチング素子を有する半導体回路とが並列接続されたハーフブリッジ構成を有する、請求項1〜請求項4のいずれか1項に記載の電力変換装置。

- 前記レグ回路は、前記交流回路に接続された交流接続部と前記直流回路に接続された正極直流端子との間に設けられた第1アームと、前記交流接続部と前記直流回路に接続された負極直流端子との間に設けられた第2アームとを含み、

前記第1アームおよび前記第2アームの各々は、1以上のサブモジュール群を含み、

前記1以上のサブモジュール群の各々は、バイパス回路と並列接続されており、

前記1以上のサブモジュール群の各々は、1以上の前記第1サブモジュールと、1以上の第2サブモジュールとを含み、

前記第2サブモジュールは、エネルギー蓄積要素と、2つの半導体スイッチング素子を直列接続した半導体回路とが並列接続されたハーフブリッジ構成を有する、請求項1〜請求項4のいずれか1項に記載の電力変換装置。 - 前記バイパス回路は、前記負極直流端子から前記正極直流端子の方向が順方向となるように配置された少なくとも1つのダイオードを含む、請求項6に記載の電力変換装置。

- 前記サブモジュールに流れる電流を検出する電流検出器と、

前記複数のサブモジュールの各々を制御する制御装置とをさらに備え、

前記制御装置は、

前記電流検出器により検出された電流に基づいて、前記直流回路の短絡事故が発生したか否かを判定し、

前記直流回路の短絡事故が発生した場合に、前記レグ回路の前記複数のサブモジュールに含まれるすべてのスイッチング素子をオフにする、請求項1〜請求項7のいずれか1項に記載の電力変換装置。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| PCT/JP2019/047263 WO2021111526A1 (ja) | 2019-12-03 | 2019-12-03 | 電力変換装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP6719692B1 true JP6719692B1 (ja) | 2020-07-08 |

| JPWO2021111526A1 JPWO2021111526A1 (ja) | 2021-12-02 |

Family

ID=71402374

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2020512896A Active JP6719692B1 (ja) | 2019-12-03 | 2019-12-03 | 電力変換装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US20220385209A1 (ja) |

| EP (1) | EP4071996A4 (ja) |

| JP (1) | JP6719692B1 (ja) |

| WO (1) | WO2021111526A1 (ja) |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013121223A (ja) * | 2011-12-07 | 2013-06-17 | Hitachi Ltd | 電力変換装置 |

| WO2017168519A1 (ja) * | 2016-03-28 | 2017-10-05 | 三菱電機株式会社 | 電力変換装置 |

| JP6345379B1 (ja) * | 2017-08-09 | 2018-06-20 | 三菱電機株式会社 | 電力変換装置 |

| JP2019022313A (ja) * | 2017-07-14 | 2019-02-07 | 株式会社東芝 | 電力変換装置 |

| WO2019064705A1 (ja) * | 2017-09-26 | 2019-04-04 | 三菱電機株式会社 | 電力変換装置 |

Family Cites Families (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE10217889A1 (de) * | 2002-04-22 | 2003-11-13 | Siemens Ag | Stromversorgung mit einem Direktumrichter |

| DE102009057288B4 (de) * | 2009-12-01 | 2018-02-15 | Siemens Aktiengesellschaft | Umrichter für hohe Spannungen |

| AU2010348910B2 (en) * | 2010-03-18 | 2015-12-03 | Abb Research Ltd | Converter cell for cascaded converters, control system and method for bypassing a faulty converter cell |

| EP2747267B1 (en) * | 2012-12-18 | 2020-02-05 | General Electric Technology GmbH | Electrical apparatus including chain-link converter and protection circuit |

| EP2946464B1 (en) | 2013-01-21 | 2019-12-18 | ABB Schweiz AG | A multilevel converter with hybrid full-bridge cells |

| WO2014148100A1 (ja) * | 2013-03-18 | 2014-09-25 | 三菱電機株式会社 | 電力変換装置 |

| ES2792107T3 (es) * | 2013-07-15 | 2020-11-10 | Siemens Ag | Convertidor CC/CC modular multinivel para aplicaciones de corriente continua de alta tensión |

| DE102013219466A1 (de) * | 2013-09-26 | 2015-03-26 | Siemens Aktiengesellschaft | Multilevelumrichter |

| CN105099242B (zh) * | 2014-05-09 | 2018-09-11 | 南京南瑞继保电气有限公司 | 电压源型多电平换流器、直流输电系统、故障处理方法和装置 |

| CN105098812B (zh) * | 2014-05-22 | 2018-03-30 | 南京南瑞继保电气有限公司 | 一种三极柔性直流输电系统和方法 |

| US9871437B2 (en) * | 2014-07-10 | 2018-01-16 | University-Industry Foundation(UIF) | Fault current reduction structure of multi-level converter and apparatus using the fault current reduction structure |

| WO2016167114A1 (ja) * | 2015-04-13 | 2016-10-20 | 三菱電機株式会社 | 電力変換装置 |

| DE102015105889A1 (de) * | 2015-04-17 | 2016-10-20 | Ge Energy Power Conversion Technology Limited | Schaltmodul und Umrichter mit wenigstens einem Schaltmodul |

| US10199936B2 (en) * | 2015-05-27 | 2019-02-05 | Koninklijke Philips N.V. | DC to DC converter |

| EP3309950B1 (en) * | 2015-06-15 | 2022-10-19 | Toshiba Mitsubishi-Electric Industrial Systems Corporation | Power conversion device |

| CN106329899B (zh) * | 2015-07-01 | 2018-10-16 | 南京南瑞继保电气有限公司 | 故障电流抑制阻尼器拓扑电路及其控制方法及换流器 |

| EP3324531B1 (en) * | 2015-07-14 | 2022-11-23 | Mitsubishi Electric Corporation | Power conversion device |

| EP3255773B1 (de) * | 2016-06-09 | 2021-01-13 | GE Energy Power Conversion Technology Ltd. | Verlustarmes doppel-submodul für einen modularen mehrpunktstromrichter und modularer mehrpunktstromrichter mit diesem |

| JP6798179B2 (ja) * | 2016-07-29 | 2020-12-09 | 富士電機株式会社 | 3レベルチョッパ装置 |

| US9923472B1 (en) * | 2016-09-07 | 2018-03-20 | Apple Inc. | Fixed frequency series-parallel mode (SPM) active clamp flyback converter |

| JP6702429B2 (ja) * | 2016-11-16 | 2020-06-03 | 富士電機株式会社 | 半導体試験回路、半導体試験装置および半導体試験方法 |

| JP6824379B2 (ja) * | 2017-02-27 | 2021-02-03 | 三菱電機株式会社 | 電力変換装置および直流送電システム |

| JP6440923B1 (ja) * | 2017-09-26 | 2018-12-19 | 三菱電機株式会社 | 電力変換装置 |

| KR20220024907A (ko) * | 2019-06-24 | 2022-03-03 | 제너럴 일렉트릭 캄파니 | 플라잉 커패시터 기반 벅 부스트 컨버터를 위한 단락 보호 시스템 및 방법 |

| EP3780366A1 (en) * | 2019-08-13 | 2021-02-17 | Vestas Wind Systems A/S | Dc chopper for mmc cell with integrated chopper resistor |

-

2019

- 2019-12-03 US US17/772,686 patent/US20220385209A1/en active Pending

- 2019-12-03 WO PCT/JP2019/047263 patent/WO2021111526A1/ja unknown

- 2019-12-03 JP JP2020512896A patent/JP6719692B1/ja active Active

- 2019-12-03 EP EP19955250.6A patent/EP4071996A4/en active Pending

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013121223A (ja) * | 2011-12-07 | 2013-06-17 | Hitachi Ltd | 電力変換装置 |

| WO2017168519A1 (ja) * | 2016-03-28 | 2017-10-05 | 三菱電機株式会社 | 電力変換装置 |

| JP2019022313A (ja) * | 2017-07-14 | 2019-02-07 | 株式会社東芝 | 電力変換装置 |

| JP6345379B1 (ja) * | 2017-08-09 | 2018-06-20 | 三菱電機株式会社 | 電力変換装置 |

| WO2019064705A1 (ja) * | 2017-09-26 | 2019-04-04 | 三菱電機株式会社 | 電力変換装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP4071996A4 (en) | 2022-11-23 |

| EP4071996A1 (en) | 2022-10-12 |

| JPWO2021111526A1 (ja) | 2021-12-02 |

| WO2021111526A1 (ja) | 2021-06-10 |

| US20220385209A1 (en) | 2022-12-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP2786479B1 (en) | Power converter | |

| JP6545425B1 (ja) | 電力変換装置 | |

| US10637371B2 (en) | Interface arrangement between an alternating current power system and a direct current power system with control of converter valve for fault protection | |

| JP6180693B1 (ja) | 電力変換装置 | |

| RU2652690C2 (ru) | Модульный многоточечный вентильный преобразователь для высоких напряжений | |

| US20200177097A1 (en) | Power Conversion Device | |

| JPWO2019003290A1 (ja) | 電力変換装置 | |

| US11139733B2 (en) | Modular multilevel converter sub-module having DC fault current blocking function and method of controlling the same | |

| JP6689472B1 (ja) | 電力変換装置 | |

| JP6833151B1 (ja) | 電力変換システム | |

| US20230170822A1 (en) | Power conversion device | |

| JP6847322B1 (ja) | 電力変換システム | |

| US12081138B2 (en) | Power conversion device | |

| WO2017080597A1 (en) | A modular multilevel converter for handling ac side faults | |

| US20230163694A1 (en) | Power conversion device | |

| JP6719692B1 (ja) | 電力変換装置 | |

| JP6765588B1 (ja) | 電力変換システム | |

| JP6910579B1 (ja) | 電力変換システムおよびその制御装置 | |

| JP7134306B2 (ja) | 電力変換システムおよびその制御装置 | |

| JP7442749B1 (ja) | 電力変換装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20200303 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20200303 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20200323 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20200519 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20200616 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6719692 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |