JP6234008B2 - 発振回路及び電子機器 - Google Patents

発振回路及び電子機器 Download PDFInfo

- Publication number

- JP6234008B2 JP6234008B2 JP2012074294A JP2012074294A JP6234008B2 JP 6234008 B2 JP6234008 B2 JP 6234008B2 JP 2012074294 A JP2012074294 A JP 2012074294A JP 2012074294 A JP2012074294 A JP 2012074294A JP 6234008 B2 JP6234008 B2 JP 6234008B2

- Authority

- JP

- Japan

- Prior art keywords

- power supply

- supply voltage

- circuit

- transistor

- supplied

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Oscillators With Electromechanical Resonators (AREA)

- Inductance-Capacitance Distribution Constants And Capacitance-Resistance Oscillators (AREA)

- Manipulation Of Pulses (AREA)

- Logic Circuits (AREA)

Description

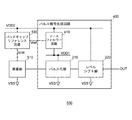

本形態においては、交流信号から所望の振幅レベルを有するパルス信号を生成する場合に、パルス化の機能とレベルシフト機能とに分け、パルス化は、第1の電源電圧の下で行い、レベルシフトは、パルス化の際の電源電圧より高い電源電圧の下で行う。従って、本形態によれば、パルス化をレベルシフト部の電圧よりも低い電圧で行うため、ユーザーが要求する電源電圧が高い場合でも、より低い電源電圧の下で消費電流が小さくなるようにパルス化を実現した後、レベルシフト機能により、ユーザーが要求する電源電圧まで振幅レベルを上げたパルス信号を生成することができる。従って、広い電圧範囲での動作が要求される場合、低消費電力化とパルス整形の安定性や低い位相雑音とを両立することができるようになる。

本発明の第2の形態に係るパルス信号生成回路では、第1の形態において、前記パルス化部は、前記交流信号の入力ノードに接続される一方の電極と、他方の電極とを有する前記容量と、前記要領の前記他方の電極に接続される入力端子と、前記第1のパルス信号を出力する出力端子と、を有するインバーター回路と、前記インバーター回路の前記入力端子と前記出力端子との間に接続される帰還抵抗とを含む。

本形態によれば、パルス化部を容量結合インバーター回路により構成するようにしたので、第1の電源電圧の中間電圧にバイアスされた直流レベルに交流信号が重畳するため、ディーティー比が50パーセントのパルス信号を生成しやすくなる。そのため、低消費電力で、ユーザーが要求する振幅レベルでデューティー比が50パーセントの出力信号を出力することに加えて、パルス整形の安定性や低い位相雑音を実現することができるようになる。

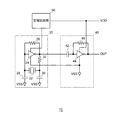

本発明の第3の形態に係るパルス信号生成回路では、第1の形態又は第2の形態において、前記レベルシフト部は、ソースに第3の電源電圧が供給され、ゲートに前記第1のパルス信号が供給されるN型の第1のトランジスターと、ソースに前記第2の電源電圧が供給され、ドレインに前記第1のトランジスターのドレインが接続されるP型の第2のトランジスターと、ソースに前記第3の電源電圧が供給され、ゲートに前記第1のパルス信号の反転信号が供給され、ドレインに前記第2のトランジスターのゲートが接続されるN型の第3のトランジスターと、ソースに前記第2の電源電圧が供給され、ドレインに前記第3のトランジスターのドレインが接続され、ゲートに前記第2のトランジスターのドレインが接続されるP型の第4のトランジスターと、を含み、前記第4のトランジスターのドレインから前記第2のパルス信号を出力する。

本形態によれば、レベルシフト部を、たすきがけ接続したインバーター回路により構成したので、電源電圧によらず貫通電流が大きく変化しない。このため、パルス化部におけるデューティー良好性を生かしながら、低消費電流化とパルス整形の安定性と低位相雑音特性を満足することができるようになる。

本発明の第4の形態に係るパルス信号生成回路は、第1の形態乃至第3の形態のいずれかにおいて、ソースから前記第1の電源電圧を出力するN型トランジスターを有するソースフォロワー回路を含む。

本形態によれば、ソースフォロワー回路により第1の電源電圧を供給するようにしたので、上記の効果に加えて、複数の電源電圧を供給するための不要な回路を省略することができるようになる。

本発明の第5の形態に係るパルス信号生成回路は、第4の形態において、前記N型トランジスターのドレインに前記第2の電源電圧が供給され、前記N型トランジスターのゲートに前記第2の電源電圧に基づく電圧が供給される。

本形態によれば、ソースフォロワー回路により、第2の電源電圧に基づいて第1の電源電圧を生成するようにしたので、上記の効果に加えて、複数の電源電圧を供給するための演算増幅器等の不要な回路を省略することができ、構成を簡素化することができる。

本発明の第6の形態は、発振回路が、第1の形態乃至第5の形態のいずれかのパルス信号生成回路と、共振子を駆動して前記第1のパルス信号を出力する共振子駆動回路と、を含む。

本形態によれば、パルス化部におけるデューティー良好性を生かしながら、低消費電流化とパルス整形の安定性と低位相雑音特性を満足する発振回路を提供することができるようになる。

本発明の第7の形態は、発振回路が、第4の形態のパルス信号生成回路と、共振子を駆動して前記第1のパルス信号を出力する共振子駆動回路と、前記共振子駆動回路にPTAT(Proportional To Absolute Temperature)電流を出力するとともに、前記N型トランジスターのゲートに電圧を出力するバンドギャップリファレンス回路と、を含む。

本形態によれば、パルス化部におけるデューティー良好性を生かしながら、低消費電流化とパルス整形の安定性と低位相雑音特性を満足する発振回路を提供することができるようになる。更に、本形態によれば、電流駆動を行う素子の温度特性を補償することができるようになる。

本発明の第8の形態は、電子機器が、第6の形態又は第7の形態に記載の発振回路を含む。

本形態によれば、パルス化部におけるデューティー良好性を生かしながら、低消費電流化とパルス整形の安定性と低位相雑音特性を満足する発振回路が適用された電子機器を提供することができる。

本発明の第9の形態は、パルス信号生成方法が、共振子を駆動して発振信号を生成する発振信号生成ステップと、第1の電源電圧の下で、容量を介して入力される前記発振信号から第1の振幅レベルを有する第1のパルス信号を生成するパルス化ステップと、前記第1の電源電圧より高い第2の電源電圧の下で、前記第1のパルス信号を第2の振幅レベルを有する第2のパルス信号に変換するレベルシフトステップとを含む。

本形態においては、交流信号から所望の振幅レベルを有するパルス信号を生成する場合に、パルス化の機能とレベルシフト機能とに分け、パルス化は、第1の電源電圧の下で行い、レベルシフトは、パルス化の際の電源電圧より高い電源電圧の下で行う。従って、本形態によれば、パルス化をレベルシフト部の電圧よりも低い電圧で行うため、ユーザーが要求する電源電圧が高い場合でも、より低い電源電圧の下で消費電流が小さくなるようにパルス化を実現した後、レベルシフト機能により、ユーザーが要求する電源電圧まで振幅レベルを上げたパルス信号を生成することができる。従って、広い電圧範囲での動作が要求される場合、低消費電力化とパルス整形の安定性や低い位相雑音とを両立することができるようになる。

本発明の第10の形態に係るパルス信号生成方法では、第9の形態において、前記発振信号生成ステップは、バンドギャップリファレンス回路から出力されるPTAT電流を用いた電流駆動により前記発振信号を生成し、前記パルス化ステップは、前記バンドギャップリファレンス回路により生成された電圧がゲートに供給されるN型トランジスターのソース電圧を前記第1の電源電圧として、前記第1のパルス信号を生成する。

本形態によれば、上記の効果に加えて、構成を簡素化し、電流駆動を行う素子の温度特性を補償することができるようになる。

(1)本発明の第1の態様は、パルス信号生成回路が、定電圧である第1の電源電圧が供給され、容量を介して入力される交流信号から第1の振幅レベルを有する第1のパルス信号を生成するパルス化部と、前記第1の電源電圧より高い第2の電源電圧が供給され、前記第1のパルス信号を第2の振幅レベルを有する第2のパルス信号に変換するレベルシフト部とを含む。

図1に、本発明の第1の実施形態における発振回路の構成例のブロック図を示す。

第1の実施形態では、第1の電源電圧VDD1及び第2の電源電圧VDD2を図示しない電圧発生回路から供給することができるが、第1の電源電圧VDD1を、第2の電源電圧VDD2に基づいて生成するようにしてもよい。

第1の実施形態又は第2の実施形態では、発振部において電圧駆動によって発振信号を生成する発振回路を例に説明したが、本発明に係る実施形態は、これに限定されるものではない。

第3の実施形態では、バンドギャップリファレンス回路530として図8に示す構成を例に説明したが、本発明に係る実施形態は、これに限定されるものではない。

図10に、上記のいずれかの実施形態又はその変形例における発振回路が適用された電子機器として携帯型情報端末の構成例のブロック図を示す。なお、図10において、図1と同様の部分には同一符号を付し、適宜説明を省略する。また、図10では、第1の実施形態における発振回路100が携帯型情報端末に適用される例を示したが、第2の実施形態、第3の実施形態、又はその変形例における発振回路を適用してもよい。

112,512…水晶振動子(共振子)、 114,230…インバーター回路、

116,218,516…帰還抵抗、

118,120,212,518,520…容量、 122,522…ドレイン抵抗、

200,400…パルス信号生成回路、 210…パルス化部、

214,222,224…P型のMOSトランジスター、

216,226,228,412…N型のMOSトランジスター、

220…レベルシフト部、 310…定電圧回路、 410…ソースフォロワー回路、

530…バンドギャップリファレンス回路、 600…携帯型情報端末(電子機器)、

610…制御部、 620…記憶部、 630…通信回路、 640…操作部、

650…表示部、 Iptat…PTAT電流、 OUT…出力端子、

VDD1…第1の電源電圧、 VDD2…第2の電源電圧、 Vref…定電圧、

VSS…接地電圧(第3の電源電圧)

Claims (5)

- 共振子を駆動して交流信号を出力する共振子駆動回路と、

第1の電源電圧が供給され、容量を介して入力される前記交流信号から第1の増幅器を介して第1の振幅レベルを有する第1のパルス信号を生成するパルス化部と、

前記第1の電源電圧より高い第2の電源電圧が供給され、前記第1のパルス信号が入力されて第2の振幅レベルを有する第2のパルス信号を出力するレベルシフト部と、

ソースから前記第1の電源電圧を出力するN型トランジスターを有するソースフォロワー回路と、

前記共振子駆動回路にPTAT(Proportional To Absolute Temperature)電流を出力するとともに、前記N型トランジスターのゲートに電圧を出力するバンドギャップリファレンス回路と、を含み、

前記第1の増幅器の増幅率が前記レベルシフト部の増幅率よりも大きいことを特徴とする発振回路。 - 前記パルス化部は、

前記交流信号の入力ノードに接続される一方の電極と、他方の電極とを有する前記容量と、

前記容量の前記他方の電極に接続される入力端子と、前記第1のパルス信号を出力する出力端子と、を有するインバーター回路と、

前記インバーター回路の前記入力端子と前記出力端子との間に接続される帰還抵抗と、を含むことを特徴とする請求項1に記載の発振回路。 - 前記レベルシフト部は、

ソースに第3の電源電圧が供給され、ゲートに前記第1のパルス信号が供給されるN型の第1のトランジスターと、

ソースに前記第2の電源電圧が供給され、ドレインに前記第1のトランジスターのドレインが接続されるP型の第2のトランジスターと、

ソースに前記第3の電源電圧が供給され、ゲートに前記第1のパルス信号の反転信号が供給され、ドレインに前記第2のトランジスターのゲートが接続されるN型の第3のトランジスターと、

ソースに前記第2の電源電圧が供給され、ドレインに前記第3のトランジスターのドレインが接続され、ゲートに前記第2のトランジスターのドレインが接続されるP型の第4のトランジスターと、を含み、

前記第4のトランジスターのドレインから前記第2のパルス信号を出力することを特徴とする請求項1又は2に記載の発振回路。 - 前記N型トランジスターのドレインに前記第2の電源電圧が供給され、前記N型トランジスターのゲートに前記第2の電源電圧に基づく電圧が供給されることを特徴とする請求項1乃至3のいずれか一項に記載の発振回路。

- 請求項1乃至4のいずれか一項に記載の発振回路を含む電子機器。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012074294A JP6234008B2 (ja) | 2012-03-28 | 2012-03-28 | 発振回路及び電子機器 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012074294A JP6234008B2 (ja) | 2012-03-28 | 2012-03-28 | 発振回路及び電子機器 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2013207537A JP2013207537A (ja) | 2013-10-07 |

| JP2013207537A5 JP2013207537A5 (ja) | 2015-05-07 |

| JP6234008B2 true JP6234008B2 (ja) | 2017-11-22 |

Family

ID=49526226

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012074294A Active JP6234008B2 (ja) | 2012-03-28 | 2012-03-28 | 発振回路及び電子機器 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6234008B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11789482B2 (en) | 2021-03-26 | 2023-10-17 | Samsung Electronics Co., Ltd. | Bandgap reference circuit including resistivity temperature coefficient cancellation circuit, and oscillator circuit including the bandgap reference circuit |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2016144128A (ja) * | 2015-02-04 | 2016-08-08 | セイコーエプソン株式会社 | 発振器、電子機器及び移動体 |

| JP6870403B2 (ja) * | 2017-03-16 | 2021-05-12 | セイコーエプソン株式会社 | 発振回路、回路装置、発振器、電子機器及び移動体 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS549544A (en) * | 1977-06-24 | 1979-01-24 | Citizen Watch Co Ltd | Mutual complement type insulation gate type electric field effect transistor circuit |

| US5705946A (en) * | 1995-06-07 | 1998-01-06 | Sgs-Thomson Microelectronics, Inc. | Low power low voltage level shifter |

| JP4259485B2 (ja) * | 2005-04-28 | 2009-04-30 | エプソントヨコム株式会社 | 圧電発振回路 |

| JP2008160510A (ja) * | 2006-12-25 | 2008-07-10 | Epson Toyocom Corp | 2出力型水晶発振器 |

| JP5325591B2 (ja) * | 2009-01-28 | 2013-10-23 | ラピスセミコンダクタ株式会社 | 発振回路 |

| US8044740B2 (en) * | 2009-09-03 | 2011-10-25 | S3C, Inc. | Temperature compensated RC oscillator for signal conditioning ASIC using source bulk voltage of MOSFET |

-

2012

- 2012-03-28 JP JP2012074294A patent/JP6234008B2/ja active Active

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11789482B2 (en) | 2021-03-26 | 2023-10-17 | Samsung Electronics Co., Ltd. | Bandgap reference circuit including resistivity temperature coefficient cancellation circuit, and oscillator circuit including the bandgap reference circuit |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2013207537A (ja) | 2013-10-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5475598B2 (ja) | 基準電流発生回路 | |

| TWI392219B (zh) | 用於改善環形振盪器頻率變動的低雜訊基準電壓產生電路 | |

| JP4684616B2 (ja) | 発振回路 | |

| JP6234008B2 (ja) | 発振回路及び電子機器 | |

| JPH11150471A (ja) | 差動増幅回路 | |

| KR101911367B1 (ko) | 기준 전류 생성 회로, 기준 전압 생성 회로, 및 온도 검출 회로 | |

| CN115223473A (zh) | 输出缓冲器以及具有输出缓冲器的数据驱动器 | |

| US8890497B2 (en) | Electronic device and method for a limiter in an AC application | |

| US7847645B2 (en) | Oscillation control apparatus and oscillator | |

| JP2003283306A (ja) | 発振器 | |

| CN103412611B (zh) | 一种高精度基准电压源 | |

| JP6045148B2 (ja) | 基準電流発生回路および基準電圧発生回路 | |

| JP5035017B2 (ja) | 発振回路 | |

| US7515001B2 (en) | AC amplifier and piezoelectric vibrator oscillator | |

| JP5801333B2 (ja) | 電源回路 | |

| CN112394830B (zh) | 触摸模拟前端电路及其触摸显示设备 | |

| JP2018186457A (ja) | 増幅回路および光モジュール | |

| JP2013207339A (ja) | レベルシフト回路、発振回路、及び電子機器 | |

| US7876082B2 (en) | DC/DC converter and slope compensation circuit thereof | |

| JPH0720960A (ja) | 電流発生装置 | |

| JP6611007B2 (ja) | レベルシフト回路 | |

| WO2021215457A1 (ja) | 交流増幅器 | |

| CN112825003B (zh) | 放大装置以及电压电流转换装置 | |

| JP2010287997A (ja) | 増幅器および発振器 | |

| JP4729982B2 (ja) | 演算増幅器、駆動回路及び電気光学装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20150107 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150319 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150319 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20160112 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160126 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160322 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20160609 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20160617 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20160906 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161109 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20161116 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20170127 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20171024 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6234008 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |