JP6029704B2 - 半導体装置およびその製造方法 - Google Patents

半導体装置およびその製造方法 Download PDFInfo

- Publication number

- JP6029704B2 JP6029704B2 JP2015068517A JP2015068517A JP6029704B2 JP 6029704 B2 JP6029704 B2 JP 6029704B2 JP 2015068517 A JP2015068517 A JP 2015068517A JP 2015068517 A JP2015068517 A JP 2015068517A JP 6029704 B2 JP6029704 B2 JP 6029704B2

- Authority

- JP

- Japan

- Prior art keywords

- insulating film

- region

- semiconductor layer

- groove

- semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Element Separation (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

Description

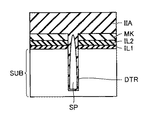

MOSトランジスタと第1の分離を含む素子形成領域を平面視において取り囲み、第3の半導体層および第2の半導体層を貫いて第1の半導体層の内部にまで達する第2の溝が形成される。ゲート電極の上を覆い、第2の溝の内部を埋め込む第2の絶縁膜が形成される。第2の溝内には中空が形成される。

(実施の形態1)

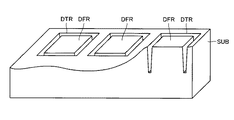

図1を参照して、BiC−DMOS(Bipolar Complementary Double-diffused Metal Oxide Semiconductor)の半導体チップCHは、たとえば低耐圧のCMOS(Complementary MOS)トランジスタを集積したようなロジック部LGと、高耐圧素子を用いた出力ドライバ部HVとを有している。上記のロジック部LGではその形成領域がDTI構造によって平面視において取り囲まれている。また出力ドライバ部HVでは素子の1つ1つの形成領域がDTI構造によって平面視において取り囲まれている。

次に、DTI構造における溝DTR内に中空がある場合とない場合との特性(リーク電流、ブレークダウン電圧、ブレークダウン時の電界強度分布)の違いについて調べた結果を説明する。

図13を参照して、このサンプルでは、半導体基板SUBのp型領域PR上に、p-エピタキシャル領域EP1、n型埋め込み領域NBRおよびp-エピタキシャル領域EP2が順に積層して形成されている。半導体基板SUBには、その表面からp-エピタキシャル領域EP2、n型埋め込み領域NBRおよびp-エピタキシャル領域EP1を貫通してp型領域PRに達する溝DTRが形成されている。この溝DTR内には絶縁膜IIが形成されている。p-エピタキシャル領域EP2の溝DTRを挟んだ一方側には導電層CL1が電気的に接続されており、溝DTRを挟んだ他方側には導電層CL2が電気的に接続されている。

本実施の形態によれば、図4〜図7に示すように高耐圧横型MOSトランジスタなどの素子が完成した後にDTI構造の溝DTRが形成されるため、その溝DTRを層間絶縁膜IIで埋め込むことが可能となる。これにより、溝DTRを埋め込む絶縁膜を層間絶縁膜とは別途に形成する必要がなくなるため、製造方法における工程数を大幅に削減することができる。

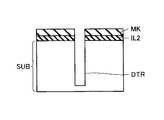

実施の形態1においては、製造工程においてSTI構造が形成された領域にDTI構造を形成する場合について説明したが、STI構造が形成されていない領域にDTI構造が形成されてもよい。STI構造が形成されていない領域にDTI構造を形成する場合を実施の形態2として以下に説明する。

実施の形態2においては、製造工程においてマスク材MKを等方性エッチングにより削除する場合について説明したが、マスク材MKは削除されずに残されてもよい。マスク材MKを残す場合を実施の形態3として以下に説明する。

実施の形態2においては、製造工程において絶縁膜IL1と絶縁膜IL2とマスク材MKとを積層した場合について説明したが、絶縁膜IL1は省略されてもよい。絶縁膜IL1を省略する場合を実施の形態4として以下に説明する。

実施の形態3においては、製造工程において絶縁膜IL1と絶縁膜IL2とマスク材MKとを積層した場合について説明したが、絶縁膜IL1と絶縁膜IL2とは省略されてもよい。絶縁膜IL1と絶縁膜IL2とを省略する場合を実施の形態5として以下に説明する。

図28に示すように、DTI構造により取り囲まれた素子形成領域DFR(図においてはpMOSトランジスタ形成領域)同士は、所定の領域SRを挟んで隣り合うように配置されていてもよい。この場合、所定の領域SRにおける半導体基板SUBの表面にはSTI構造が形成されていてもよい。このSTI構造は上述したように、半導体基板SUBの表面に形成された溝STRと、その溝STR内を埋め込む絶縁膜BILとを有している。

Claims (10)

- 第1導電型の第1の半導体層と、前記第1の半導体層上に形成され、前記第1導電型と逆導電型の第2導電型の第2の半導体層と、前記第2の半導体層上に形成された、前記第1導電型の第3の半導体層と、を有する半導体基板と、

前記第3の半導体層の主表面上にゲート絶縁膜を介して設けられたゲート電極と、前記第3の半導体層の前記主表面に前記ゲート電極を挟んで形成されたソース領域とドレイン領域とを有するMOSトランジスタと、

前記MOSトランジスタの前記ソース領域または前記ドレイン領域の側面と接し、前記ソース領域または前記ドレイン領域より深い第1の溝内に第1の絶縁膜が埋め込まれてなる第1の分離と、

複数の前記MOSトランジスタと前記第1の分離を含む素子形成領域と、

前記素子形成領域を取り囲む第2の溝からなる第2の分離と、

前記ゲート電極の上を覆い、前記第2の溝内を埋め込む第2の絶縁膜と、

を備え、

前記第2の溝は前記第1の溝より深く、

前記第2の分離は前記第2の半導体層を貫いて前記第1の半導体層にまで達し、

前記第2の分離には中空が形成されている、半導体装置。 - 前記第2の分離の前記中空は、前記中空の底が前記第1の半導体層の内部まで達する、請求項1記載の半導体装置。

- 前記第2の絶縁膜上に形成された配線層と、

前記第2の絶縁膜内に形成された導電層と、

をさらに備え、

前記配線層は、前記導電層により、前記MOSトランジスタの前記ソース領域または前記ドレイン領域に接続される、請求項1記載の半導体装置。 - 前記ゲート電極を覆い、前記第2の絶縁膜の下に形成された第3の絶縁膜をさらに備え、

前記第2の絶縁膜はTEOS膜であり、前記第3の絶縁膜はシリコン窒化膜である、請求項3記載の半導体装置。 - 前記第2の分離は、前記第1の分離を貫いて形成される、請求項1記載の半導体装置。

- (a)第1導電型の第1の半導体層と、

前記第1の半導体層上に形成され、前記第1導電型と逆導電型の第2導電型の第2の半導体層と、

前記第2の半導体層上に形成された、前記第1導電型の第3の半導体層と、

前記第3の半導体層の主表面にゲート絶縁膜を介して設けられたゲート電極と、前記第3の半導体層の前記主表面に前記ゲート電極を挟んで形成されたソース領域およびドレイン領域とを有するMOSトランジスタと、

前記ソース領域または前記ドレイン領域の側面と接し、前記第3の半導体層の前記主表面に形成された、前記ソース領域または前記ドレイン領域より深い第1の溝内を第1の絶縁膜で埋め込んだ第1の分離と、

を有する半導体基板を準備する工程と、

(b)前記(a)工程の後に前記MOSトランジスタと前記第1の分離を含む素子形成領域を平面視において取り囲み、前記第3の半導体層および前記第2の半導体層を貫いて前記第1の半導体層の内部にまで達する第2の溝を形成する工程と、

(c)前記ゲート電極の上を覆い、前記第2の溝の内部を埋め込む第2の絶縁膜を形成する工程と、

を備え、

前記第2の溝内には中空が形成される、半導体装置の製造方法。 - 前記(c)工程の後に、

(d)前記第2の絶縁膜を貫いて、前記MOSトランジスタの前記ソース領域または前記ドレイン領域に到達する導電層を形成する工程と、

(e)前記第2の絶縁膜上に前記導電層に接続する配線層を形成する工程と、

をさらに備えた、請求項6記載の半導体装置の製造方法。 - 前記中空の底は、前記第1の半導体層の内部にまで達する、請求項6記載の半導体装置の製造方法。

- 前記(b)工程は、

(b−1)前記MOSトランジスタを覆うマスク材を形成する工程と、

(b−2)前記マスク材上に、前記第2の溝に対応する第1開口を有するレジストパターンを形成する工程と、

(b−3)前記半導体基板に異方性エッチングを施し、前記マスク材、前記第1の絶縁膜、および、前記半導体基板に前記第2の溝を形成する工程と、

を有する、請求項6記載の半導体装置の製造方法。 - 前記(b−3)工程において、前記半導体基板に前記第2の溝を形成する前記異方性エッチングの際に、前記マスク材はマスクとして機能する、請求項9記載の半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015068517A JP6029704B2 (ja) | 2015-03-30 | 2015-03-30 | 半導体装置およびその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015068517A JP6029704B2 (ja) | 2015-03-30 | 2015-03-30 | 半導体装置およびその製造方法 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009213345A Division JP5729745B2 (ja) | 2009-09-15 | 2009-09-15 | 半導体装置およびその製造方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016201649A Division JP2017011311A (ja) | 2016-10-13 | 2016-10-13 | 半導体装置およびその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015122543A JP2015122543A (ja) | 2015-07-02 |

| JP2015122543A5 JP2015122543A5 (ja) | 2015-10-15 |

| JP6029704B2 true JP6029704B2 (ja) | 2016-11-24 |

Family

ID=53533849

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015068517A Active JP6029704B2 (ja) | 2015-03-30 | 2015-03-30 | 半導体装置およびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6029704B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7385431B2 (ja) | 2019-10-31 | 2023-11-22 | 株式会社ダイヘン | 被膜剥離装置及び巻線装置 |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6653769B2 (ja) | 2016-12-14 | 2020-02-26 | 日立オートモティブシステムズ株式会社 | 負荷駆動装置 |

| WO2022153693A1 (ja) | 2021-01-15 | 2022-07-21 | ローム株式会社 | 半導体装置 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3382063B2 (ja) * | 1995-06-14 | 2003-03-04 | 株式会社東芝 | 半導体装置の製造方法 |

| JP2002184854A (ja) * | 2000-12-12 | 2002-06-28 | Sony Corp | 半導体装置の製造方法 |

| JP2002280447A (ja) * | 2001-03-21 | 2002-09-27 | Sony Corp | 半導体装置の製造方法 |

| JP2003152071A (ja) * | 2001-11-13 | 2003-05-23 | Sony Corp | 素子形成領域の形成方法、半導体装置の製造方法、及び半導体装置 |

| US7825488B2 (en) * | 2006-05-31 | 2010-11-02 | Advanced Analogic Technologies, Inc. | Isolation structures for integrated circuits and modular methods of forming the same |

| JP2005332959A (ja) * | 2004-05-19 | 2005-12-02 | Nippon Precision Circuits Inc | 相補型バイポーラ半導体装置及びその製造方法 |

| JP2006049828A (ja) * | 2004-07-05 | 2006-02-16 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| JP2009032967A (ja) * | 2007-07-27 | 2009-02-12 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP2009164460A (ja) * | 2008-01-09 | 2009-07-23 | Renesas Technology Corp | 半導体装置 |

-

2015

- 2015-03-30 JP JP2015068517A patent/JP6029704B2/ja active Active

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7385431B2 (ja) | 2019-10-31 | 2023-11-22 | 株式会社ダイヘン | 被膜剥離装置及び巻線装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2015122543A (ja) | 2015-07-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5729745B2 (ja) | 半導体装置およびその製造方法 | |

| TWI548086B (zh) | 溝渠式橫向擴散金屬氧化半導體元件及其製造方法 | |

| CN108565261B (zh) | 半导体器件及其制造方法 | |

| US20080290411A1 (en) | Semiconductor device and method for fabricating the same | |

| US20120280291A1 (en) | Semiconductor device including gate openings | |

| TW201735264A (zh) | 作為高壓器件之閘極介電質之凹陷淺溝渠隔離 | |

| US20090273030A1 (en) | Semiconductor Device with a Trench Isolation and Method of Manufacturing Trenches in a Semiconductor Body | |

| JP6200818B2 (ja) | 半導体装置の製造方法 | |

| KR20080104774A (ko) | 반도체 소자의 고전압 드리프트 형성 방법 | |

| JP6559499B2 (ja) | 半導体装置の製造方法 | |

| KR20180111534A (ko) | 반도체 장치 및 그 제조 방법 | |

| TWI593112B (zh) | 具有矽局部氧化之絕緣體上矽的積體電路及其製造方法 | |

| JP6029704B2 (ja) | 半導体装置およびその製造方法 | |

| JP2017011311A (ja) | 半導体装置およびその製造方法 | |

| KR20130017911A (ko) | 반도체 소자 | |

| KR100853799B1 (ko) | 트렌치 게이트 반도체 소자 및 그의 제조 방법 | |

| JP5390760B2 (ja) | 半導体装置の製造方法および半導体装置 | |

| JP4887662B2 (ja) | 半導体装置およびその製造方法 | |

| JP2009176953A (ja) | 半導体装置 | |

| JP6797771B2 (ja) | 半導体装置 | |

| JP2022059519A (ja) | 半導体集積回路 | |

| JP2023027863A (ja) | 半導体装置およびその製造方法 | |

| JP5071652B2 (ja) | 半導体装置 | |

| JP2011029214A (ja) | 半導体装置の製造方法及び半導体装置 | |

| JP2009049315A (ja) | 半導体装置および半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150330 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150901 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20151208 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160209 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160411 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20160920 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20161018 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6029704 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |