JP5442634B2 - 読出ステータスのコントローラ - Google Patents

読出ステータスのコントローラ Download PDFInfo

- Publication number

- JP5442634B2 JP5442634B2 JP2010538800A JP2010538800A JP5442634B2 JP 5442634 B2 JP5442634 B2 JP 5442634B2 JP 2010538800 A JP2010538800 A JP 2010538800A JP 2010538800 A JP2010538800 A JP 2010538800A JP 5442634 B2 JP5442634 B2 JP 5442634B2

- Authority

- JP

- Japan

- Prior art keywords

- memory device

- response

- read

- host processor

- status

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000004044 response Effects 0.000 claims description 72

- 230000015654 memory Effects 0.000 claims description 43

- 238000000034 method Methods 0.000 claims description 15

- 238000012545 processing Methods 0.000 claims description 9

- 238000001514 detection method Methods 0.000 claims description 3

- 238000012544 monitoring process Methods 0.000 claims 2

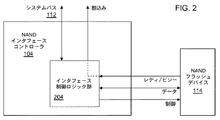

- 238000010586 diagram Methods 0.000 description 8

- 238000012546 transfer Methods 0.000 description 5

- 238000012790 confirmation Methods 0.000 description 4

- 230000008901 benefit Effects 0.000 description 3

- 230000002093 peripheral effect Effects 0.000 description 3

- 230000015556 catabolic process Effects 0.000 description 2

- 238000006731 degradation reaction Methods 0.000 description 2

- 108010076504 Protein Sorting Signals Proteins 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 238000011835 investigation Methods 0.000 description 1

- 239000003550 marker Substances 0.000 description 1

- 238000004377 microelectronic Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 230000008439 repair process Effects 0.000 description 1

- 238000010561 standard procedure Methods 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- 230000001960 triggered effect Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/20—Handling requests for interconnection or transfer for access to input/output bus

- G06F13/24—Handling requests for interconnection or transfer for access to input/output bus using interrupt

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Debugging And Monitoring (AREA)

- Bus Control (AREA)

Description

Claims (15)

- ホストプロセッサを含む処理システムにおけるメモリデバイスのためのコントローラであって、前記ホストプロセッサと前記コントローラとはシステムバスにより接続され、前記コントローラは前記メモリデバイスと通信するものであり、

前記ホストプロセッサにより前記メモリデバイスに送信される少なくとも1つのプログラム可能なビットシーケンスを検出するよう構成されたロジック部と、

前記検出されたビットシーケンスに基づいて、前記メモリデバイスに命令を発行するよう構成されたロジック部と、

前記発行された命令に基づく前記メモリデバイスにおける動作の実行を検出するために前記メモリデバイスからのビジー信号のステータスを監視するよう構成されたロジック部と、

前記ビジー信号がディアサートされたことが検出されたとき、前記ホストプロセッサからの指示なしに前記メモリデバイスに対して自動的にステータス読出し命令を発行するよう構成されたロジック部と、

前記発行されたステータス読出し命令に対して前記メモリデバイスから応答を読出すよう構成されたロジック部と、

前記メモリデバイスから前記読出された応答に基づいて、前記ホストプロセッサに割込み要求を送信するよう構成されたロジック部とを有し、

前記割込み要求は読出しステータスエラーが発生したときに、前記ホストプロセッサに送信されることを特徴とするコントローラ。 - 前記メモリデバイスに送信される前記プログラム可能なビットシーケンスは、前記メモリデバイスからの応答が読出される必要があるかどうかを示すことを特徴とする請求項1に記載のコントローラ。

- 前記メモリデバイスからの応答と格納された応答とを比較することにより、読出しステータスエラーが発生したことが判断されることを特徴とする請求項1に記載のコントローラ。

- 前記メモリデバイスからの特定の応答に対応する、前記ホストプロセッサにより送信されるアドレスとデータとを追跡するように構成されたロジック部と、

前記少なくとも1つのプログラム可能なビットシーケンスを格納する少なくとも1つのレジスタと、

の内の少なくとも1つをさらに有することを特徴とする請求項1に記載のコントローラ。 - 前記割込み要求を送信するよう構成されたロジック部は、前記メモリデバイスにおけるステータスレジスタの状態についてマスクを用いてチェックを行うように構成されていることを特徴とする請求項1に記載のコントローラ。

- ホストプロセッサとメモリコントローラとを含む処理システムにおけるメモリデバイスを制御する方法であって、

前記ホストプロセッサにより送信される少なくとも1つのプログラム可能なビットシーケンスの検出に基づいて、前記メモリデバイスに命令を送信する工程と、

前記命令に基づく前記メモリデバイスにおける動作の実行を検出するために前記メモリデバイスからのビジー信号のステータスを前記メモリコントローラにより監視する工程と、

前記ビジー信号がディアサートされたことが検出されたとき、前記ホストプロセッサからの指示なしに前記メモリコントローラにより前記メモリデバイスに対して自動的にステータス読出し命令を発行する工程と、

前記メモリコントローラにより、前記メモリデバイスによる前記ステータス読出し命令に対する応答を読出す工程と、

前記読出した応答が読出しステータスエラーを示すなら、前記メモリコントローラにより、前記ホストプロセッサに割込み要求を送信する工程とを有することを特徴とする方法。 - 前記メモリデバイスに送信される前記プログラム可能なビットシーケンスは、前記メモリデバイスからの応答が読出される必要があるかどうかを示すことを特徴とする請求項6に記載の方法。

- 前記割込み要求を送信する工程は、前記メモリデバイスからの応答と格納された応答とを比較することにより、前記読出した応答が読出しステータスエラーを示すと判断する工程を含むことを特徴とする請求項6に記載の方法。

- 前記メモリデバイスによる特定の応答に対応する、前記ホストプロセッサにより送信されるアドレスとデータとを追跡する工程と、

前記メモリコントローラに少なくとも1つの期待される応答を格納する工程と、

の内の少なくとも1つをさらに有することを特徴とする請求項6に記載の方法。 - 前記割込み要求を送信する工程は、前記メモリデバイスにおけるステータスレジスタの状態についてマスクを用いてチェックを行う工程を含むことを特徴とする請求項6に記載の方法。

- コンピュータにより実行されるときに、ホストプロセッサとメモリコントローラとを含む処理システムにおけるメモリデバイスを制御する方法を前記コンピュータに実行させるようにする命令を格納したコンピュータ可読媒体であって、前記方法は、

前記ホストプロセッサにより送信される少なくとも1つのプログラム可能なビットシーケンスの検出に基づいて、前記メモリデバイスに命令を送信する工程と、

前記命令に基づく前記メモリデバイスにおける動作の実行を検出するために前記メモリデバイスからのビジー信号のステータスを前記メモリコントローラにより監視する工程と、

前記ビジー信号がディアサートされたことが検出されたとき、前記ホストプロセッサからの指示なしに前記メモリコントローラにより前記メモリデバイスに対して自動的にステータス読出し命令を発行する工程と、

前記メモリコントローラにより、前記メモリデバイスによる前記ステータス読出し命令に対する応答を読出す工程と、

前記読出した応答が読出しステータスエラーを示すなら、前記メモリコントローラにより、前記ホストプロセッサに割込み要求を送信する工程とを有することを特徴とするコンピュータ可読媒体。 - 前記メモリデバイスに送信される前記命令は、前記メモリデバイスからの応答が読出される必要があるかどうかを示すことを特徴とする請求項11に記載のコンピュータ可読媒体。

- 前記割込み要求を送信する工程は、前記メモリデバイスからの応答と格納された応答とを比較することにより、前記読出した応答が読出しステータスエラーを示すと判断する工程を含むことを特徴とする請求項11に記載のコンピュータ可読媒体。

- 前記方法はさらに、

前記メモリデバイスによる特定の応答に対応する、前記ホストプロセッサにより送信されるアドレスとデータとを追跡する工程と、

前記メモリコントローラに少なくとも1つの期待される応答を格納する工程と、

の内の少なくとも1つを有することを特徴とする請求項11に記載のコンピュータ可読媒体。 - 前記割込み要求を送信する工程は、前記メモリデバイスにおけるステータスレジスタの状態についてマスクを用いてチェックを行う工程を含むことを特徴とする請求項11に記載のコンピュータ可読媒体。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/963,984 US7966445B2 (en) | 2007-12-24 | 2007-12-24 | Read status controller |

| US11/963,984 | 2007-12-24 | ||

| PCT/EP2008/068248 WO2009080826A1 (en) | 2007-12-24 | 2008-12-23 | Read status controller |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011508296A JP2011508296A (ja) | 2011-03-10 |

| JP2011508296A5 JP2011508296A5 (ja) | 2012-02-02 |

| JP5442634B2 true JP5442634B2 (ja) | 2014-03-12 |

Family

ID=40510565

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010538800A Expired - Fee Related JP5442634B2 (ja) | 2007-12-24 | 2008-12-23 | 読出ステータスのコントローラ |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7966445B2 (ja) |

| EP (1) | EP2225652B1 (ja) |

| JP (1) | JP5442634B2 (ja) |

| WO (1) | WO2009080826A1 (ja) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013041402A (ja) * | 2011-08-15 | 2013-02-28 | Fujitsu Semiconductor Ltd | 半導体集積回路及び回路状態監視回路 |

| JP2013041534A (ja) * | 2011-08-19 | 2013-02-28 | Fujitsu Semiconductor Ltd | 半導体集積回路および割り込み生成方法 |

| WO2015059889A1 (ja) * | 2013-10-25 | 2015-04-30 | パナソニックIpマネジメント株式会社 | イニシエータ端末、ターゲット端末、イニシエータ端末のエラー処理方法、ターゲット端末のエラー処理方法 |

| US9959078B2 (en) | 2015-01-30 | 2018-05-01 | Sandisk Technologies Llc | Multi-die rolling status mode for non-volatile storage |

| US10114690B2 (en) | 2015-02-13 | 2018-10-30 | Sandisk Technologies Llc | Multi-die status mode for non-volatile storage |

| US10303632B2 (en) | 2016-07-26 | 2019-05-28 | Micron Technology, Inc. | Accessing status information |

| CN106776391A (zh) * | 2016-12-13 | 2017-05-31 | 成都信息工程大学 | 一种NAND Flash控制器的控制方法和装置 |

| TWI696078B (zh) * | 2017-05-26 | 2020-06-11 | 旺宏電子股份有限公司 | 記憶體裝置及其操作方法 |

| US12099746B2 (en) * | 2019-12-16 | 2024-09-24 | Micron Technology, Inc. | Interrupt signaling for a memory device |

| JP2022049553A (ja) | 2020-09-16 | 2022-03-29 | キオクシア株式会社 | 半導体装置および方法 |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2667585B2 (ja) * | 1990-02-27 | 1997-10-27 | 松下電器産業株式会社 | デジタルプロセッサ |

| JPH06100998B2 (ja) * | 1992-10-02 | 1994-12-12 | インターナショナル・ビジネス・マシーンズ・コーポレイション | データ転送制御用インターフェース回路 |

| US6078520A (en) * | 1993-04-08 | 2000-06-20 | Hitachi, Ltd. | Flash memory control method and information processing system therewith |

| JPH0877066A (ja) * | 1994-08-31 | 1996-03-22 | Tdk Corp | フラッシュメモリコントローラ |

| US5799168A (en) * | 1996-01-05 | 1998-08-25 | M-Systems Flash Disk Pioneers Ltd. | Standardized flash controller |

| US5956743A (en) * | 1997-08-25 | 1999-09-21 | Bit Microsystems, Inc. | Transparent management at host interface of flash-memory overhead-bytes using flash-specific DMA having programmable processor-interrupt of high-level operations |

| US6141249A (en) * | 1999-04-01 | 2000-10-31 | Lexar Media, Inc. | Organization of blocks within a nonvolatile memory unit to effectively decrease sector write operation time |

| KR100351934B1 (ko) * | 1999-06-22 | 2002-09-12 | 삼성전자 주식회사 | 상태 읽기 동작을 갖는 플래시 메모리 장치 |

| US6442076B1 (en) * | 2000-06-30 | 2002-08-27 | Micron Technology, Inc. | Flash memory with multiple status reading capability |

| US6496900B1 (en) * | 2000-09-12 | 2002-12-17 | 3Ware, Inc. | Disk array system, controller, and method for verifying command data written to disk drives |

| US6976136B2 (en) * | 2001-05-07 | 2005-12-13 | National Semiconductor Corporation | Flash memory protection scheme for secured shared BIOS implementation in personal computers with an embedded controller |

| JP4841069B2 (ja) * | 2001-07-24 | 2011-12-21 | パナソニック株式会社 | 記憶装置 |

| KR100441608B1 (ko) * | 2002-05-31 | 2004-07-23 | 삼성전자주식회사 | 낸드 플래시 메모리 인터페이스 장치 |

| JP4550439B2 (ja) * | 2003-02-28 | 2010-09-22 | 東芝メモリシステムズ株式会社 | Ecc制御装置 |

| JP4601305B2 (ja) * | 2004-02-27 | 2010-12-22 | 富士通セミコンダクター株式会社 | 半導体装置 |

| US7315917B2 (en) * | 2005-01-20 | 2008-01-01 | Sandisk Corporation | Scheduling of housekeeping operations in flash memory systems |

| JP4849637B2 (ja) * | 2007-08-31 | 2012-01-11 | ルネサスエレクトロニクス株式会社 | メモリカード及びメモリコントローラ |

-

2007

- 2007-12-24 US US11/963,984 patent/US7966445B2/en active Active

-

2008

- 2008-12-23 EP EP08863427.4A patent/EP2225652B1/en active Active

- 2008-12-23 WO PCT/EP2008/068248 patent/WO2009080826A1/en active Application Filing

- 2008-12-23 JP JP2010538800A patent/JP5442634B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| WO2009080826A1 (en) | 2009-07-02 |

| JP2011508296A (ja) | 2011-03-10 |

| US7966445B2 (en) | 2011-06-21 |

| US20090164683A1 (en) | 2009-06-25 |

| EP2225652A1 (en) | 2010-09-08 |

| EP2225652B1 (en) | 2013-11-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5442634B2 (ja) | 読出ステータスのコントローラ | |

| US7263572B2 (en) | Bus bridge and data transfer method | |

| US7620747B1 (en) | Software based native command queuing | |

| US9146797B2 (en) | Method for ensuring remediation of hung multiplexer bus channels | |

| JP5824488B2 (ja) | トランザクション属性を修正するためのメモリ領域オーダリング要求に関するコンプリータ知識の使用 | |

| TWI498743B (zh) | 資料儲存系統以及其管理方法 | |

| US7484030B2 (en) | Storage controller and methods for using the same | |

| WO2023207571A1 (zh) | 一种数据传输方法及装置 | |

| US7934043B2 (en) | Data processing apparatus for controlling access to a memory based upon detection of completion of a DMA bus cycle | |

| US7895387B1 (en) | Devices and methods for sharing common target device with two different hosts according to common communication protocol | |

| US6883057B2 (en) | Method and apparatus embedding PCI-to-PCI bridge functions in PCI devices using PCI configuration header type 0 | |

| KR100843199B1 (ko) | 고속 아이.디.이. 인터페이스 장치 및 그 방법 | |

| US7571266B2 (en) | Peripheral device in a computerized system and method | |

| JP2008503833A (ja) | 並列通信バスに連結された装置内で割込みメッセージを待ち行列に入れるためのコンピュータシステム及び方法 | |

| EP2854039B1 (en) | Method and apparatus for copying data using cache | |

| KR100259585B1 (ko) | 디엠에이 콘트롤러 | |

| JP2006092077A (ja) | バスシステム | |

| US20060106957A1 (en) | Method and system for performance enhancement in a polled data storage environment | |

| JP4538054B2 (ja) | データ転送装置および方法 | |

| JP4343244B2 (ja) | マイクロコンピュータ | |

| JP2017199287A (ja) | 情報処理装置および情報処理方法 | |

| KR20050044197A (ko) | 피씨아이 디엠에이 에러 처리 장치 및 방법 | |

| JP2005228188A (ja) | 情報処理システム | |

| JP2004021505A (ja) | 通信制御装置及びマイクロコンピュータ | |

| JPH0261746A (ja) | Dma制御方式 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111207 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20111207 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121217 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130108 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130405 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130621 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130829 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131216 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131218 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5442634 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |