JP5412026B2 - 配線構造と配線形成方法及び薄膜トランジスタ基板とその製造方法 - Google Patents

配線構造と配線形成方法及び薄膜トランジスタ基板とその製造方法 Download PDFInfo

- Publication number

- JP5412026B2 JP5412026B2 JP2006246163A JP2006246163A JP5412026B2 JP 5412026 B2 JP5412026 B2 JP 5412026B2 JP 2006246163 A JP2006246163 A JP 2006246163A JP 2006246163 A JP2006246163 A JP 2006246163A JP 5412026 B2 JP5412026 B2 JP 5412026B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- copper

- gate

- thin film

- film transistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000010409 thin film Substances 0.000 title claims description 90

- 239000000758 substrate Substances 0.000 title claims description 81

- 238000000034 method Methods 0.000 title claims description 75

- 238000004519 manufacturing process Methods 0.000 title claims description 36

- 239000010408 film Substances 0.000 claims description 359

- 239000010949 copper Substances 0.000 claims description 156

- 229910052802 copper Inorganic materials 0.000 claims description 150

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 claims description 134

- 230000004888 barrier function Effects 0.000 claims description 69

- 239000004065 semiconductor Substances 0.000 claims description 58

- 238000005530 etching Methods 0.000 claims description 43

- -1 copper nitride Chemical class 0.000 claims description 21

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 claims description 19

- 229910000881 Cu alloy Inorganic materials 0.000 claims description 17

- 238000001039 wet etching Methods 0.000 claims description 15

- 230000015572 biosynthetic process Effects 0.000 claims description 14

- 239000007789 gas Substances 0.000 claims description 11

- 238000004544 sputter deposition Methods 0.000 claims description 9

- 238000001312 dry etching Methods 0.000 claims description 8

- 229910052757 nitrogen Inorganic materials 0.000 claims description 7

- 150000001875 compounds Chemical class 0.000 claims description 3

- 229910052759 nickel Inorganic materials 0.000 claims description 3

- 229910052758 niobium Inorganic materials 0.000 claims description 3

- 229910052763 palladium Inorganic materials 0.000 claims description 3

- 229910052697 platinum Inorganic materials 0.000 claims description 3

- 229910052715 tantalum Inorganic materials 0.000 claims description 3

- 229910052720 vanadium Inorganic materials 0.000 claims description 3

- 229910052726 zirconium Inorganic materials 0.000 claims description 3

- 238000011065 in-situ storage Methods 0.000 claims description 2

- 239000010410 layer Substances 0.000 description 116

- 239000000463 material Substances 0.000 description 32

- 229920002120 photoresistant polymer Polymers 0.000 description 32

- 238000003860 storage Methods 0.000 description 26

- 230000008569 process Effects 0.000 description 25

- 230000007797 corrosion Effects 0.000 description 21

- 238000005260 corrosion Methods 0.000 description 21

- 239000011229 interlayer Substances 0.000 description 16

- 239000004973 liquid crystal related substance Substances 0.000 description 13

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 12

- 229910021417 amorphous silicon Inorganic materials 0.000 description 12

- 230000001681 protective effect Effects 0.000 description 12

- 239000000126 substance Substances 0.000 description 12

- JPVYNHNXODAKFH-UHFFFAOYSA-N Cu2+ Chemical compound [Cu+2] JPVYNHNXODAKFH-UHFFFAOYSA-N 0.000 description 9

- 229910052581 Si3N4 Inorganic materials 0.000 description 9

- 229910045601 alloy Inorganic materials 0.000 description 9

- 239000000956 alloy Substances 0.000 description 9

- 229910001431 copper ion Inorganic materials 0.000 description 9

- 238000005401 electroluminescence Methods 0.000 description 9

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 9

- 239000012535 impurity Substances 0.000 description 7

- 238000000059 patterning Methods 0.000 description 7

- 229910052782 aluminium Inorganic materials 0.000 description 6

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 6

- 229910052786 argon Inorganic materials 0.000 description 6

- 239000011368 organic material Substances 0.000 description 6

- 238000005192 partition Methods 0.000 description 6

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 5

- 238000005229 chemical vapour deposition Methods 0.000 description 5

- 239000011810 insulating material Substances 0.000 description 5

- 229910052814 silicon oxide Inorganic materials 0.000 description 5

- 229910004205 SiNX Inorganic materials 0.000 description 4

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 4

- 230000000903 blocking effect Effects 0.000 description 4

- 239000003990 capacitor Substances 0.000 description 4

- 239000004020 conductor Substances 0.000 description 4

- 238000000151 deposition Methods 0.000 description 4

- 229910001873 dinitrogen Inorganic materials 0.000 description 4

- 230000035515 penetration Effects 0.000 description 4

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 4

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 4

- 229910052709 silver Inorganic materials 0.000 description 4

- 239000004332 silver Substances 0.000 description 4

- QTBSBXVTEAMEQO-UHFFFAOYSA-N Acetic acid Chemical compound CC(O)=O QTBSBXVTEAMEQO-UHFFFAOYSA-N 0.000 description 3

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 3

- 206010034972 Photosensitivity reaction Diseases 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- 150000002500 ions Chemical class 0.000 description 3

- 229910052751 metal Inorganic materials 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- 229910052750 molybdenum Inorganic materials 0.000 description 3

- 239000011733 molybdenum Substances 0.000 description 3

- 230000036211 photosensitivity Effects 0.000 description 3

- 238000002310 reflectometry Methods 0.000 description 3

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 2

- 229910001182 Mo alloy Inorganic materials 0.000 description 2

- 229910016027 MoTi Inorganic materials 0.000 description 2

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 239000011261 inert gas Substances 0.000 description 2

- 229910010272 inorganic material Inorganic materials 0.000 description 2

- 239000011147 inorganic material Substances 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000000149 penetrating effect Effects 0.000 description 2

- 239000000049 pigment Substances 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- GRYLNZFGIOXLOG-UHFFFAOYSA-N Nitric acid Chemical compound O[N+]([O-])=O GRYLNZFGIOXLOG-UHFFFAOYSA-N 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 238000007641 inkjet printing Methods 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 230000002452 interceptive effect Effects 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 238000010030 laminating Methods 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 238000013507 mapping Methods 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 150000002751 molybdenum Chemical class 0.000 description 1

- 229910017604 nitric acid Inorganic materials 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 238000001259 photo etching Methods 0.000 description 1

- 238000005546 reactive sputtering Methods 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 238000005477 sputtering target Methods 0.000 description 1

- OFIYHXOOOISSDN-UHFFFAOYSA-N tellanylidenegallium Chemical compound [Te]=[Ga] OFIYHXOOOISSDN-UHFFFAOYSA-N 0.000 description 1

- 239000012780 transparent material Substances 0.000 description 1

Images

Landscapes

- Liquid Crystal (AREA)

- Electrodes Of Semiconductors (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Thin Film Transistor (AREA)

Description

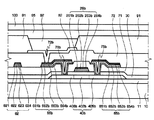

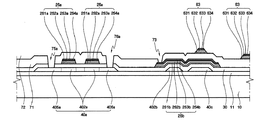

22:ゲート線

24:ゲート端部

26:ゲート電極

27:ストレージ電極

28:ストレージ電極線

30:ゲート絶縁膜

40:半導体層

55、56:オーミックコンタクト層

62:データ線

65:ソース電極

66:ドレイン電極

67:ドレイン電極拡張部

68:データ端部

70:保護膜

82:画素電極

Claims (10)

- 絶縁基板上に第1の方向に延長されたゲート線及び前記ゲート線に接続されたゲート電極を含むゲート配線を形成し、

前記絶縁基板上に前記ゲート線と交差するように第2の方向に延長されたデータ線、前記データ線に接続されたソース電極及び前記ソース電極と離隔されて設けられるドレイン電極を含み、前記ゲート配線と絶縁されているデータ配線を形成し、

前記ゲート配線と前記データ線及び前記データ線に接続されたソース電極を含むデータ配線との上に各画素毎に前記ドレイン電極と接続された画素電極を形成し、

前記ゲート配線又は前記データ配線の形成は、

バリヤ膜を形成し、

前記バリヤ膜上に銅又は銅合金を含む銅導電膜を形成し、

前記銅導電膜上に銅窒化物を含む中間膜を形成し、

前記中間膜上にIZO、ITO、アモルファスITO、又はこれらの組み合わせを含むキャッピング膜を形成し、

前記キャッピング膜、前記中間膜及び前記銅導電膜をエッチングして下部の前記バリヤ膜を露出させ、

前記バリヤ膜をエッチングすること、

を含み、

前記バリヤ膜は、Ta、V、Zr、Nb、Co、Ni、Pd、Pt又はこれらの化合物を含むことを特徴とする薄膜トランジスタ基板の製造方法。 - 前記中間膜の形成は、窒素を含む雰囲気下で銅をターゲットとしてスパッタリングすることを特徴とする請求項1に記載の薄膜トランジスタ基板の製造方法。

- 前記中間膜の形成は、前記銅導電膜の形成に連続して窒素を供給しながらin−situにおこなわれることを特徴とする請求項2に記載の薄膜トランジスタ基板の製造方法。

- 前記中間膜の厚さは、5nm以上100nm以下であることを特徴とする請求項1に記載の薄膜トランジスタ基板の製造方法。

- 前記中間膜は、0.001atom%以上50atom%以下の窒素を含有することを特徴とする請求項1に記載の薄膜トランジスタ基板の製造方法。

- 前記キャッピング膜、前記中間膜及び前記銅導電膜のエッチングは、ウエットエッチングであることを特徴とする請求項1に記載の薄膜トランジスタ基板の製造方法。

- 前記キャッピング膜、前記中間膜及び前記銅導電膜のエッチングは、前記キャッピング膜、前記中間膜及び前記銅導電膜を一括的にエッチングすることを特徴とする請求項6に記載の薄膜トランジスタ基板の製造方法。

- 前記バリヤ膜のエッチングは、HCl、Cl2、H2、O2又はこれらの組み合わせを含むエッチングガスを使用してドライエッチングすることを特徴とする請求項1に記載の薄膜トランジスタ基板の製造方法。

- 前記データ配線の形成の前記バリヤ膜のエッチング後に前記エッチングされたバリヤ膜下部のオーミックコンタクト層をエッチングして下部の半導体層を露出させることを特徴とする請求項1に記載の薄膜トランジスタ基板の製造方法。

- 前記オーミックコンタクト層のエッチングは、前記データ配線のバリヤ膜と連続的にエッチングすることを特徴とする請求項9に記載の薄膜トランジスタ基板の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006246163A JP5412026B2 (ja) | 2006-09-11 | 2006-09-11 | 配線構造と配線形成方法及び薄膜トランジスタ基板とその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006246163A JP5412026B2 (ja) | 2006-09-11 | 2006-09-11 | 配線構造と配線形成方法及び薄膜トランジスタ基板とその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008066678A JP2008066678A (ja) | 2008-03-21 |

| JP2008066678A5 JP2008066678A5 (ja) | 2009-10-15 |

| JP5412026B2 true JP5412026B2 (ja) | 2014-02-12 |

Family

ID=39289073

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006246163A Active JP5412026B2 (ja) | 2006-09-11 | 2006-09-11 | 配線構造と配線形成方法及び薄膜トランジスタ基板とその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5412026B2 (ja) |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20070049278A (ko) * | 2005-11-08 | 2007-05-11 | 삼성전자주식회사 | 배선, 이를 포함하는 박막 트랜지스터 기판과 그 제조 방법 |

| JP5214125B2 (ja) * | 2006-09-11 | 2013-06-19 | 三星ディスプレイ株式會社 | 配線構造と配線形成方法及び薄膜トランジスタ基板とその製造方法 |

| JP5150382B2 (ja) * | 2008-06-24 | 2013-02-20 | 株式会社アルバック | 表示装置用パネル、液晶表示装置、配線形成方法 |

| JP2012033516A (ja) * | 2008-11-26 | 2012-02-16 | Ulvac Japan Ltd | トランジスタ及びその製造方法。 |

| KR101117642B1 (ko) | 2009-11-16 | 2012-03-05 | 삼성모바일디스플레이주식회사 | 유기 발광 표시 장치 및 그 제조 방법 |

| KR102450889B1 (ko) * | 2009-12-04 | 2022-10-06 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| WO2011104943A1 (ja) | 2010-02-24 | 2011-09-01 | シャープ株式会社 | 液晶表示パネル及び液晶表示装置 |

| KR102068956B1 (ko) | 2012-02-15 | 2020-01-23 | 엘지디스플레이 주식회사 | 박막트랜지스터, 박막트랜지스터 어레이 기판 및 이의 제조방법 |

| KR20140032155A (ko) * | 2012-09-06 | 2014-03-14 | 삼성디스플레이 주식회사 | 박막 트랜지스터 기판 및 그 제조방법 |

| KR101953215B1 (ko) * | 2012-10-05 | 2019-03-04 | 삼성디스플레이 주식회사 | 식각 조성물, 금속 배선 및 표시 기판의 제조방법 |

| US10263114B2 (en) * | 2016-03-04 | 2019-04-16 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, method for manufacturing the same, or display device including the same |

| JP6706653B2 (ja) * | 2018-03-20 | 2020-06-10 | シャープ株式会社 | アクティブマトリクス基板 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10133597A (ja) * | 1996-07-26 | 1998-05-22 | Canon Inc | 配線基板、該配線基板の製造方法、該配線基板を備えた液晶素子及び該液晶素子の製造方法 |

| JP3447535B2 (ja) * | 1997-10-24 | 2003-09-16 | シャープ株式会社 | 薄膜トランジスタおよびその製造方法 |

| JP3916334B2 (ja) * | 1999-01-13 | 2007-05-16 | シャープ株式会社 | 薄膜トランジスタ |

| JP4238956B2 (ja) * | 2000-01-12 | 2009-03-18 | エルジー ディスプレイ カンパニー リミテッド | 銅配線基板及びその製造方法並びに液晶表示装置 |

| JP2004172150A (ja) * | 2002-11-15 | 2004-06-17 | Nec Kagoshima Ltd | 積層構造配線の製造方法 |

| JP2006005190A (ja) * | 2004-06-18 | 2006-01-05 | Renesas Technology Corp | 半導体装置 |

| KR20060064388A (ko) * | 2004-12-08 | 2006-06-13 | 삼성전자주식회사 | 박막 트랜지스터, 이의 제조 방법, 이를 갖는 표시장치 및표시장치의 제조 방법 |

| KR20070049278A (ko) * | 2005-11-08 | 2007-05-11 | 삼성전자주식회사 | 배선, 이를 포함하는 박막 트랜지스터 기판과 그 제조 방법 |

| JP5214125B2 (ja) * | 2006-09-11 | 2013-06-19 | 三星ディスプレイ株式會社 | 配線構造と配線形成方法及び薄膜トランジスタ基板とその製造方法 |

-

2006

- 2006-09-11 JP JP2006246163A patent/JP5412026B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2008066678A (ja) | 2008-03-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5412026B2 (ja) | 配線構造と配線形成方法及び薄膜トランジスタ基板とその製造方法 | |

| KR101167661B1 (ko) | 배선 구조와 배선 형성 방법 및 박막 트랜지스터 기판과 그제조 방법 | |

| KR101168728B1 (ko) | 배선 구조와 배선 형성 방법 및 박막 트랜지스터 기판과 그제조 방법 | |

| JP5214125B2 (ja) | 配線構造と配線形成方法及び薄膜トランジスタ基板とその製造方法 | |

| KR101168729B1 (ko) | 배선 구조와 배선 형성 방법 및 박막 트랜지스터 기판과 그제조 방법 | |

| JP5111790B2 (ja) | エッチング液及びこれを用いた配線形成方法 | |

| JP2007134691A (ja) | 配線、これを含む薄膜トランジスタ基板、及びその製造方法 | |

| KR102068956B1 (ko) | 박막트랜지스터, 박막트랜지스터 어레이 기판 및 이의 제조방법 | |

| US7635436B2 (en) | Etchant composition and manufacturing method for thin film transistor array panel | |

| US20060118793A1 (en) | Thin film transistor array panel and method for manufacturing the same | |

| JP2007212699A (ja) | 反射型tft基板及び反射型tft基板の製造方法 | |

| KR20080037296A (ko) | 박막 트랜지스터 기판 및 그 제조방법 | |

| JP2010147494A (ja) | 薄膜トランジスタ及びその製造方法 | |

| JP2006191013A (ja) | 薄膜トランジスタ基板、その製造方法及び液晶表示装置 | |

| JP4632617B2 (ja) | 液晶表示装置用薄膜トランジスタ基板及びその製造方法 | |

| KR101046928B1 (ko) | 박막 트랜지스터 표시판과 그 제조방법 | |

| JP2007506139A (ja) | 薄膜トランジスタ表示板、これを含む平板ディスプレイ表示装置及びその製造方法 | |

| KR20080047179A (ko) | 박막 트랜지스터 기판 및 이의 제조 방법 | |

| JP3221094B2 (ja) | アクティブマトリクスパネル及びその製造方法 | |

| KR20070018287A (ko) | 배선 구조와 배선 형성 방법 및 박막 트랜지스터 기판과 그제조 방법 | |

| KR20060068996A (ko) | Tft 기판과 이의 다층 배선의 제조방법 | |

| KR20050051866A (ko) | 박막 트랜지스터 표시판 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090902 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090902 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100709 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120919 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120925 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20121213 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121219 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130402 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130627 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131022 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131111 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5412026 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: R3D02 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |